ECE 448 Lab 6 Using Pico Blaze Fast

ECE 448: Lab 6 Using Pico. Blaze Fast Sorting Class Exercise 2

Agenda for today • Introduction to Lab 6 Exercise 2 • Lab 5 Demos

Introduction to Lab 6 Exercise 2 ECE 448 – FPGA and ASIC Design with VHDL

Sources • P. Chu, FPGA Prototyping by VHDL Examples Chapter 14, Picoblaze Overview Chapter 15, Picoblaze Assembly Code Development Chapter 16, Picoblaze I/O Interface Chapter 17, Picoblaze Interrupt Interface • K. Chapman, Pico. Blaze for Spartan-6, Virtex-6, 7 -Series, Zynq and Ultra. Scale Devices (KCPSM 6)) ECE 448 – FPGA and ASIC Design with VHDL 4

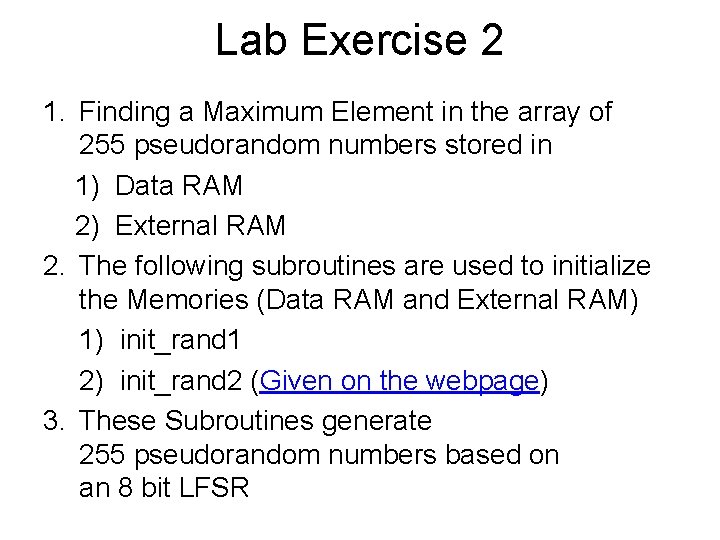

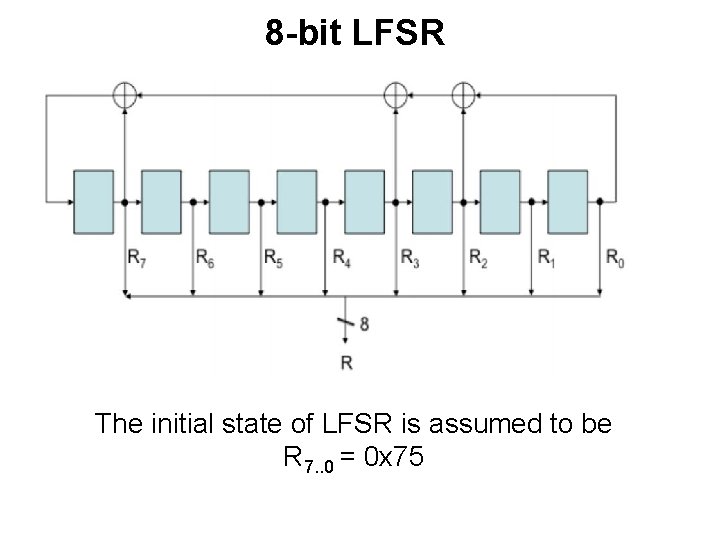

Lab Exercise 2 1. Finding a Maximum Element in the array of 255 pseudorandom numbers stored in 1) Data RAM 2) External RAM 2. The following subroutines are used to initialize the Memories (Data RAM and External RAM) 1) init_rand 1 2) init_rand 2 (Given on the webpage) 3. These Subroutines generate 255 pseudorandom numbers based on an 8 bit LFSR

8 -bit LFSR The initial state of LFSR is assumed to be R 7. . 0 = 0 x 75

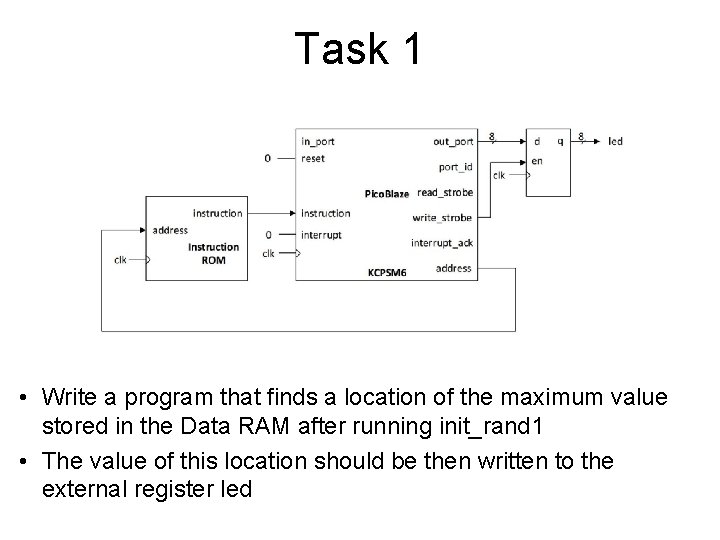

Task 1 • Write a program that finds a location of the maximum value stored in the Data RAM after running init_rand 1 • The value of this location should be then written to the external register led

Task 1 - Subtasks 1) Debug, verify, and demonstrate the operation of your program using FIDEx IDE 2) Generate the code of Instruction RAM 3) Describe a top-level circuit, shown in the diagram on the previous slide, using VHDL 4) Prepare a UCF file in which you associate outputs of the register led with the pins of Spartan-6/Artix-7 connected to 8 LEDs of Nexys 3/Nexys 4 5) Implement the entire circuit using FPGA tools, and verify its operation using Nexys 3/Nexys 4

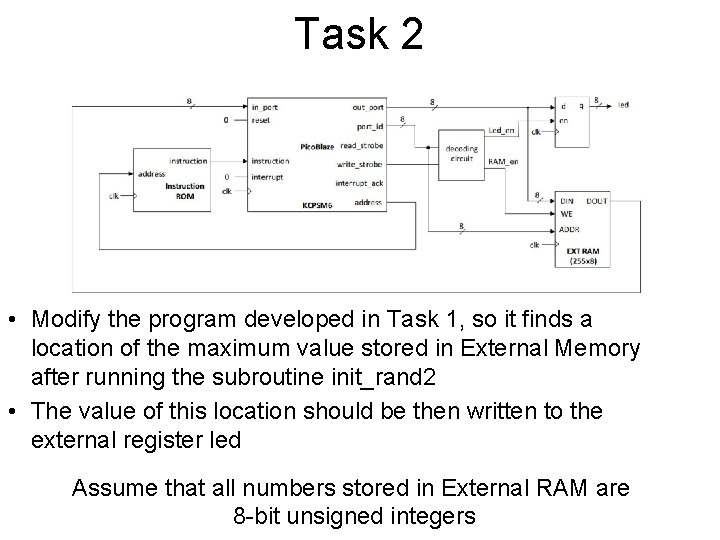

Task 2 • Modify the program developed in Task 1, so it finds a location of the maximum value stored in External Memory after running the subroutine init_rand 2 • The value of this location should be then written to the external register led Assume that all numbers stored in External RAM are 8 -bit unsigned integers

Task 2 - Subtasks 1) Design the “decoding circuit” shown in the diagram. This circuit should generate the control signals led_en and RAM_en, based on the values of write_strobe and port_id. Assume that the register led is visible under the I/O address 0 x. FF and EXT RAM is visible under the address range 0 x 00. . 0 x. FE. 2) Generate the code of Instruction RAM. 3) Describe a top-level circuit, shown in the diagram on the previous slide, using VHDL. 4) Simulate, verify, and demonstrate the operation of this circuit using ISim. 5) Implement the top-level circuit using FPGA tools, and verify its operation using Nexys 3/Nexys 4. Use the UCF file developed in Task 1.

Lab 5 Demos ECE 448 – FPGA and ASIC Design with VHDL 11

- Slides: 11