Digital Packaging Processor G Hurford Conceptual Design Review

- Slides: 17

Digital Packaging Processor G. Hurford Conceptual Design Review - NJIT April 25, 2011

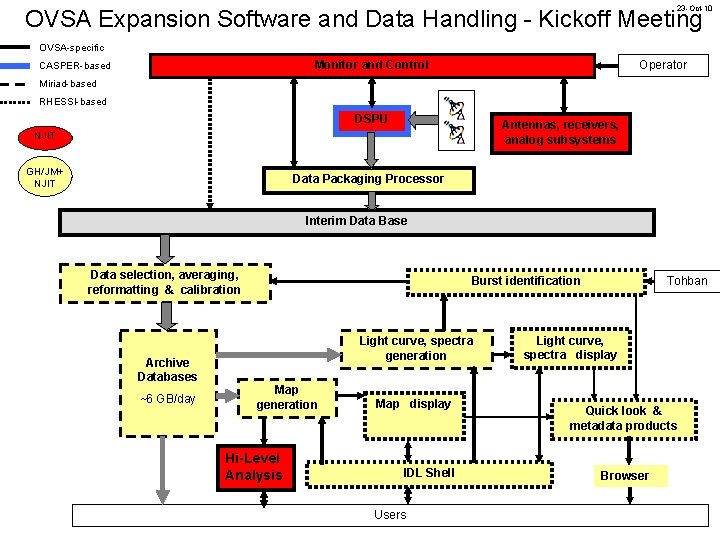

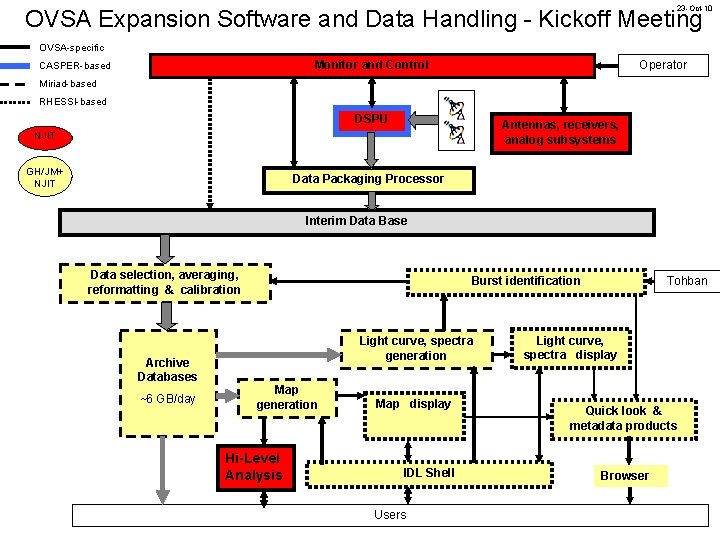

23 -Oct-10 OVSA Expansion Software and Data Handling - Kickoff Meeting OVSA-specific Monitor and Control CASPER-based Operator Miriad-based RHESSI-based DSPU Antennas, receivers, analog subsystems NJIT GH/JM+ NJIT Data Packaging Processor Interim Data Base Data selection, averaging, reformatting & calibration Archive Databases ~6 GB/day Burst identification Light curve, spectra generation Map generation Hi-Level Analysis Map display IDL Shell Users Tohban Light curve, spectra display Quick look & metadata products Browser

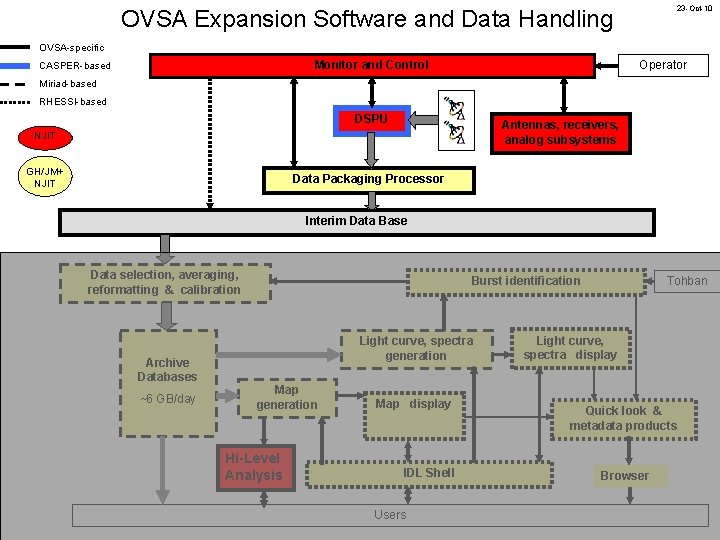

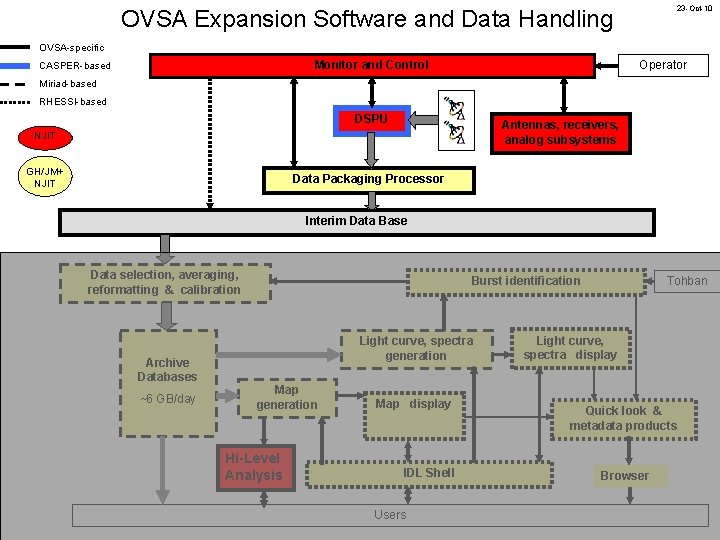

23 -Oct-10 OVSA Expansion Software and Data Handling OVSA-specific Monitor and Control CASPER-based Operator Miriad-based RHESSI-based DSPU Antennas, receivers, analog subsystems NJIT GH/JM+ NJIT Data Packaging Processor Interim Data Base Data selection, averaging, reformatting & calibration Archive Databases ~6 GB/day Burst identification Light curve, spectra generation Map generation Hi-Level Analysis Map display IDL Shell Users Tohban Light curve, spectra display Quick look & metadata products Browser

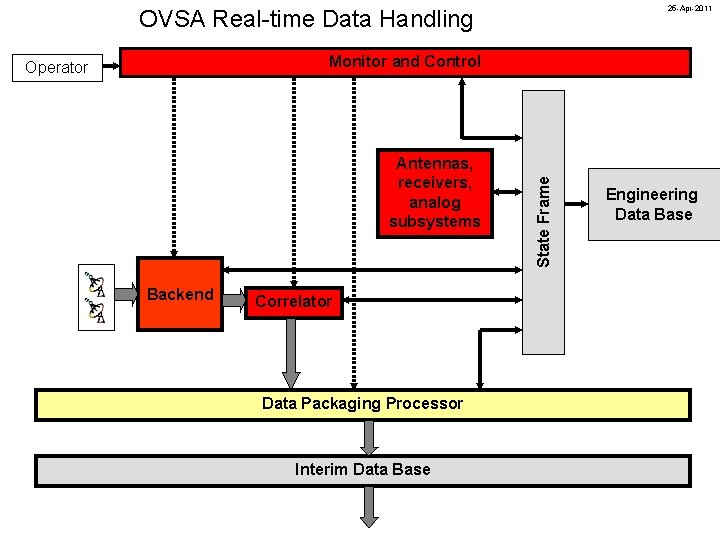

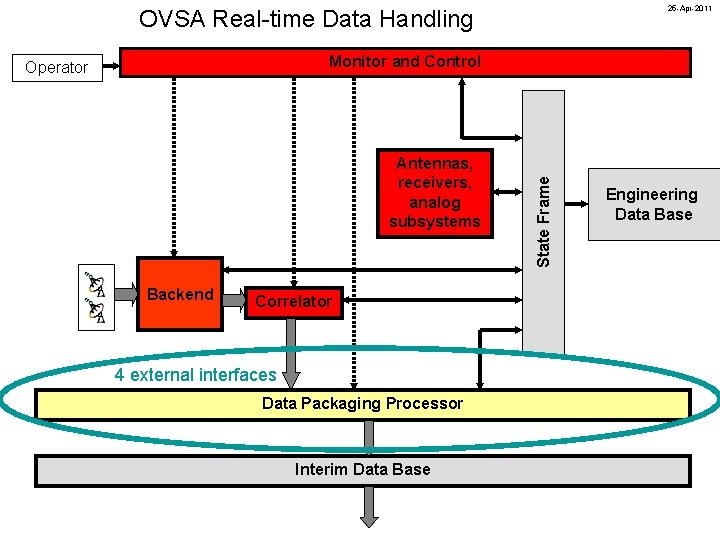

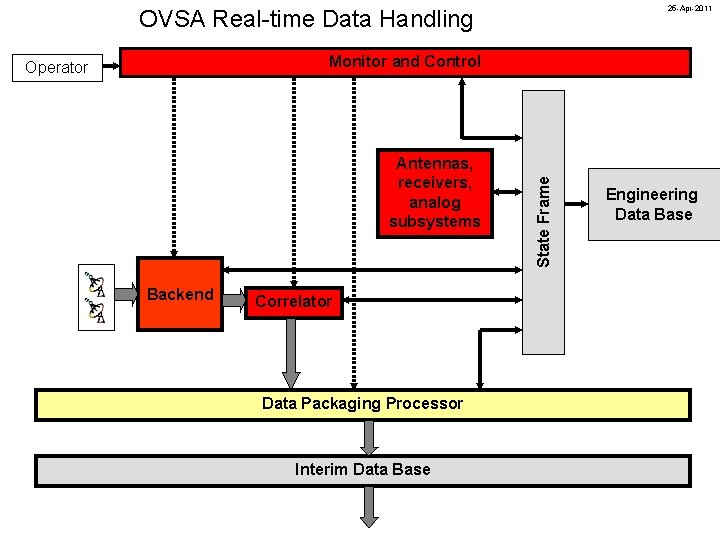

25 -Apr-2011 OVSA Real-time Data Handling Antennas, receivers, analog subsystems Backend Correlator Data Packaging Processor Interim Data Base State Frame Monitor and Control Operator Engineering Data Base

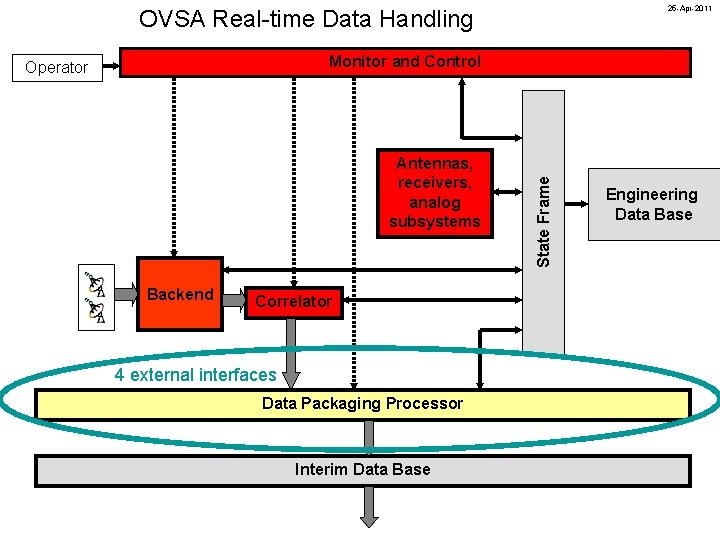

25 -Apr-2011 OVSA Real-time Data Handling Antennas, receivers, analog subsystems Backend Correlator 4 external interfaces Data Packaging Processor Interim Data Base State Frame Monitor and Control Operator Engineering Data Base

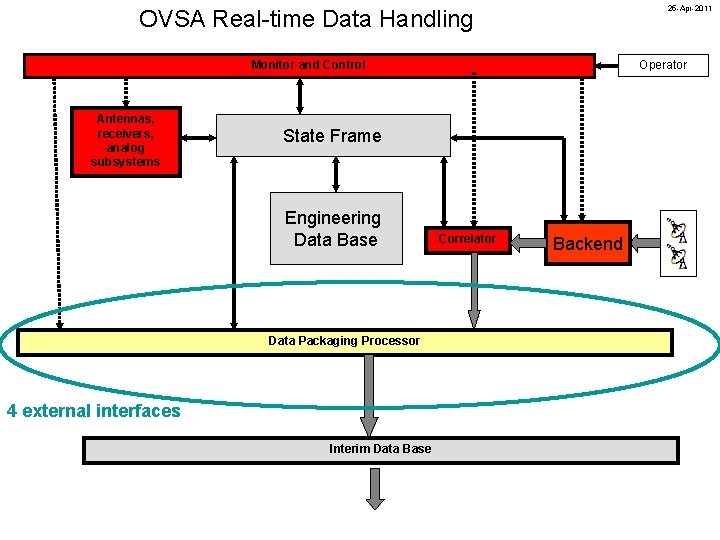

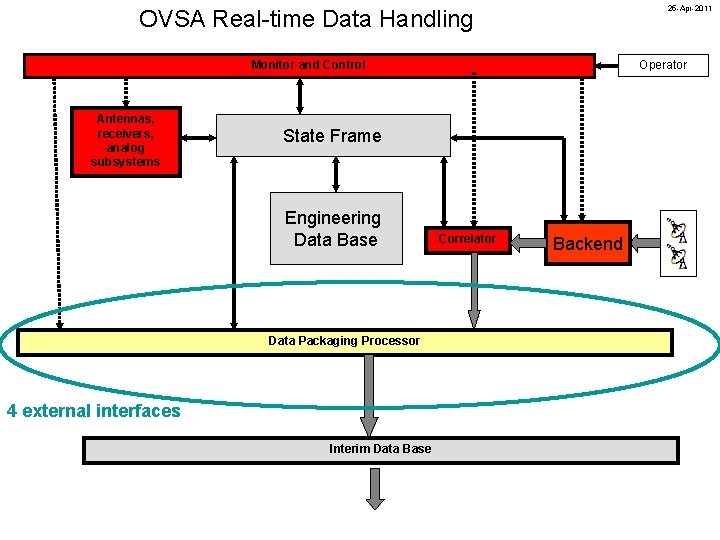

25 -Apr-2011 OVSA Real-time Data Handling Monitor and Control Antennas, receivers, analog subsystems Operator State Frame Engineering Data Base Data Packaging Processor 4 external interfaces Interim Data Base Correlator Backend

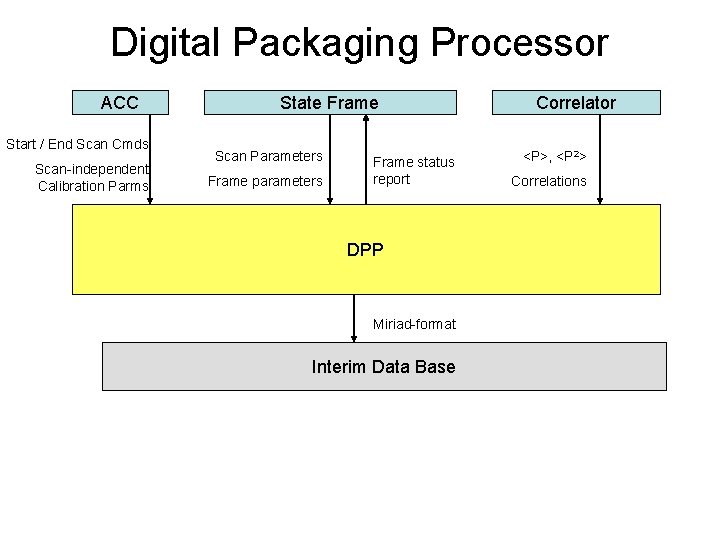

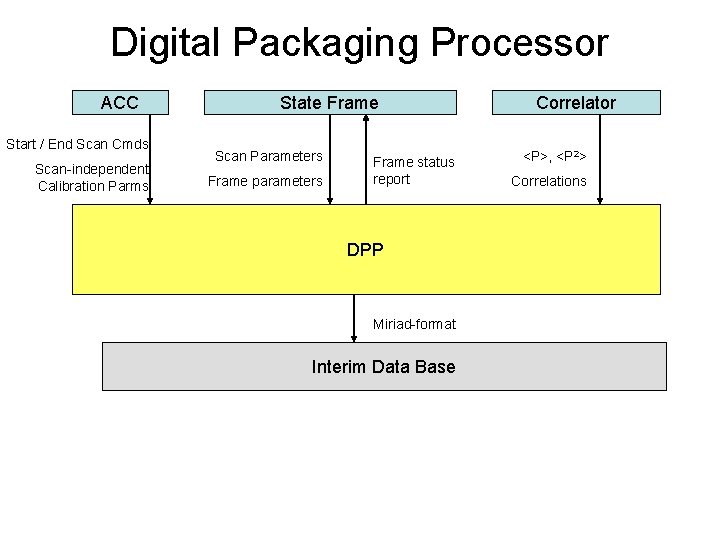

Digital Packaging Processor ACC Start / End Scan Cmds Scan-independent Calibration Parms State Frame Scan Parameters Frame parameters Frame status report DPP Miriad-format Interim Data Base Correlator <P>, <P 2> Correlations

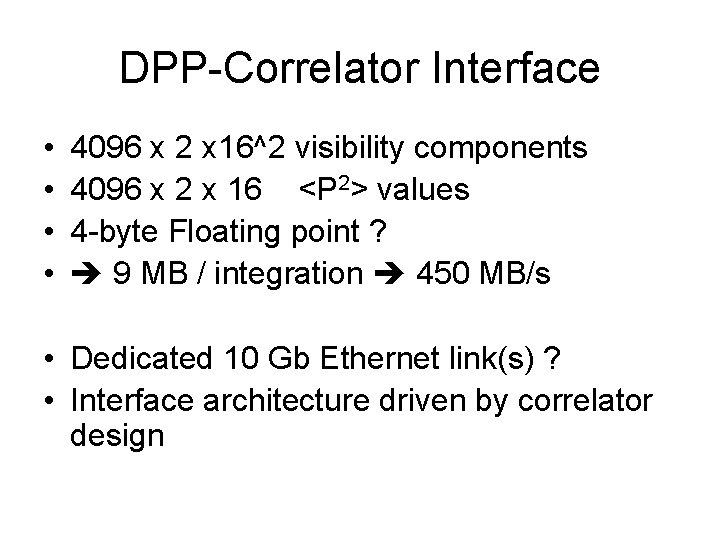

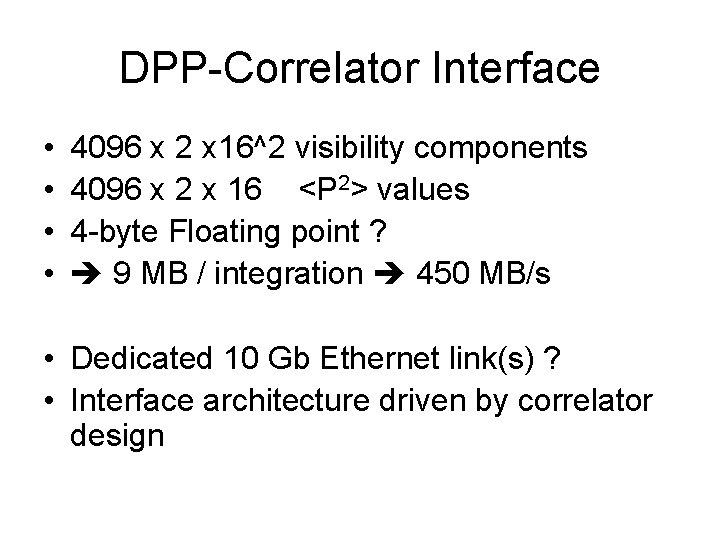

DPP-Correlator Interface • • 4096 x 2 x 16^2 visibility components 4096 x 2 x 16 <P 2> values 4 -byte Floating point ? 9 MB / integration 450 MB/s • Dedicated 10 Gb Ethernet link(s) ? • Interface architecture driven by correlator design

DPP State Frame Interface • Specifics TBD • DPP will assume ‘header’ parameters are stable during scan • Otherwise DPP reads state frame every ½ second • Assume state frame has flags indicating update state • DPP updates state frame with processing status • ISSUE: Should RFI statistics be ignored, written to state frame, or included in IDB?

DPP – ACC Interface • Low data volume • Shared Ethernet line • ACC issues start scan, end scan commands • ACC provides scan-independent calibration parameters (or should these be in state frame? )

DPP – Interim Data Base Interface • DPP writes directly to dual-port IDB disk • DPP writes data in a Miriad-compatible format • Science frame: ~1 MB 1. 4 MB/s 60 GB/day (0. 7 second, 500 science channels, 2 polarizations, 2 byte data, 16^2 visibility components, x 2 overhead) • IDB disk is also accessible to a data analysis platform

DPP – Processing Tasks (1) • Stage 1 – Every integration interval • Evaluate kurtosis data to identify RFI-affected subbands as a function of frequeny only. • Combine with pre-flagged subbands to generate a destination vector for each subband • Apply complex gains at subband level ? ? • Average subband data into science frequency bands • Save 1 st 3 moments of averages. • Save RFI statistics ? ?

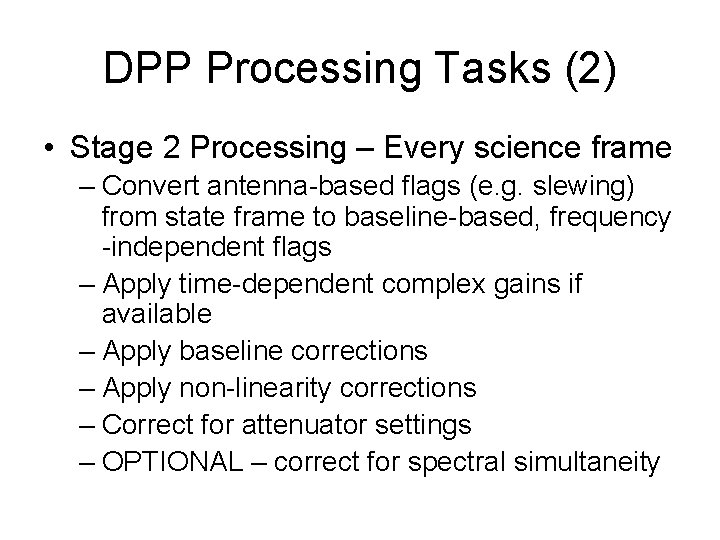

DPP Processing Tasks (2) • Stage 2 Processing – Every science frame – Convert antenna-based flags (e. g. slewing) from state frame to baseline-based, frequency -independent flags – Apply time-dependent complex gains if available – Apply baseline corrections – Apply non-linearity corrections – Correct for attenuator settings – OPTIONAL – correct for spectral simultaneity

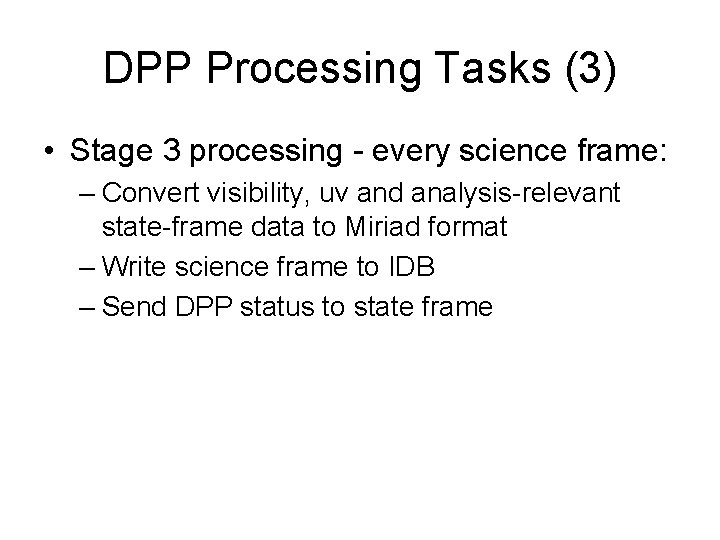

DPP Processing Tasks (3) • Stage 3 processing - every science frame: – Convert visibility, uv and analysis-relevant state-frame data to Miriad format – Write science frame to IDB – Send DPP status to state frame

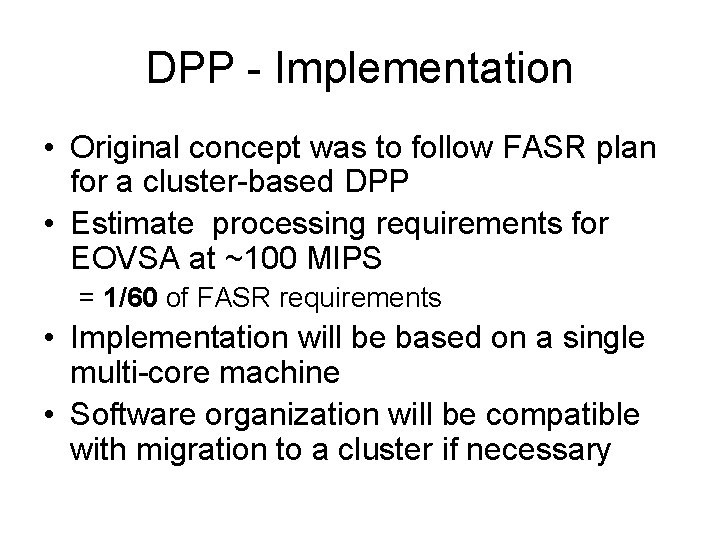

DPP - Implementation • Original concept was to follow FASR plan for a cluster-based DPP • Estimate processing requirements for EOVSA at ~100 MIPS = 1/60 of FASR requirements • Implementation will be based on a single multi-core machine • Software organization will be compatible with migration to a cluster if necessary

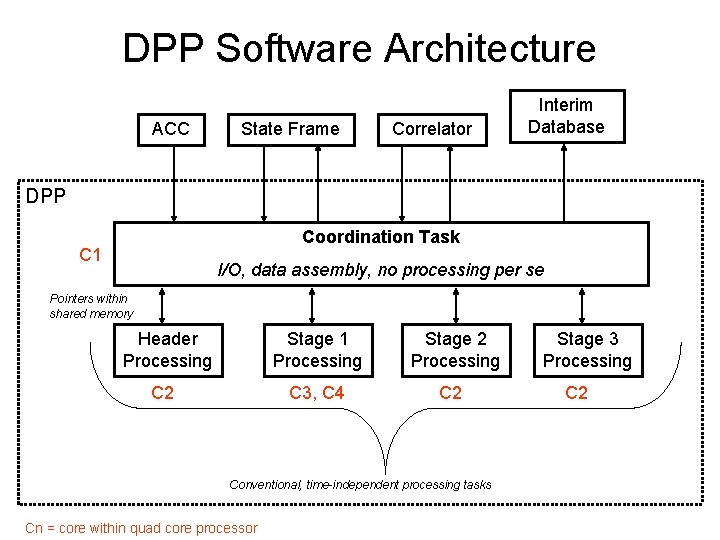

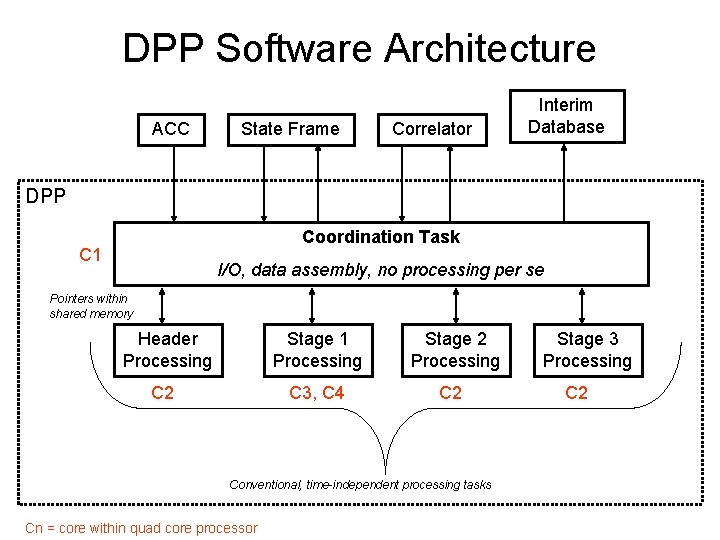

DPP Software Architecture ACC State Frame Correlator Interim Database DPP Coordination Task C 1 I/O, data assembly, no processing per se Pointers within shared memory Header Processing Stage 1 Processing Stage 2 Processing C 2 C 3, C 4 C 2 Conventional, time-independent processing tasks Cn = core within quad core processor Stage 3 Processing C 2

DPP Next Steps • • Agreement on approach Detailed definition of interfaces Definition of processing algorithms Machine selection and purchase – Development platform? – Language selection (Fortran + ? ) • Test data sets? • Early timing tests