Design and Implementation of VLSI Systems EN 0160

- Slides: 15

Design and Implementation of VLSI Systems (EN 0160) Lecture 12: Logical Effort (2/2) Prof. Sherief Reda Division of Engineering, Brown University Spring 2007 [sources: Weste/Addison Wesley – Rabaey/Pearson] S. Reda EN 160 SP’ 07

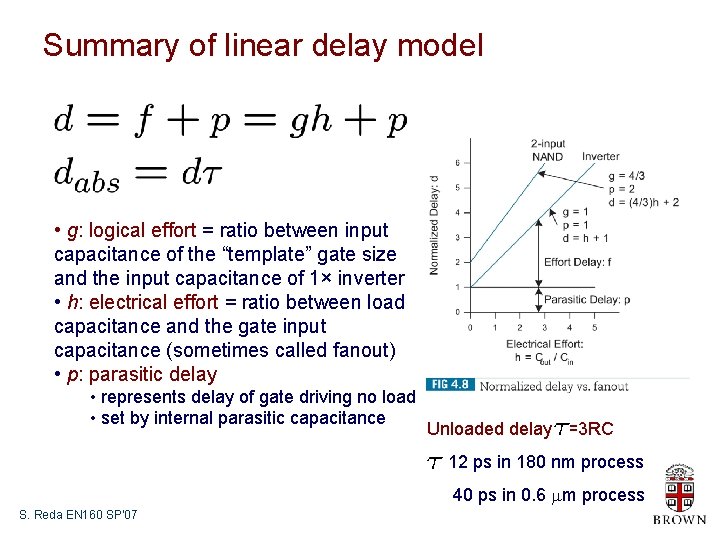

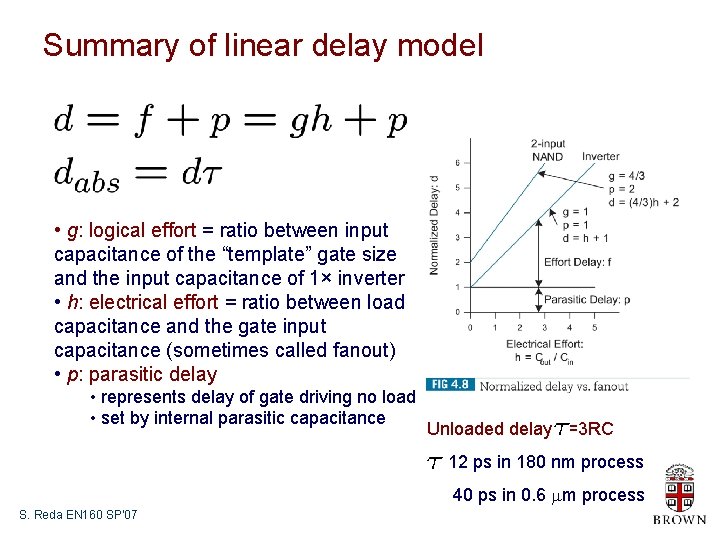

Summary of linear delay model • g: logical effort = ratio between input capacitance of the “template” gate size and the input capacitance of 1× inverter • h: electrical effort = ratio between load capacitance and the gate input capacitance (sometimes called fanout) • p: parasitic delay • represents delay of gate driving no load • set by internal parasitic capacitance Unloaded delay =3 RC 12 ps in 180 nm process 40 ps in 0. 6 mm process S. Reda EN 160 SP’ 07

Example: FO 4 Inverter • Estimate the delay of a fanout-of-4 (FO 4) inverter Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: Absolute Delay: S. Reda EN 160 SP’ 07 g= h= p= d= dabs =

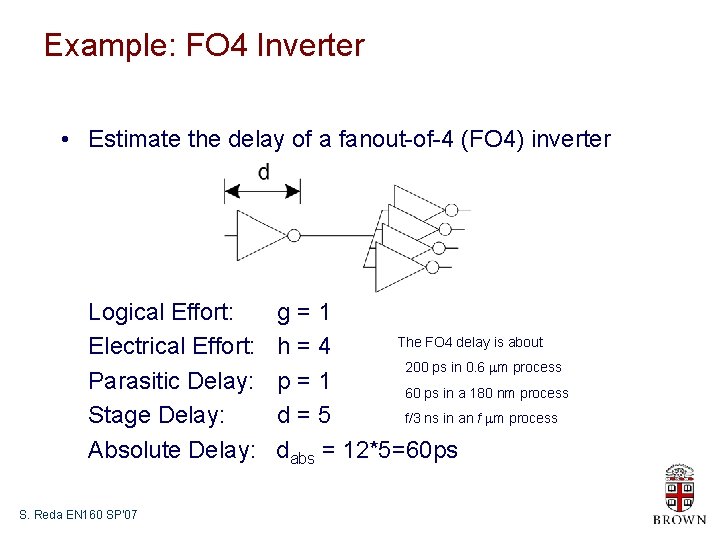

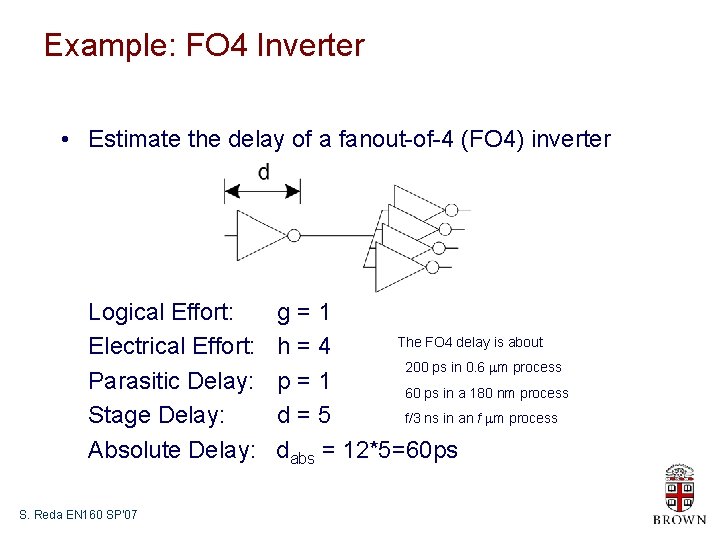

Example: FO 4 Inverter • Estimate the delay of a fanout-of-4 (FO 4) inverter Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: Absolute Delay: S. Reda EN 160 SP’ 07 g=1 The FO 4 delay is about h=4 200 ps in 0. 6 mm process p=1 60 ps in a 180 nm process f/3 ns in an f mm process d=5 dabs = 12*5=60 ps

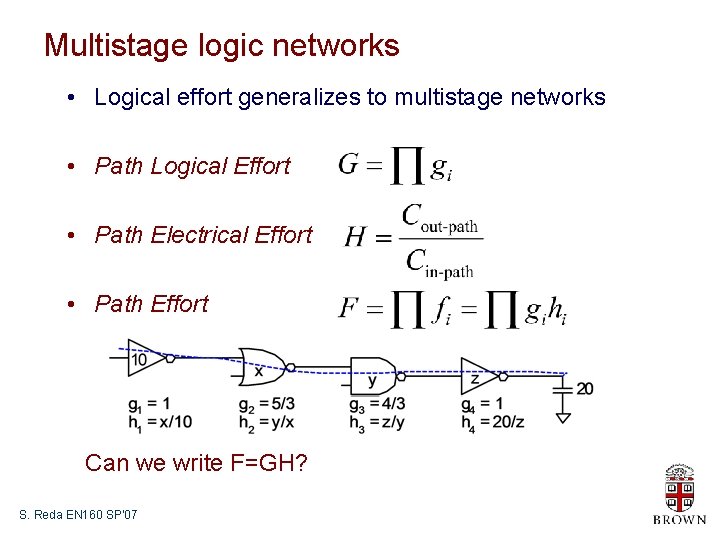

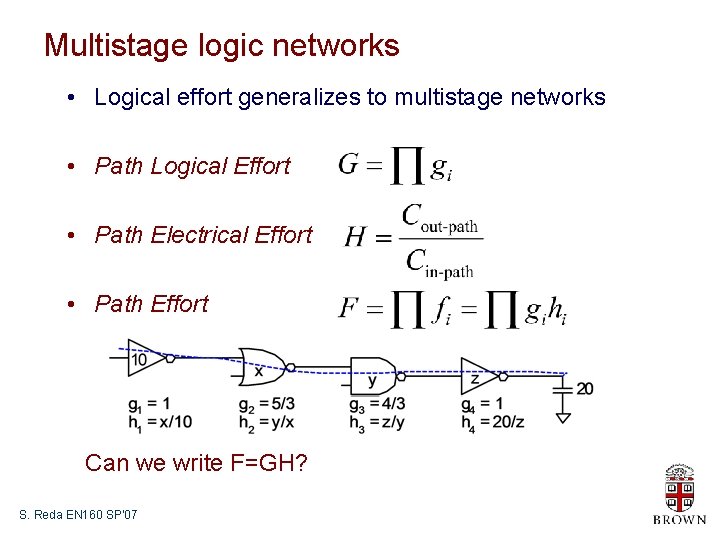

Multistage logic networks • Logical effort generalizes to multistage networks • Path Logical Effort • Path Electrical Effort • Path Effort Can we write F=GH? S. Reda EN 160 SP’ 07

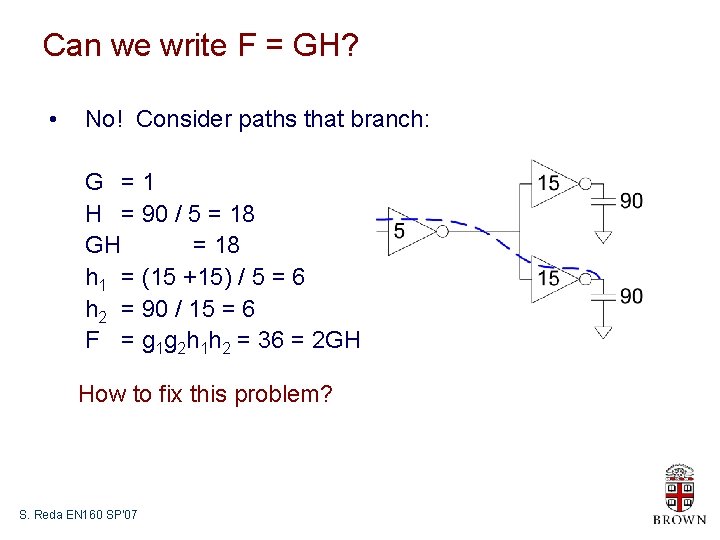

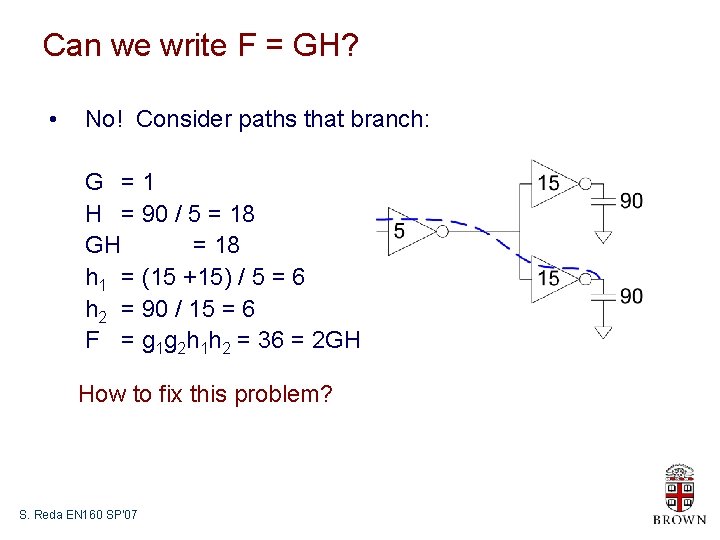

Can we write F = GH? • No! Consider paths that branch: G =1 H = 90 / 5 = 18 GH = 18 h 1 = (15 +15) / 5 = 6 h 2 = 90 / 15 = 6 F = g 1 g 2 h 1 h 2 = 36 = 2 GH How to fix this problem? S. Reda EN 160 SP’ 07

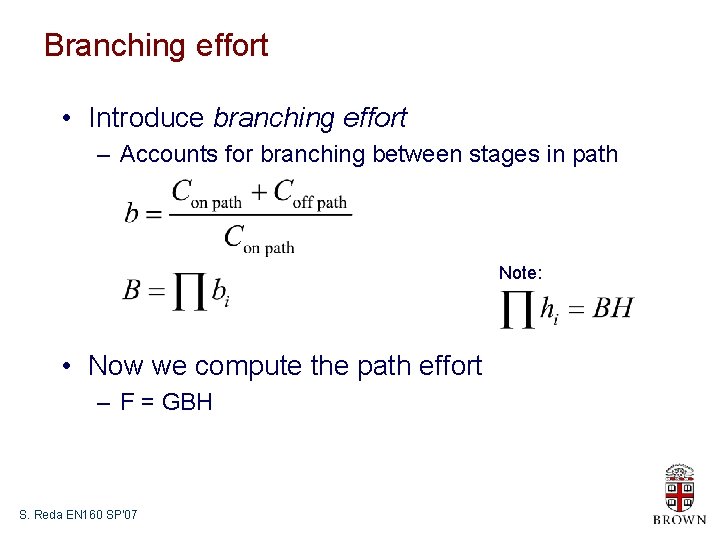

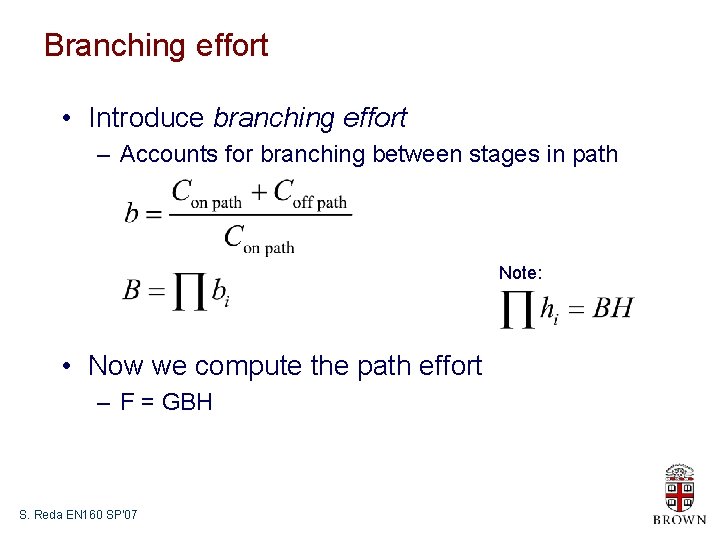

Branching effort • Introduce branching effort – Accounts for branching between stages in path Note: • Now we compute the path effort – F = GBH S. Reda EN 160 SP’ 07

Logical Effort can help us answering two key questions 1. How large should be each stage in a multistage network to achieve the minimium delay? 2. What is the optimal number of stages to achieve the minimum delay S. Reda EN 160 SP’ 07

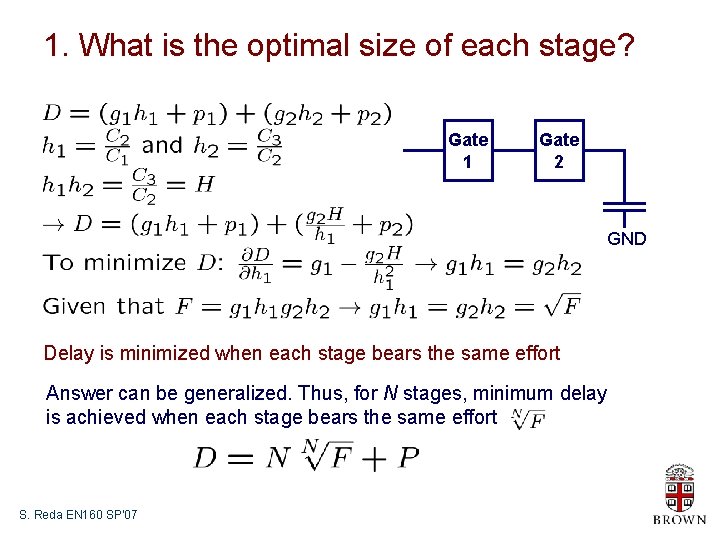

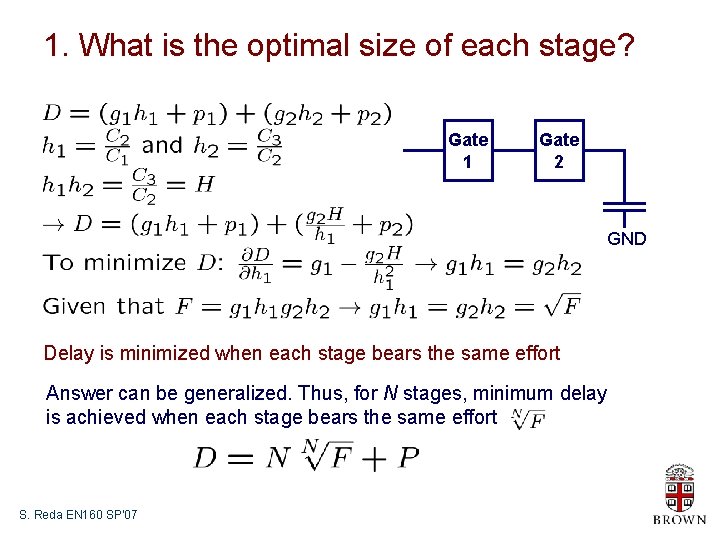

1. What is the optimal size of each stage? Gate 1 Gate 2 GND Delay is minimized when each stage bears the same effort Answer can be generalized. Thus, for N stages, minimum delay is achieved when each stage bears the same effort S. Reda EN 160 SP’ 07

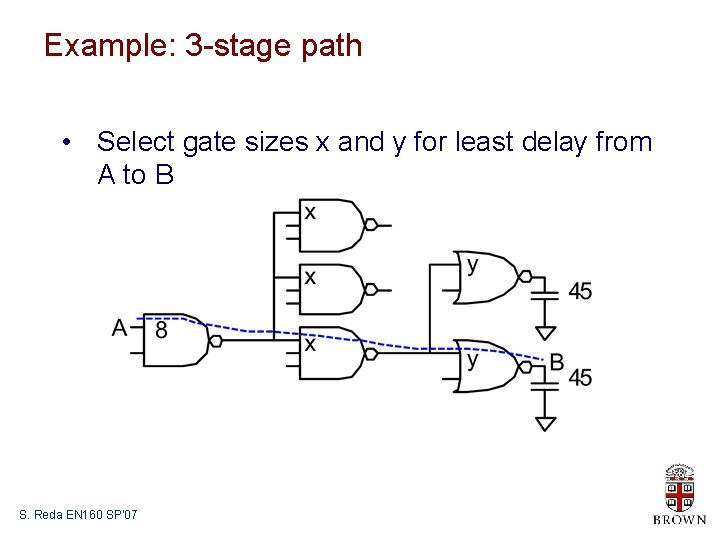

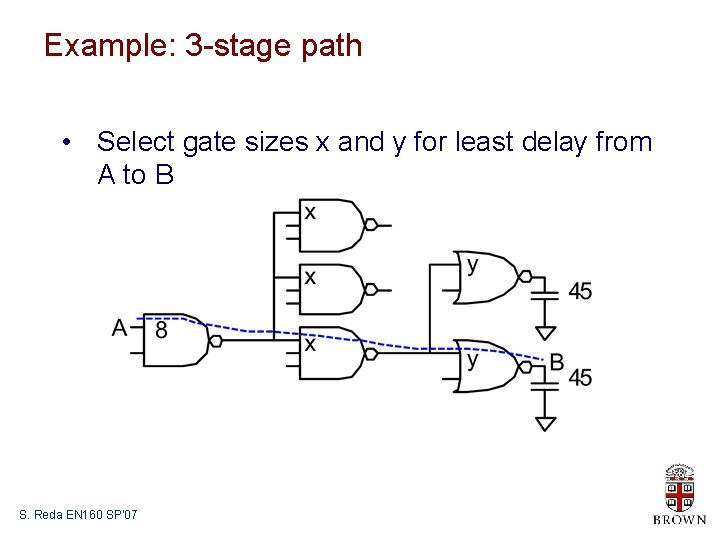

Example: 3 -stage path • Select gate sizes x and y for least delay from A to B S. Reda EN 160 SP’ 07

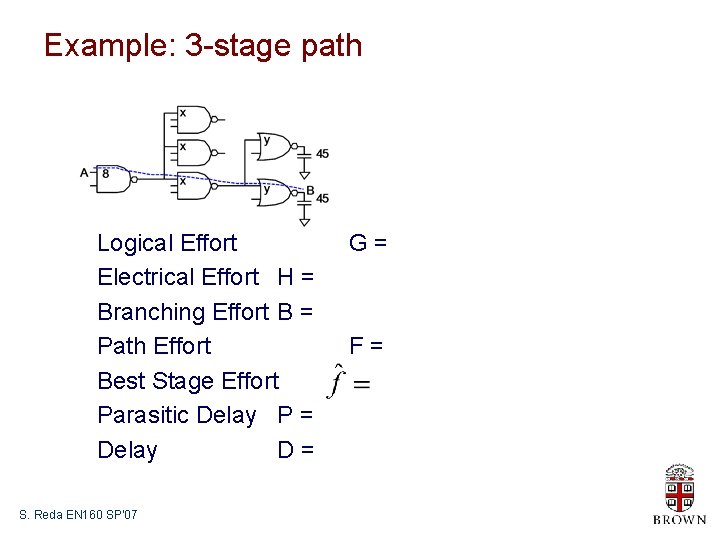

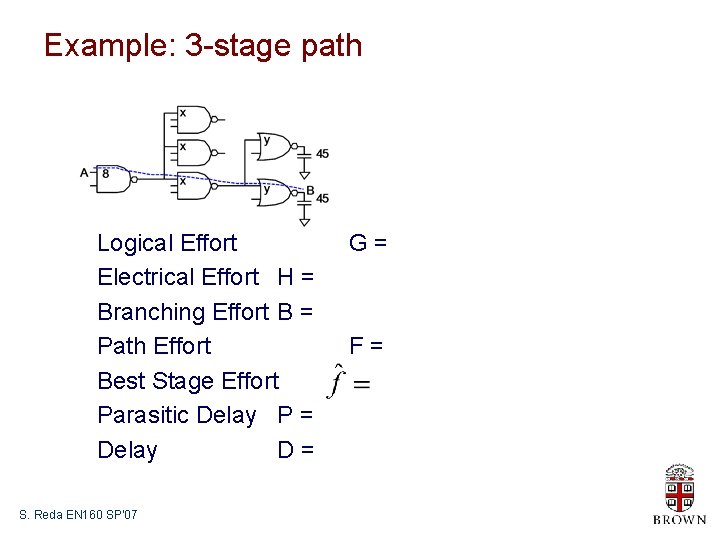

Example: 3 -stage path Logical Effort Electrical Effort H = Branching Effort B = Path Effort Best Stage Effort Parasitic Delay P = Delay D= S. Reda EN 160 SP’ 07 G= F=

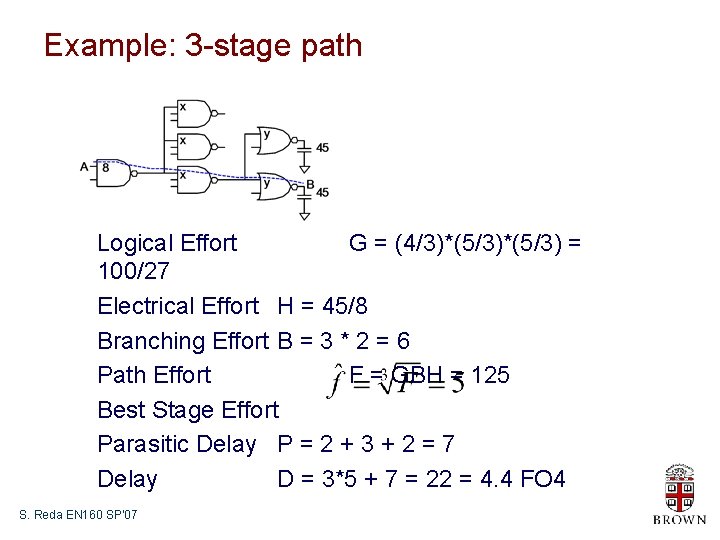

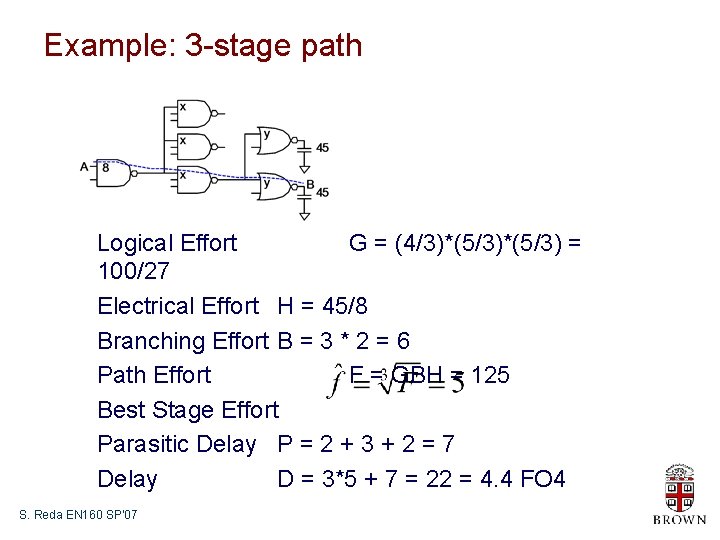

Example: 3 -stage path Logical Effort G = (4/3)*(5/3) = 100/27 Electrical Effort H = 45/8 Branching Effort B = 3 * 2 = 6 Path Effort F = GBH = 125 Best Stage Effort Parasitic Delay P = 2 + 3 + 2 = 7 Delay D = 3*5 + 7 = 22 = 4. 4 FO 4 S. Reda EN 160 SP’ 07

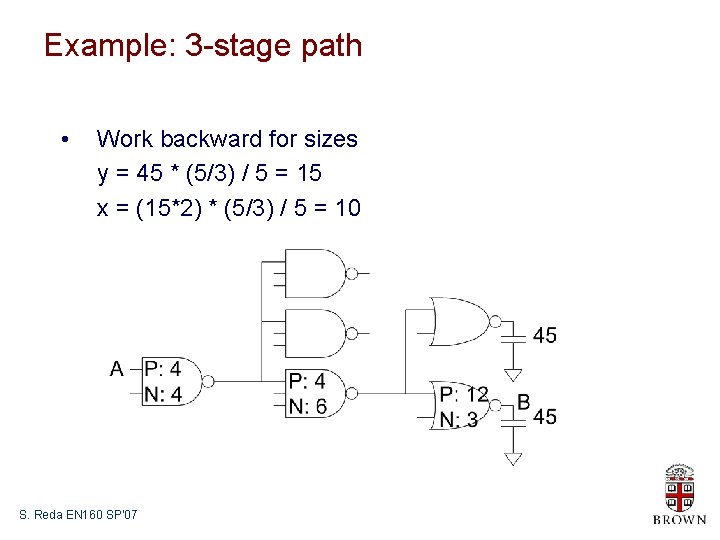

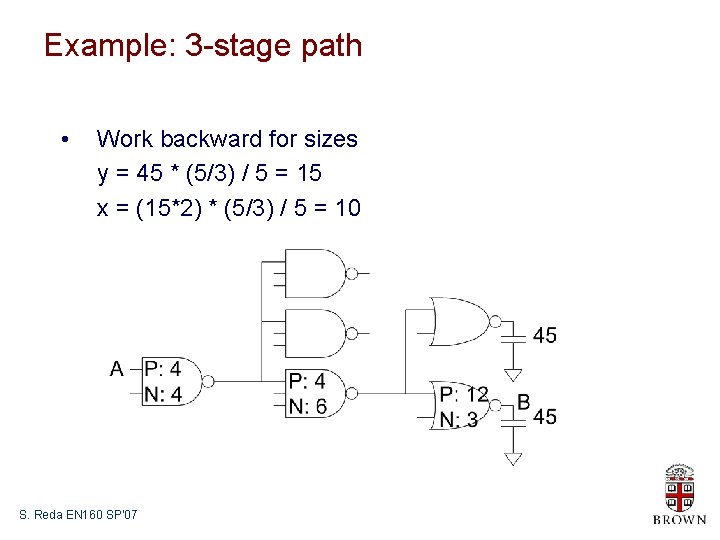

Example: 3 -stage path • Work backward for sizes y = 45 * (5/3) / 5 = 15 x = (15*2) * (5/3) / 5 = 10 S. Reda EN 160 SP’ 07

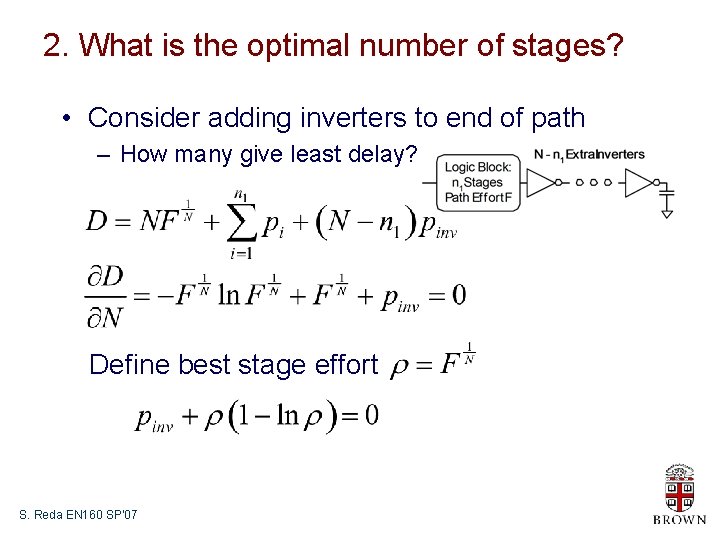

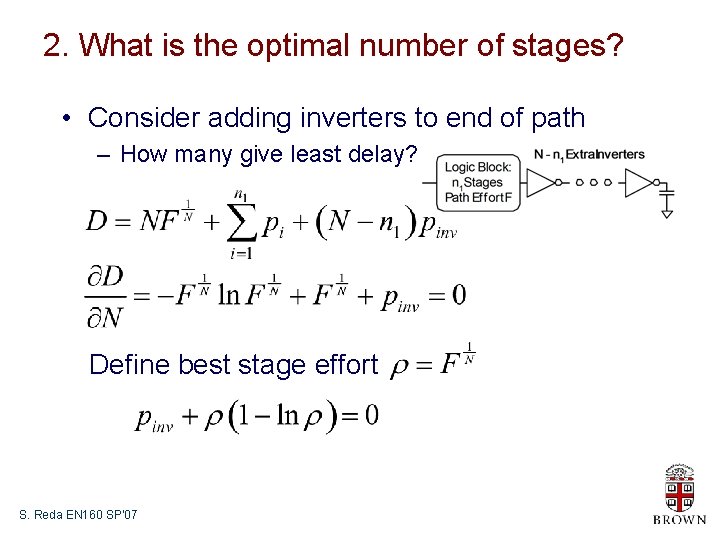

2. What is the optimal number of stages? • Consider adding inverters to end of path – How many give least delay? Define best stage effort S. Reda EN 160 SP’ 07

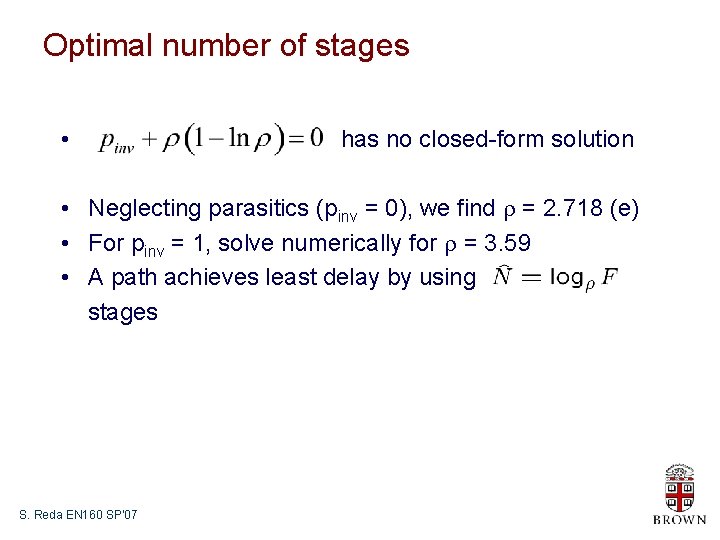

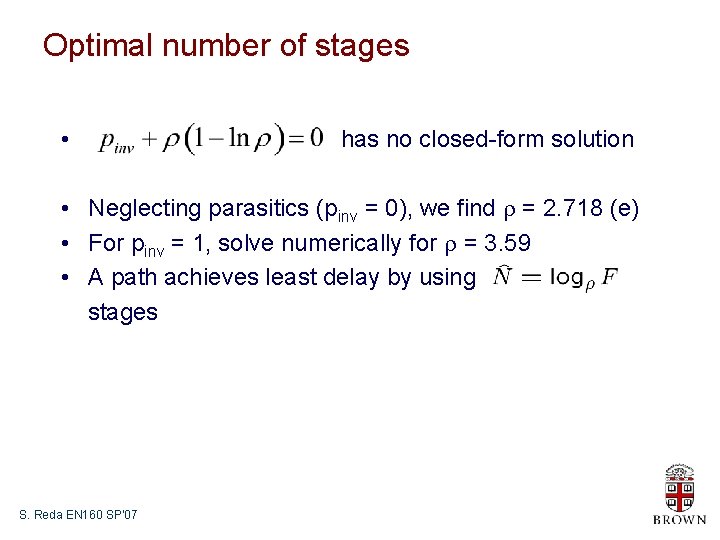

Optimal number of stages • has no closed-form solution • Neglecting parasitics (pinv = 0), we find r = 2. 718 (e) • For pinv = 1, solve numerically for r = 3. 59 • A path achieves least delay by using stages S. Reda EN 160 SP’ 07