Delay Test Quality Evaluation Using Bounded Gate Delays

Delay Test Quality Evaluation Using Bounded Gate Delays Soumitra Bose Intel Corporation, Design Technology, Folsom, CA 95630 Vishwani D. Agrawal Auburn University, Dept. of ECE, Auburn, AL 36849 5/7/2007 VTS'07 1

Problem Statement • Investigate logic simulation with bounded delays specified for process variation. • Improve upon existing min-max delay simulation. 5/7/2007 VTS'07 2

Some Previous Work • J. W. Bierbauer, J. A. Eiseman, F. A. Fazal, and J. J. Kulikowski, “System Simulation with MIDAS, ” AT&T Tech. Jour. , vol. 70, no. 1, pp. 36 -51, January 1991. • A. K. Pramanick and S. M. Reddy, “On the Fault Coverage of Gate Delay Fault Detecting Tests, ” IEEE Trans. CAD, vol. 16, no. 1, pp. 78 -94, January 1997. • S. Chakraborty, D. L. Dill, and K. Y. Yun, “Min-max Timing Analysis and Application to Asynchronous Circuits, ” Proc. IEEE, vol. 87, no. 2, pp. 332 -346, February 1999. 5/7/2007 VTS'07 3

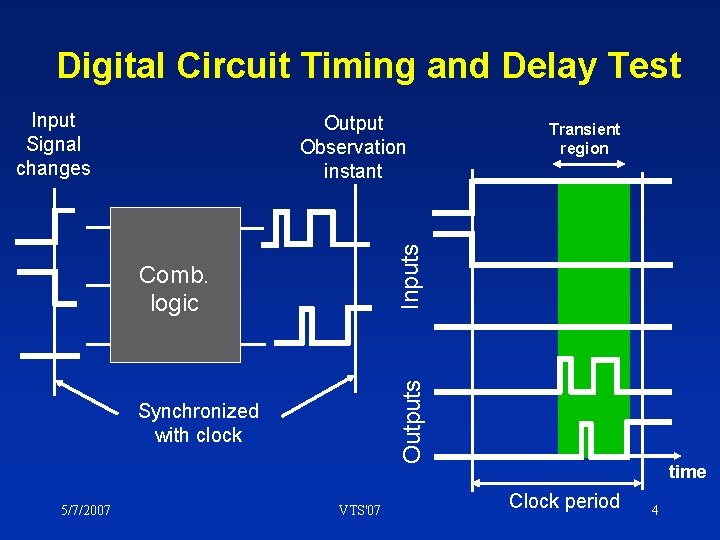

Digital Circuit Timing and Delay Test Input Signal changes Outputs Comb. logic Synchronized with clock 5/7/2007 Transient region Inputs Output Observation instant VTS'07 time Clock period 4

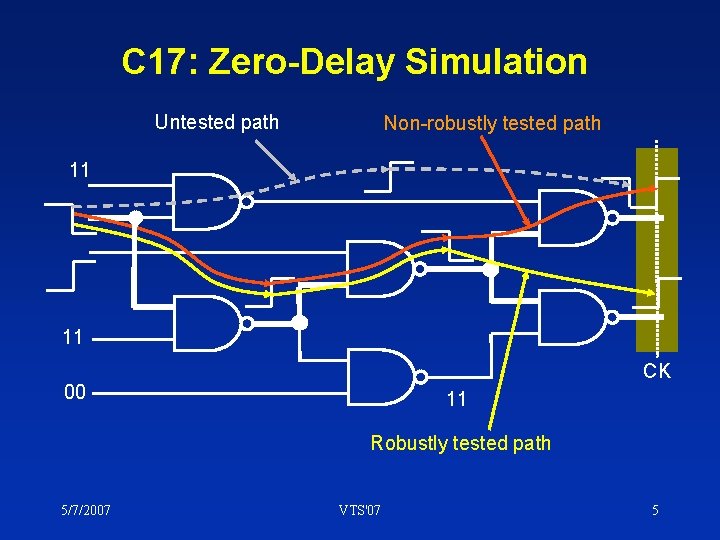

C 17: Zero-Delay Simulation Untested path Non-robustly tested path 11 11 CK 00 11 Robustly tested path 5/7/2007 VTS'07 5

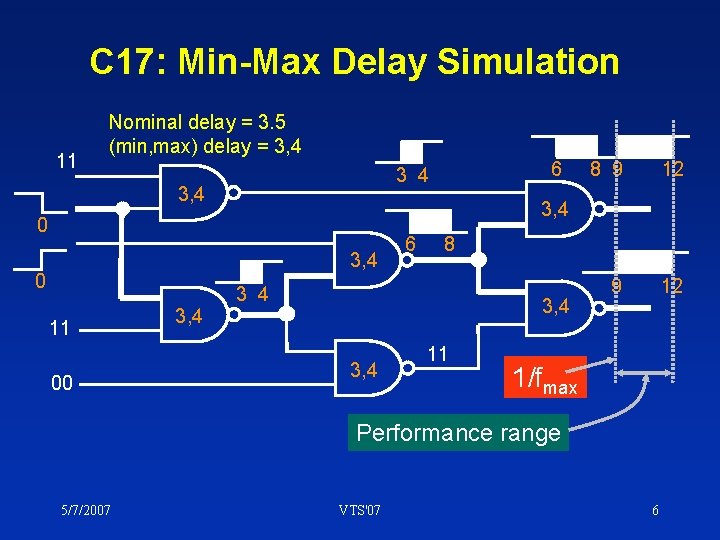

C 17: Min-Max Delay Simulation 11 Nominal delay = 3. 5 (min, max) delay = 3, 4 11 00 3, 4 8 9 12 3, 4 0 0 6 3 4 6 8 3 4 3, 4 11 1/fmax Performance range 5/7/2007 VTS'07 6

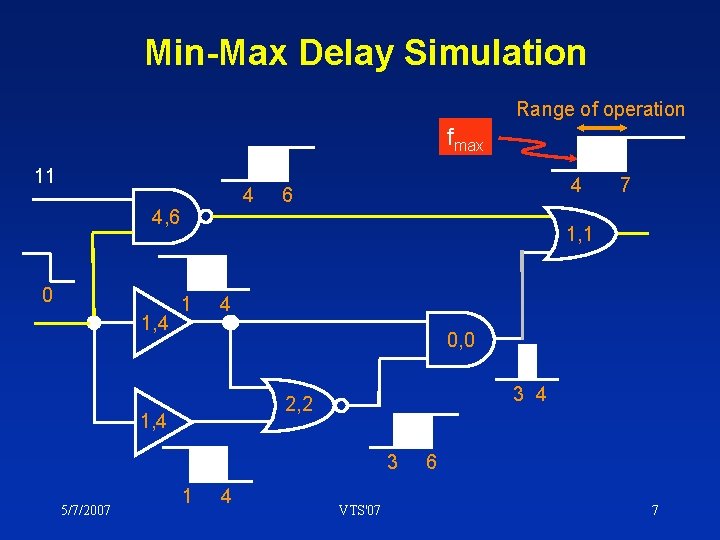

Min-Max Delay Simulation Range of operation fmax 11 4 4, 6 0 1, 4 4 6 1, 1 1 4 0, 0 3 4 2, 2 1, 4 3 5/7/2007 7 1 4 VTS'07 6 7

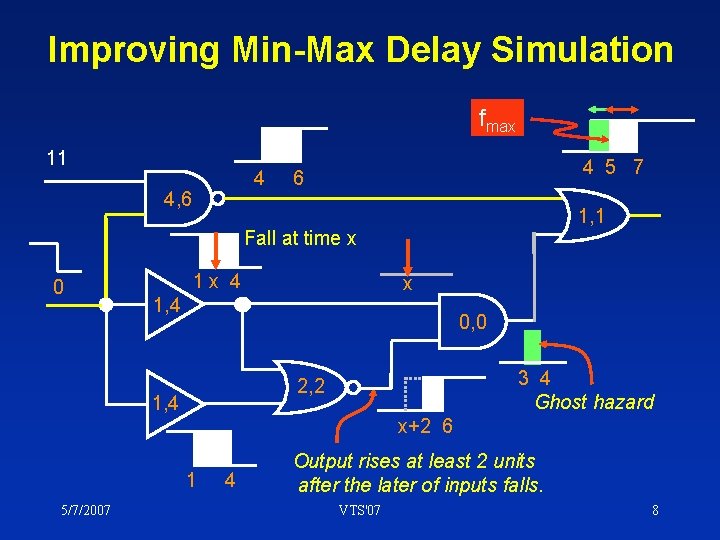

Improving Min-Max Delay Simulation fmax 11 4 4, 6 4 5 7 6 1, 1 Fall at time x 0 1 x 4 x 1, 4 0, 0 3 4 Ghost hazard 2, 2 1, 4 x+2 6 1 5/7/2007 4 Output rises at least 2 units after the later of inputs falls. VTS'07 8

A New Idea in Simulation • Generate ambiguity intervals at fanouts. • Propagate ambiguity interval lists through gates – similar to fault lists in concurrent fault simulation. • Use ambiguity interval correlations among reconverging signals to improve hazard analysis. 5/7/2007 VTS'07 9

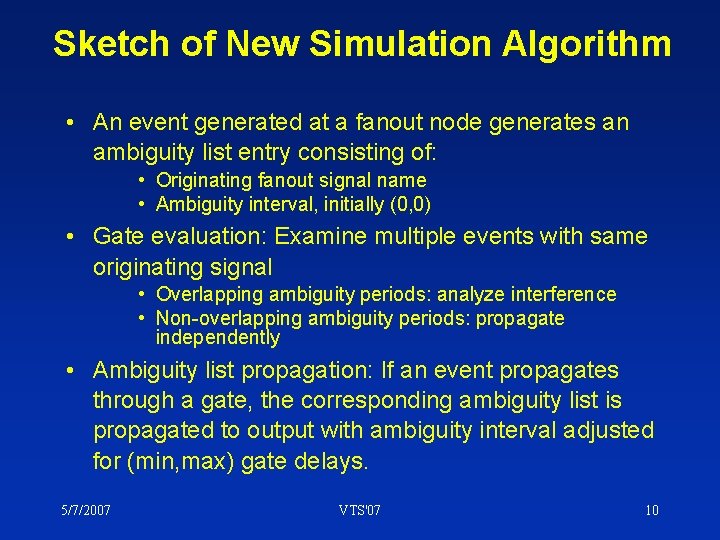

Sketch of New Simulation Algorithm • An event generated at a fanout node generates an ambiguity list entry consisting of: • Originating fanout signal name • Ambiguity interval, initially (0, 0) • Gate evaluation: Examine multiple events with same originating signal • Overlapping ambiguity periods: analyze interference • Non-overlapping ambiguity periods: propagate independently • Ambiguity list propagation: If an event propagates through a gate, the corresponding ambiguity list is propagated to output with ambiguity interval adjusted for (min, max) gate delays. 5/7/2007 VTS'07 10

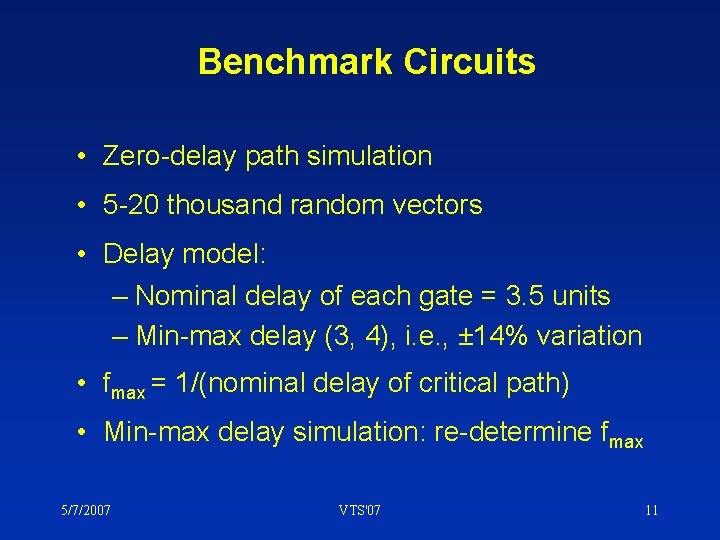

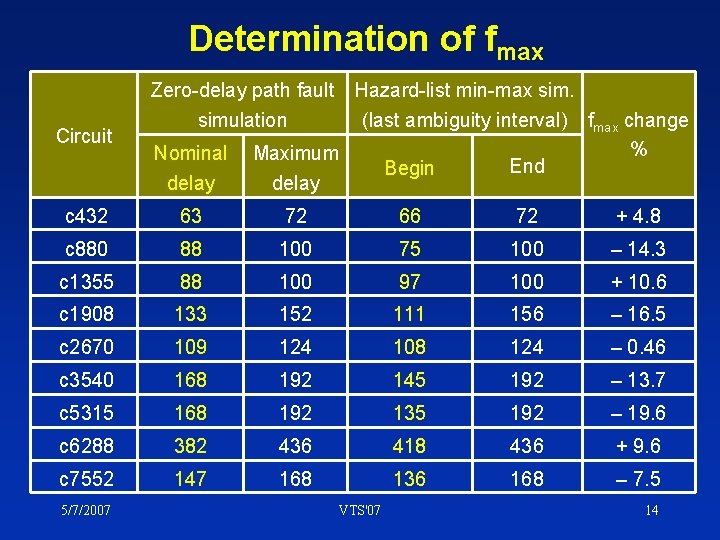

Benchmark Circuits • Zero-delay path simulation • 5 -20 thousand random vectors • Delay model: – Nominal delay of each gate = 3. 5 units – Min-max delay (3, 4), i. e. , ± 14% variation • fmax = 1/(nominal delay of critical path) • Min-max delay simulation: re-determine fmax 5/7/2007 VTS'07 11

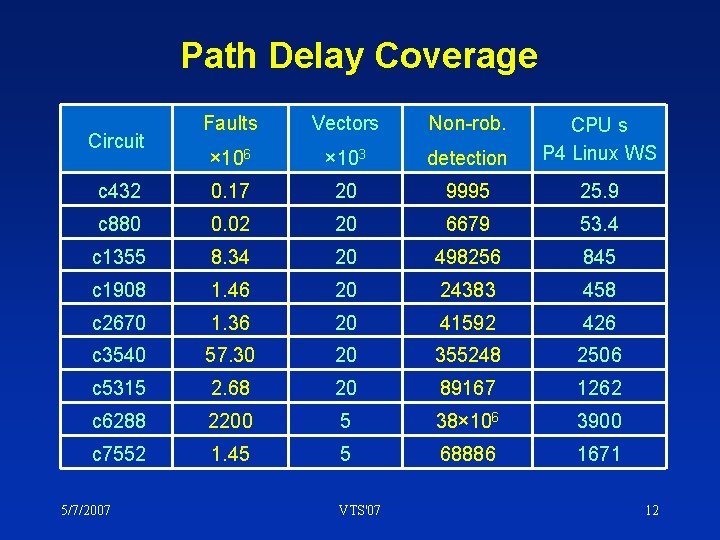

Path Delay Coverage Faults Vectors Non-rob. × 106 × 103 detection CPU s P 4 Linux WS c 432 0. 17 20 9995 25. 9 c 880 0. 02 20 6679 53. 4 c 1355 8. 34 20 498256 845 c 1908 1. 46 20 24383 458 c 2670 1. 36 20 41592 426 c 3540 57. 30 20 355248 2506 c 5315 2. 68 20 89167 1262 c 6288 2200 5 38× 106 3900 c 7552 1. 45 5 68886 1671 Circuit 5/7/2007 VTS'07 12

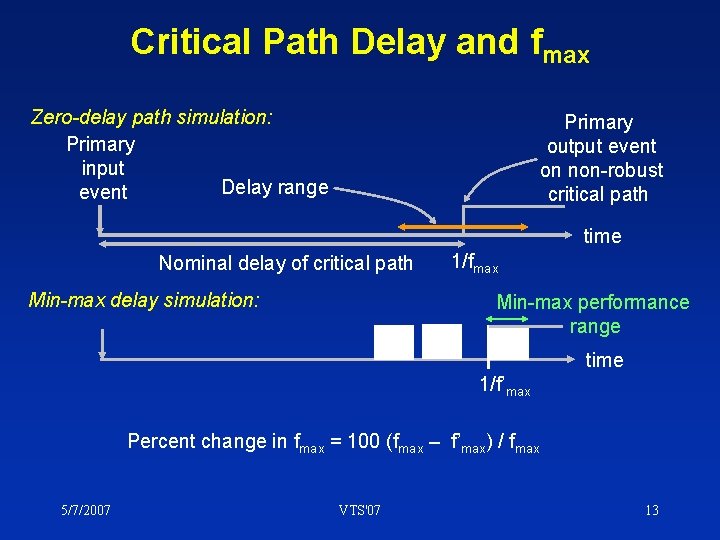

Critical Path Delay and fmax Zero-delay path simulation: Primary input Delay range event Primary output event on non-robust critical path time Nominal delay of critical path Min-max delay simulation: 1/fmax Min-max performance range time 1/f’max Percent change in fmax = 100 (fmax – f’max) / fmax 5/7/2007 VTS'07 13

Determination of fmax Circuit Zero-delay path fault simulation Nominal delay Hazard-list min-max sim. (last ambiguity interval) fmax change % Maximum End Begin delay c 432 63 72 66 72 + 4. 8 c 880 88 100 75 100 – 14. 3 c 1355 88 100 97 100 + 10. 6 c 1908 133 152 111 156 – 16. 5 c 2670 109 124 108 124 – 0. 46 c 3540 168 192 145 192 – 13. 7 c 5315 168 192 135 192 – 19. 6 c 6288 382 436 418 436 + 9. 6 c 7552 147 168 136 168 – 7. 5 5/7/2007 VTS'07 14

Conclusion • Delay independent simulation becomes too pessimistic when we want the result to remain correct in the presence of large process variations. • Conventional min-max delay (bounded delay) simulation produces extra ambiguity periods (hazards) because correlations between signals are neglected. • Pessimism (ambiguity, hazards) is reduced when correlation among reconverging signals is considered. • This paper presents an improved min-max delay (bounded delay) simulation algorithm. 5/7/2007 VTS'07 15

- Slides: 15