CSL 718 Main Memory 6 th Mar 2006

- Slides: 26

CSL 718 : Main Memory 6 th Mar, 2006 Anshul Kumar, CSE IITD

Requirements • CPU – Main Memory : word transfers • Cache – Main Memory : block/line transfers (words also in WT) • I/O – Main Memory : large block transfers • Use of write buffers • Out of order execution How to speed-up transfer? Anshul Kumar, CSE IITD 2

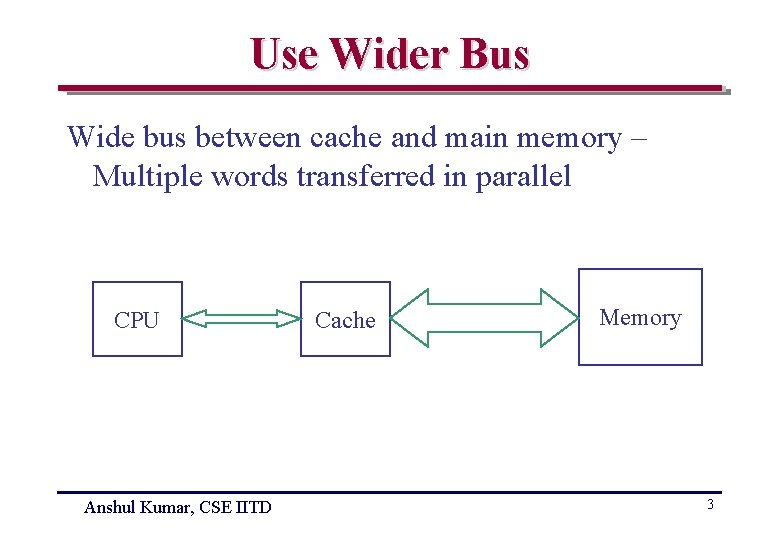

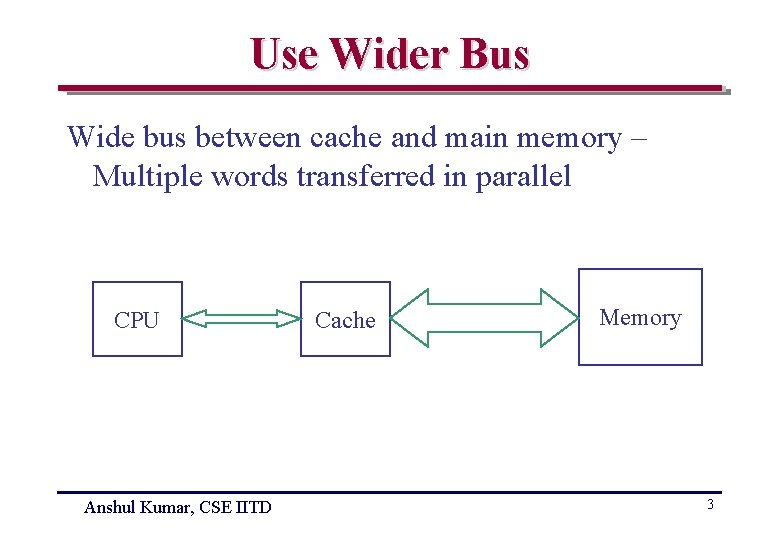

Use Wider Bus Wide bus between cache and main memory – Multiple words transferred in parallel CPU Anshul Kumar, CSE IITD Cache Memory 3

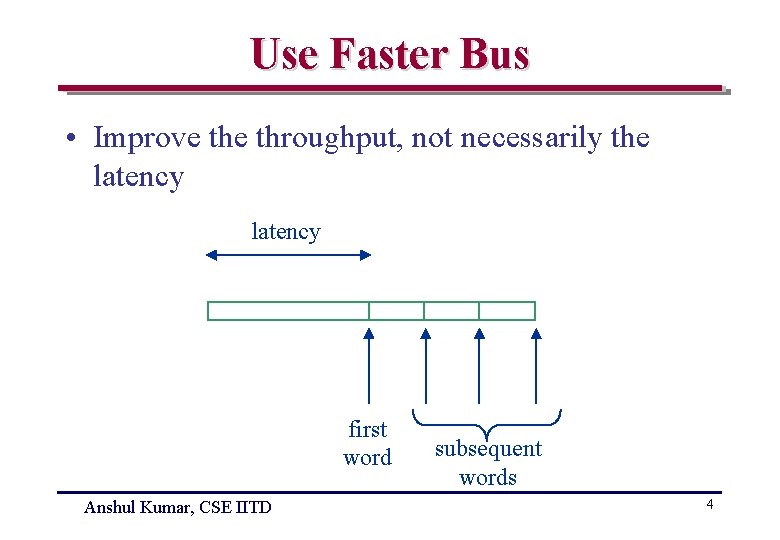

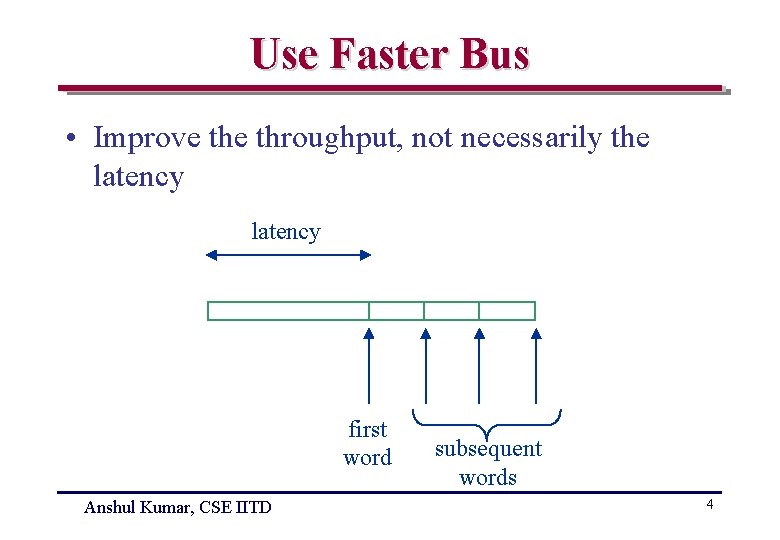

Use Faster Bus • Improve throughput, not necessarily the latency first word Anshul Kumar, CSE IITD subsequent words 4

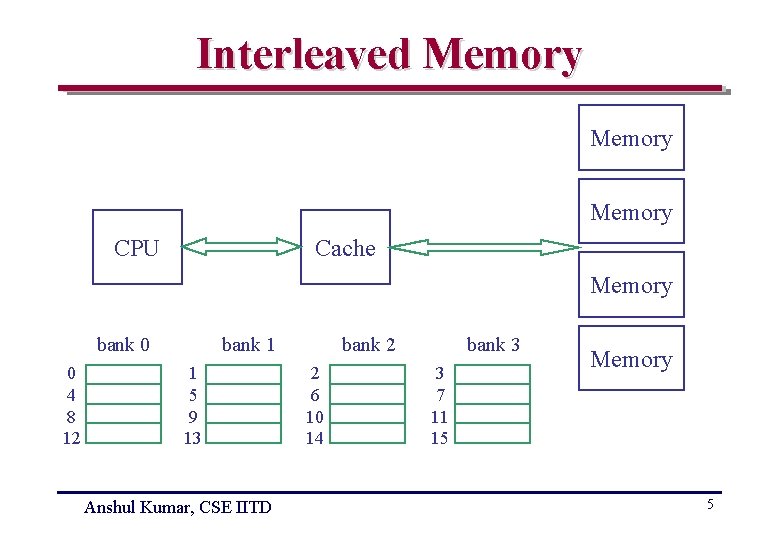

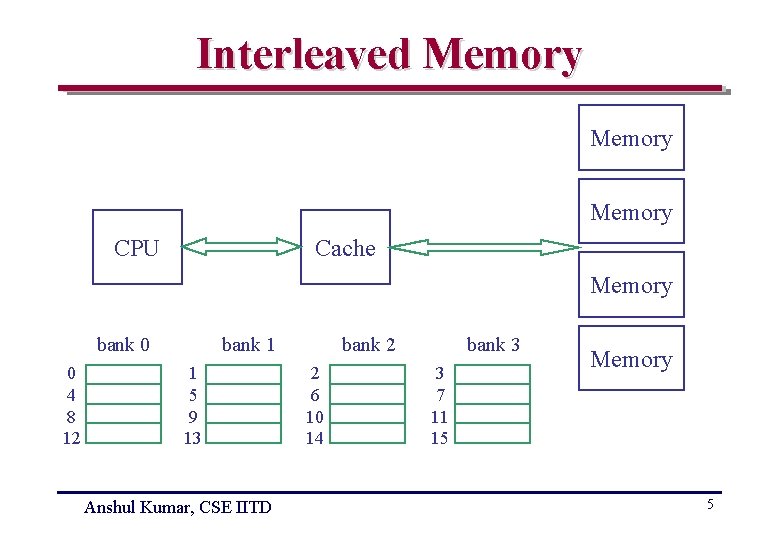

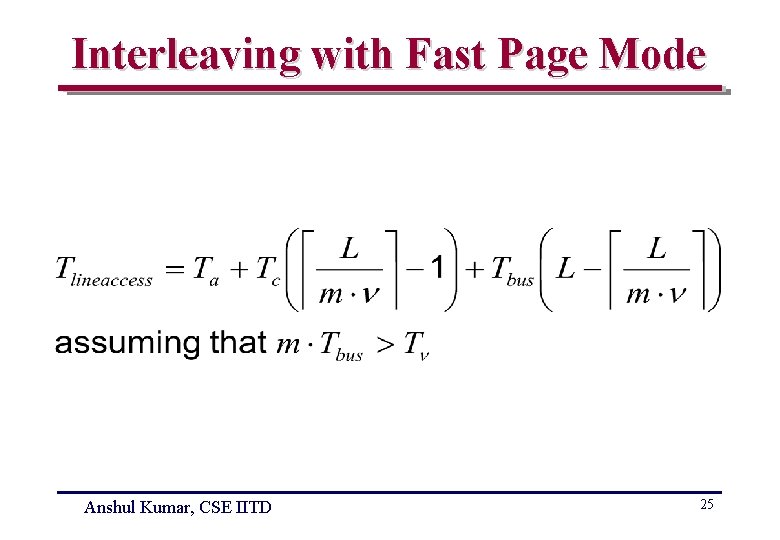

Interleaved Memory CPU Cache Memory bank 0 0 4 8 12 bank 1 1 5 9 13 Anshul Kumar, CSE IITD bank 2 2 6 10 14 bank 3 3 7 11 15 Memory 5

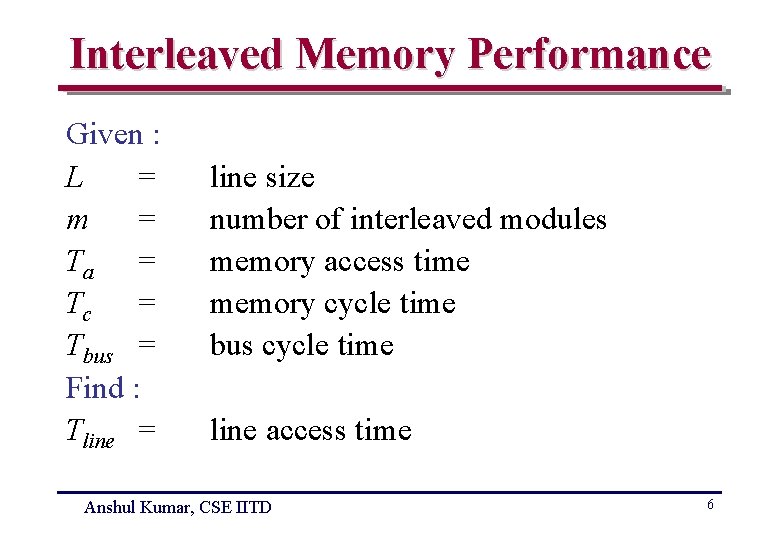

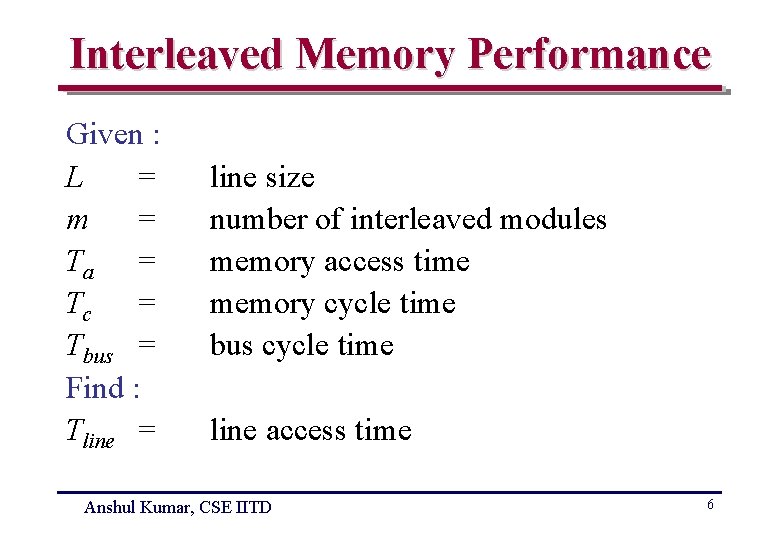

Interleaved Memory Performance Given : L = m = Ta = Tc = Tbus = Find : Tline = line size number of interleaved modules memory access time memory cycle time bus cycle time line access time Anshul Kumar, CSE IITD 6

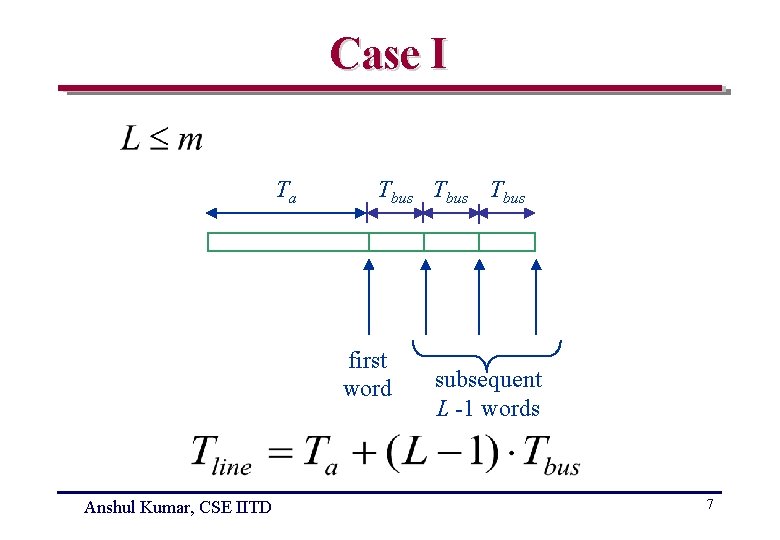

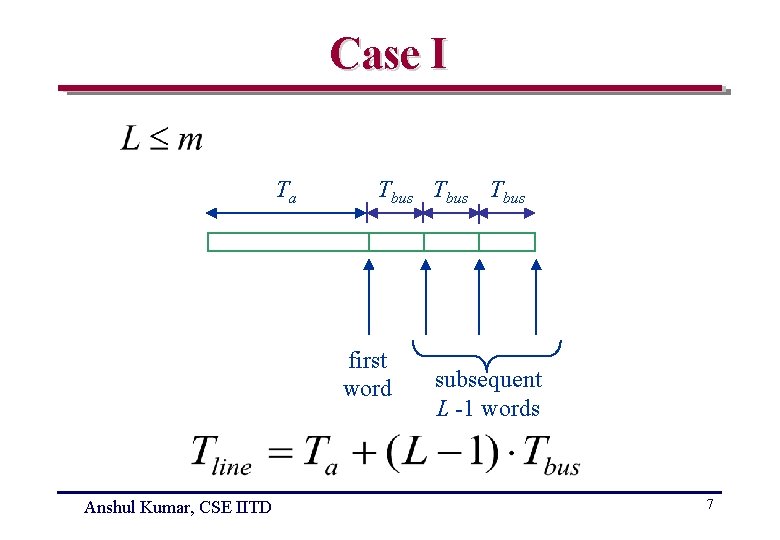

Case I Ta Tbus first word Anshul Kumar, CSE IITD subsequent L -1 words 7

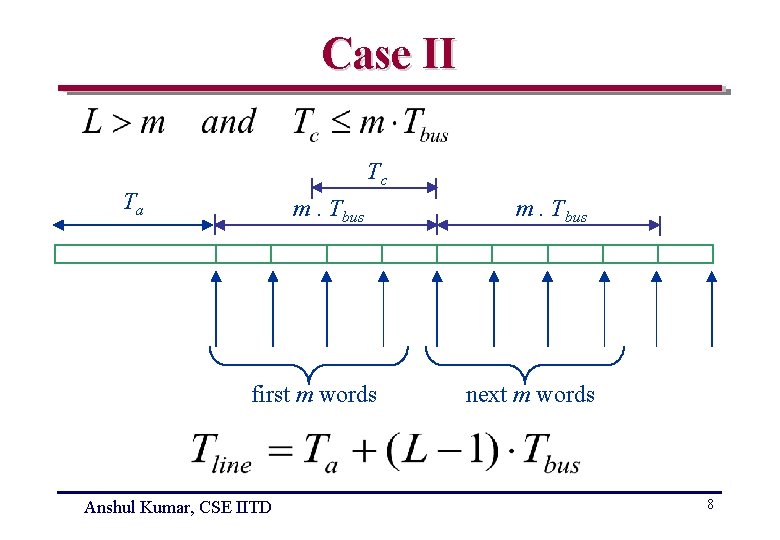

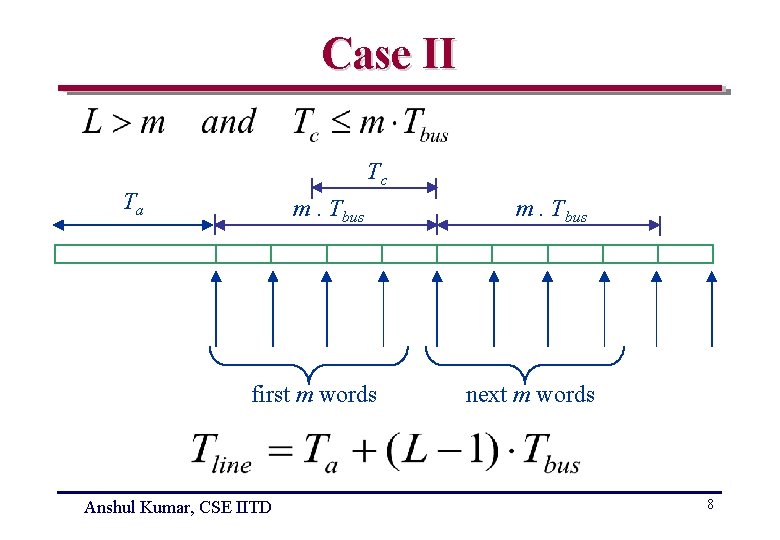

Case II Tc Ta m. Tbus first m words Anshul Kumar, CSE IITD m. Tbus next m words 8

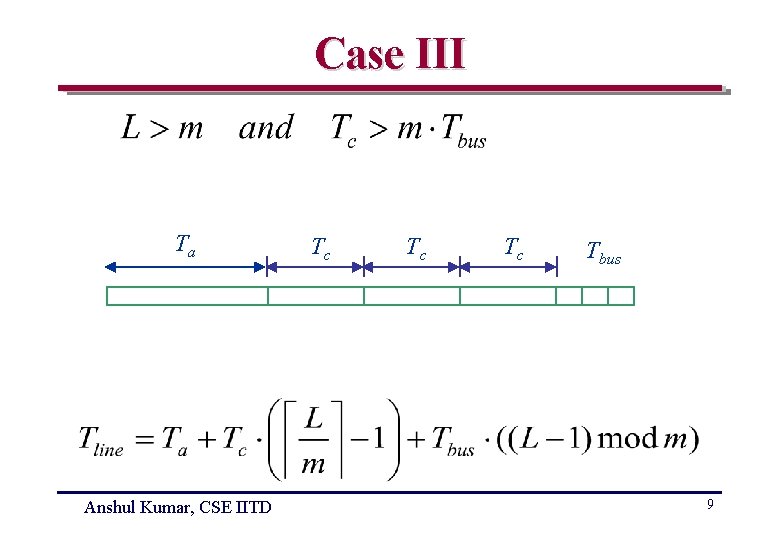

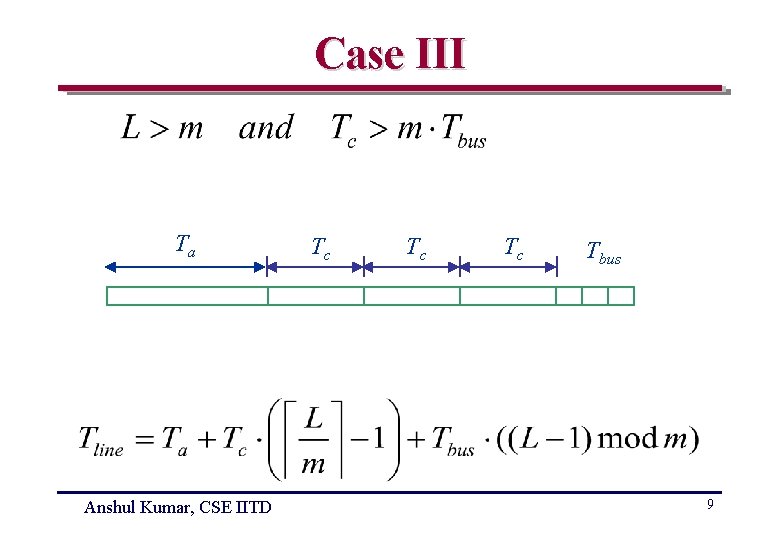

Case III Ta Anshul Kumar, CSE IITD Tc Tc Tc Tbus 9

Semiconductor Memory Technology • Fast memory for cache - Static RAM (SRAM) • High density main memory - Dynamic RAM (DRAM) • Non volatile memories for embedded systems ROM, PROM, EPROM, Flash Anshul Kumar, CSE IITD 10

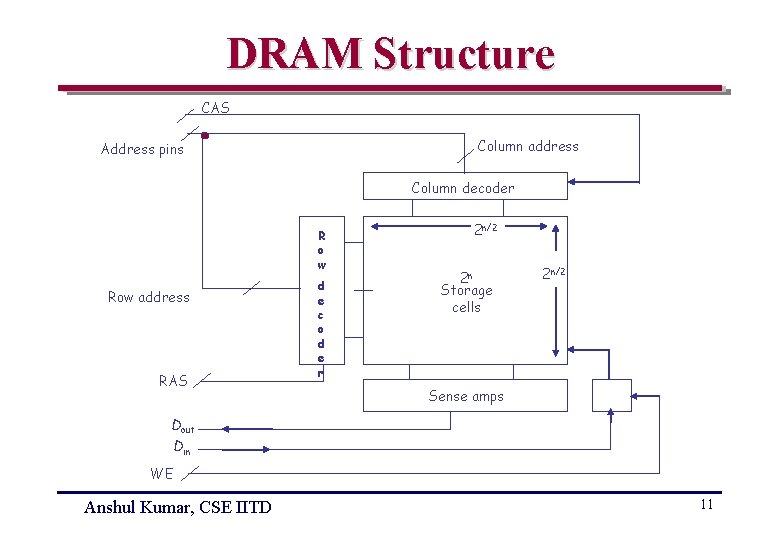

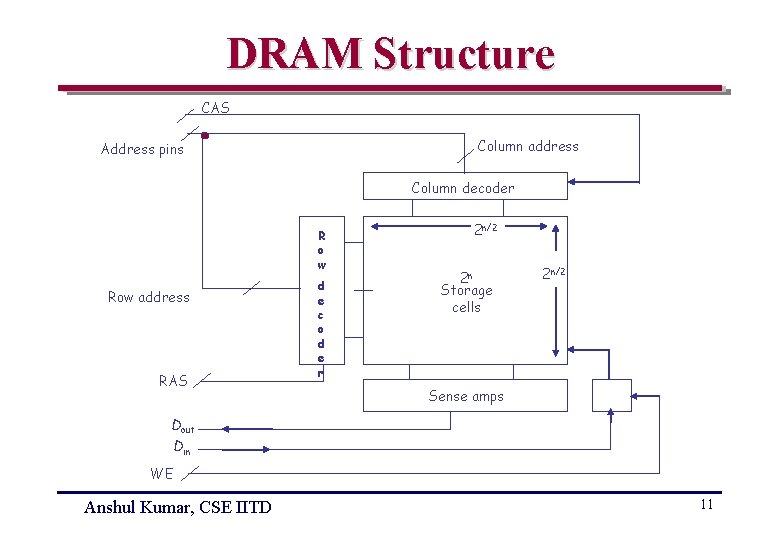

DRAM Structure CAS Column address Address pins Column decoder R o w Row address RAS d e c o d e r 2 n/2 2 n Storage cells 2 n/2 Sense amps Dout Din WE Anshul Kumar, CSE IITD 11

Enhancing DRAM Performance • Multiple arrays of cells • Access multiple bits in a row (sequentially | randomly) • Synchronous interface rather than asynchronous interface • Transfer data on both edges of clock Anshul Kumar, CSE IITD 12

DRAM Technologies Fast Page Mode (FPM) DRAM Extended Data Out (EDO) DRAM Burst Extended Data Out (BEDO) DRAM Synchronous DRAM (SDRAM) Synchronous-Link DRAM (SLDRAM) Double Data Rate SDRAM (DDR SDRAM) Direct Rambus DRAM (DRDRAM) Video RAM (VRAM) – dual ported Anshul Kumar, CSE IITD 13

Memory Modules in PCs • SIMM (single in-line memory module): Have 72 or 30 pins. Support 32 -bit and 16 -bit data transfers. • DIMM (dual in-line memory module): Have 168 pins. Support 64 -bit data transfers. Anshul Kumar, CSE IITD 14

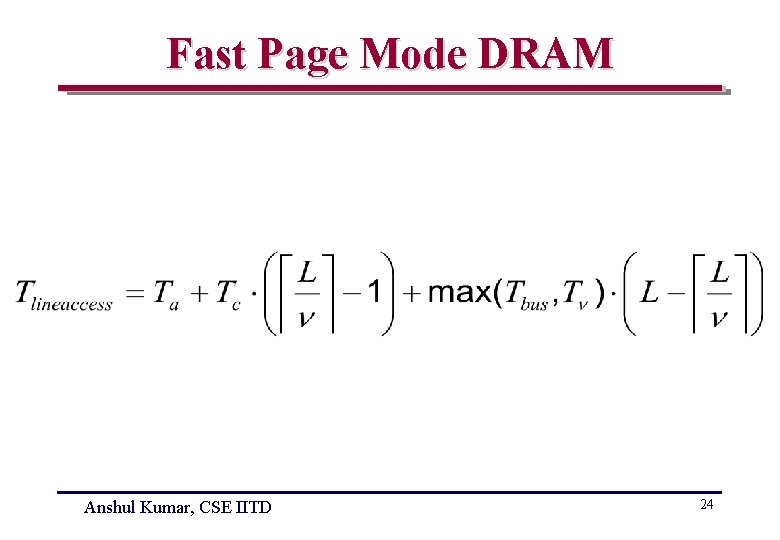

Fast Page Mode (FPM) DRAM • Row address selects a page (row) • Bits in a page selected by column addresses Anshul Kumar, CSE IITD 15

Extended Data Out (EDO) DRAM • extends the time for which output data is valid, easing timing issues between the CPU and RAM and enhancing performance Anshul Kumar, CSE IITD 16

Burst EDO (BEDO) DRAM • A variant on EDO DRAM • Read or write cycles are batched in bursts of four • Two LSBs of the column address get modified internally to produce each address of the burst sequence Anshul Kumar, CSE IITD 17

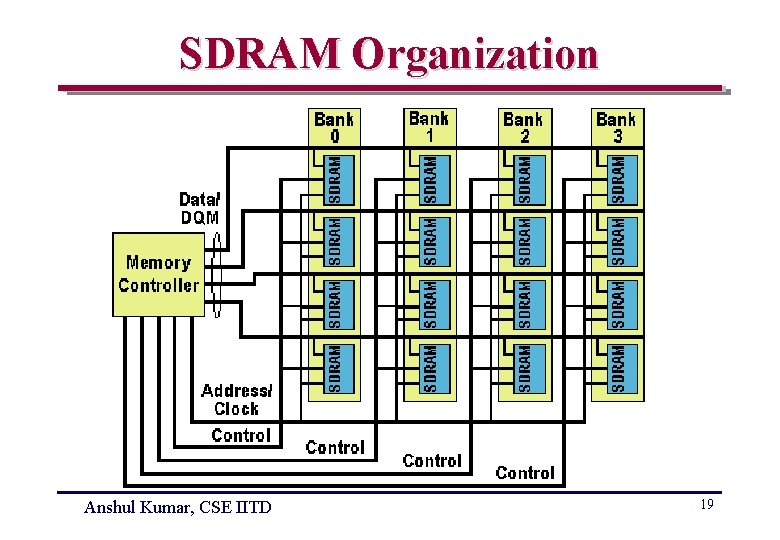

SDRAM • Synchronizes itself with the CPU's bus • One block of data can be sent to the CPU while another is being prepared for access • About three times faster than conventional FPM RAM and about twice as fast EDO DRAM and BEDO DRAM • Standards : PC 66, PC 100, PC 133, PC 150 (PC 150 means 150 MHz, peak bandwidth upto 1. 2 GB/s) • DDRSDRAM : PC 1600, PC 2100, PC 2700, PC 3200 – figure refers to MB/s Anshul Kumar, CSE IITD 18

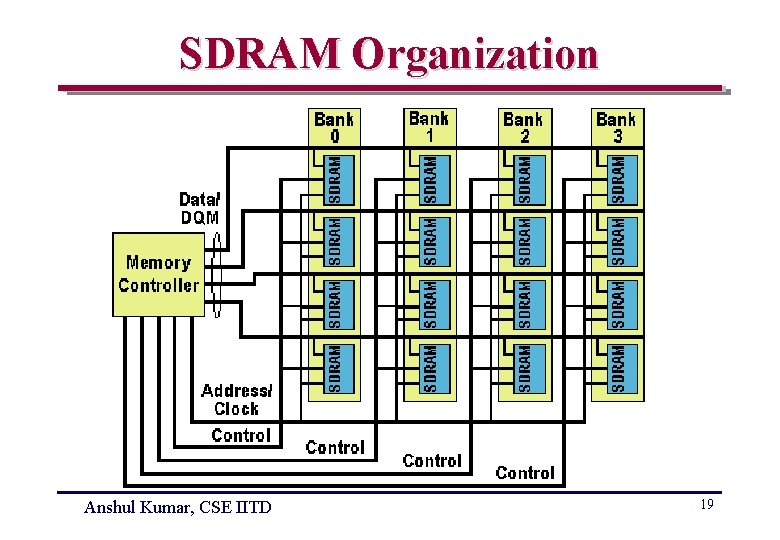

SDRAM Organization Anshul Kumar, CSE IITD 19

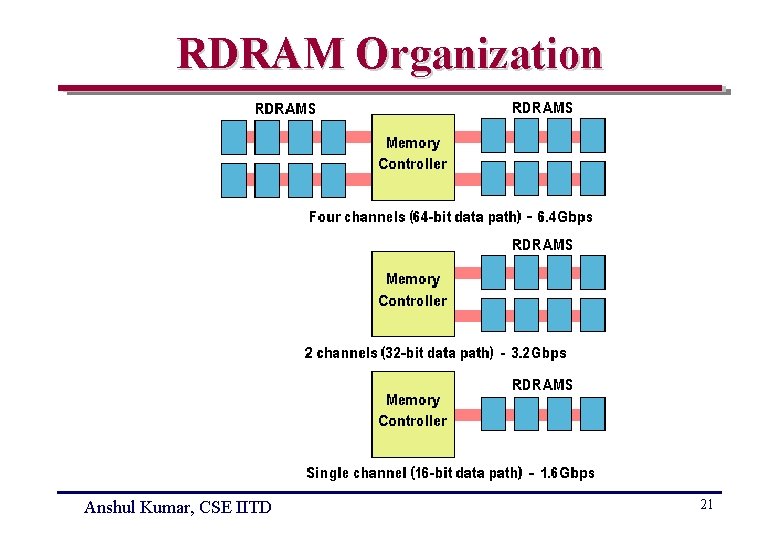

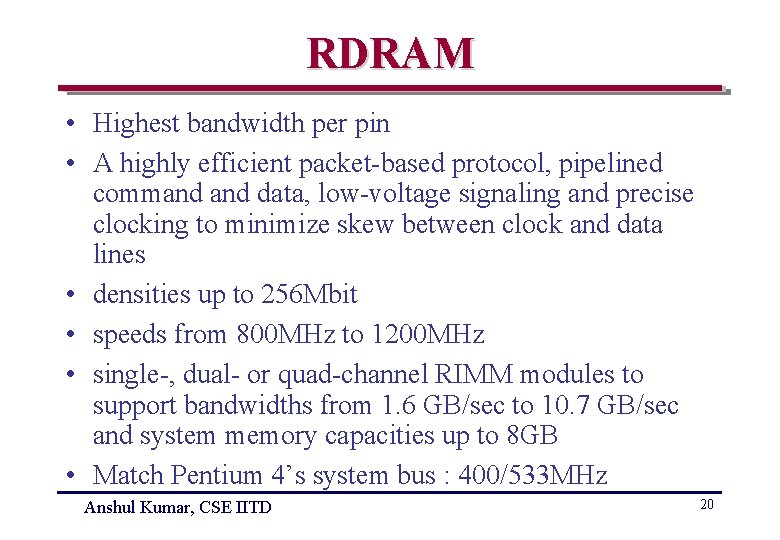

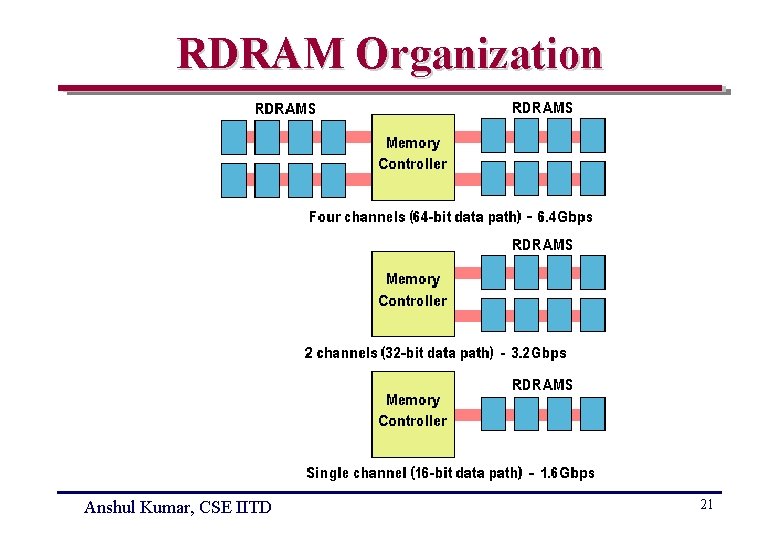

RDRAM • Highest bandwidth per pin • A highly efficient packet-based protocol, pipelined command data, low-voltage signaling and precise clocking to minimize skew between clock and data lines • densities up to 256 Mbit • speeds from 800 MHz to 1200 MHz • single-, dual- or quad-channel RIMM modules to support bandwidths from 1. 6 GB/sec to 10. 7 GB/sec and system memory capacities up to 8 GB • Match Pentium 4’s system bus : 400/533 MHz Anshul Kumar, CSE IITD 20

RDRAM Organization Anshul Kumar, CSE IITD 21

RIMM Anshul Kumar, CSE IITD 22

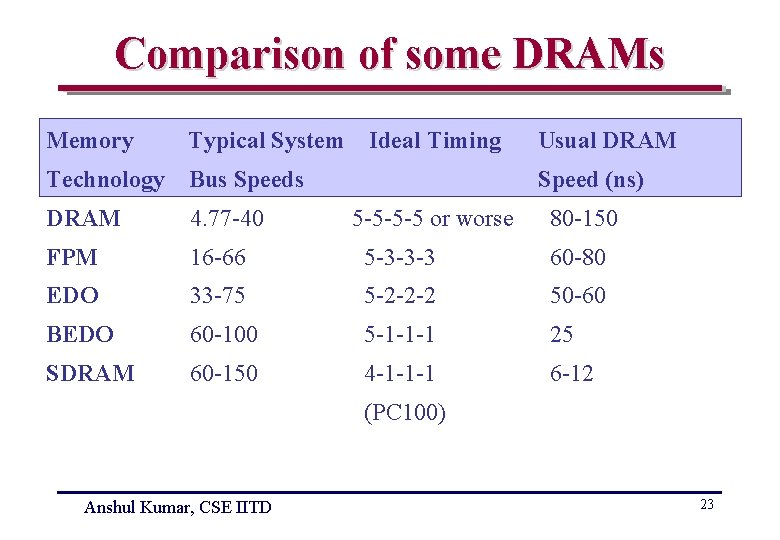

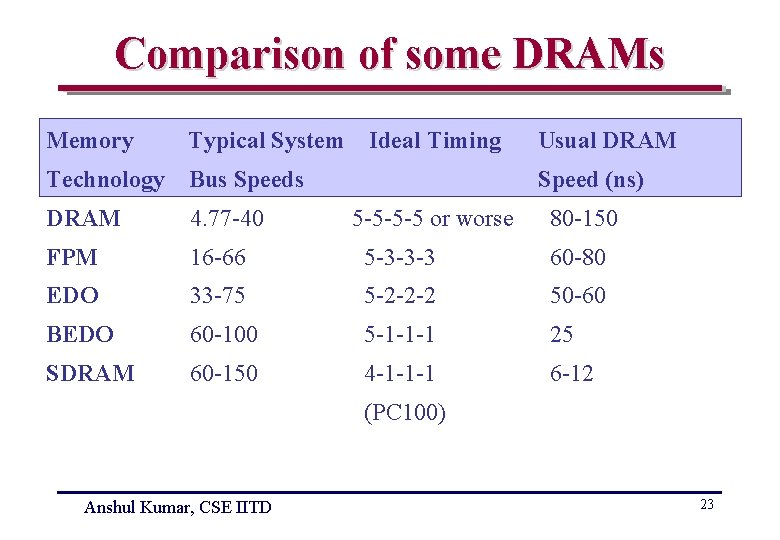

Comparison of some DRAMs Memory Typical System Ideal Timing Usual DRAM Technology Bus Speeds DRAM 4. 77 -40 FPM 16 -66 5 -3 -3 -3 60 -80 EDO 33 -75 5 -2 -2 -2 50 -60 BEDO 60 -100 5 -1 -1 -1 25 SDRAM 60 -150 4 -1 -1 -1 6 -12 Speed (ns) 5 -5 -5 -5 or worse 80 -150 (PC 100) Anshul Kumar, CSE IITD 23

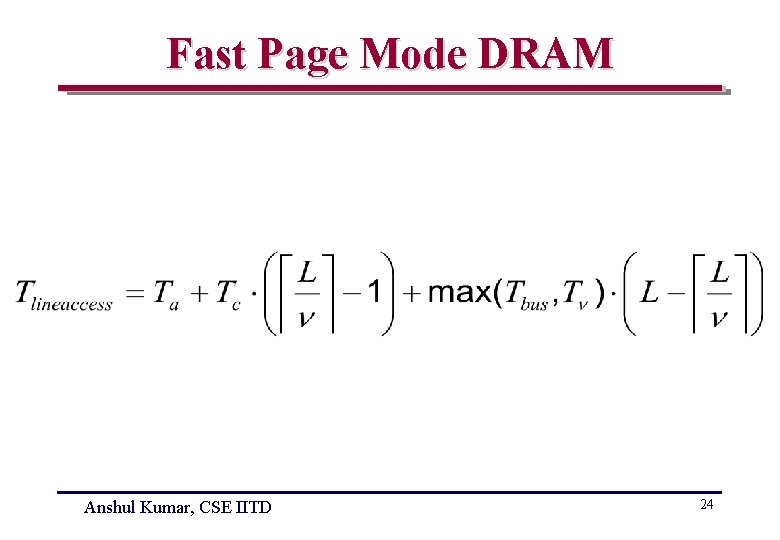

Fast Page Mode DRAM Anshul Kumar, CSE IITD 24

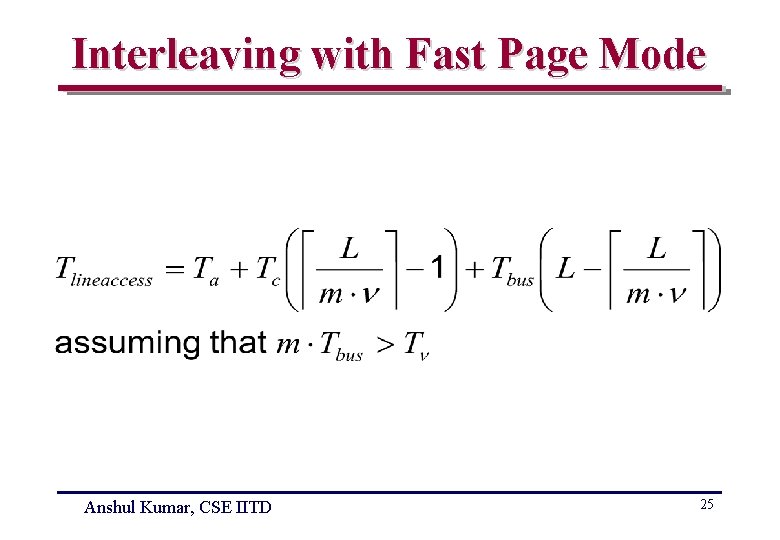

Interleaving with Fast Page Mode Anshul Kumar, CSE IITD 25

References http: //home. cfl. rr. com/eaa/Memory. Types. htm http: //home. cfl. rr. com/bjp/Computer. Memory. htm http: //www. pctechguide. com/03 memory. htm Flynn’s Book Hennessy & Patterson’s Book Anshul Kumar, CSE IITD 26