CSL 718 Superscalar Processors Speculative Execution 2 nd

![Execute • Wait until RS[r]. Qj = 0 and RS[r]. Qk = 0 • Execute • Wait until RS[r]. Qj = 0 and RS[r]. Qk = 0 •](https://slidetodoc.com/presentation_image_h/0fed0c70ac2a0be8d47e506c78387dcb/image-14.jpg)

![Execute (no change) • Wait until RS[r]. Qj = 0 and RS[r]. Qk = Execute (no change) • Wait until RS[r]. Qj = 0 and RS[r]. Qk =](https://slidetodoc.com/presentation_image_h/0fed0c70ac2a0be8d47e506c78387dcb/image-27.jpg)

- Slides: 30

CSL 718 : Superscalar Processors Speculative Execution 2 nd Feb, 2006 Anshul Kumar, CSE IITD

Handling Control Dependence • Simple pipeline – Branch prediction reduces stalls due to control dependence • Wide issue processor – Mere branch prediction is not sufficient – Instructions in the predicted path need to be fetched and EXECUTED (speculated execution) Anshul Kumar, CSE IITD 2

What is required for speculation? • Branch prediction to choose which instructions to execute • Execution of instructions before control dependences are resolved • Ability to undo the effects of incorrectly speculated sequence • Preserving of correct behaviour under exceptions Anshul Kumar, CSE IITD 3

Types of speculation • Hardware based speculation – done with dynamic branch prediction and dynamic scheduling – used in Superscalar processors • Compiler based speculation – done with static branch prediction and static scheduling – used in VLIW processors Anshul Kumar, CSE IITD 4

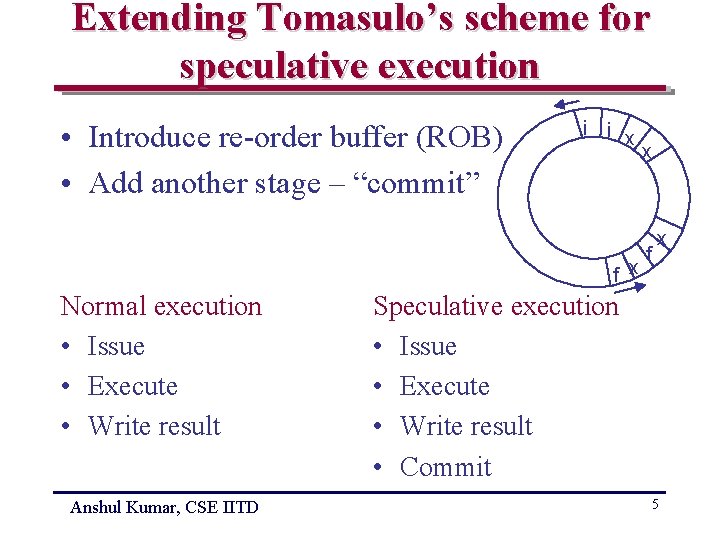

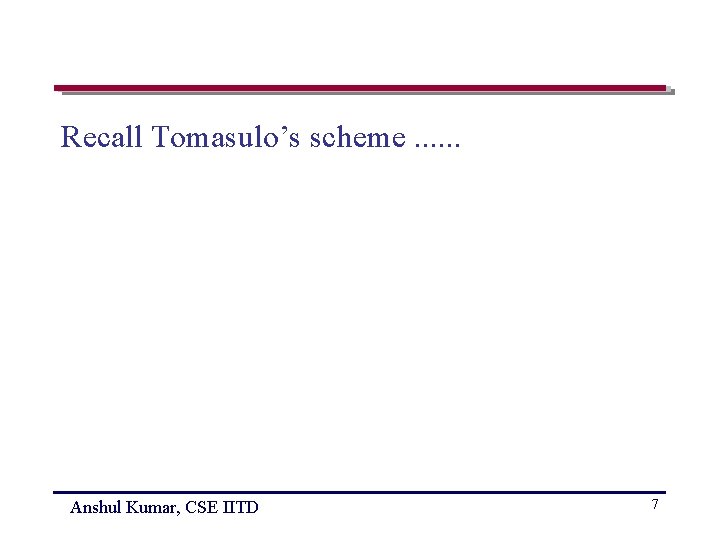

Extending Tomasulo’s scheme for speculative execution • Introduce re-order buffer (ROB) • Add another stage – “commit” i i x f x Normal execution • Issue • Execute • Write result Anshul Kumar, CSE IITD x f x Speculative execution • Issue • Execute • Write result • Commit 5

Extending Tomasulo’s scheme for speculative execution – contd. • Write results into ROB in the “write result” stage • Write results into register file or memory in the “commit” stage • Dependent instructions can read operands from ROB • A speculative instruction commits only if the prediction is determined to be correct • Instructions may complete execution out-of-order, but they commit in-order Anshul Kumar, CSE IITD 6

Recall Tomasulo’s scheme. . . Anshul Kumar, CSE IITD 7

Issue • Get next instruction from instruction queue • Check if there is a matching RS which is empty – no: structural hazard, instruction stalls – yes: issue the instruction to that RS • For each operand, check if it is available in RF – yes: put the operand in the RS – no: keep track of FU that will produce it Anshul Kumar, CSE IITD 8

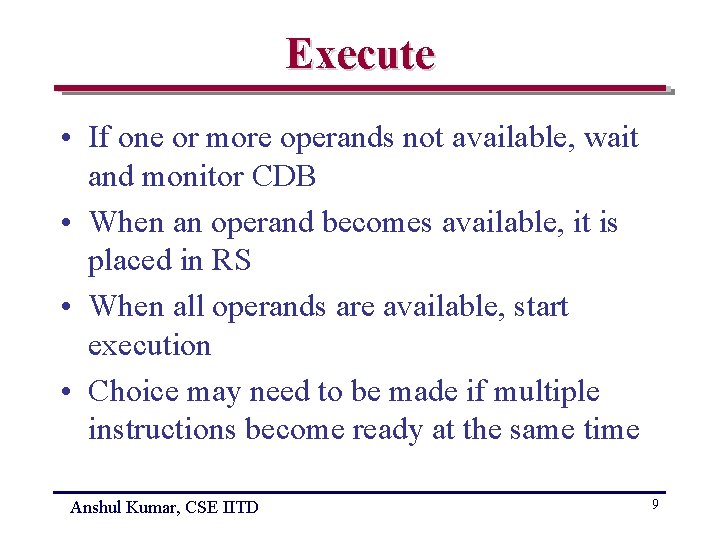

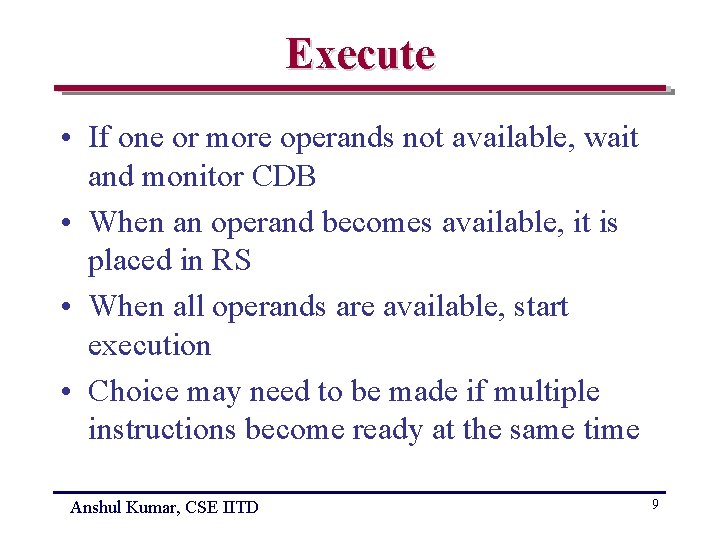

Execute • If one or more operands not available, wait and monitor CDB • When an operand becomes available, it is placed in RS • When all operands are available, start execution • Choice may need to be made if multiple instructions become ready at the same time Anshul Kumar, CSE IITD 9

Write result • When result is available – write it on CDB and – from there into RF and relevant RSs • Mark RS as available Anshul Kumar, CSE IITD 10

More formal description. . . Anshul Kumar, CSE IITD 11

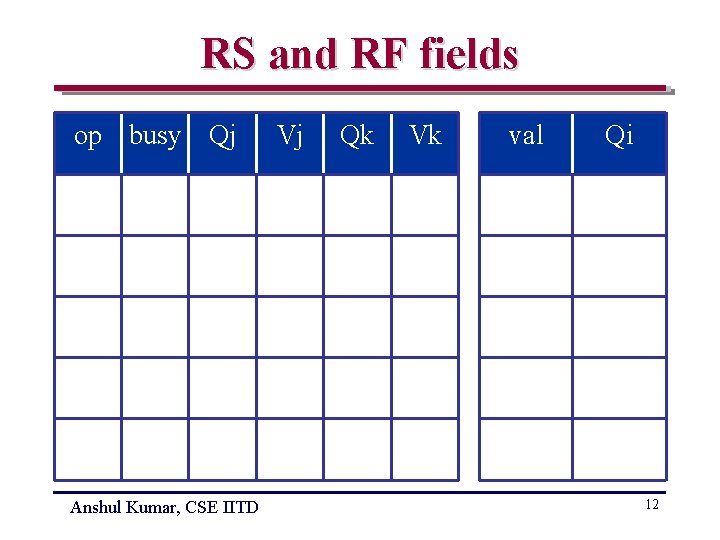

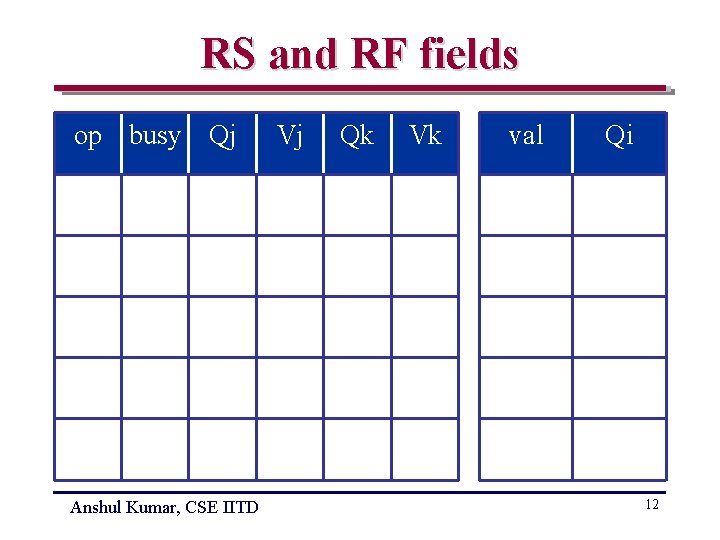

RS and RF fields op busy Qj Anshul Kumar, CSE IITD Vj Qk Vk val Qi 12

Issue • Get instruction <op, rd, rs, rt> from instruction queue • Wait until r RS[r]. busy = no • if (RF[rs]. Qi 0) {RS[r]. Qj RF[rs]. Qi} else {RS[r]. Vj RF[rs]. val; RS[r]. Qj 0} • similarly for rt • RS[r]. op op; RS[r]. busy yes; RF[rd]. Qi r Anshul Kumar, CSE IITD 13

![Execute Wait until RSr Qj 0 and RSr Qk 0 Execute • Wait until RS[r]. Qj = 0 and RS[r]. Qk = 0 •](https://slidetodoc.com/presentation_image_h/0fed0c70ac2a0be8d47e506c78387dcb/image-14.jpg)

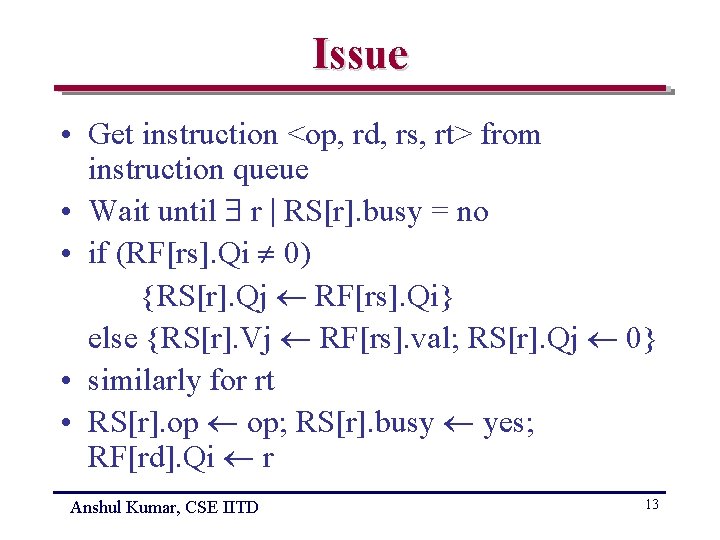

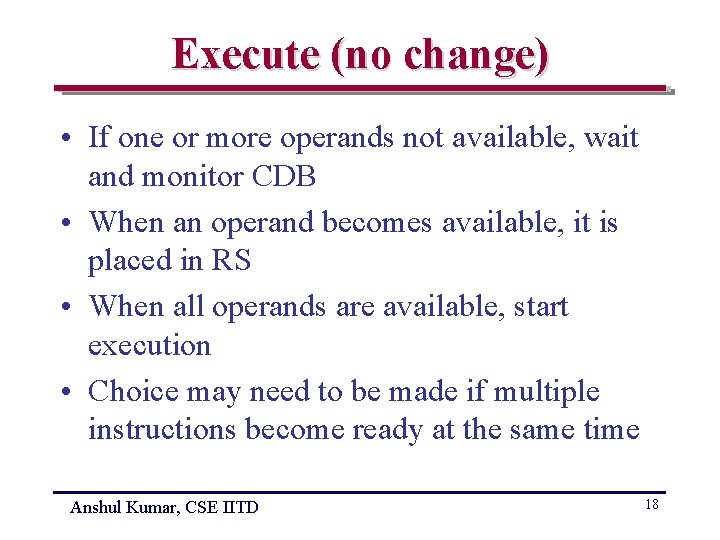

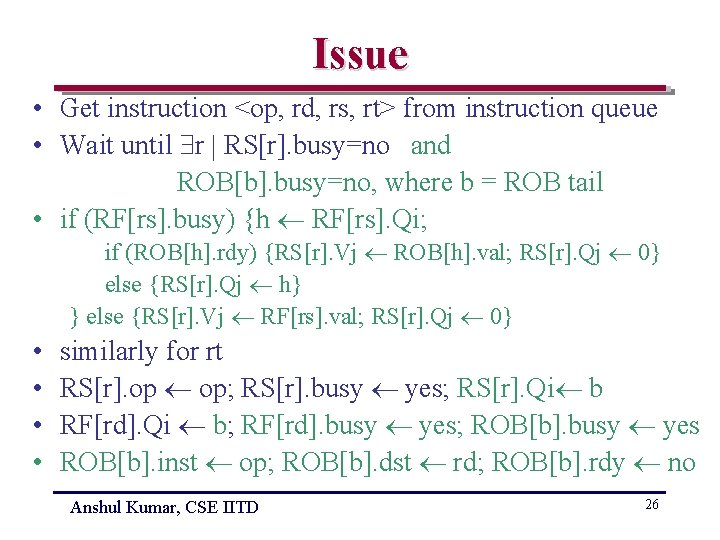

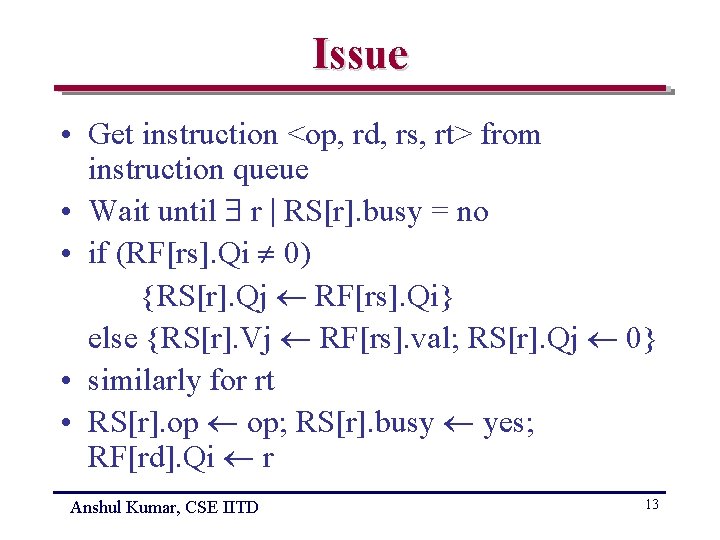

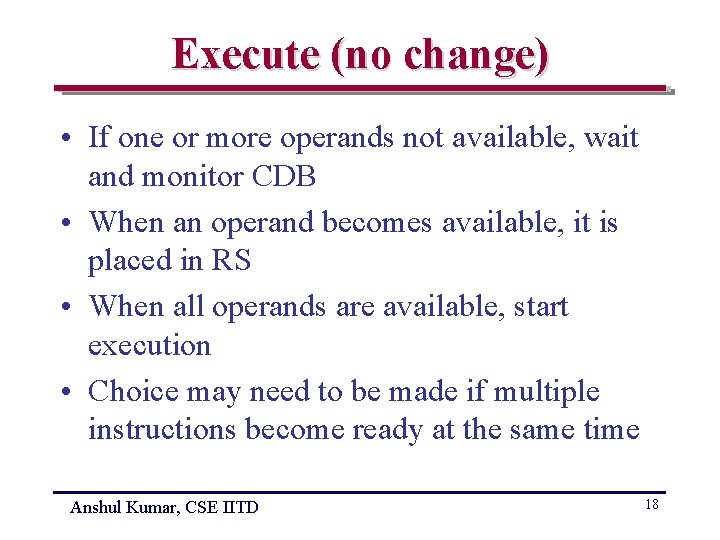

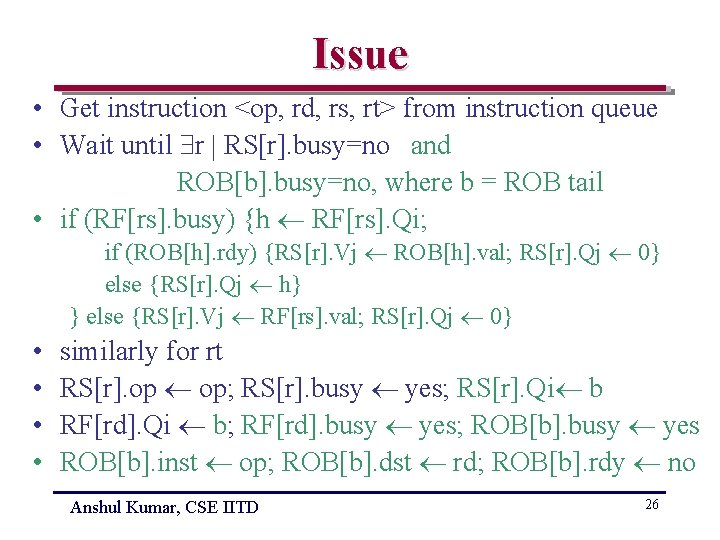

Execute • Wait until RS[r]. Qj = 0 and RS[r]. Qk = 0 • Compute result: operation is RS[r]. op, operands are RS[r]. Vj and RS[r]. Vk Anshul Kumar, CSE IITD 14

Write result • Wait until execution complete at r and CDB available • x if (RF[x]. Qi = r) {RF[x]. val result; RF[x]. Qi 0} • x if (RS[x]. Qj = r) {RS[x]. Vj result; RS[x]. Qj 0} • similarly for Qk / Vk • RS[r]. busy no Anshul Kumar, CSE IITD 15

Tomasulo’s scheme plus ROB. . . Anshul Kumar, CSE IITD 16

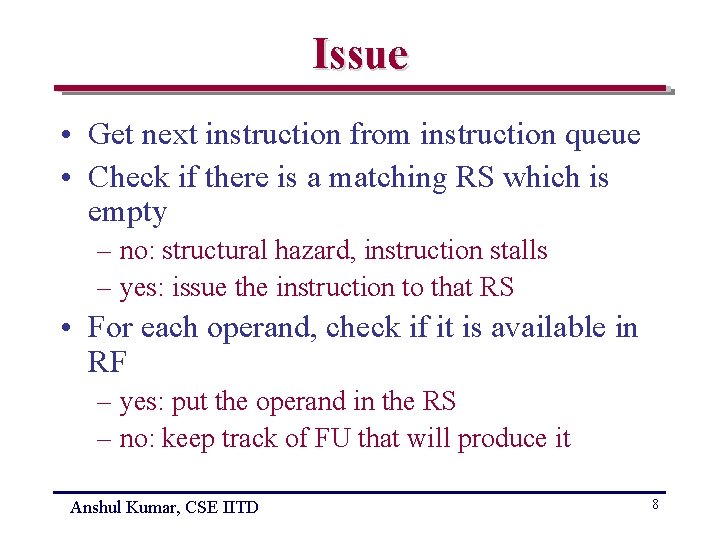

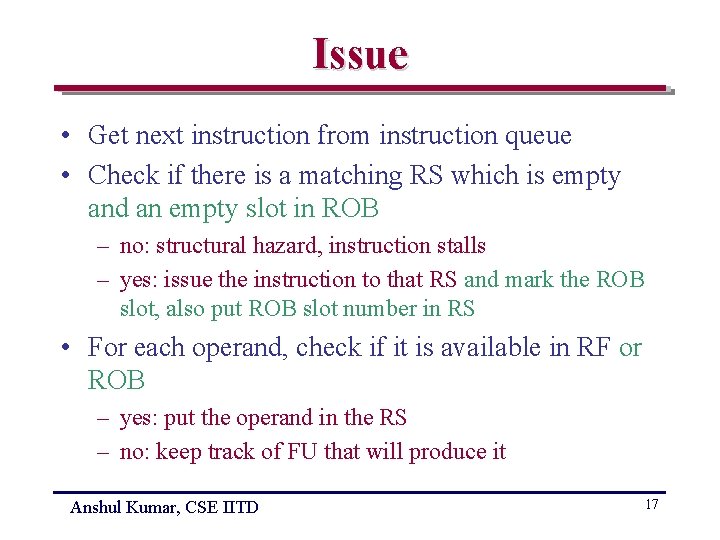

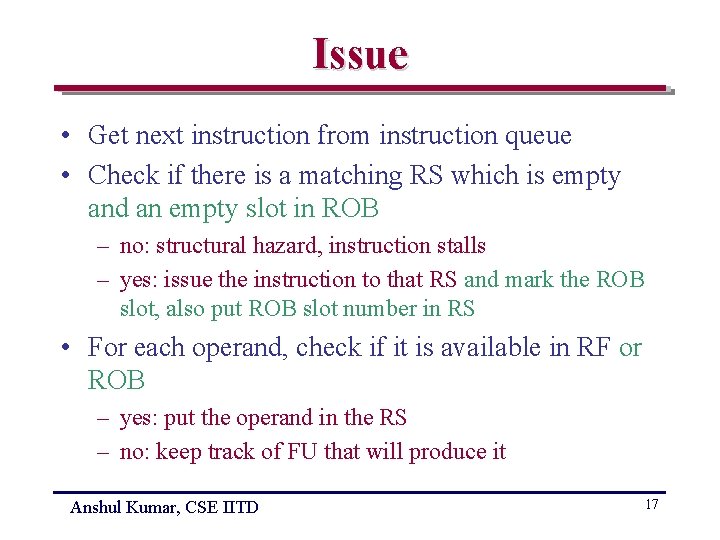

Issue • Get next instruction from instruction queue • Check if there is a matching RS which is empty and an empty slot in ROB – no: structural hazard, instruction stalls – yes: issue the instruction to that RS and mark the ROB slot, also put ROB slot number in RS • For each operand, check if it is available in RF or ROB – yes: put the operand in the RS – no: keep track of FU that will produce it Anshul Kumar, CSE IITD 17

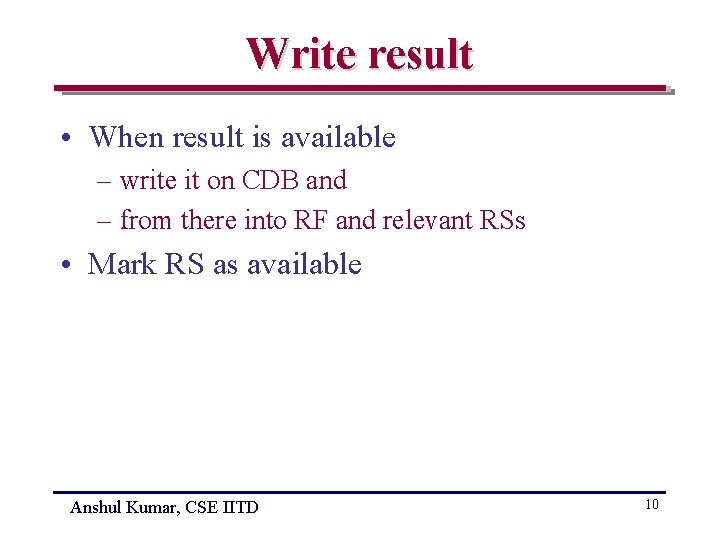

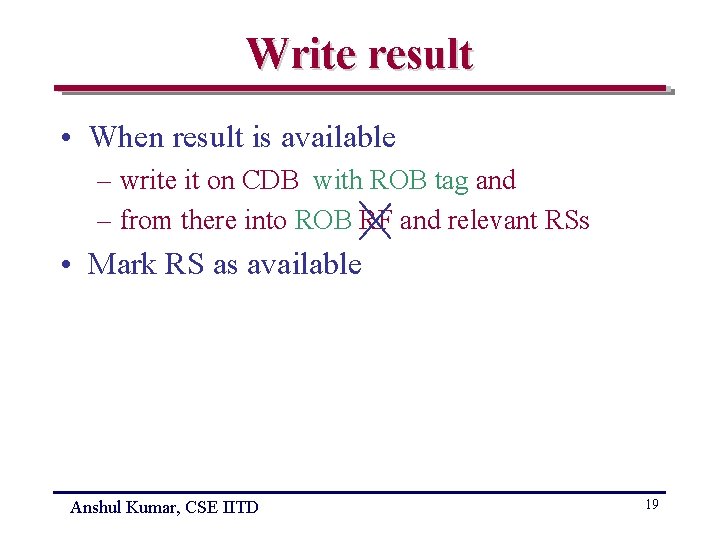

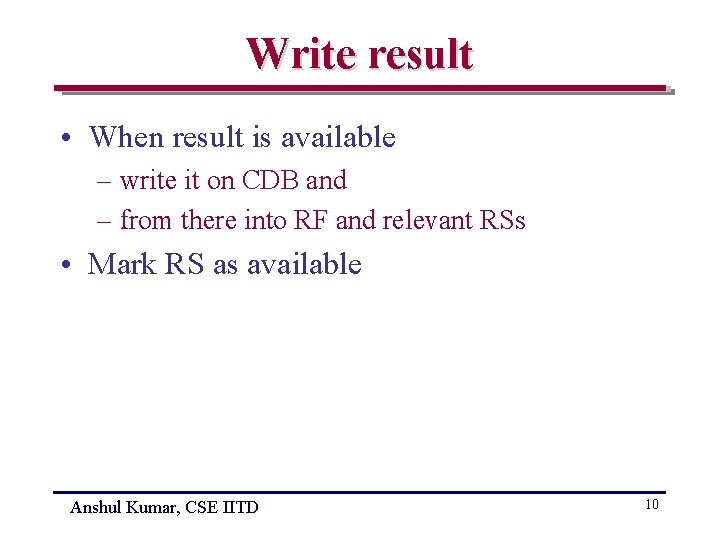

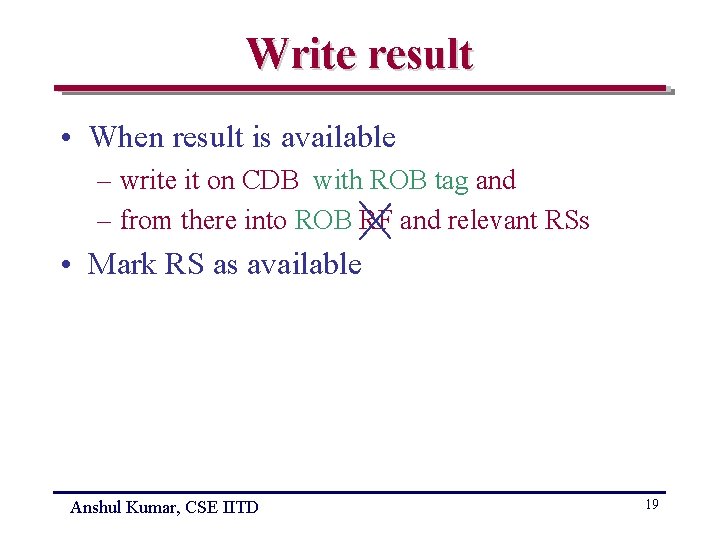

Execute (no change) • If one or more operands not available, wait and monitor CDB • When an operand becomes available, it is placed in RS • When all operands are available, start execution • Choice may need to be made if multiple instructions become ready at the same time Anshul Kumar, CSE IITD 18

Write result • When result is available – write it on CDB with ROB tag and – from there into ROB RF and relevant RSs • Mark RS as available Anshul Kumar, CSE IITD 19

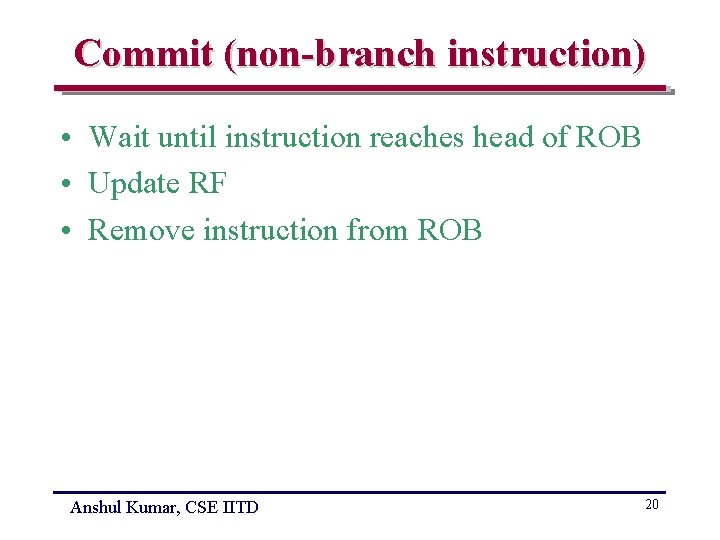

Commit (non-branch instruction) • Wait until instruction reaches head of ROB • Update RF • Remove instruction from ROB Anshul Kumar, CSE IITD 20

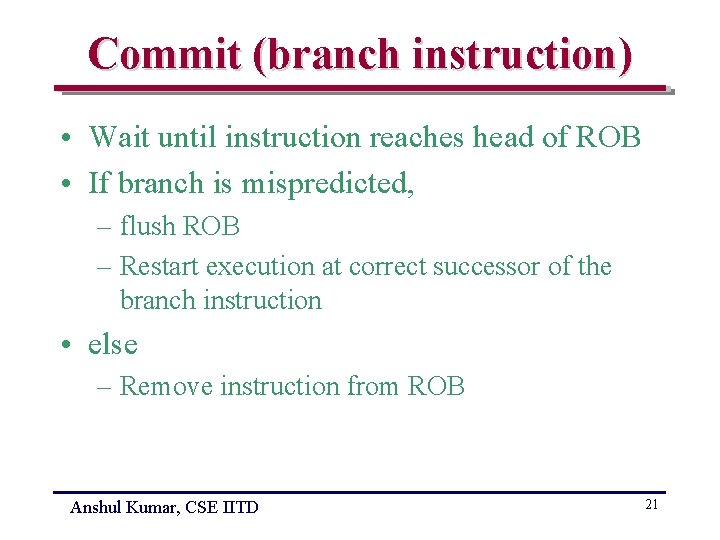

Commit (branch instruction) • Wait until instruction reaches head of ROB • If branch is mispredicted, – flush ROB – Restart execution at correct successor of the branch instruction • else – Remove instruction from ROB Anshul Kumar, CSE IITD 21

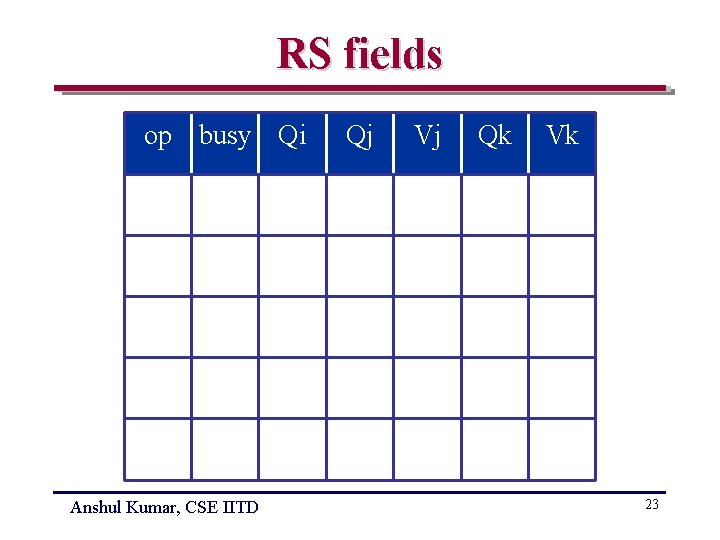

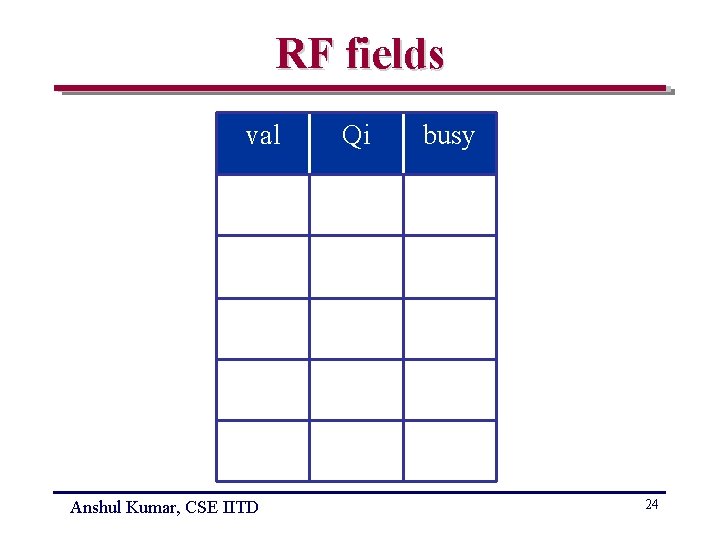

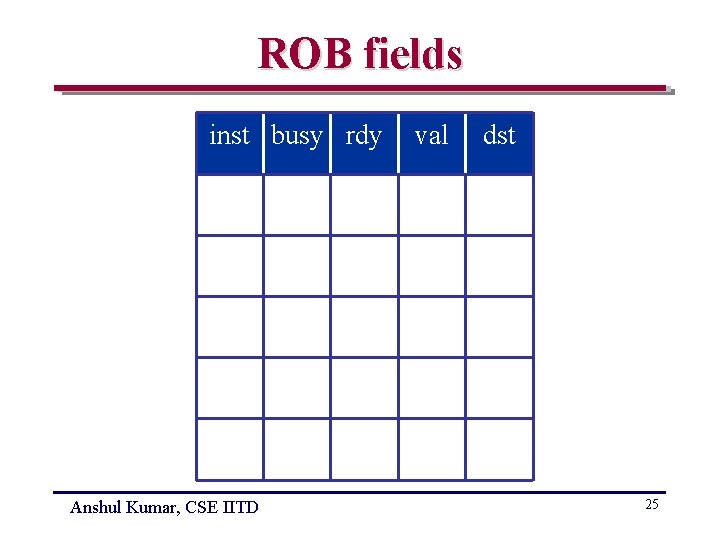

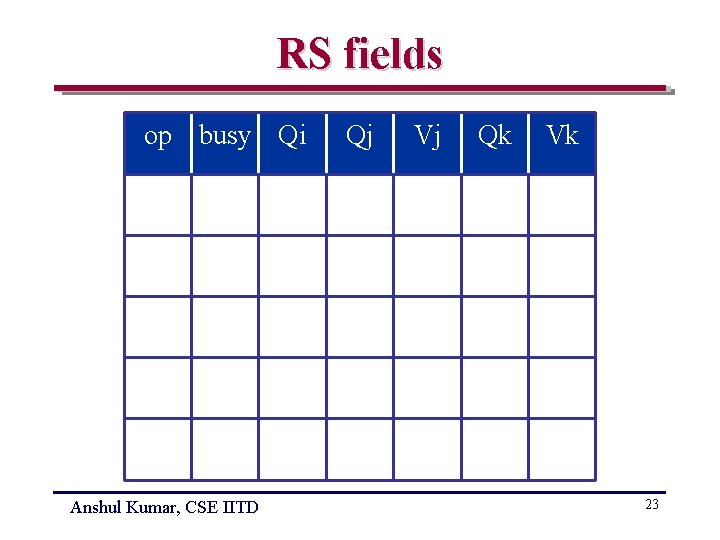

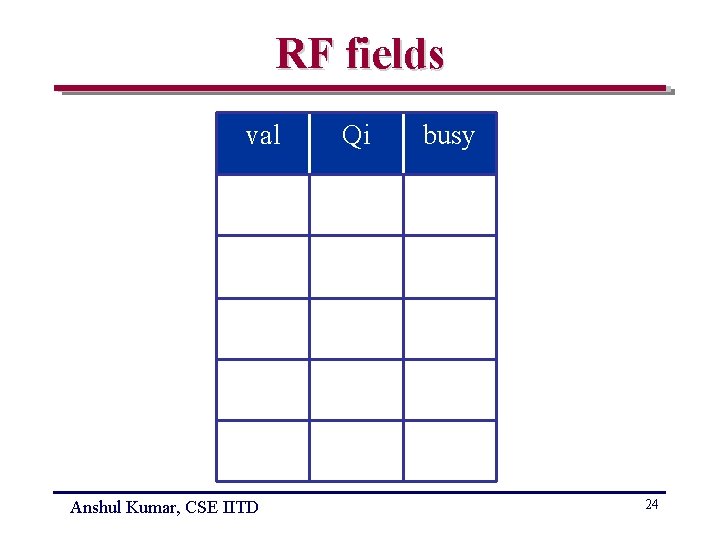

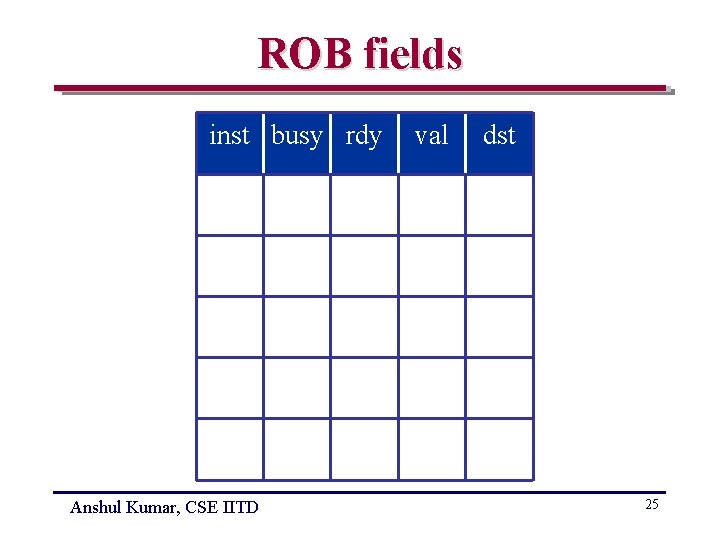

More formal description. . . Anshul Kumar, CSE IITD 22

RS fields op busy Qi Anshul Kumar, CSE IITD Qj Vj Qk Vk 23

RF fields val Anshul Kumar, CSE IITD Qi busy 24

ROB fields inst busy rdy Anshul Kumar, CSE IITD val dst 25

Issue • Get instruction <op, rd, rs, rt> from instruction queue • Wait until r RS[r]. busy=no and ROB[b]. busy=no, where b = ROB tail • if (RF[rs]. busy) {h RF[rs]. Qi; if (ROB[h]. rdy) {RS[r]. Vj ROB[h]. val; RS[r]. Qj 0} else {RS[r]. Qj h} } else {RS[r]. Vj RF[rs]. val; RS[r]. Qj 0} • • similarly for rt RS[r]. op op; RS[r]. busy yes; RS[r]. Qi b RF[rd]. Qi b; RF[rd]. busy yes; ROB[b]. busy yes ROB[b]. inst op; ROB[b]. dst rd; ROB[b]. rdy no Anshul Kumar, CSE IITD 26

![Execute no change Wait until RSr Qj 0 and RSr Qk Execute (no change) • Wait until RS[r]. Qj = 0 and RS[r]. Qk =](https://slidetodoc.com/presentation_image_h/0fed0c70ac2a0be8d47e506c78387dcb/image-27.jpg)

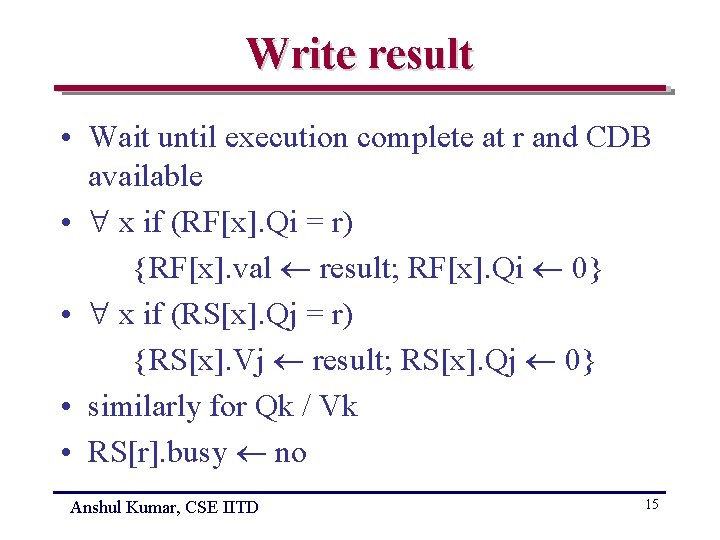

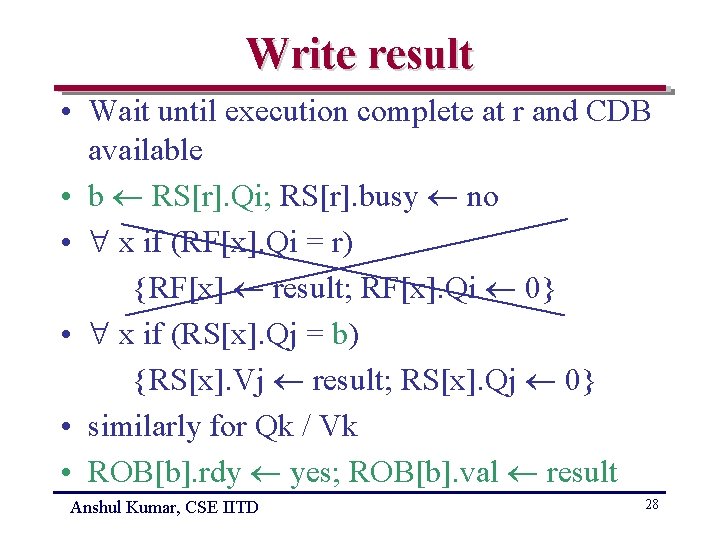

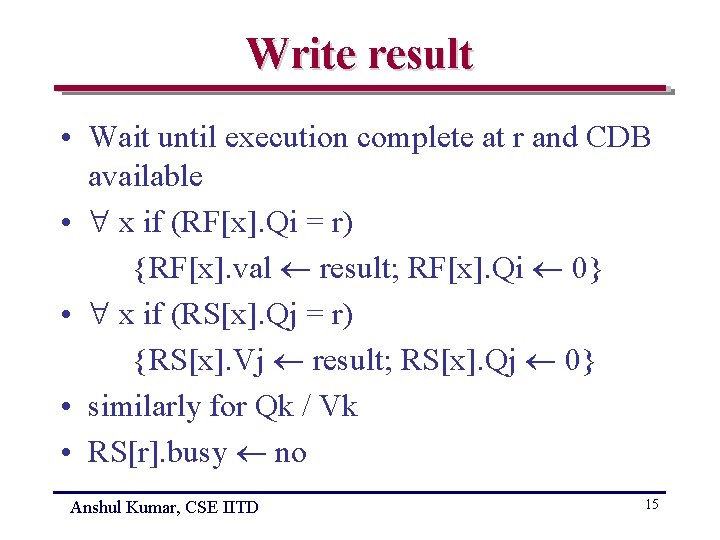

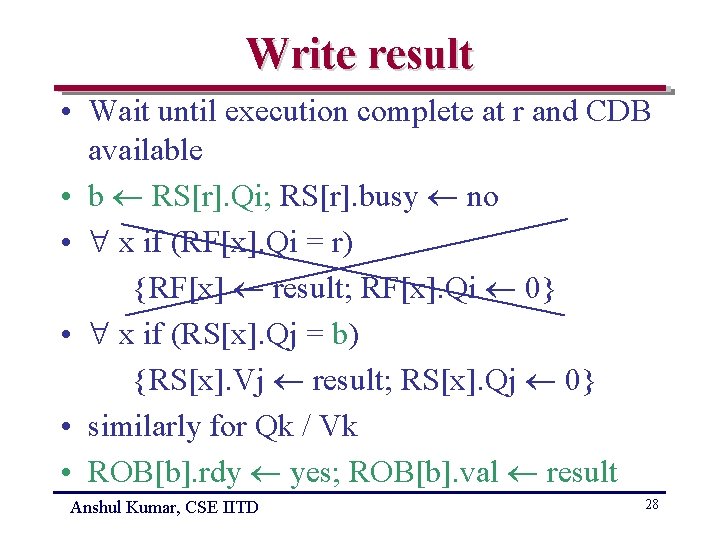

Execute (no change) • Wait until RS[r]. Qj = 0 and RS[r]. Qk = 0 • Compute result: operation is RS[r]. op, operands are RS[r]. Vj and RS[r]. Vk Anshul Kumar, CSE IITD 27

Write result • Wait until execution complete at r and CDB available • b RS[r]. Qi; RS[r]. busy no • x if (RF[x]. Qi = r) {RF[x] result; RF[x]. Qi 0} • x if (RS[x]. Qj = b) {RS[x]. Vj result; RS[x]. Qj 0} • similarly for Qk / Vk • ROB[b]. rdy yes; ROB[b]. val result Anshul Kumar, CSE IITD 28

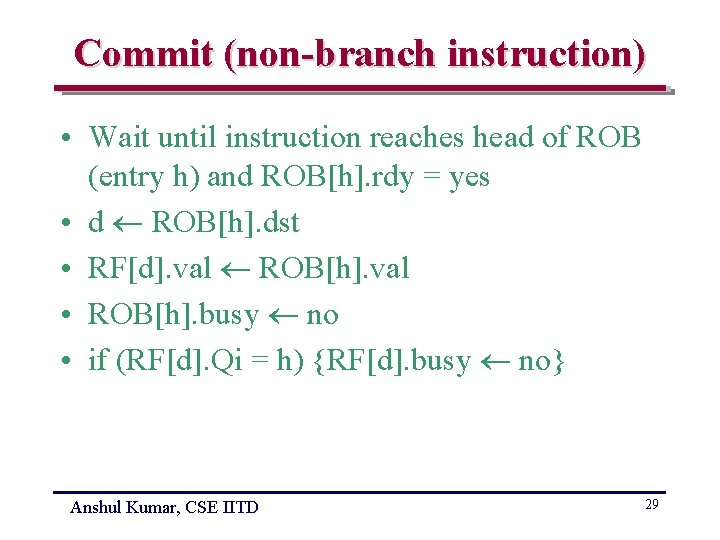

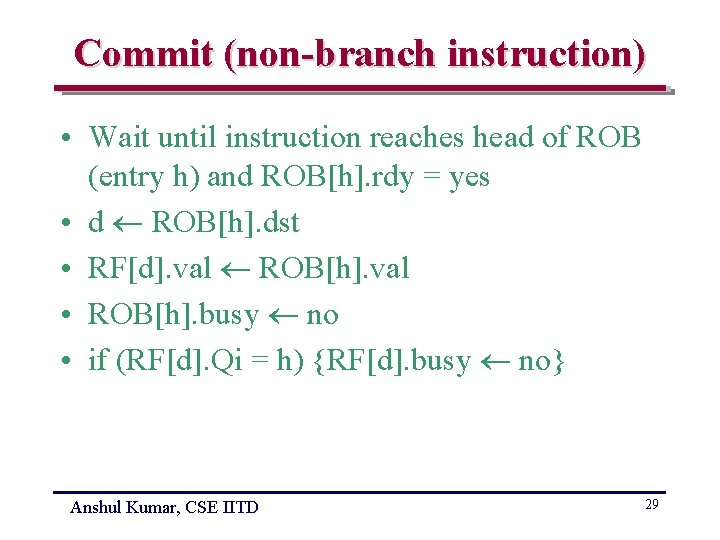

Commit (non-branch instruction) • Wait until instruction reaches head of ROB (entry h) and ROB[h]. rdy = yes • d ROB[h]. dst • RF[d]. val ROB[h]. val • ROB[h]. busy no • if (RF[d]. Qi = h) {RF[d]. busy no} Anshul Kumar, CSE IITD 29

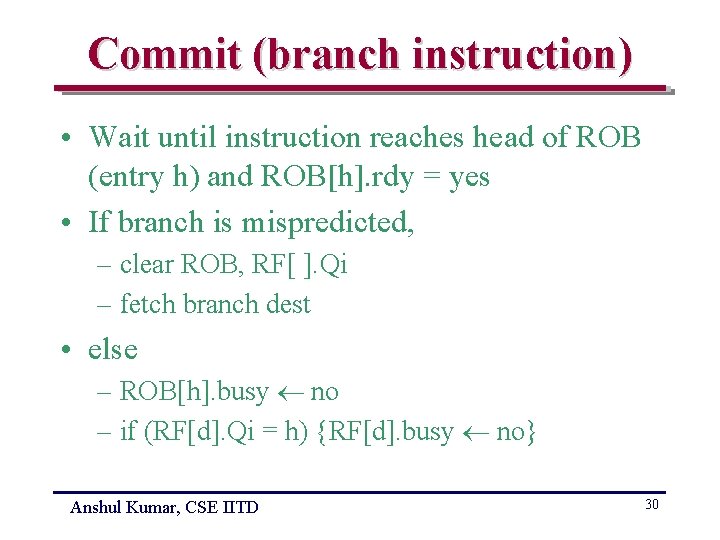

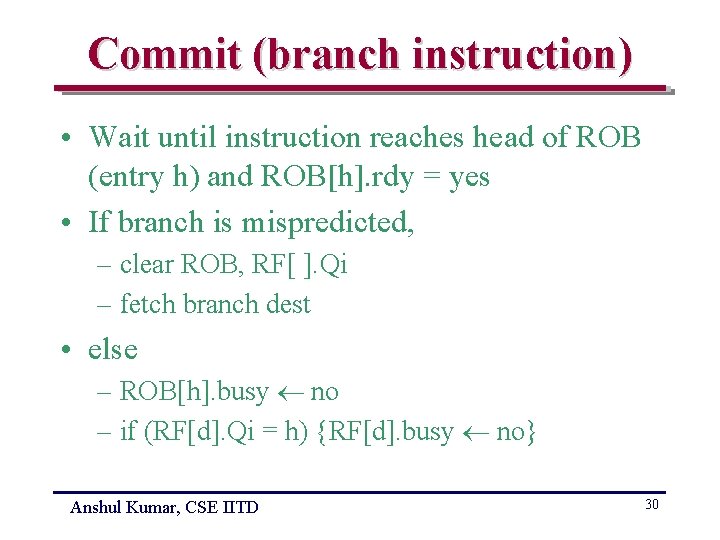

Commit (branch instruction) • Wait until instruction reaches head of ROB (entry h) and ROB[h]. rdy = yes • If branch is mispredicted, – clear ROB, RF[ ]. Qi – fetch branch dest • else – ROB[h]. busy no – if (RF[d]. Qi = h) {RF[d]. busy no} Anshul Kumar, CSE IITD 30