CS M 51 AEE M 16 Winter 05

- Slides: 34

CS M 51 A/EE M 16 Winter’ 05 Section 1 Logic Design of Digital Systems Lecture 16 March 14 W’ 05 Yutao He yutao@cs. ucla. edu 4532 B Boelter Hall http: //courseweb. seas. ucla. edu/class. View. php? term=05 W&srs=187154200 CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 1 Y. He @ 11/24/2020

Outline • Administrative Matters • Recap – Registers – Shift Registers • Chapter 11 – Sequential macro modules – Counters CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 2 Y. He @ 11/24/2020

Administrative Matters • HW# 9 – Is posted and will be self-graded – Describes how the topics in Ch. 11 and 12 will be tested • The Final – Is given on Friday – A review session will be held on Wednesday – Extra office hours will be scheduled • My office hours this week – Monday and Wednesday * 6 -7: 30 pm – Thursday * 7: 30 -9 pm • Graded work CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 3 Y. He @ 11/24/2020

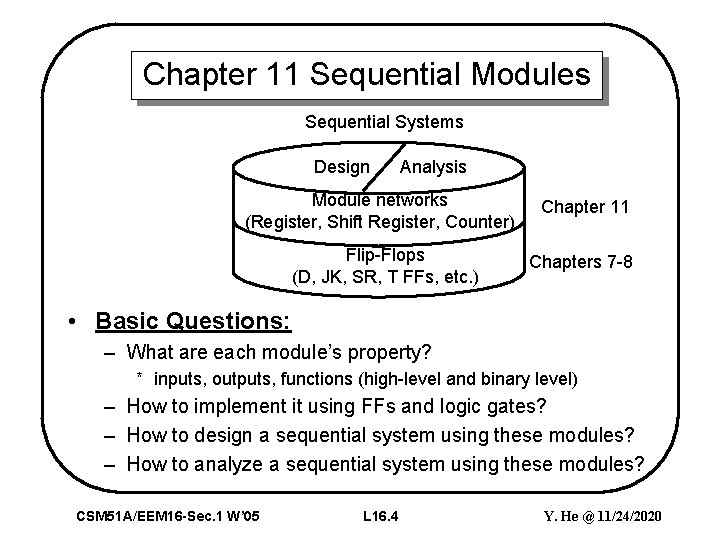

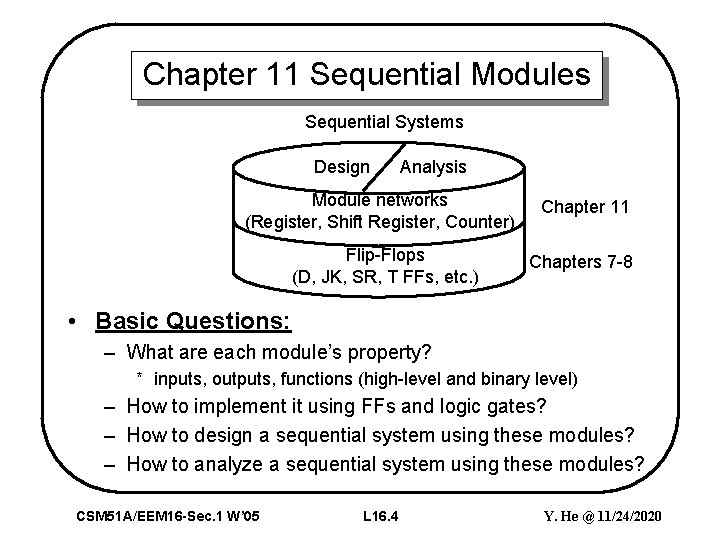

Chapter 11 Sequential Modules Sequential Systems Design Analysis Module networks (Register, Shift Register, Counter) Flip-Flops (D, JK, SR, T FFs, etc. ) Chapter 11 Chapters 7 -8 • Basic Questions: – What are each module’s property? * inputs, outputs, functions (high-level and binary level) – How to implement it using FFs and logic gates? – How to design a sequential system using these modules? – How to analyze a sequential system using these modules? CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 4 Y. He @ 11/24/2020

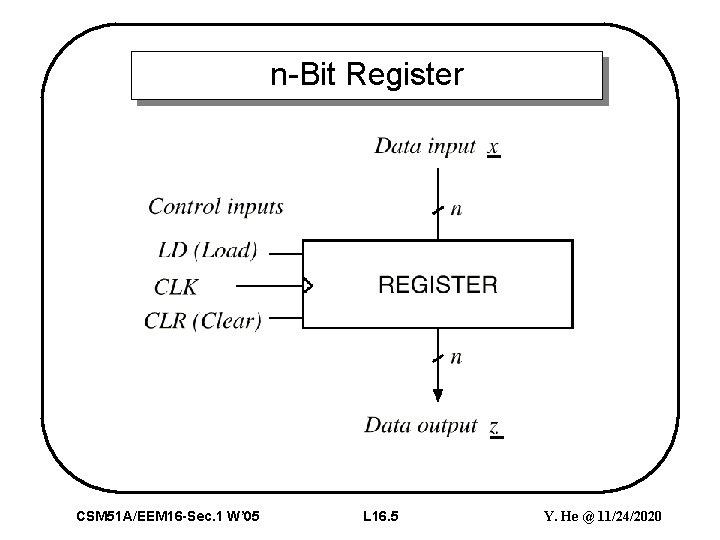

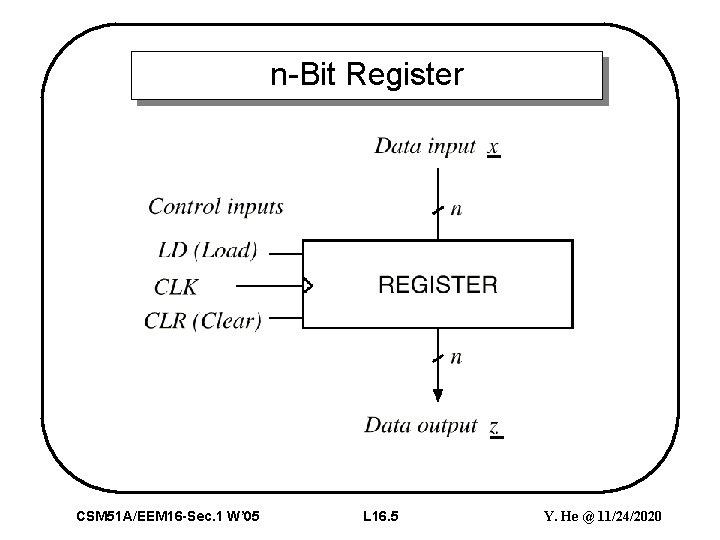

n-Bit Register CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 5 Y. He @ 11/24/2020

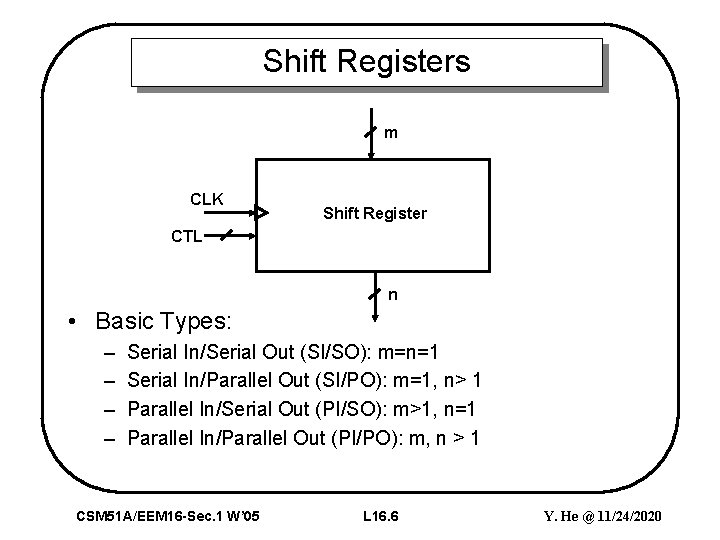

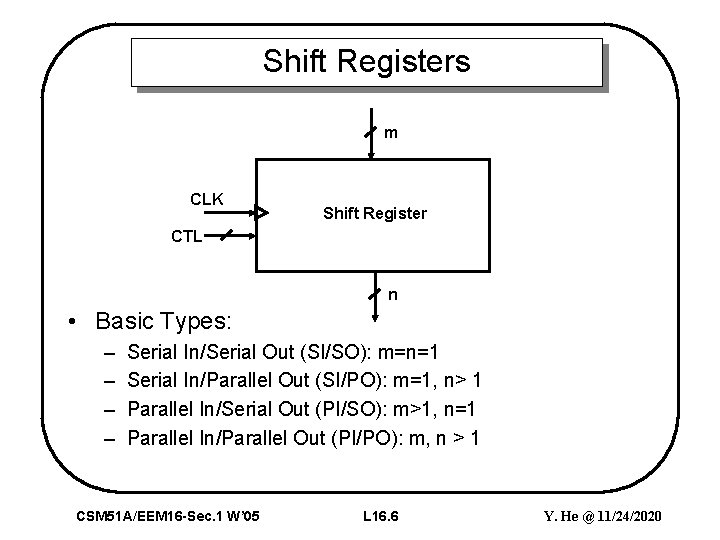

Shift Registers m CLK Shift Register CTL n • Basic Types: – – Serial In/Serial Out (SI/SO): m=n=1 Serial In/Parallel Out (SI/PO): m=1, n> 1 Parallel In/Serial Out (PI/SO): m>1, n=1 Parallel In/Parallel Out (PI/PO): m, n > 1 CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 6 Y. He @ 11/24/2020

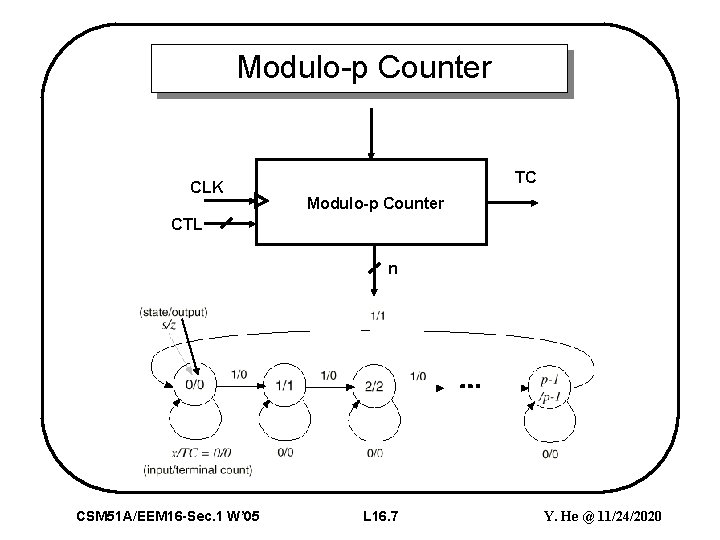

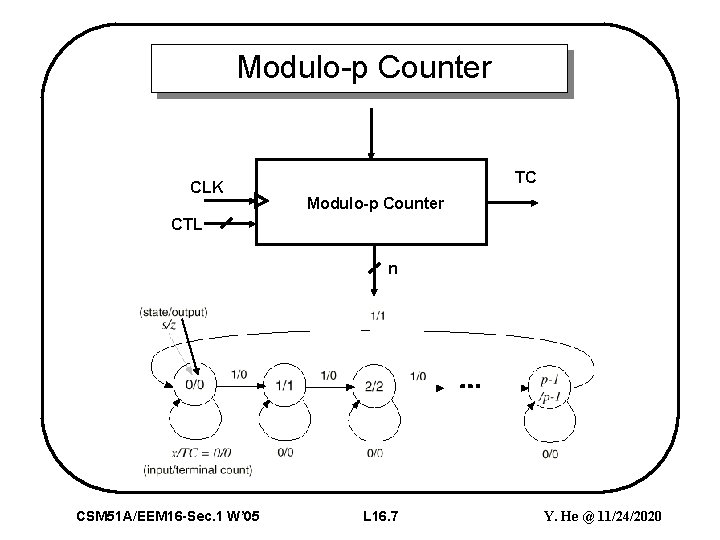

Modulo-p Counter CLK TC Modulo-p Counter CTL n CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 7 Y. He @ 11/24/2020

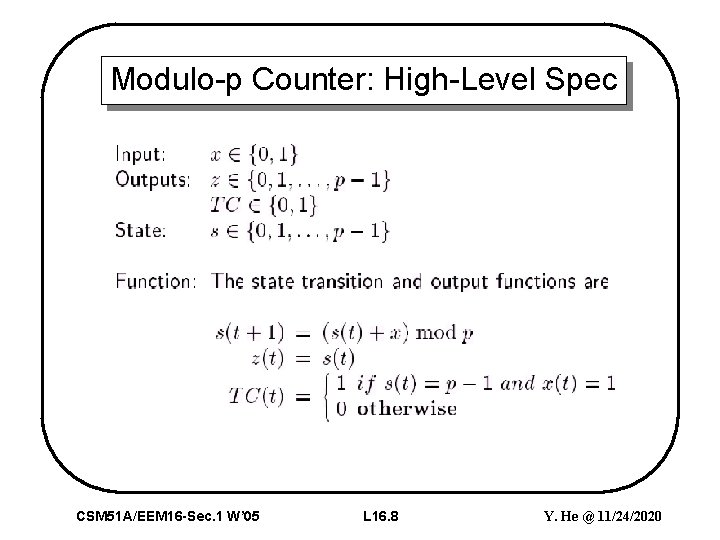

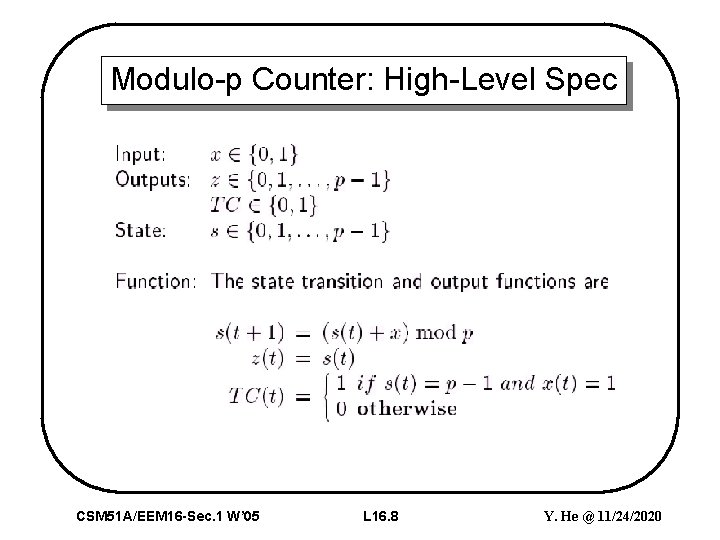

Modulo-p Counter: High-Level Spec CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 8 Y. He @ 11/24/2020

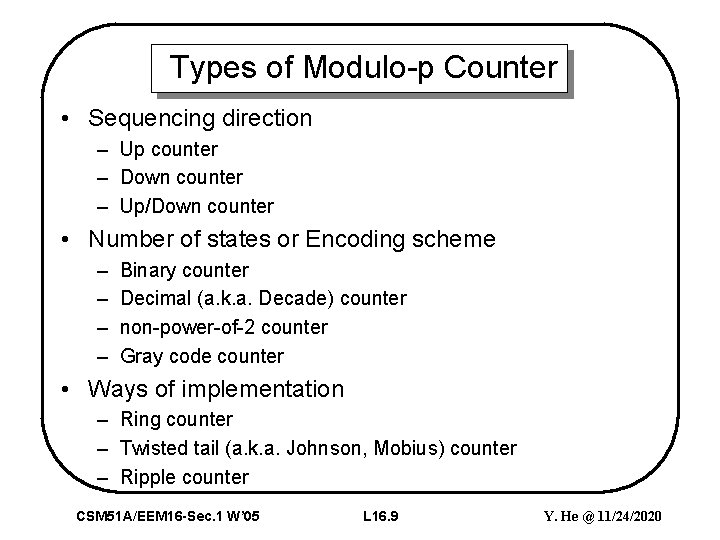

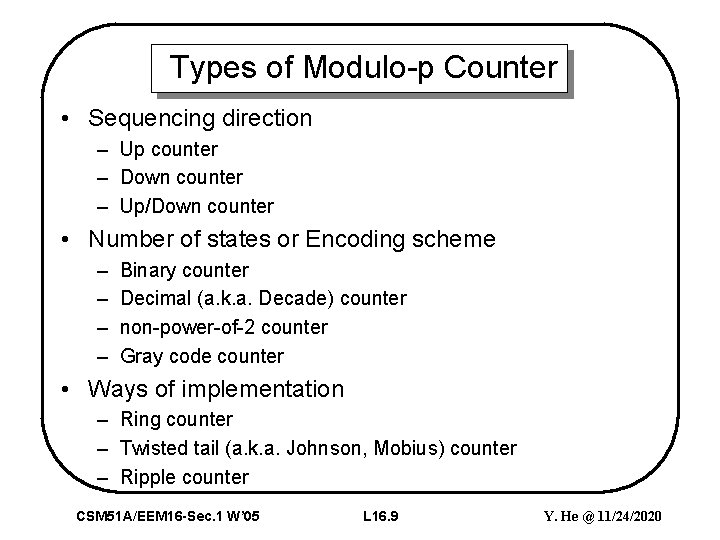

Types of Modulo-p Counter • Sequencing direction – Up counter – Down counter – Up/Down counter • Number of states or Encoding scheme – – Binary counter Decimal (a. k. a. Decade) counter non-power-of-2 counter Gray code counter • Ways of implementation – Ring counter – Twisted tail (a. k. a. Johnson, Mobius) counter – Ripple counter CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 9 Y. He @ 11/24/2020

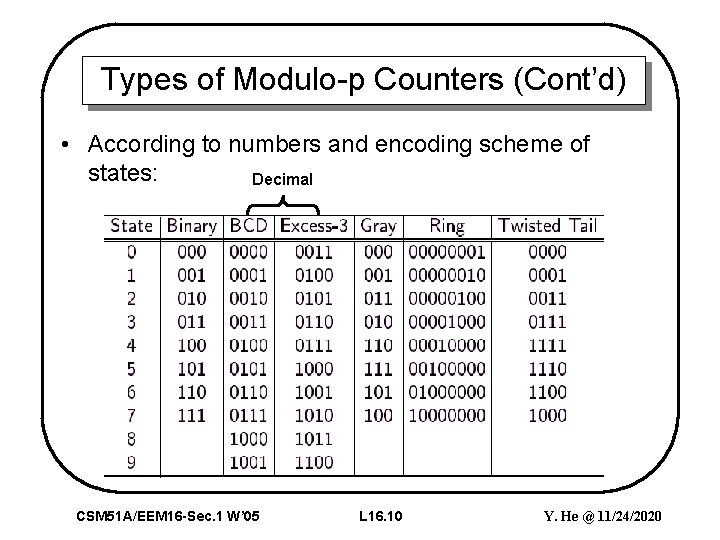

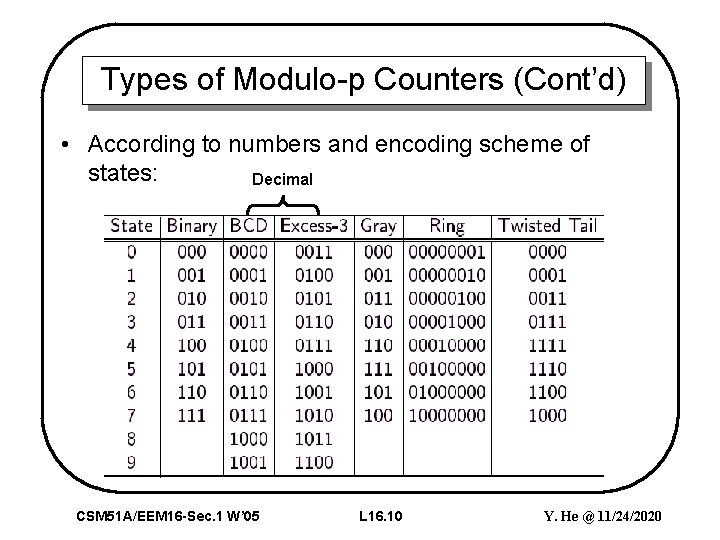

Types of Modulo-p Counters (Cont’d) • According to numbers and encoding scheme of states: Decimal CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 10 Y. He @ 11/24/2020

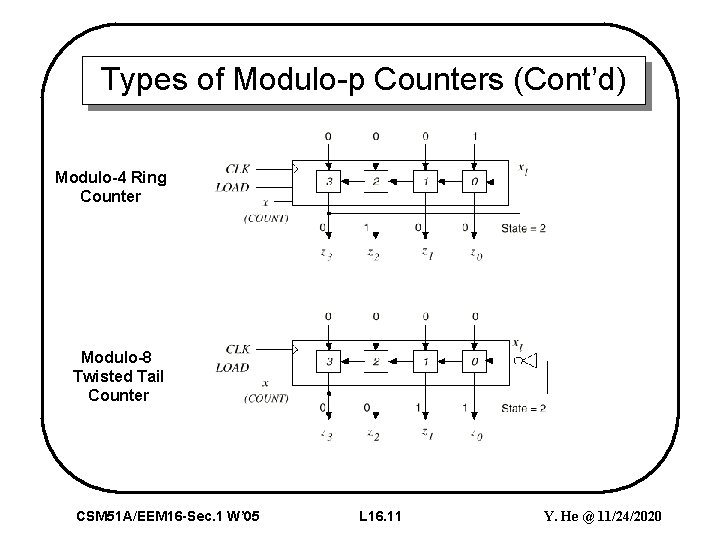

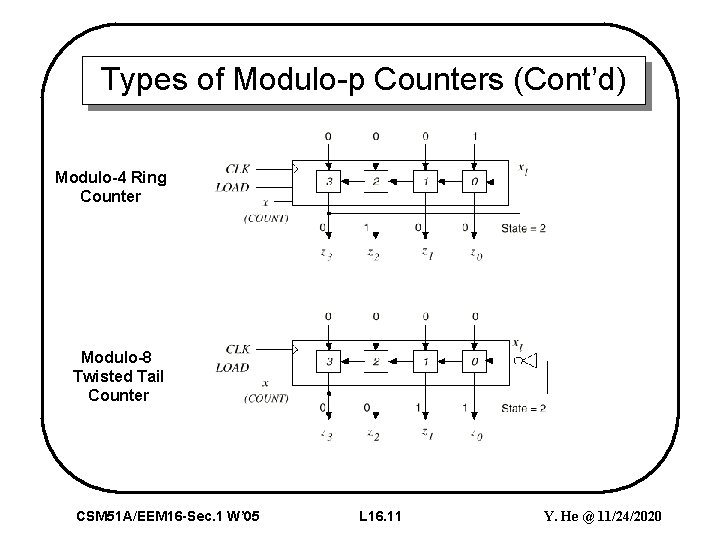

Types of Modulo-p Counters (Cont’d) Modulo-4 Ring Counter Modulo-8 Twisted Tail Counter CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 11 Y. He @ 11/24/2020

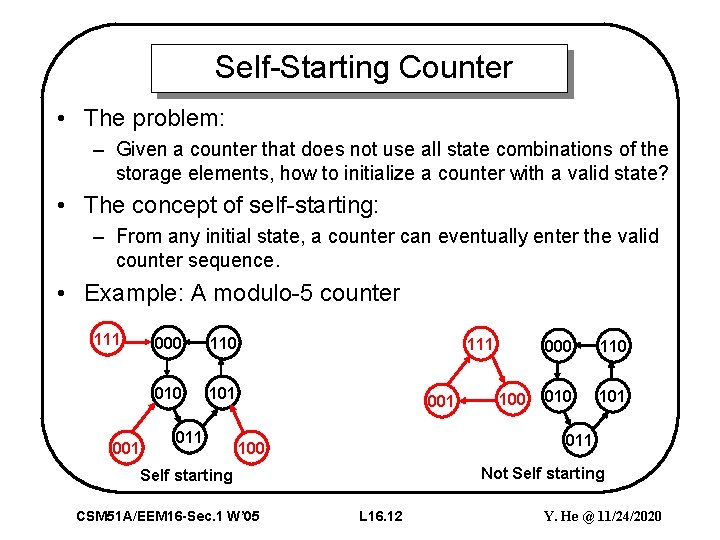

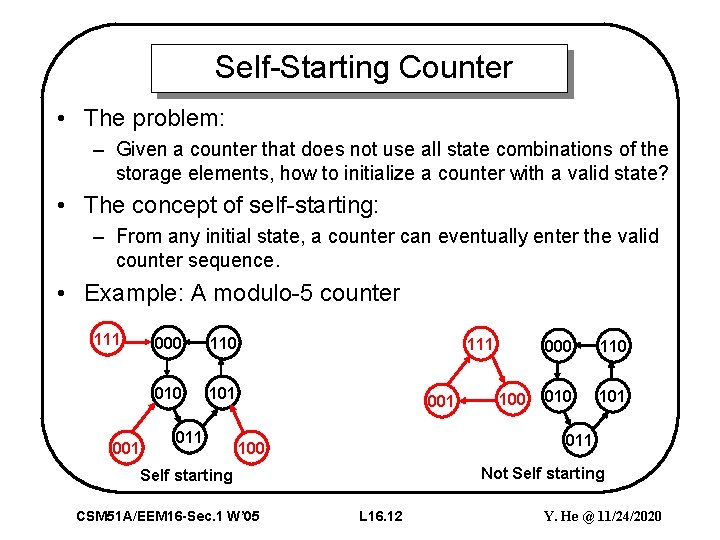

Self-Starting Counter • The problem: – Given a counter that does not use all state combinations of the storage elements, how to initialize a counter with a valid state? • The concept of self-starting: – From any initial state, a counter can eventually enter the valid counter sequence. • Example: A modulo-5 counter 111 000 110 010 101 011 111 001 110 010 101 011 100 Not Self starting CSM 51 A/EEM 16 -Sec. 1 W’ 05 100 000 L 16. 12 Y. He @ 11/24/2020

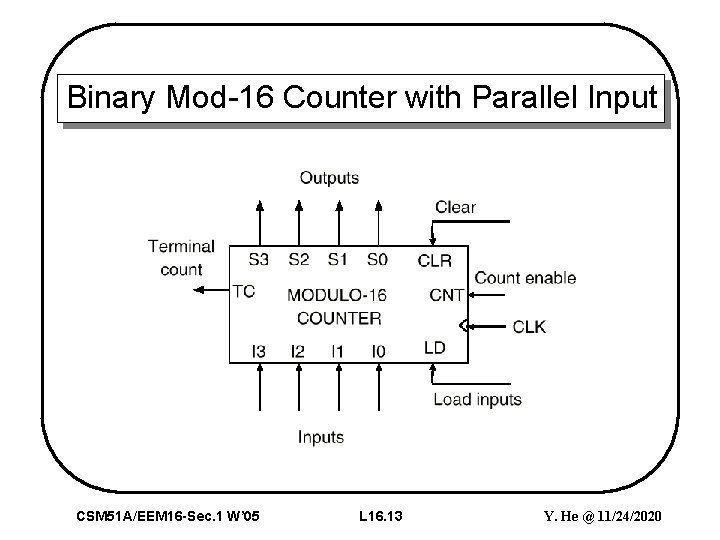

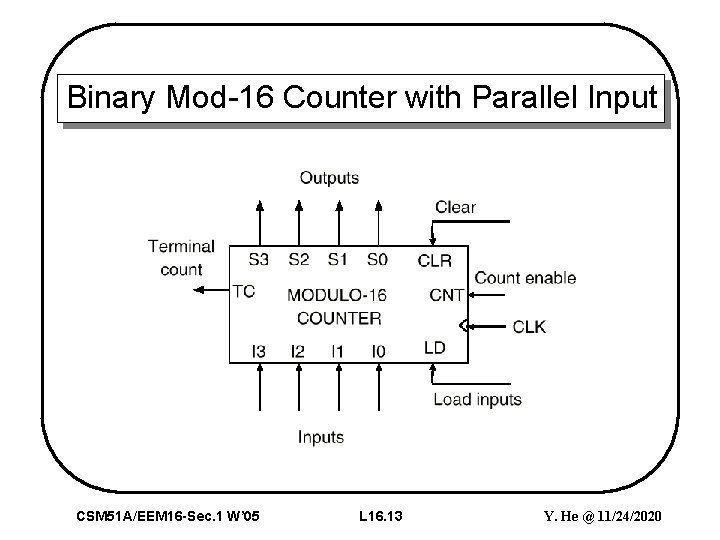

Binary Mod-16 Counter with Parallel Input CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 13 Y. He @ 11/24/2020

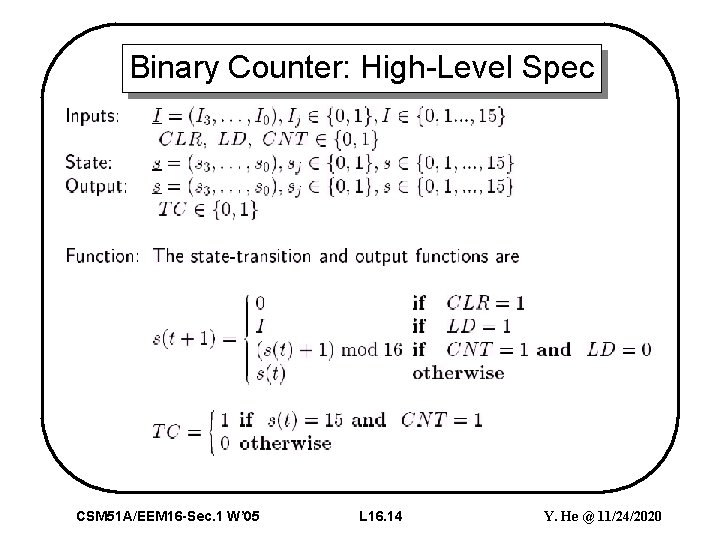

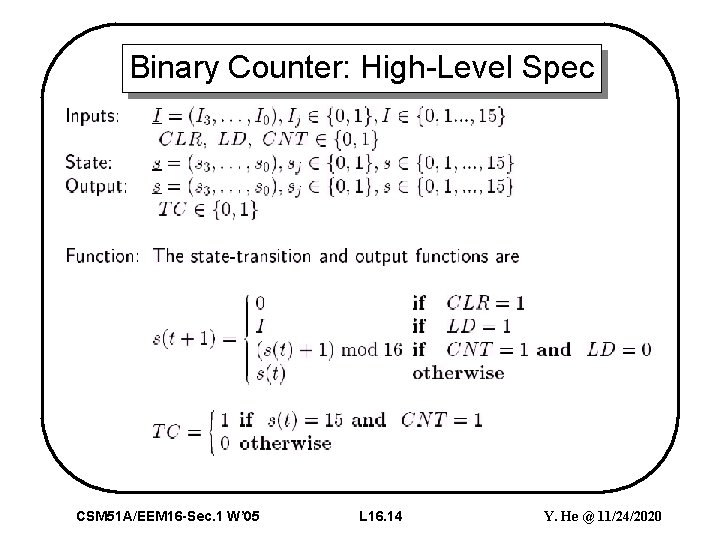

Binary Counter: High-Level Spec CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 14 Y. He @ 11/24/2020

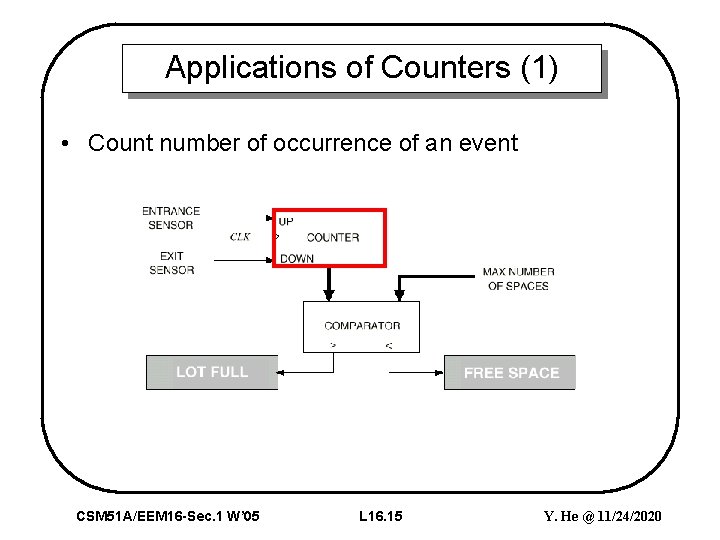

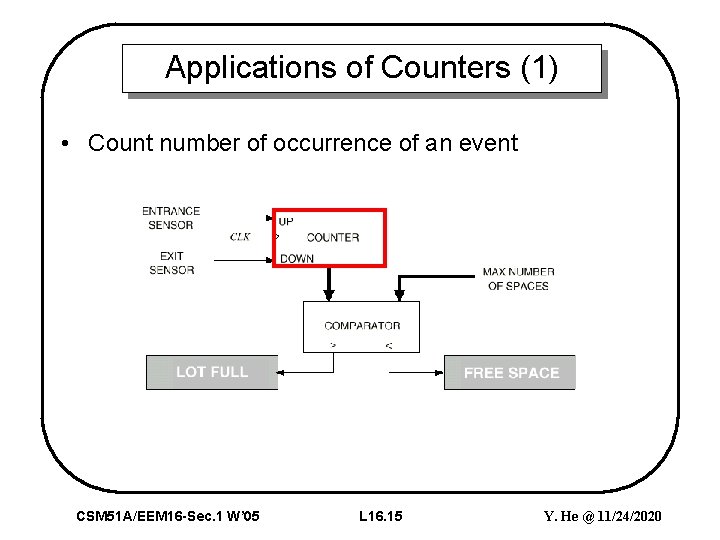

Applications of Counters (1) • Count number of occurrence of an event CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 15 Y. He @ 11/24/2020

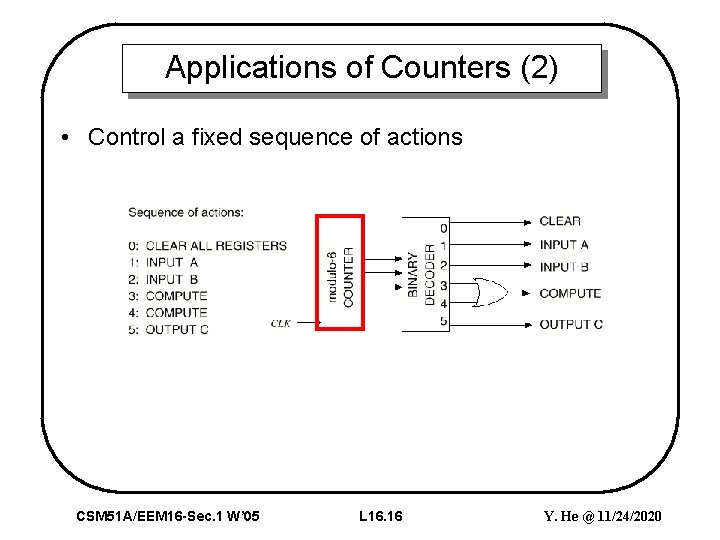

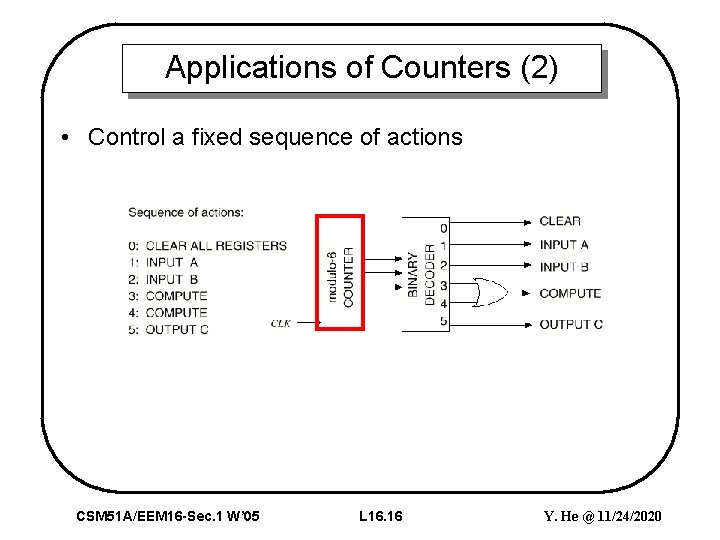

Applications of Counters (2) • Control a fixed sequence of actions CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 16 Y. He @ 11/24/2020

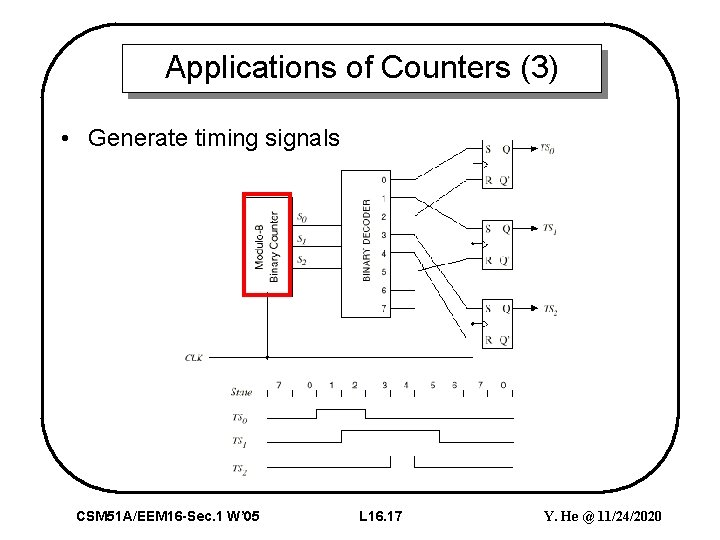

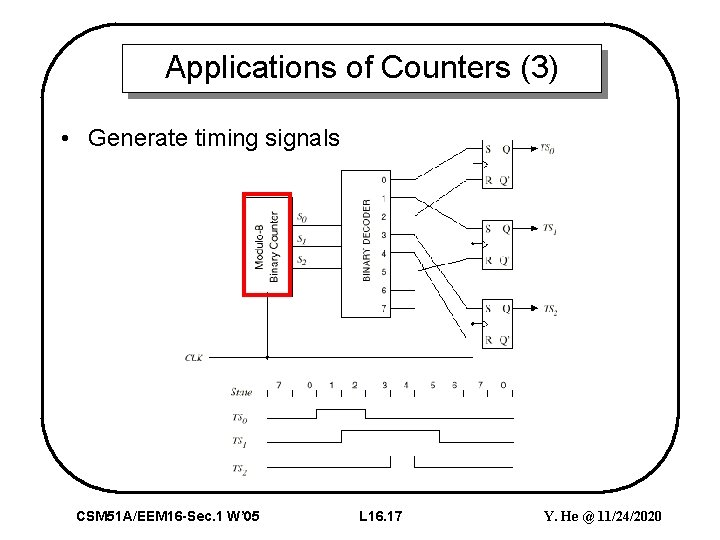

Applications of Counters (3) • Generate timing signals CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 17 Y. He @ 11/24/2020

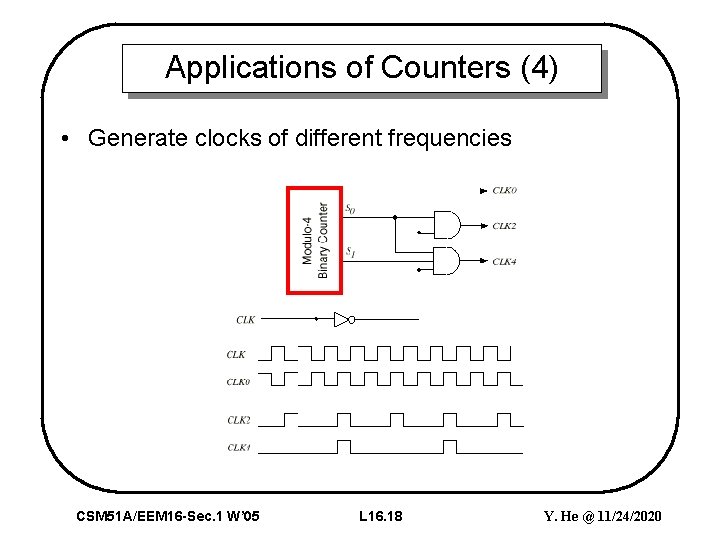

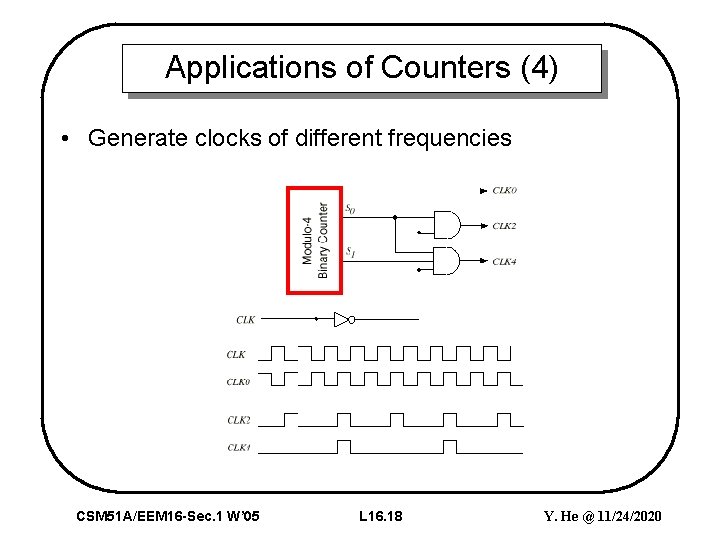

Applications of Counters (4) • Generate clocks of different frequencies CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 18 Y. He @ 11/24/2020

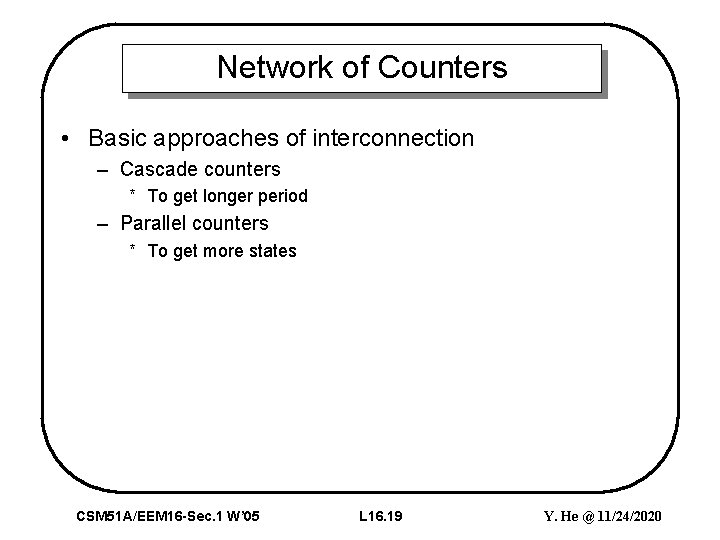

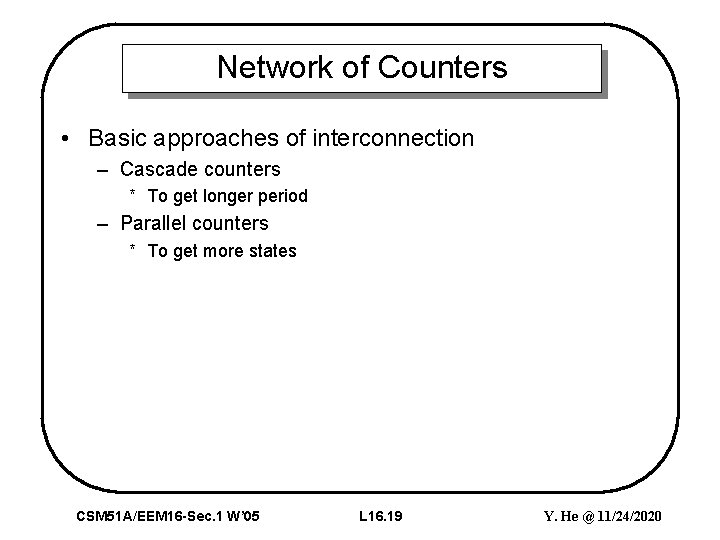

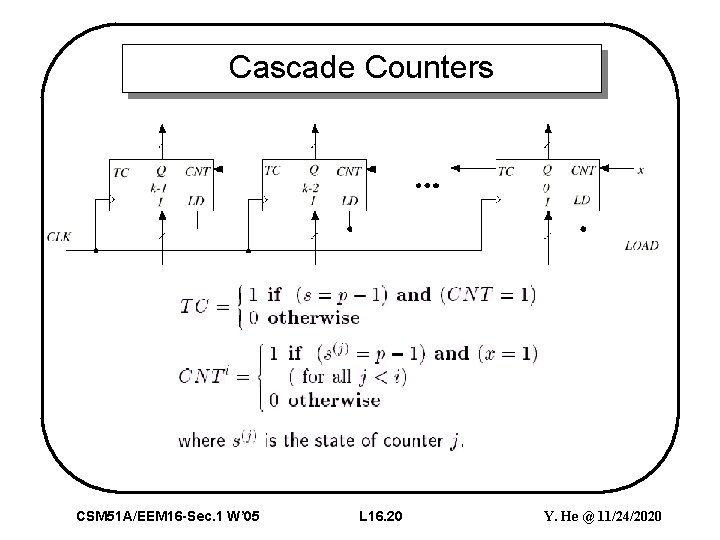

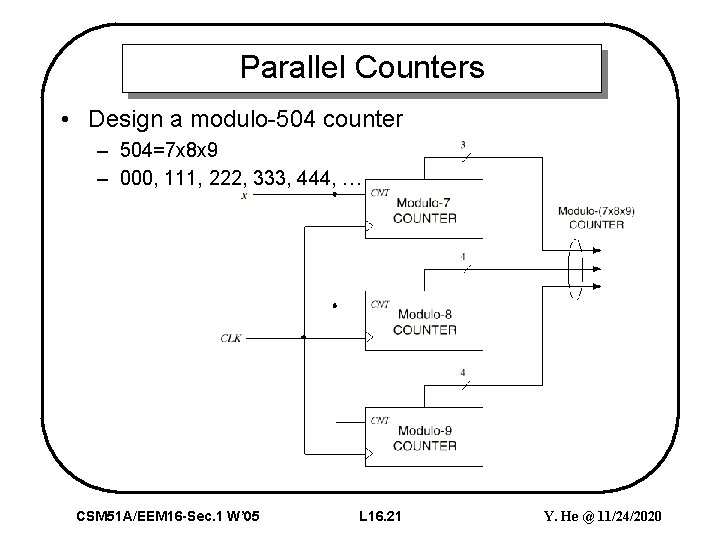

Network of Counters • Basic approaches of interconnection – Cascade counters * To get longer period – Parallel counters * To get more states CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 19 Y. He @ 11/24/2020

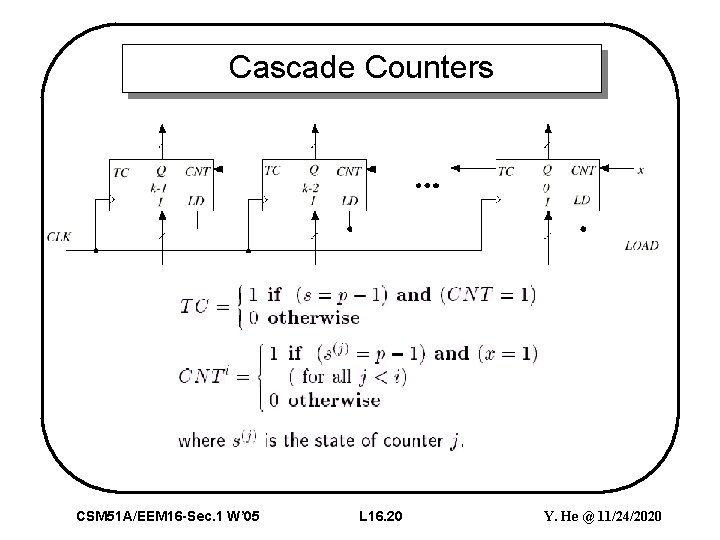

Cascade Counters CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 20 Y. He @ 11/24/2020

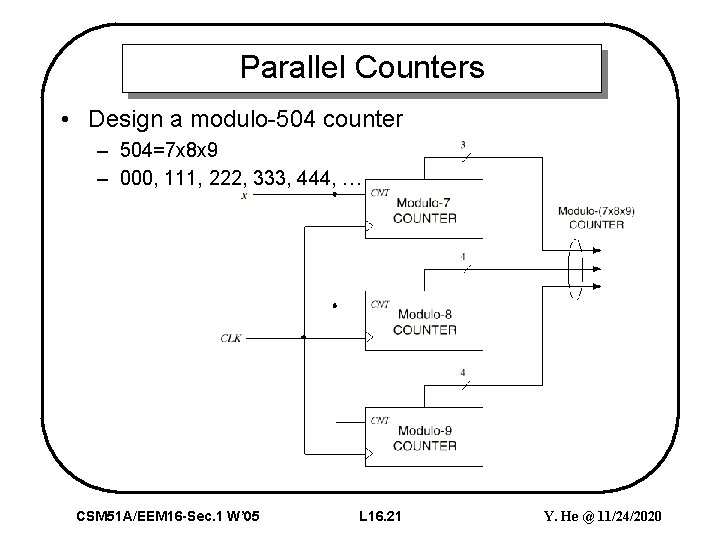

Parallel Counters • Design a modulo-504 counter – 504=7 x 8 x 9 – 000, 111, 222, 333, 444, … CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 21 Y. He @ 11/24/2020

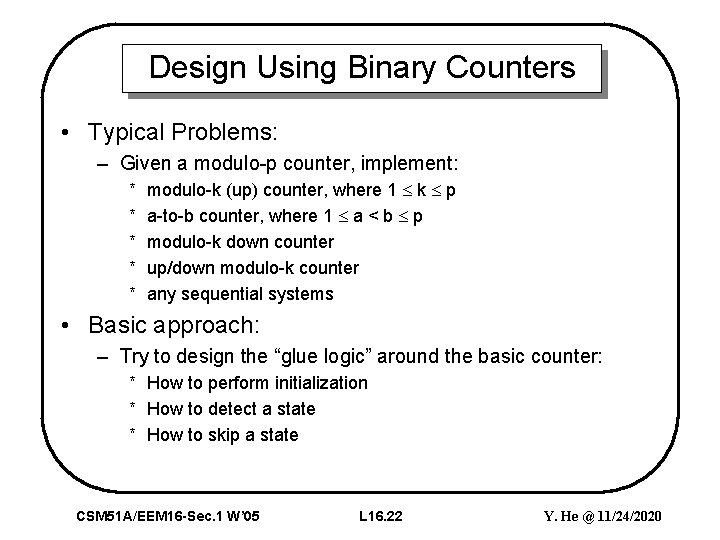

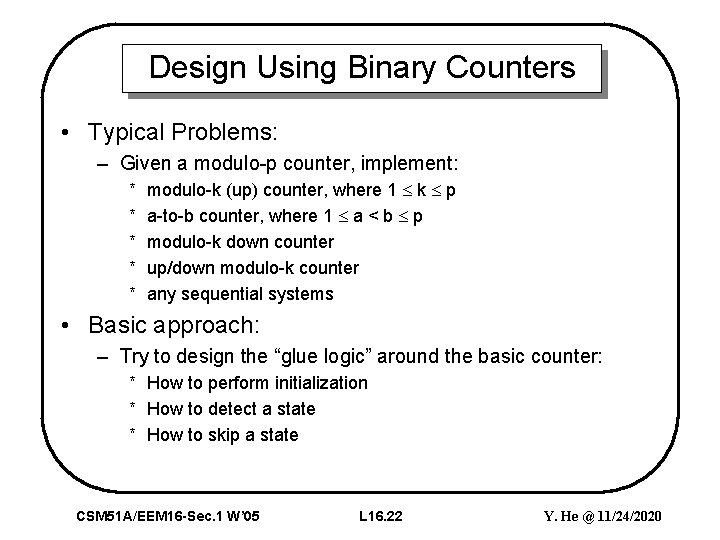

Design Using Binary Counters • Typical Problems: – Given a modulo-p counter, implement: * * * modulo-k (up) counter, where 1 k p a-to-b counter, where 1 a < b p modulo-k down counter up/down modulo-k counter any sequential systems • Basic approach: – Try to design the “glue logic” around the basic counter: * How to perform initialization * How to detect a state * How to skip a state CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 22 Y. He @ 11/24/2020

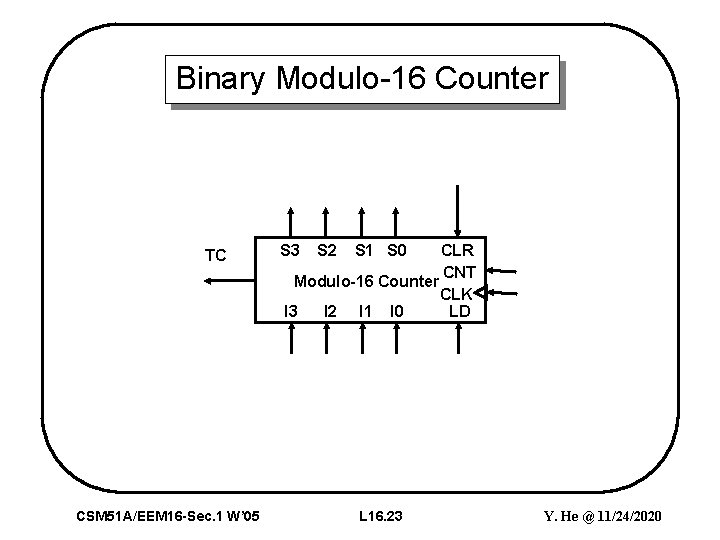

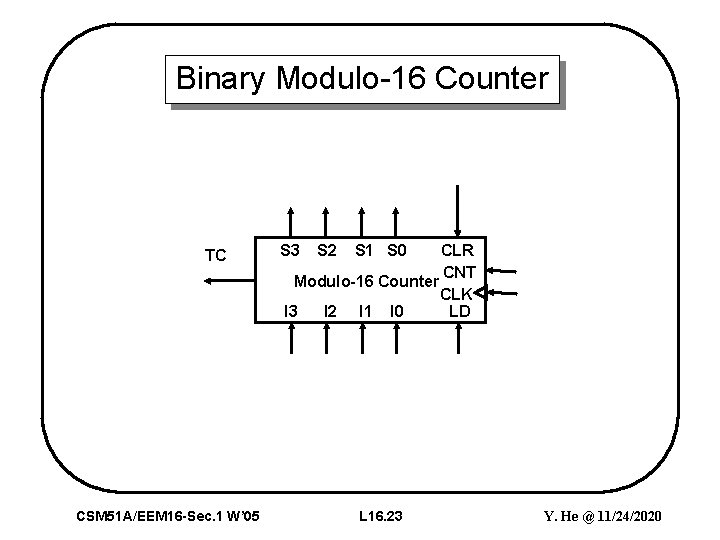

Binary Modulo-16 Counter TC CSM 51 A/EEM 16 -Sec. 1 W’ 05 CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 S 2 S 1 S 0 L 16. 23 Y. He @ 11/24/2020

Design with Modulo-16 Counter 4 • • s Modulo-16 Counter • x 4 I • • CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 24 Y. He @ 11/24/2020

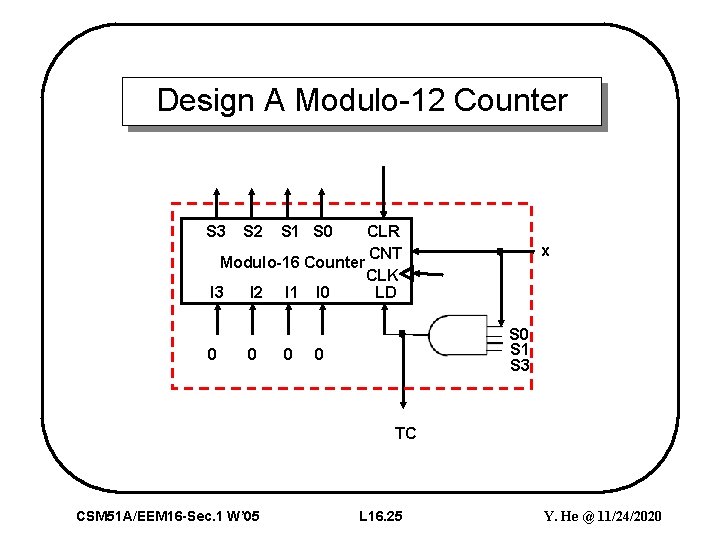

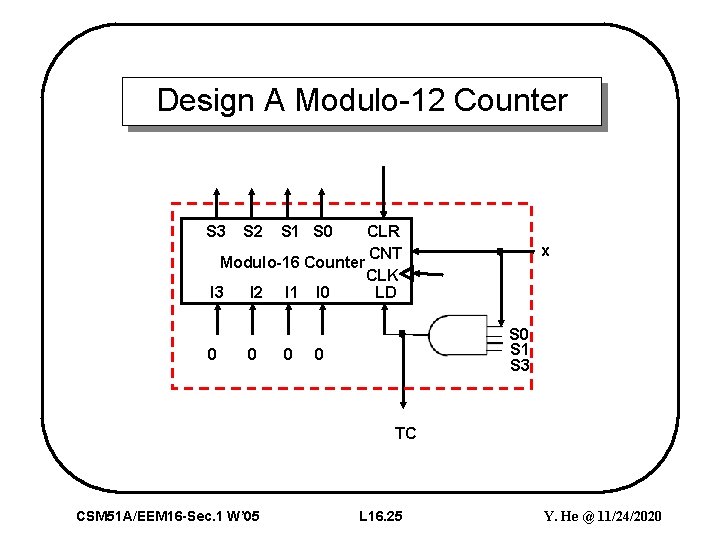

Design A Modulo-12 Counter CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 0 S 2 0 S 1 S 0 0 x S 0 S 1 S 3 0 TC CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 25 Y. He @ 11/24/2020

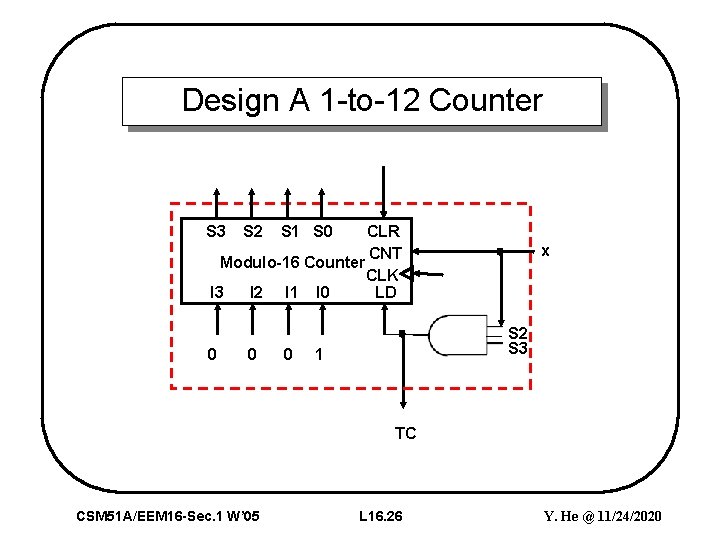

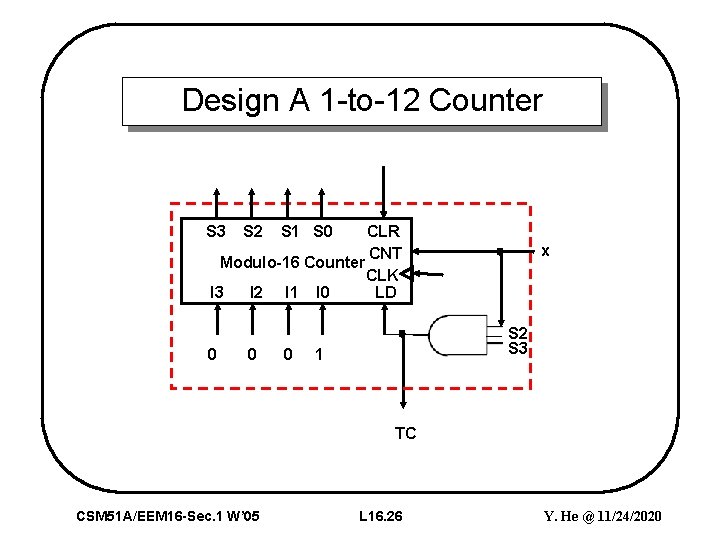

Design A 1 -to-12 Counter CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 0 S 2 0 S 1 S 0 0 x S 2 S 3 1 TC CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 26 Y. He @ 11/24/2020

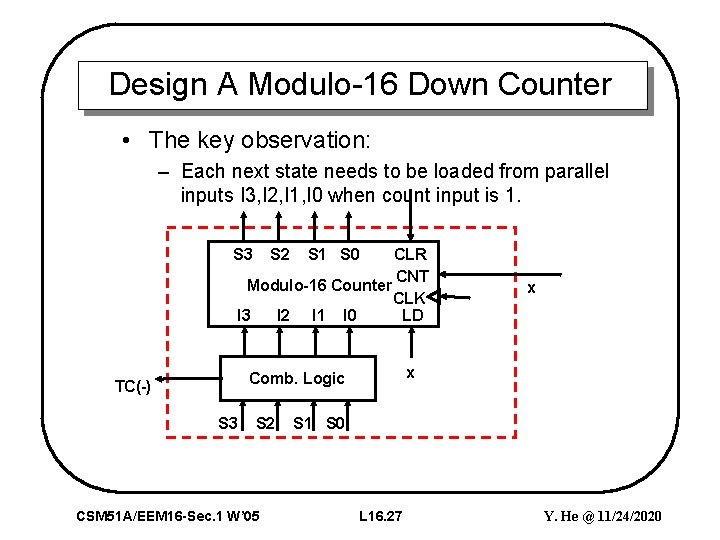

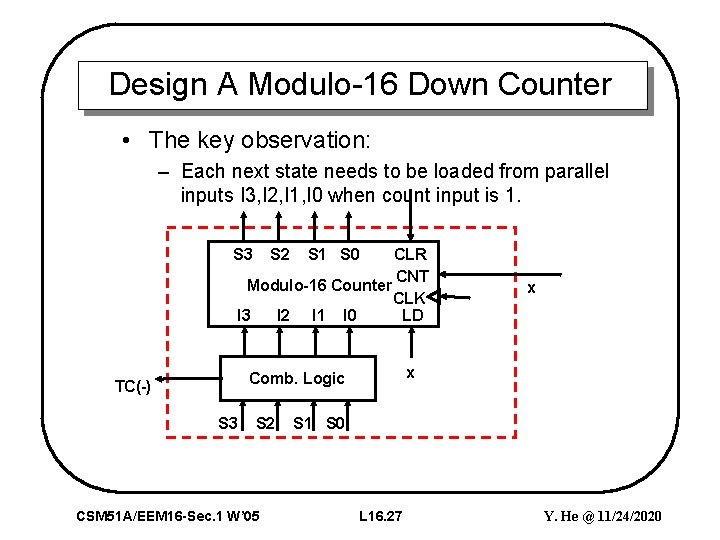

Design A Modulo-16 Down Counter • The key observation: – Each next state needs to be loaded from parallel inputs I 3, I 2, I 1, I 0 when count input is 1. CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 S 2 S 1 S 0 x Comb. Logic TC(-) S 3 S 2 CSM 51 A/EEM 16 -Sec. 1 W’ 05 x S 1 S 0 L 16. 27 Y. He @ 11/24/2020

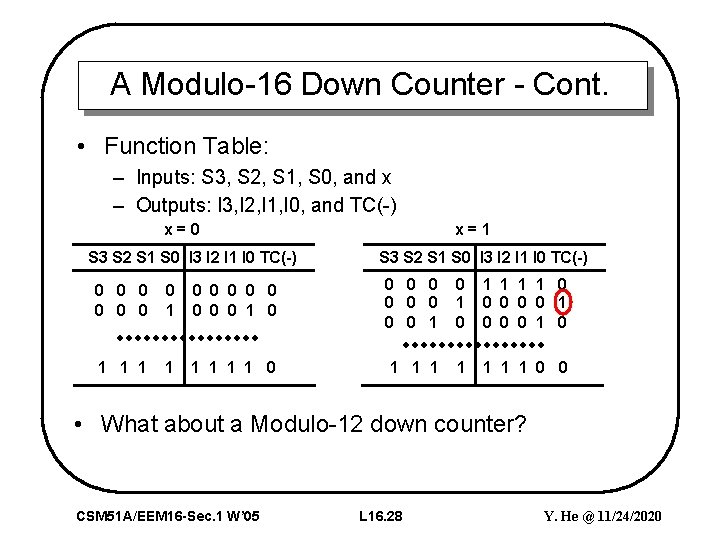

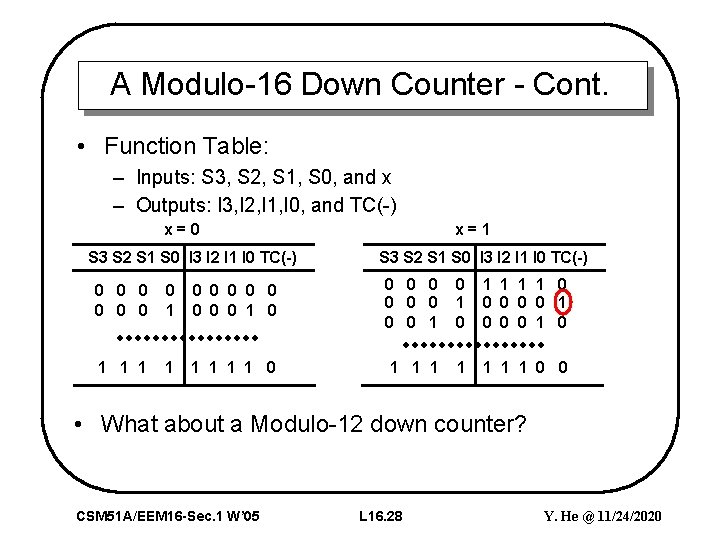

A Modulo-16 Down Counter - Cont. • Function Table: – Inputs: S 3, S 2, S 1, S 0, and x – Outputs: I 3, I 2, I 1, I 0, and TC(-) x=1 x=0 S 3 S 2 S 1 S 0 I 3 I 2 I 1 I 0 TC(-) 0 0 0 0 1 0 0 0 0 0 1 0 1 1 0 0 0 1 1 1 1 0 0 • What about a Modulo-12 down counter? CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 28 Y. He @ 11/24/2020

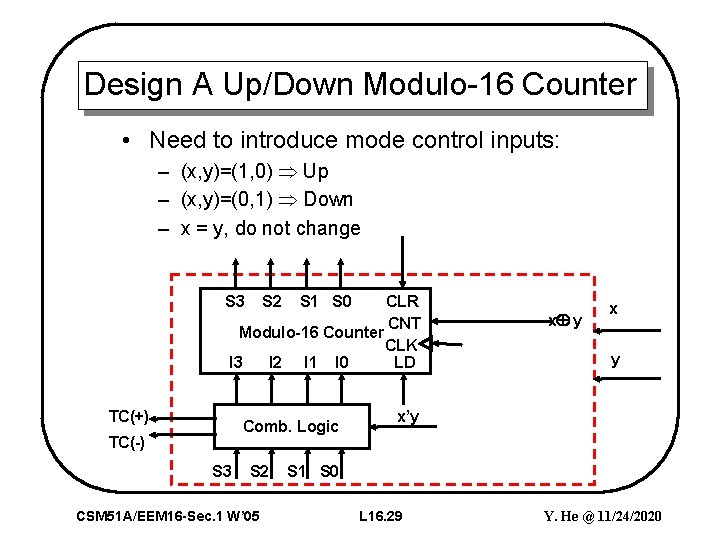

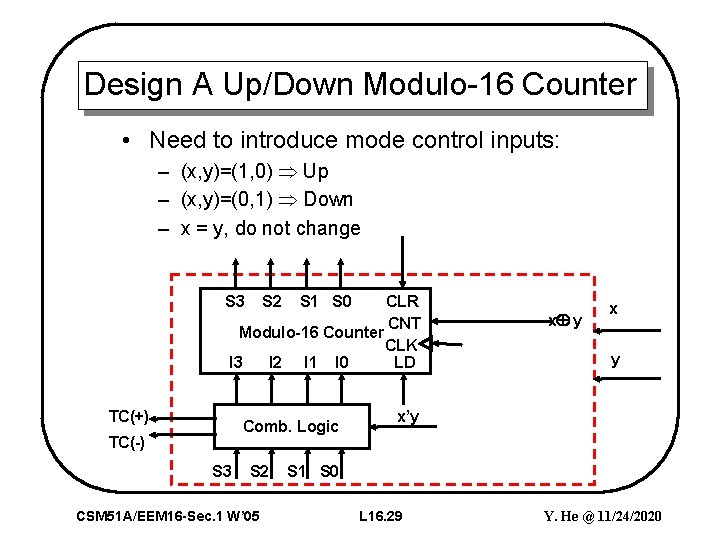

Design A Up/Down Modulo-16 Counter • Need to introduce mode control inputs: – (x, y)=(1, 0) Up – (x, y)=(0, 1) Down – x = y, do not change CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 TC(+) S 2 S 1 S 0 Comb. Logic TC(-) S 3 S 2 CSM 51 A/EEM 16 -Sec. 1 W’ 05 x y x’y S 1 S 0 L 16. 29 Y. He @ 11/24/2020

Design Any Sequential Systems • Key steps: – Obtain the transition tables – Design the combinational logic CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 30 Y. He @ 11/24/2020

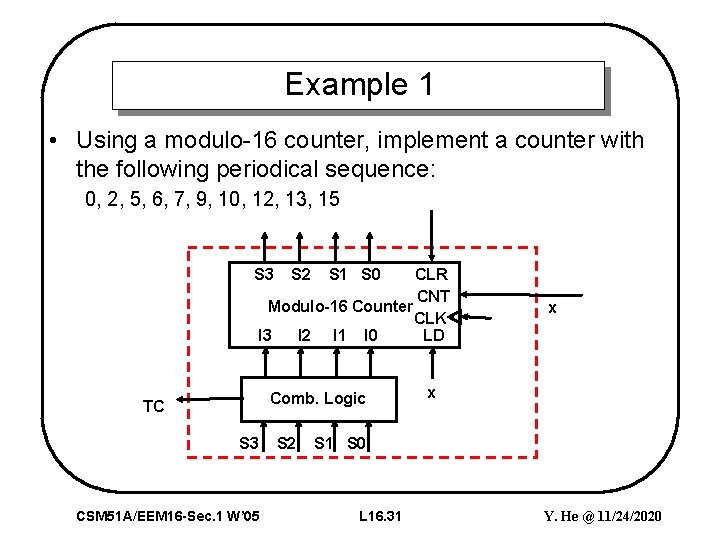

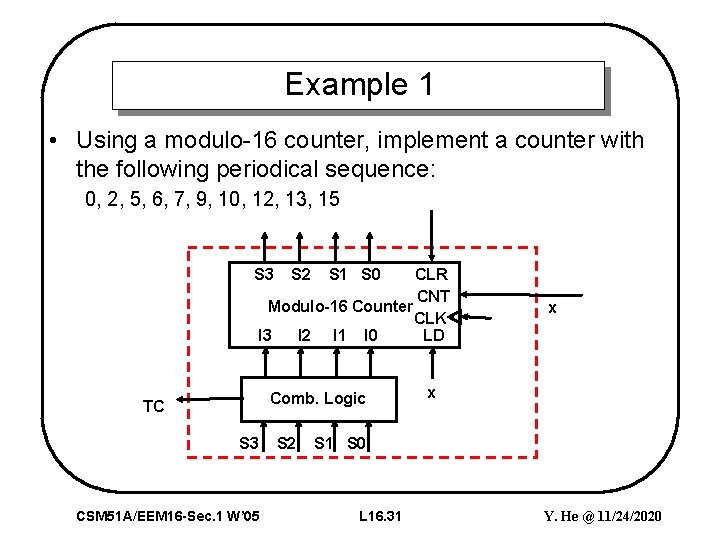

Example 1 • Using a modulo-16 counter, implement a counter with the following periodical sequence: 0, 2, 5, 6, 7, 9, 10, 12, 13, 15 CLR CNT Modulo-16 Counter CLK LD I 3 I 2 I 1 I 0 S 3 S 2 S 1 S 0 Comb. Logic TC S 3 CSM 51 A/EEM 16 -Sec. 1 W’ 05 S 2 x x S 1 S 0 L 16. 31 Y. He @ 11/24/2020

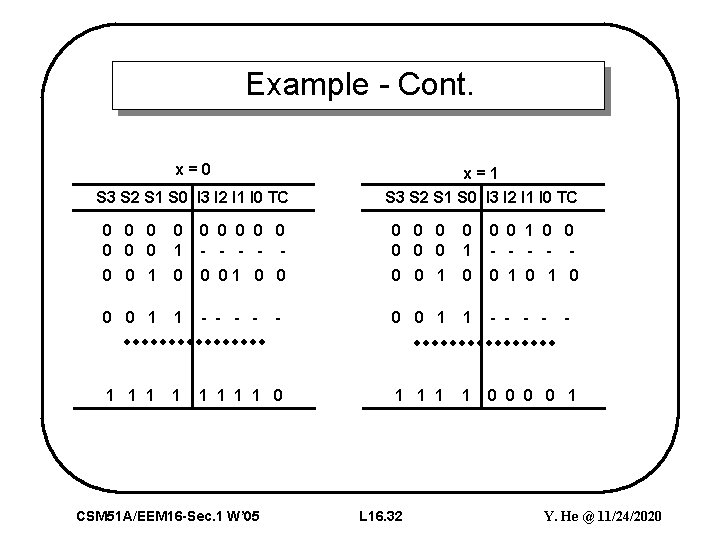

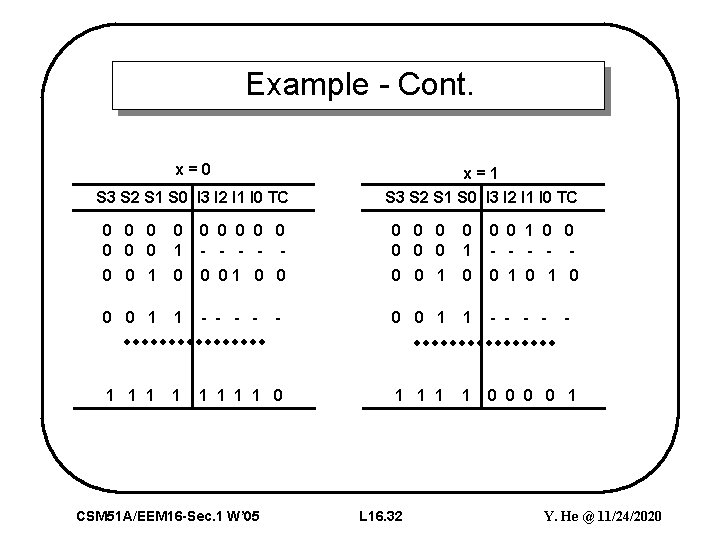

Example - Cont. x=0 x=1 S 3 S 2 S 1 S 0 I 3 I 2 I 1 I 0 TC 0 0 0 0 1 0 0 0 - - - 0 0 0 0 1 0 0 - - - 0 0 1 0 0 0 0 1 0 1 0 0 0 1 1 - - - 0 0 1 1 - - 1 1 1 1 0 0 1 CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 32 - Y. He @ 11/24/2020

Summary • Chapter 11 – Counter CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 33 Y. He @ 11/24/2020

Next Lecture • Chapter 12 - ROM • Final Review • Course Evaluation CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 16. 34 Y. He @ 11/24/2020