CS M 51 AEE M 16 Winter 05

- Slides: 33

CS M 51 A/EE M 16 Winter’ 05 Section 1 Logic Design of Digital Systems Lecture 1 January 10 W’ 05 Yutao He yutao@cs. ucla. edu 4532 B Boelter Hall http: //courseweb. seas. ucla. edu/class. View. php? term=05 W&srs=187154200 CSM 51 A/EEM 16 -Sec. 1 W’ 05 L 1. 1 Y. He @ 10/26/2021

Outline • Welcome • Chapter 1 - Class Overview • Summary CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 2 Y. He @ 10/26/2021

Why Are We Here? • Because the computer is everywhere! Welcome to the class! CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 3 Y. He @ 10/26/2021

Course Administration • • • Instructor: Yutao He (yutao@cs. ucla. edu) Office Hours: MW 6 -7 pm (4750 BH) TA: Kenneth Leung (kyleung@ucla. edu) Office Hours: TTh 1 -2 pm (4428 BH) Textbook: Introduction to Digital Systems by Ercegovac, Lang, and Moreno John Wiley & Sons, 1999 • Course Website: – http: //courseweb. seas. ucla. edu/class. View. php? term=05 W&srs=187154200 CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 4 Y. He @ 10/26/2021

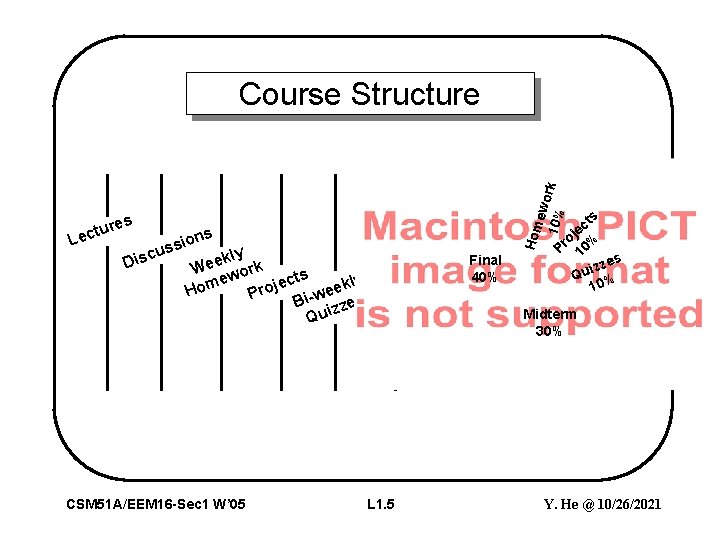

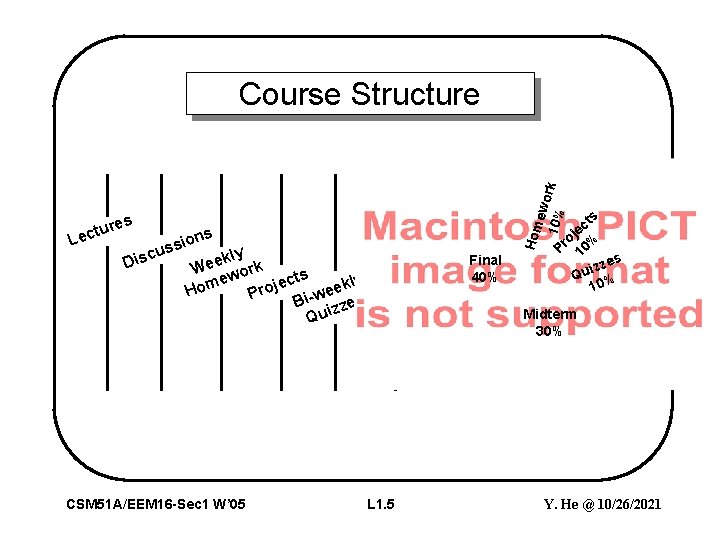

res u t c ns Le o i s cus s i ekly k D e W wor e cts e m kly j e o o e H Pr Bi-w zzes rm, e t Qui Mid al Fin CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 5 Hom ewo 10% rk Course Structure Final 40% s ct e oj % r P 10 zes z i Qu % 10 Midterm 30% Y. He @ 10/26/2021

Homework • • • Available on-line every Monday before the class Due at 4 pm on the following Monday Drop off in the class mailbox in Room 4428 BH Each homework hand-in should attach a cover sheet Solution is available on-line Tuesday 9 Homework in total CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 6 Y. He @ 10/26/2021

Quizzes • • To get you acquainted with Midterm and Final To have you keep up with the class progress 3 quizzes in total Given every two weeks at the end of Friday session Closed-book and Closed-note 30 minutes Test class materials covered in the past two weeks CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 7 Y. He @ 10/26/2021

Projects • To get hands-on experiences on current industry practice (EDA tools dominated) • 2 or 3 small projects • Design simple digital systems in VHDL • Use the Altera MAX+PLUS II toolkit • May team up with your fellow classmates • SEASNET accounts are required unless you have PC at home CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 8 Y. He @ 10/26/2021

Midterm and Final • Goal is to test knowledge not to test speed writing • Midterm – Date: 2 -3: 50 pm Friday, February 18 – Location: in the lecture room – Closed-book/Closed-note but allows a cheat-sheet • Final – Date: 8 -11 am Monday, March 18 – Location: TBD – Closed-book/Closed-note but allows a cheat-sheet CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 9 Y. He @ 10/26/2021

Academic Integrity • Studying in groups is encouraged • Actual work must be your own PLAGIARISM • Common cheating scenarios: – running out of time on an assignment and then cut-andpaste from your buddy’s work – cross-talking and cross-eyeing during exams • Will be reported to Dean’s Office if catch any violation CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 10 Y. He @ 10/26/2021

Course Problems • Can’t make quizzes or exams – should ask for permission ahead of time – the score would be zero unless some unexpected emergencies • Forget to turn in homework or your pet dog ate it – Only one time is allowed CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 11 Y. He @ 10/26/2021

Course Protocols • • Please do not have small talk Please do not read newspapers Please do not wear the headphone Please put your cell phone in a non-disturbing mode Sleep is ok as long as you make sure not to snore Quiet food is allowed Don’t be shy to ask any questions occur to your mind – Don’t get intimidated if some fellow students happen to know better than you in the beginning – That’s why you take the class CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 12 Y. He @ 10/26/2021

What You Need to Do Well • You have common sense – There are 12 months in a year • You can count properly – 1+1 = ? • You can do logic reasoning – if I miss one lecture, then I’ll fail the class • You have the positive motivation – I’ll shoot for an A+ • You know how to work smart CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 13 Y. He @ 10/26/2021

What We will Learn • Language of logic design – Boolean algebra, logic minimization, state, timing, CAD tools • Concept of state in digital systems – Analogous to variables in software systems • How to design/analysis digital systems • Contrast with software design – Both map well-posed problems to physical devices – Both must be flawless CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 14 Y. He @ 10/26/2021

Applications of Logic Design • Conventional computer design – CPUs, memories, busses, peripherals • Networking and communications – Phones, modems, NICs, routers • Embedded products – Cars, PDAs, entertainment devices • Scientific equipments – Testing, measuring, sensing, reporting • World of computing much bigger than just PCs! CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 15 Y. He @ 10/26/2021

A Brief Historic Flashback • 1850: George Boole invents Boolean algebra – Maps logical propositions to symbols – Permits manipulation of logic statements using mathematics • 1938: Claude Shannon links Boolean algebra to switches – His Masters’ thesis • 1945: John von Neumann develops first stored program computer – Its switching elements are vacuum tubes • 1947: Shockley, Brittain, and Bardeen invent the transistor – enable integration of multiple devices into one package – gateway to modern electronics CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 16 Y. He @ 10/26/2021

Follow-on Courses • CS 152 A (Lab) • CS 151 B (Computer Architecture) • CS 152 B (Lab) CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 17 Y. He @ 10/26/2021

Questionnaire • Help us better know your background and thus teach the course more effectively. CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 18 Y. He @ 10/26/2021

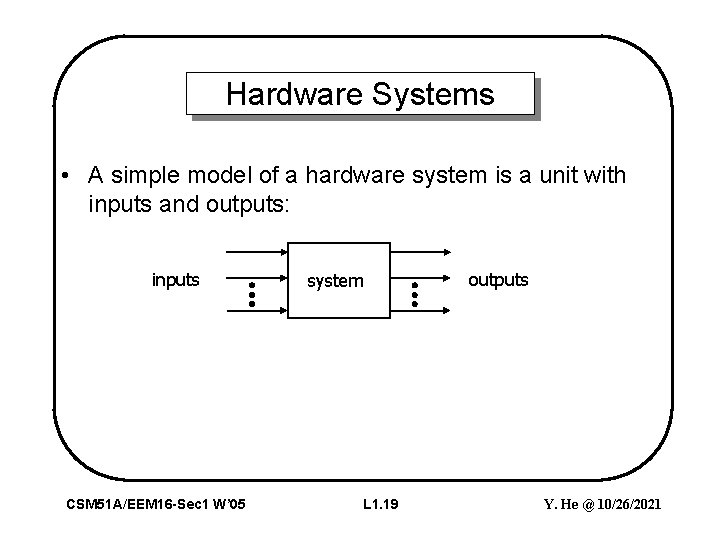

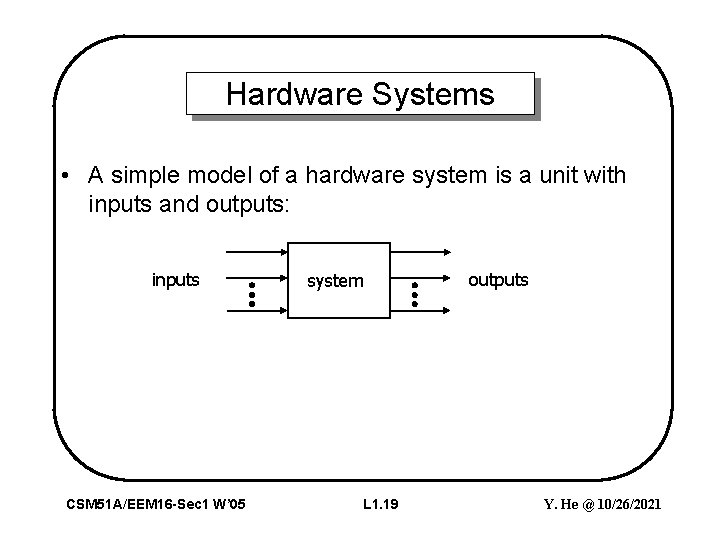

Hardware Systems • A simple model of a hardware system is a unit with inputs and outputs: inputs CSM 51 A/EEM 16 -Sec 1 W’ 05 system L 1. 19 outputs Y. He @ 10/26/2021

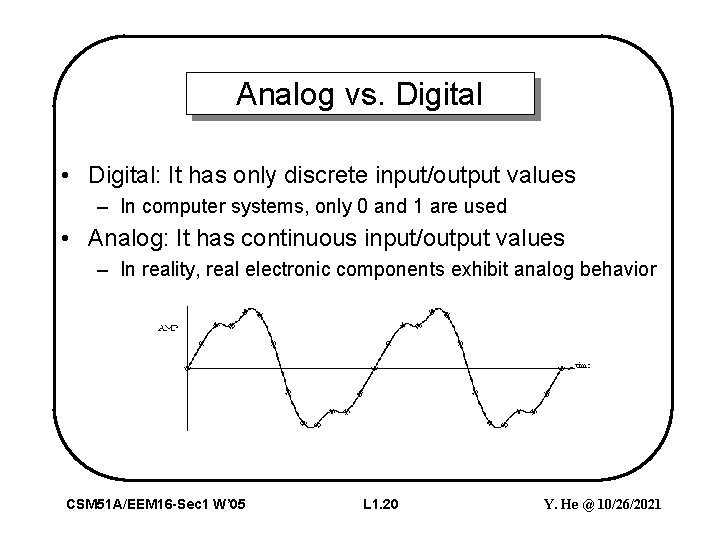

Analog vs. Digital • Digital: It has only discrete input/output values – In computer systems, only 0 and 1 are used • Analog: It has continuous input/output values – In reality, real electronic components exhibit analog behavior CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 20 Y. He @ 10/26/2021

Combinational vs. Sequential • Combinational: – a digital circuit is combinational if its current output values only depend on its current input values – means "memory-less” – AND, OR gates • Sequential: – Exhibit behaviors (output values) that depend not only on the current input values, but also on previous input values – In reality, all circuits are sequential CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 21 Y. He @ 10/26/2021

Synchronous vs. Asynchronous • Synchronous: – The outputs can only change at prescribed time instant • Asynchronous: – The outputs can change at any time instant CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 22 Y. He @ 10/26/2021

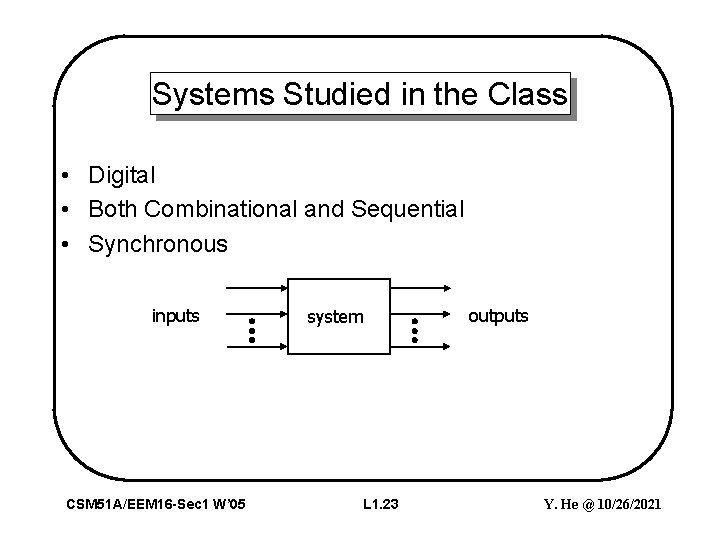

Systems Studied in the Class • Digital • Both Combinational and Sequential • Synchronous inputs CSM 51 A/EEM 16 -Sec 1 W’ 05 system L 1. 23 outputs Y. He @ 10/26/2021

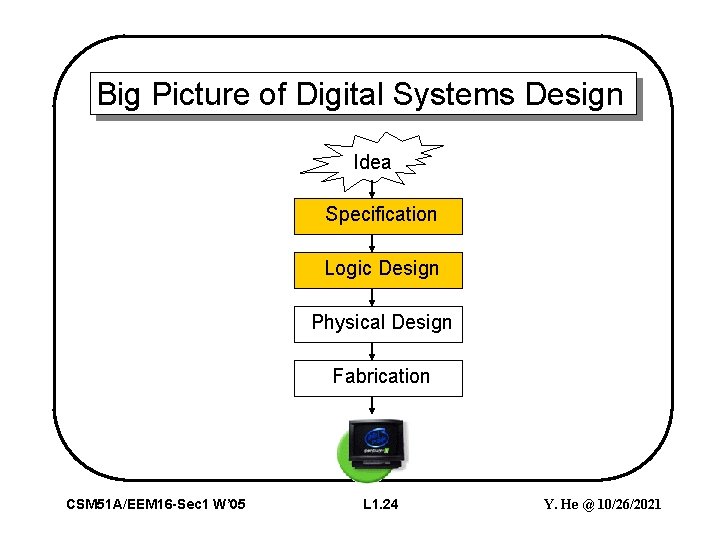

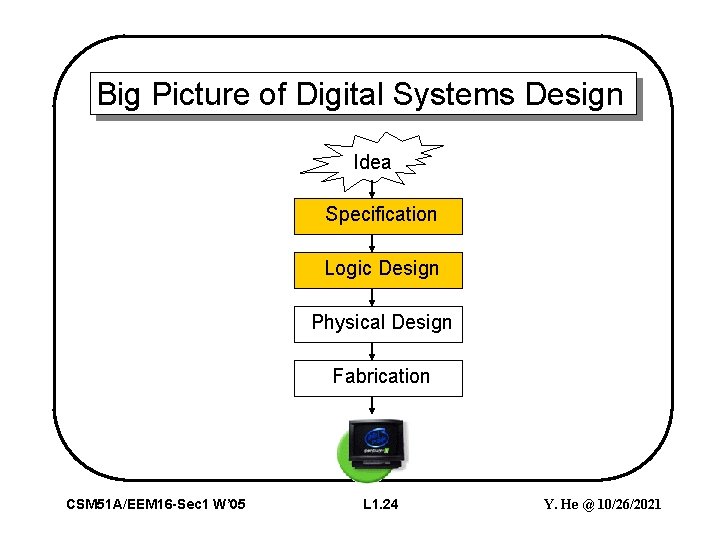

Big Picture of Digital Systems Design Idea Specification Logic Design Physical Design Fabrication CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 24 Y. He @ 10/26/2021

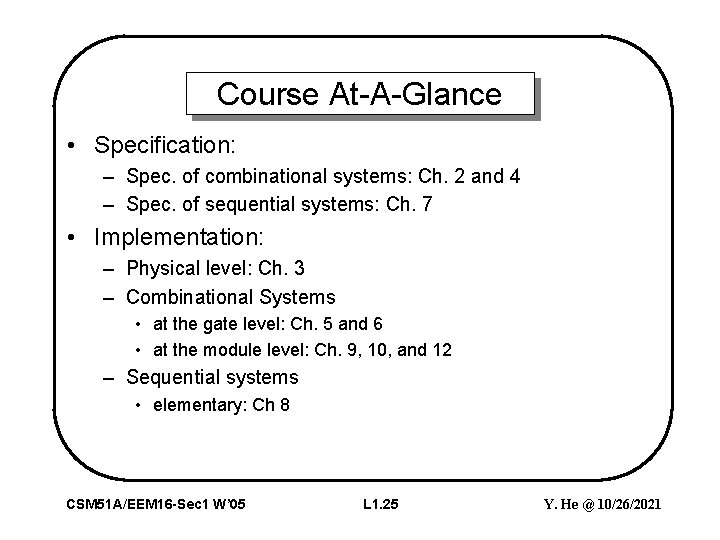

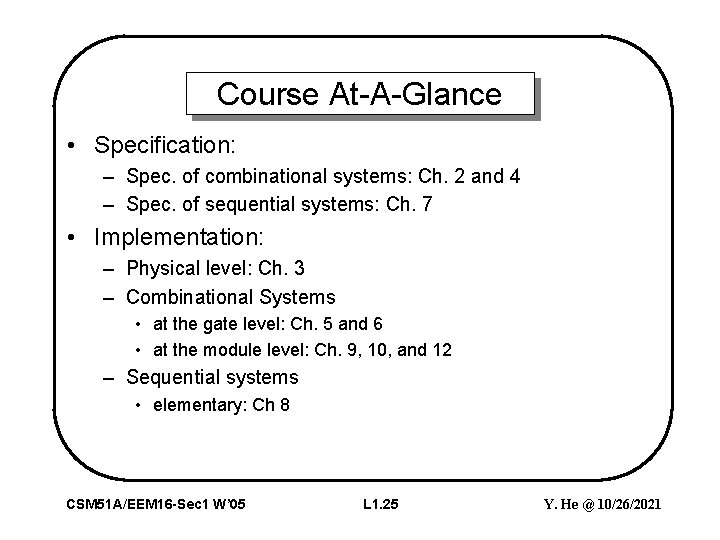

Course At-A-Glance • Specification: – Spec. of combinational systems: Ch. 2 and 4 – Spec. of sequential systems: Ch. 7 • Implementation: – Physical level: Ch. 3 – Combinational Systems • at the gate level: Ch. 5 and 6 • at the module level: Ch. 9, 10, and 12 – Sequential systems • elementary: Ch 8 CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 25 Y. He @ 10/26/2021

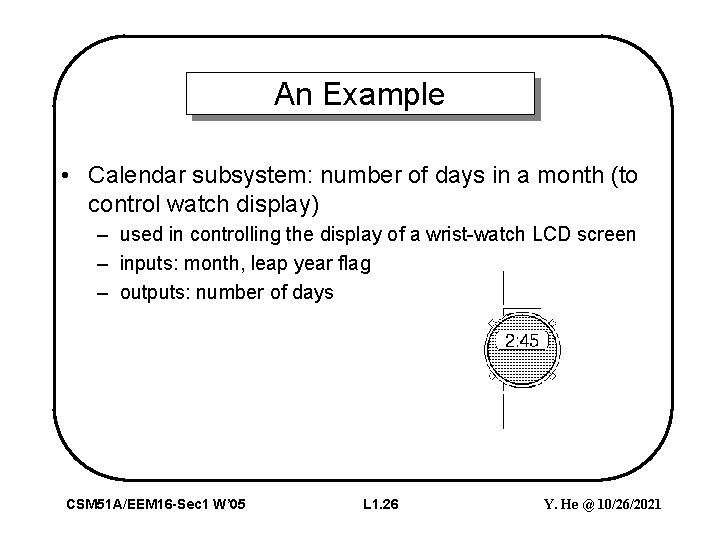

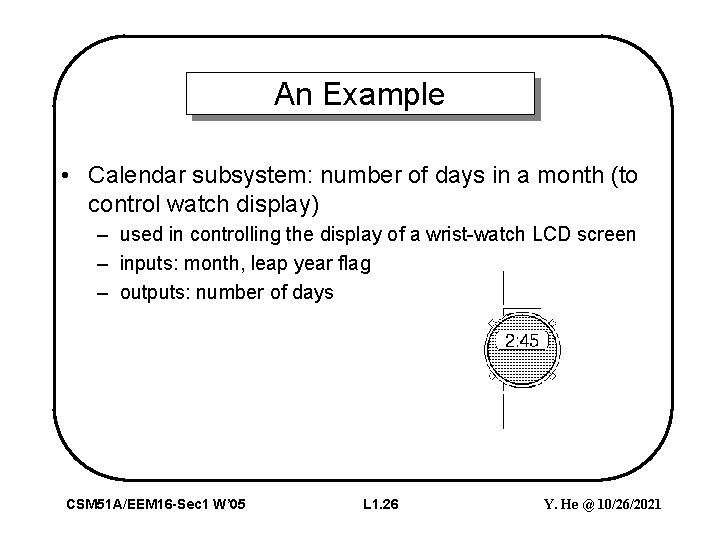

An Example • Calendar subsystem: number of days in a month (to control watch display) – used in controlling the display of a wrist-watch LCD screen – inputs: month, leap year flag – outputs: number of days CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 26 Y. He @ 10/26/2021

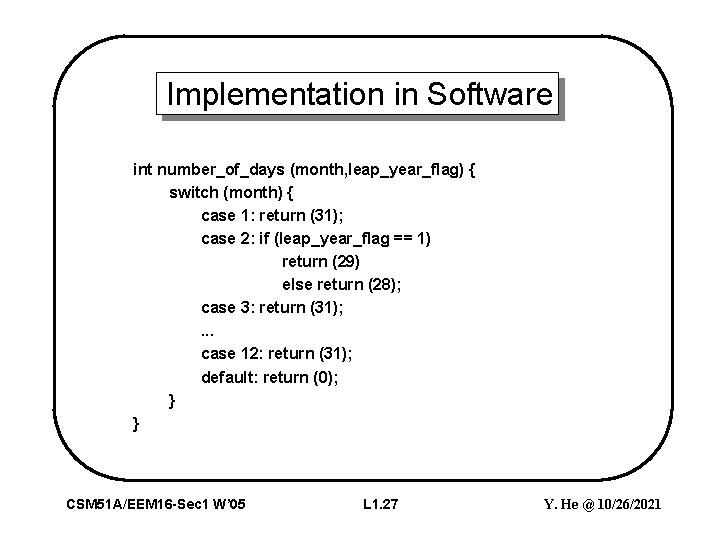

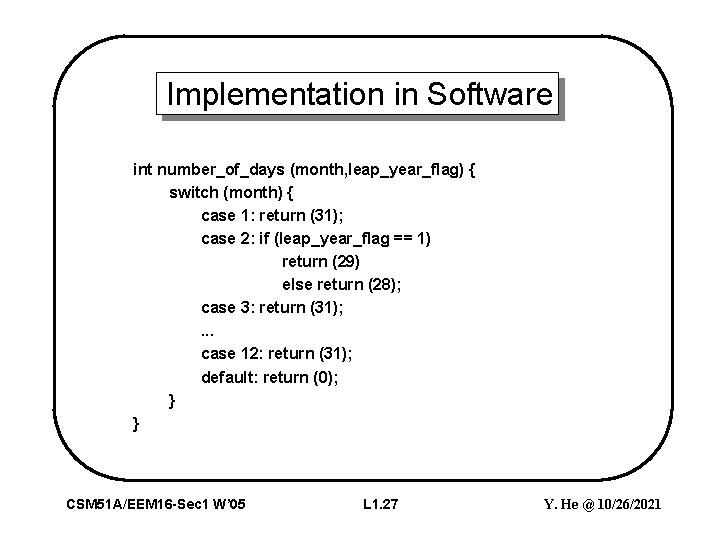

Implementation in Software int number_of_days (month, leap_year_flag) { switch (month) { case 1: return (31); case 2: if (leap_year_flag == 1) return (29) else return (28); case 3: return (31); . . . case 12: return (31); default: return (0); } } CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 27 Y. He @ 10/26/2021

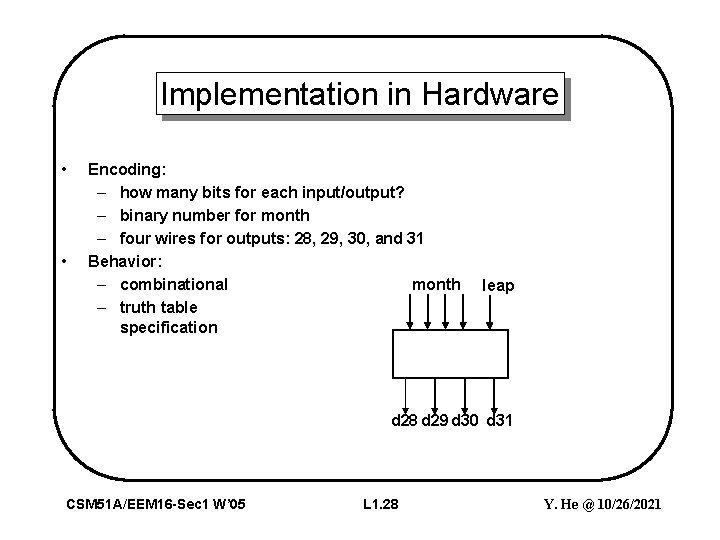

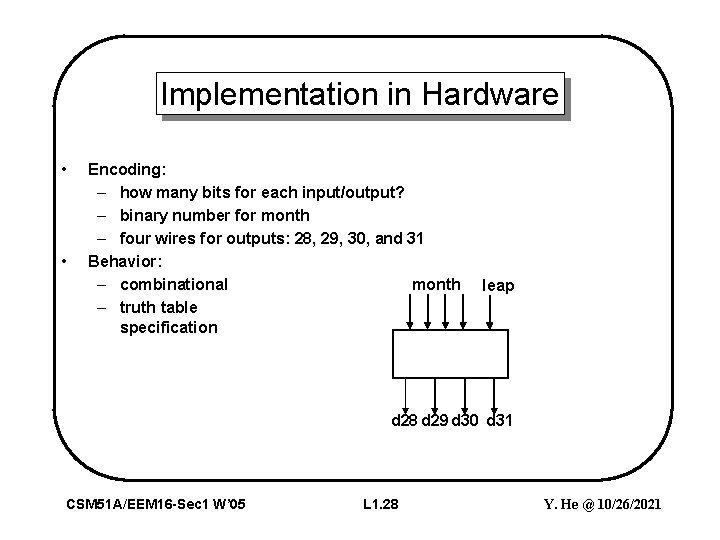

Implementation in Hardware • • Encoding: – how many bits for each input/output? – binary number for month – four wires for outputs: 28, 29, 30, and 31 Behavior: month – combinational – truth table specification leap d 28 d 29 d 30 d 31 CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 28 Y. He @ 10/26/2021

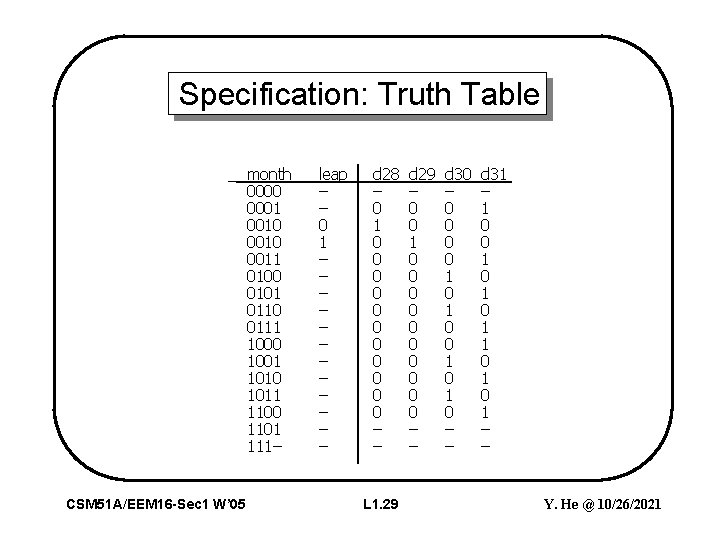

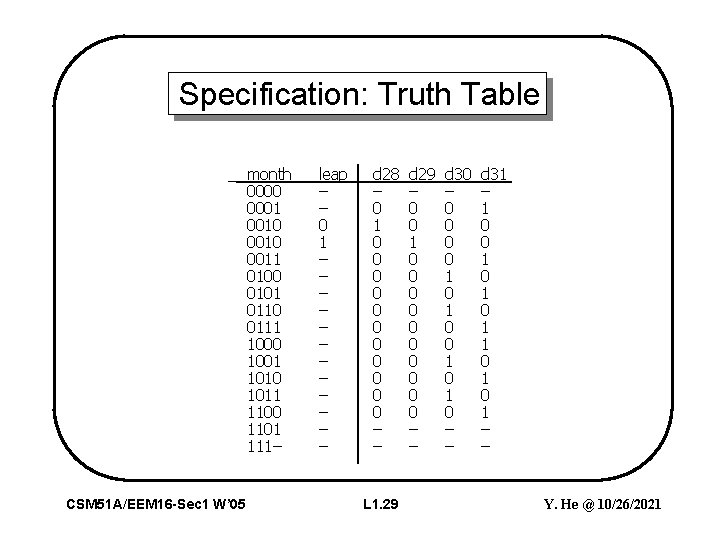

Specification: Truth Table month 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 111– CSM 51 A/EEM 16 -Sec 1 W’ 05 leap – – 0 1 – – – d 28 – 0 1 0 0 0 – – L 1. 29 d 29 – 0 0 1 0 0 0 0 0 – – d 30 – 0 0 1 0 – – d 31 – 1 0 0 1 0 1 – – Y. He @ 10/26/2021

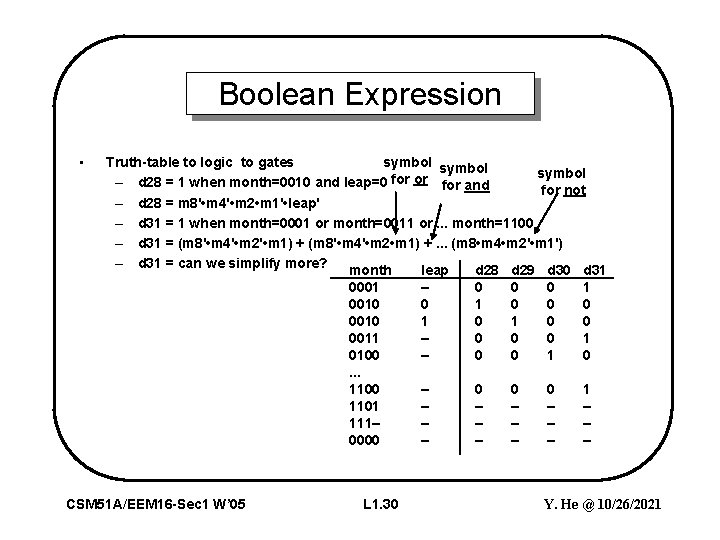

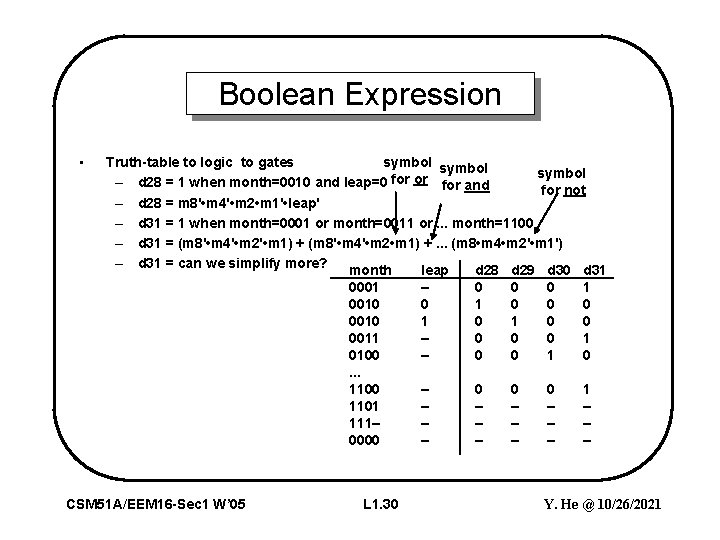

Boolean Expression • symbol Truth-table to logic to gates symbol – d 28 = 1 when month=0010 and leap=0 for or for and for not – d 28 = m 8' • m 4' • m 2 • m 1' • leap' – d 31 = 1 when month=0001 or month=0011 or. . . month=1100 – d 31 = (m 8' • m 4' • m 2' • m 1) + (m 8' • m 4' • m 2 • m 1) +. . . (m 8 • m 4 • m 2' • m 1') – d 31 = can we simplify more? month leap d 28 d 29 d 30 d 31 0001 – 0 0 0 1 0010 0 1 0 0010 1 0 0 0011 – 0 0 0 1 0100 – 0 0 1 0. . . 1100 – 0 0 0 1 1101 – – – 111– – – 0000 – – – CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 30 Y. He @ 10/26/2021

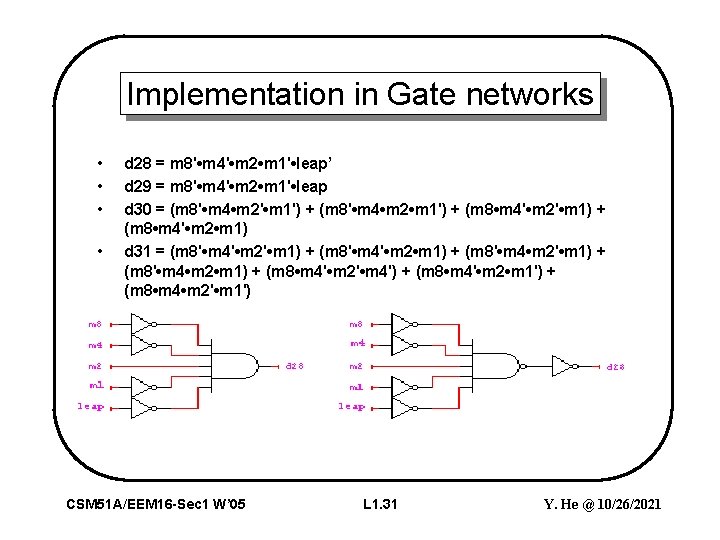

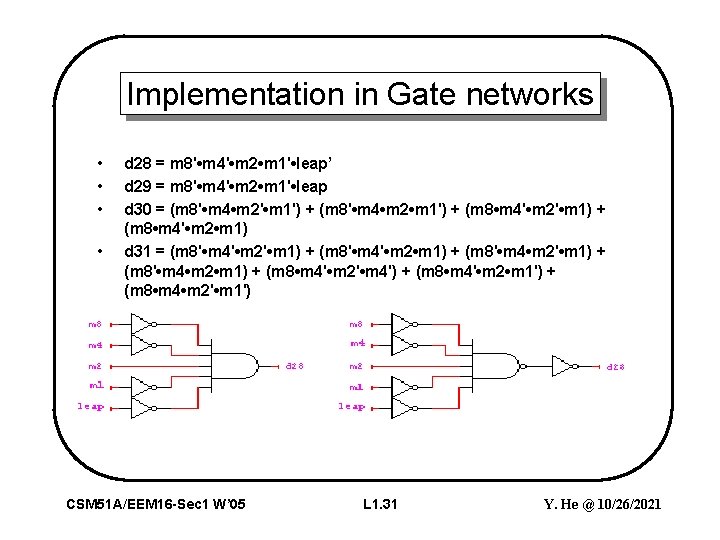

Implementation in Gate networks • • d 28 = m 8' • m 4' • m 2 • m 1' • leap’ d 29 = m 8' • m 4' • m 2 • m 1' • leap d 30 = (m 8' • m 4 • m 2' • m 1') + (m 8' • m 4 • m 2 • m 1') + (m 8 • m 4' • m 2' • m 1) + (m 8 • m 4' • m 2 • m 1) d 31 = (m 8' • m 4' • m 2' • m 1) + (m 8' • m 4' • m 2 • m 1) + (m 8' • m 4 • m 2' • m 1) + (m 8' • m 4 • m 2 • m 1) + (m 8 • m 4' • m 2' • m 4') + (m 8 • m 4' • m 2 • m 1') + (m 8 • m 4 • m 2' • m 1') CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 31 Y. He @ 10/26/2021

Summary • That was what the entire course is all about – Converting solutions to problems into combinational and sequential networks effectively – Organizing the design hierarchically and systematically – Taking advantage of optimization opportunities – Analyze a digital system • Now let us do it again – This time we'll take the rest of the quarter! CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 32 Y. He @ 10/26/2021

Next Lecture • Section 2. 3 - Data Representation and Coding • Class Note #1 CSM 51 A/EEM 16 -Sec 1 W’ 05 L 1. 33 Y. He @ 10/26/2021