Chapter Five The Processor Datapath and Control Mario

![Register File (e Memória) Register File: built out D-FF Memória: • acesso Mem[addr] RD Register File (e Memória) Register File: built out D-FF Memória: • acesso Mem[addr] RD](https://slidetodoc.com/presentation_image_h2/e24867c9810ae3d13a3f919cecd92f42/image-5.jpg)

![Adicionando a instrução jump Instruction [25– 0] 26 Shift left 2 Jump address [31– Adicionando a instrução jump Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/e24867c9810ae3d13a3f919cecd92f42/image-24.jpg)

- Slides: 26

Chapter Five The Processor: Datapath and Control Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-1

The Processor: Datapath & Control • • We're ready to look at an implementation of the MIPS Simplified to contain only: – memory-reference instructions: lw, sw – arithmetic-logical instructions: add, sub, and, or, slt – control flow instructions: beq, j • Não implementadas: mult, div, jal, fp • Generic Implementation: – – • use the program counter (PC) to supply instruction address get the instruction from memory read registers use the instruction to decide exactly what to do All instructions use the ALU after reading the registers: – memory-reference (sw lw), arithmetic, control flow Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-2

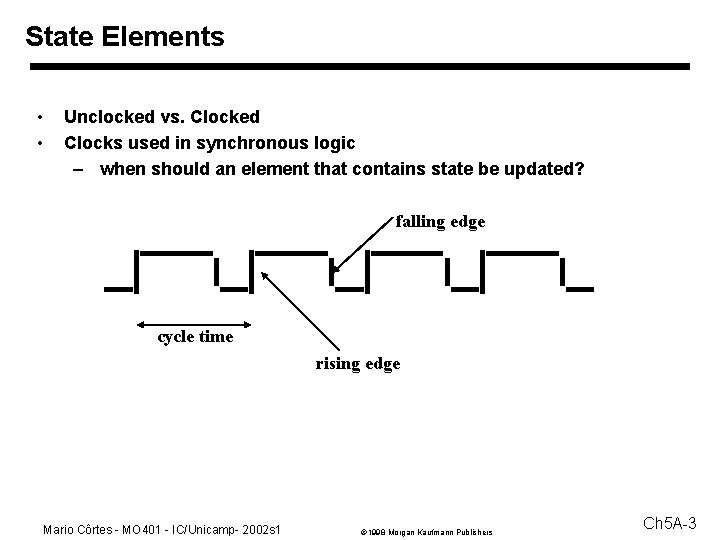

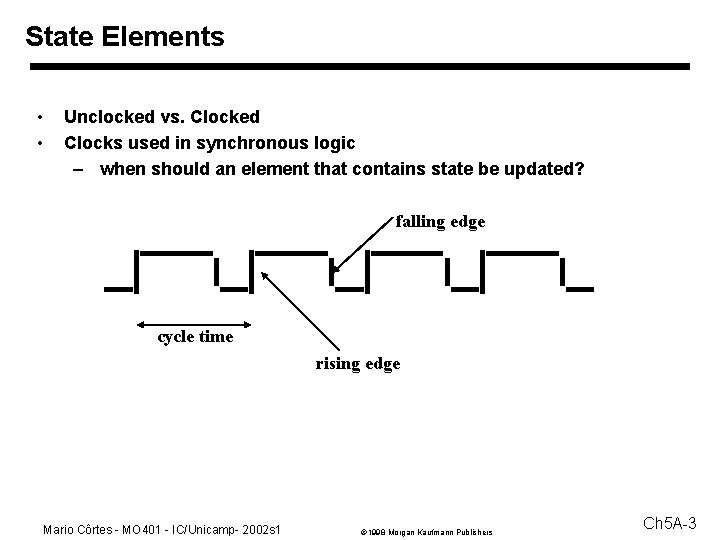

State Elements • • Unclocked vs. Clocked Clocks used in synchronous logic – when should an element that contains state be updated? falling edge cycle time rising edge Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-3

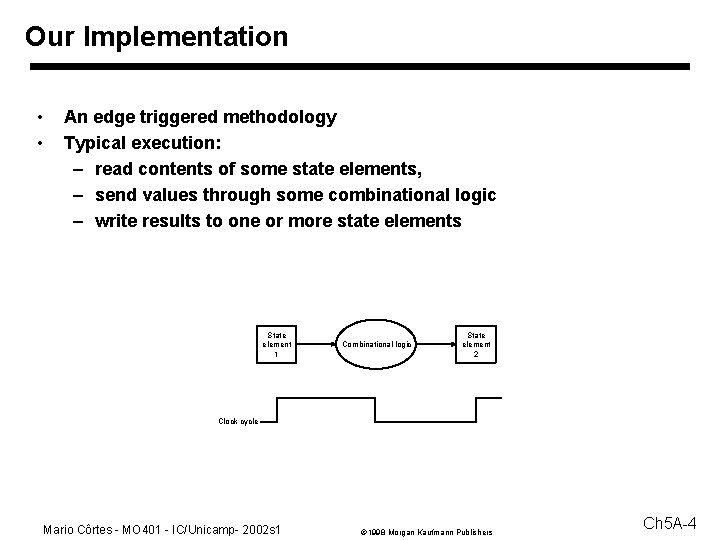

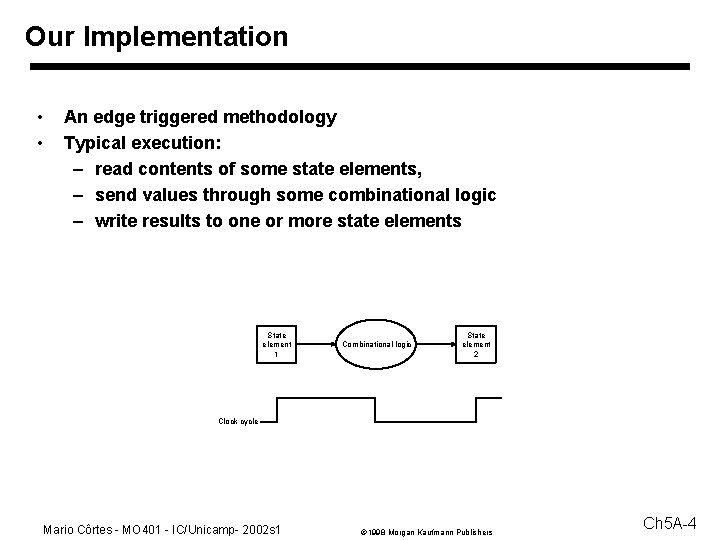

Our Implementation • • An edge triggered methodology Typical execution: – read contents of some state elements, – send values through some combinational logic – write results to one or more state elements State element 1 Combinational logic State element 2 Clock cycle Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-4

![Register File e Memória Register File built out DFF Memória acesso Memaddr RD Register File (e Memória) Register File: built out D-FF Memória: • acesso Mem[addr] RD](https://slidetodoc.com/presentation_image_h2/e24867c9810ae3d13a3f919cecd92f42/image-5.jpg)

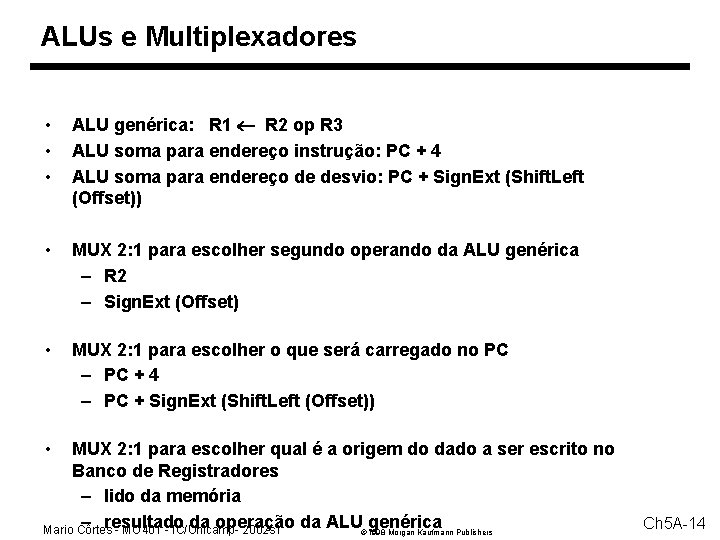

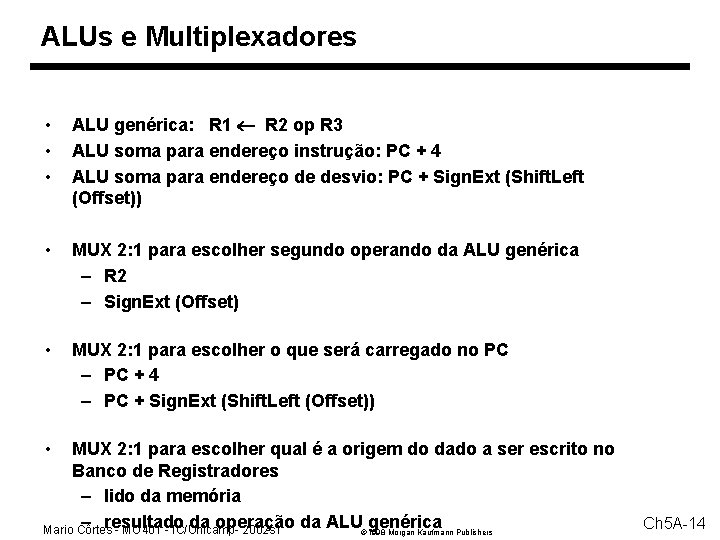

Register File (e Memória) Register File: built out D-FF Memória: • acesso Mem[addr] RD WR Dados Endereço Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-5

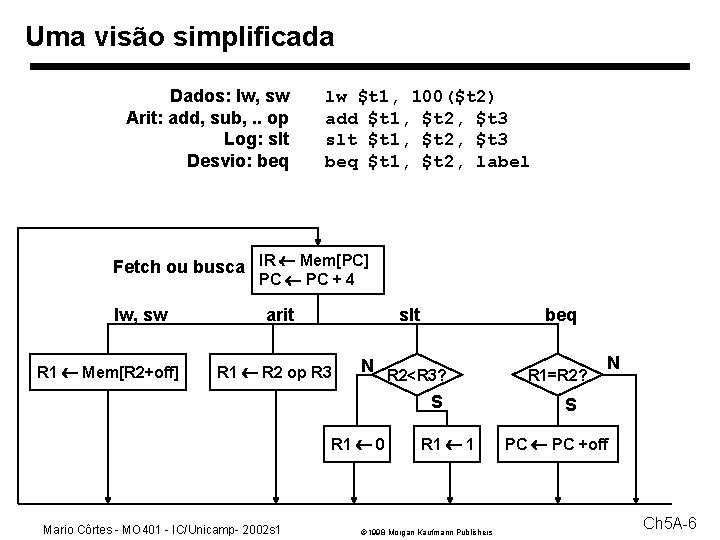

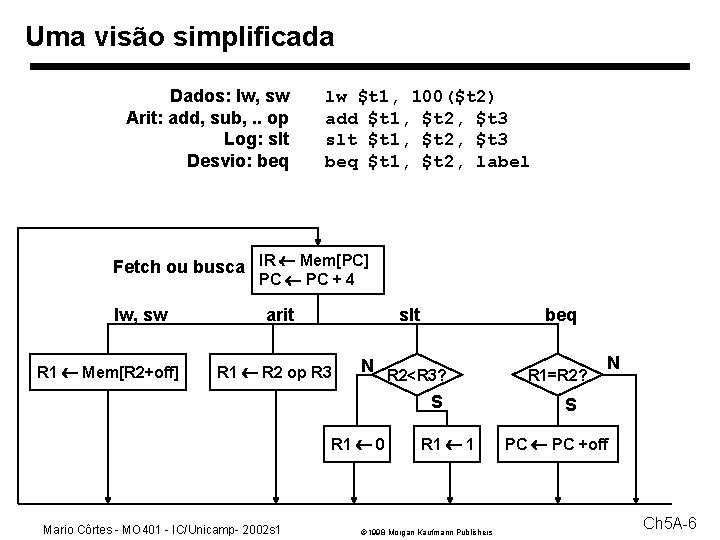

Uma visão simplificada Dados: lw, sw Arit: add, sub, . . op Log: slt Desvio: beq lw $t 1, 100($t 2) add $t 1, $t 2, $t 3 slt $t 1, $t 2, $t 3 beq $t 1, $t 2, label Fetch ou busca IR Mem[PC] PC + 4 lw, sw R 1 Mem[R 2+off] arit slt R 1 R 2 op R 3 beq N R 2<R 3? S R 1 0 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 R 1 1 1998 Morgan Kaufmann Publishers R 1=R 2? N S PC +off Ch 5 A-6

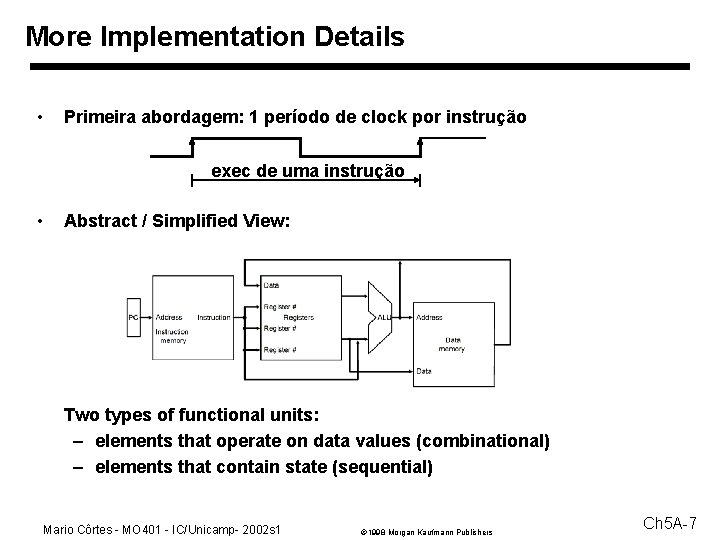

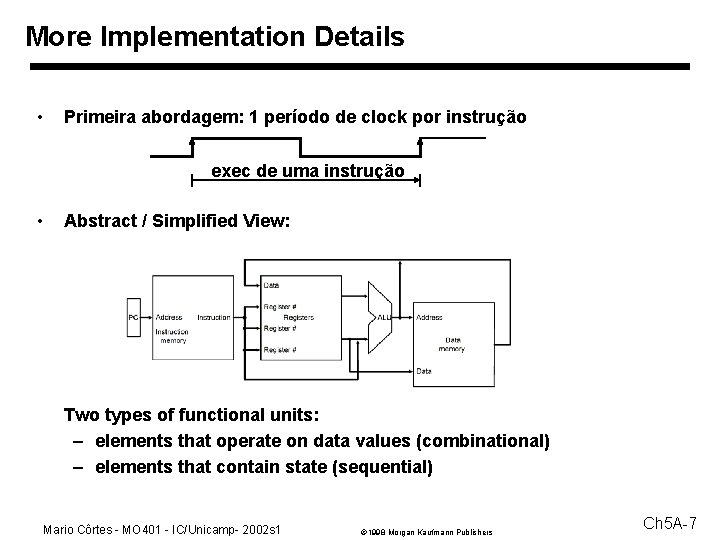

More Implementation Details • Primeira abordagem: 1 período de clock por instrução exec de uma instrução • Abstract / Simplified View: Two types of functional units: – elements that operate on data values (combinational) – elements that contain state (sequential) Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-7

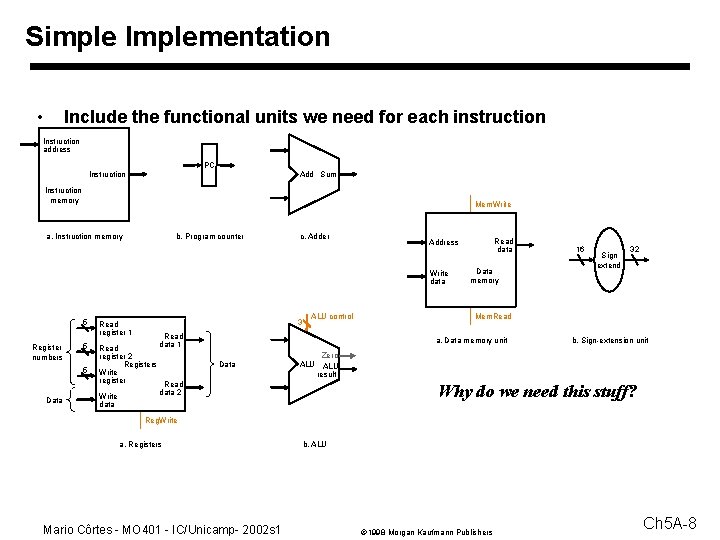

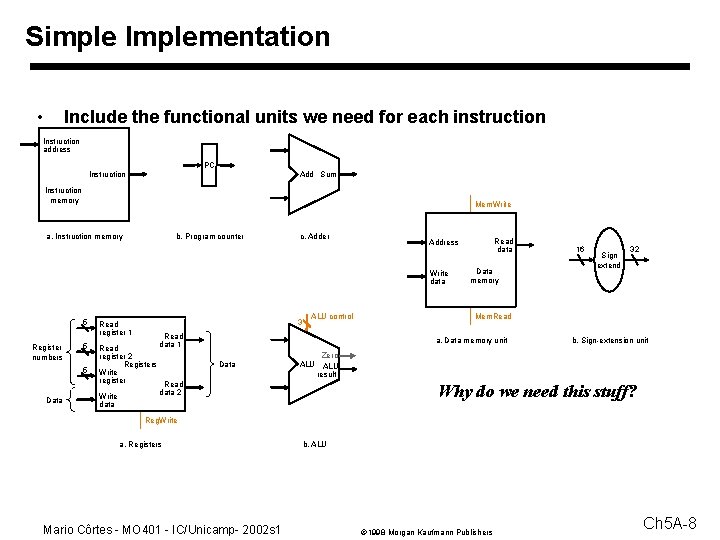

Simple Implementation • Include the functional units we need for each instruction Instruction address PC Instruction Add Sum Instruction memory Mem. Write a. Instruction memory b. Program counter c. Adder Write data 5 Register numbers 5 5 Data 3 Read register 1 Read data 1 Read register 2 Registers Write register Read data 2 Write data ALU control Read data Address Data memory Sign extend 32 Mem. Read a. Data memory unit Data 16 b. Sign-extension unit Zero ALU result Why do we need this stuff? Reg. Write a. Registers Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 b. ALU 1998 Morgan Kaufmann Publishers Ch 5 A-8

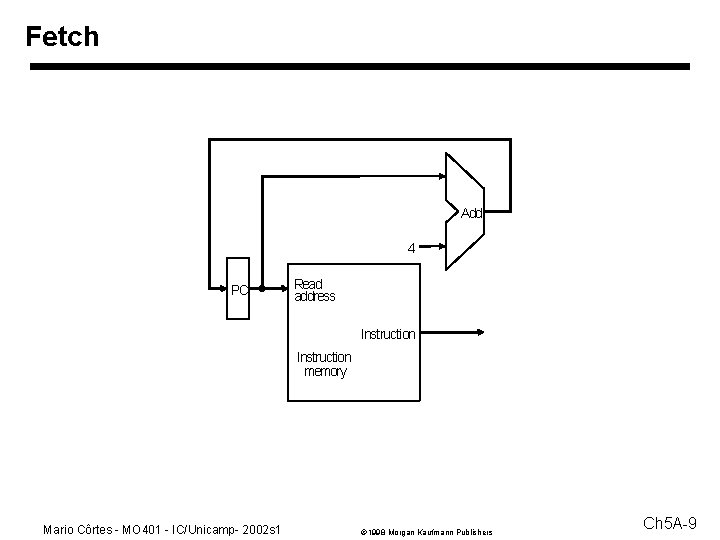

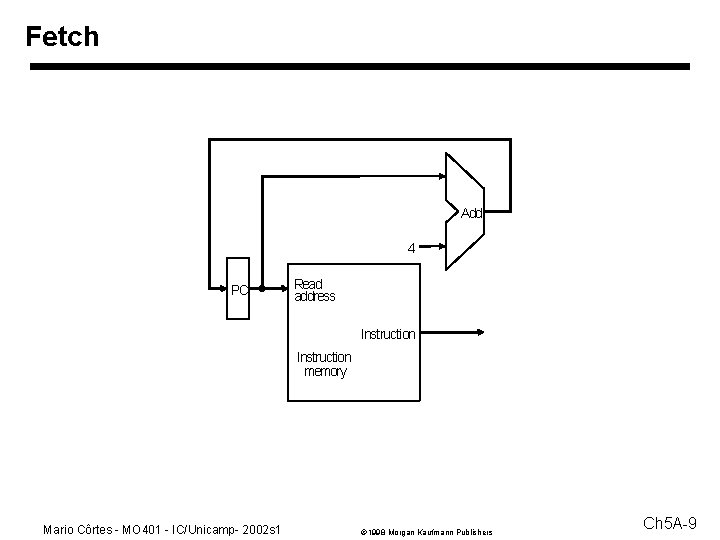

Fetch Add 4 PC Read address Instruction memory Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-9

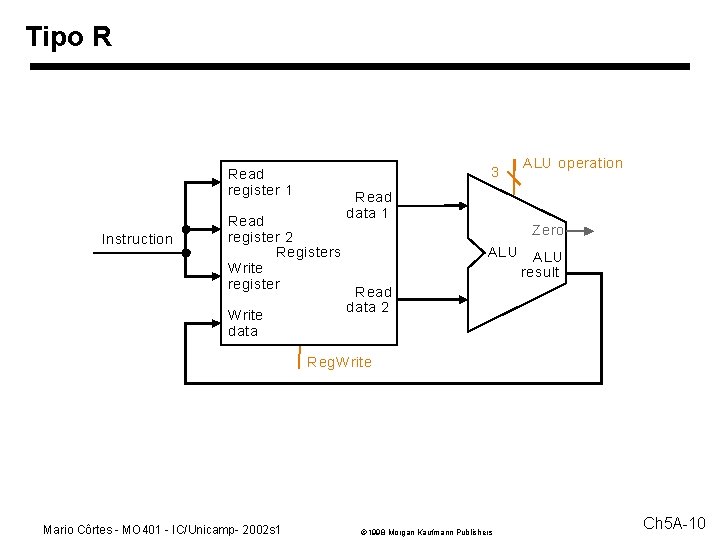

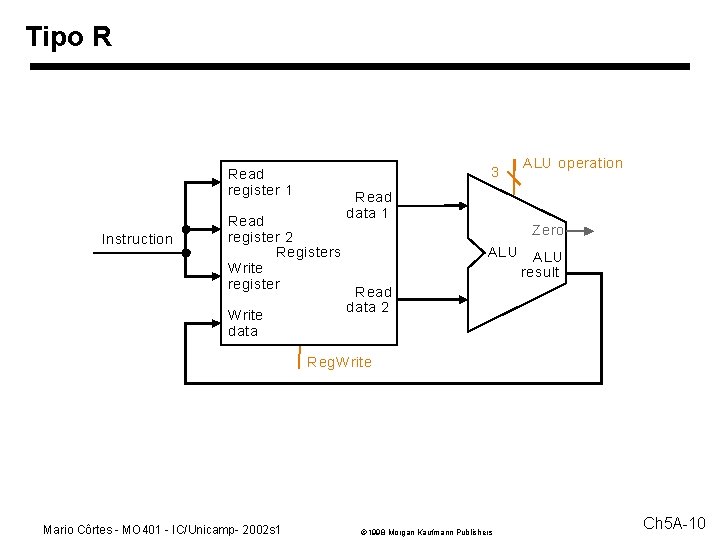

Tipo R 3 Read register 1 Instruction Read register 2 Registers W rite register W rite data ALU operation R ead data 1 Zero AL U ALU result R ead data 2 Reg. W rite Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-10

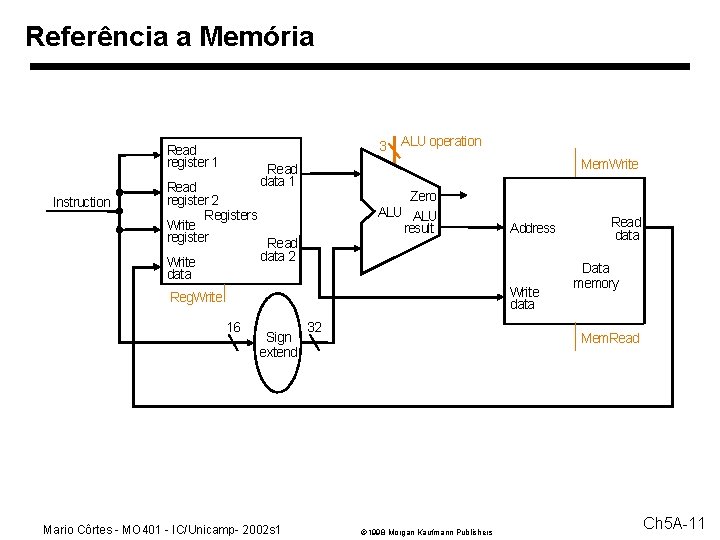

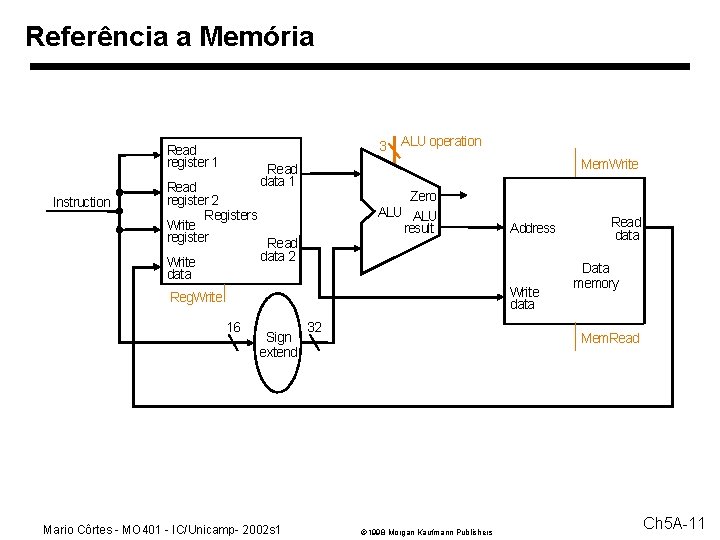

Referência a Memória 3 Read register 1 Instruction ALU operation Mem. Write Read data 1 Read register 2 Registers Write register Read data 2 Write data Zero ALU result Address Write data Reg. Write 16 Sign extend Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 32 Read data Data memory Mem. Read 1998 Morgan Kaufmann Publishers Ch 5 A-11

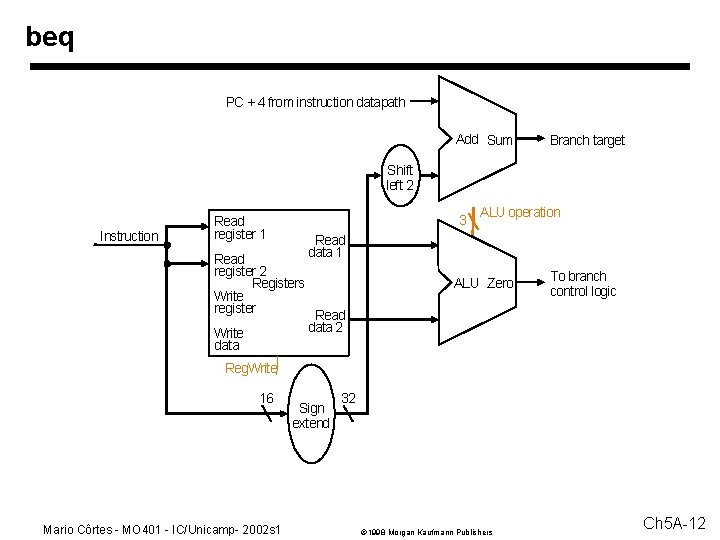

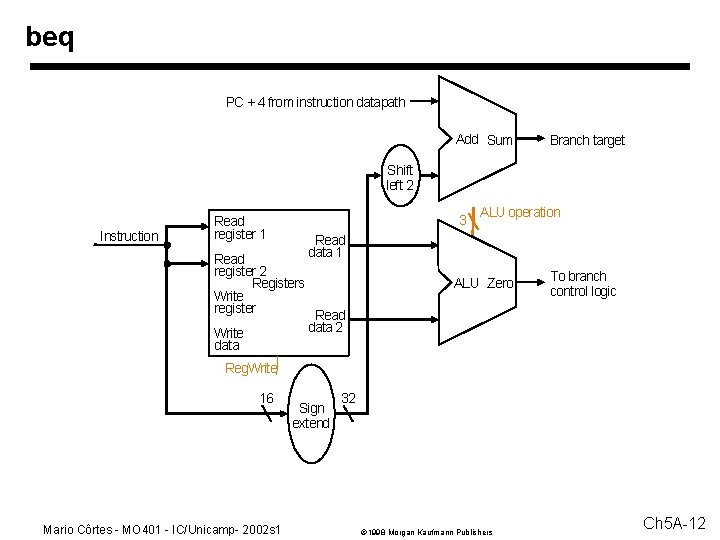

beq PC + 4 from instruction datapath Add Sum Branch target Shift left 2 Instruction Read register 1 3 ALU operation Read data 1 Read register 2 Registers Write register Read data 2 Write data ALU Zero To branch control logic Reg. Write 16 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 Sign extend 32 1998 Morgan Kaufmann Publishers Ch 5 A-12

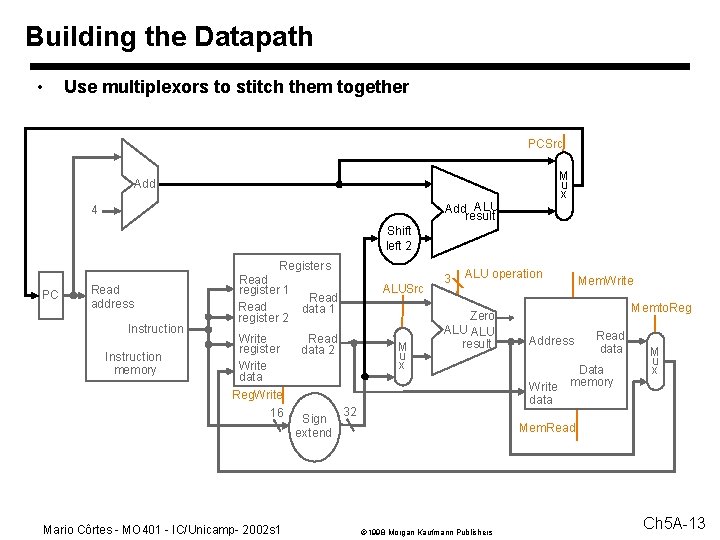

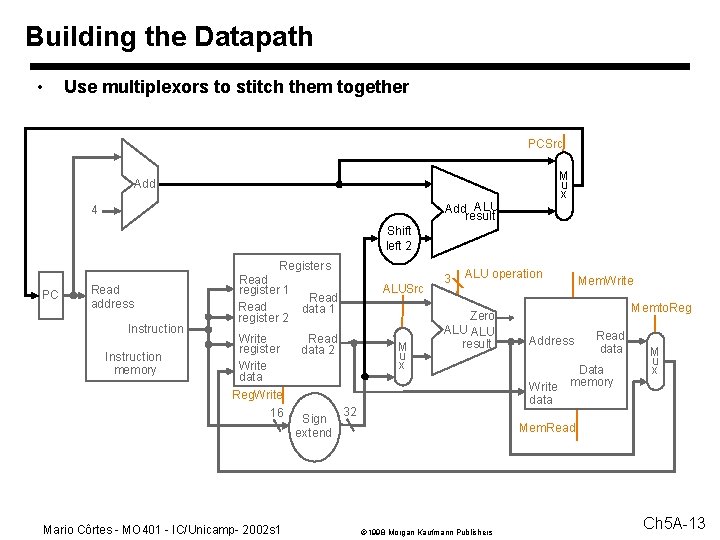

Building the Datapath • Use multiplexors to stitch them together PCSrc M u x Add ALU result 4 Shift left 2 PC Read address Instruction memory Registers Read register 1 Read data 1 register 2 Write register Write data Reg. Write 16 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 ALUSrc Read data 2 Sign extend M u x 3 ALU operation Zero ALU result Memto. Reg Address Write data 32 Mem. Write Read data Data memory M u x Mem. Read 1998 Morgan Kaufmann Publishers Ch 5 A-13

ALUs e Multiplexadores • • • ALU genérica: R 1 R 2 op R 3 ALU soma para endereço instrução: PC + 4 ALU soma para endereço de desvio: PC + Sign. Ext (Shift. Left (Offset)) • MUX 2: 1 para escolher segundo operando da ALU genérica – R 2 – Sign. Ext (Offset) • MUX 2: 1 para escolher o que será carregado no PC – PC + 4 – PC + Sign. Ext (Shift. Left (Offset)) • MUX 2: 1 para escolher qual é a origem do dado a ser escrito no Banco de Registradores – lido da memória – resultado da operação da ALU 1998 genérica Mario Côrtes - MO 401 - IC/Unicamp 2002 s 1 Morgan Kaufmann Publishers Ch 5 A-14

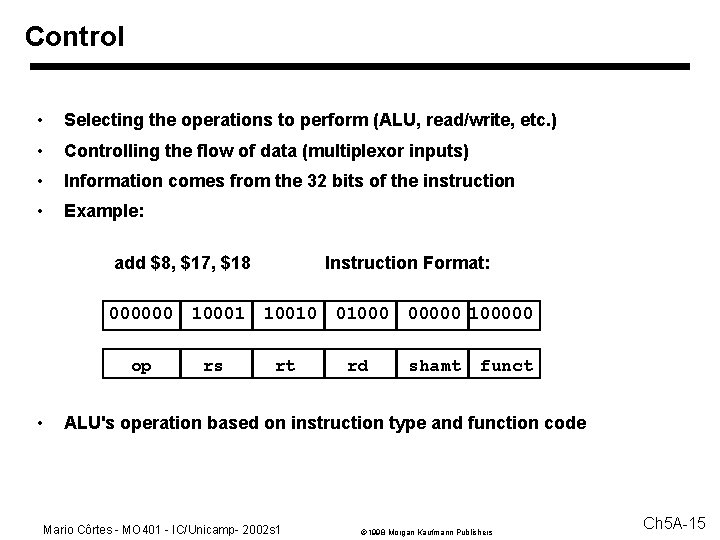

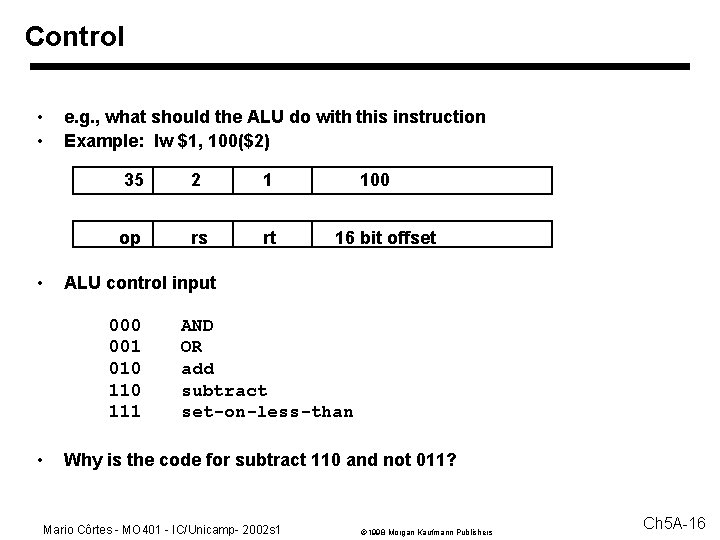

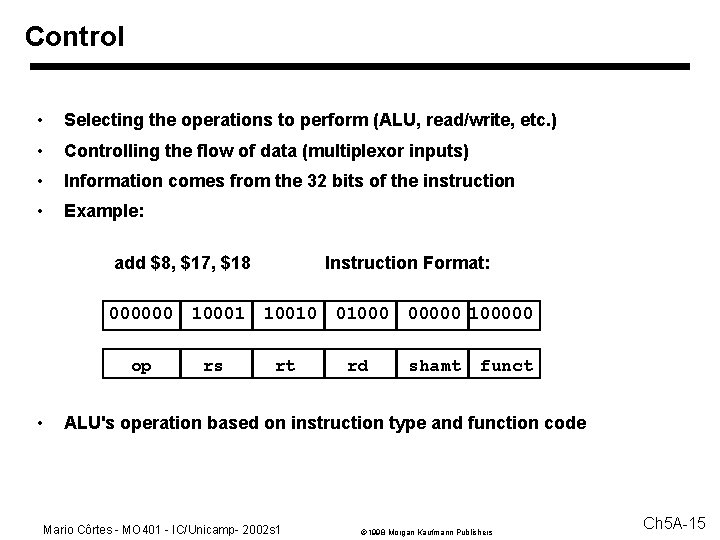

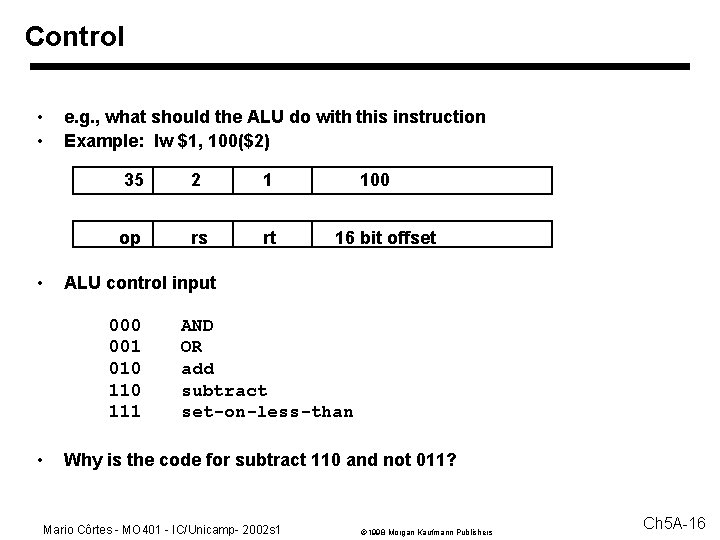

Control • Selecting the operations to perform (ALU, read/write, etc. ) • Controlling the flow of data (multiplexor inputs) • Information comes from the 32 bits of the instruction • Example: add $8, $17, $18 000000 op • Instruction Format: 10001 10010 01000 00000 100000 rs rt rd shamt funct ALU's operation based on instruction type and function code Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-15

Control • • • e. g. , what should the ALU do with this instruction Example: lw $1, 100($2) 35 2 1 op rs rt 16 bit offset ALU control input 000 001 010 111 • 100 AND OR add subtract set-on-less-than Why is the code for subtract 110 and not 011? Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-16

Controle da ALU OPCODE IR 6 Unid. Contr. (parte) OPCODE ALUop funct 2 6 ALU Control 3 ALU Funct. Binv - cod Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-17

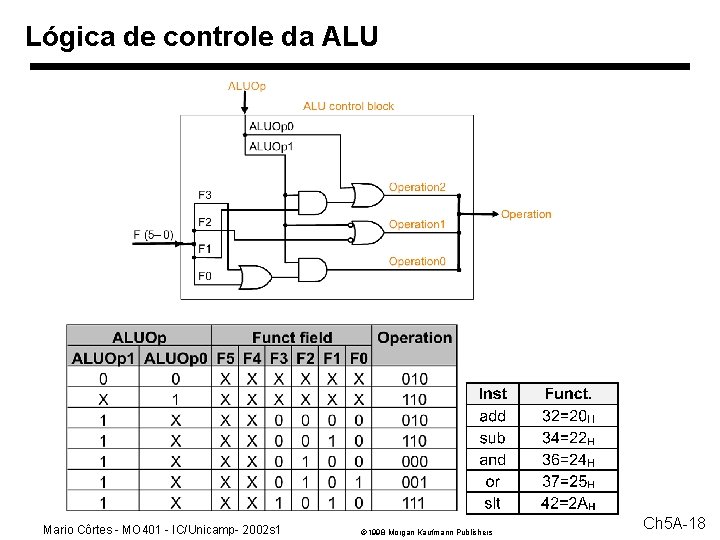

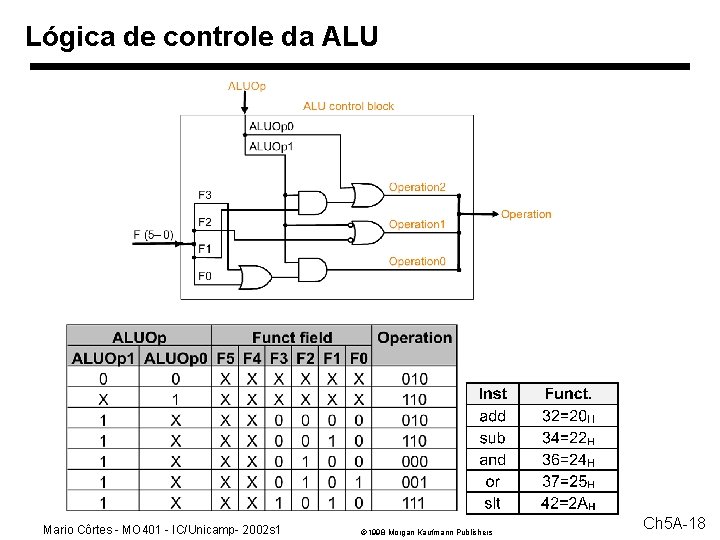

Lógica de controle da ALU Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-18

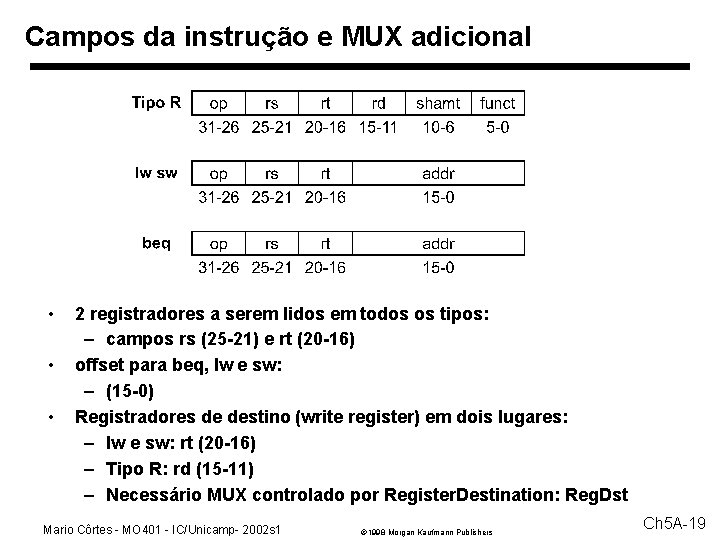

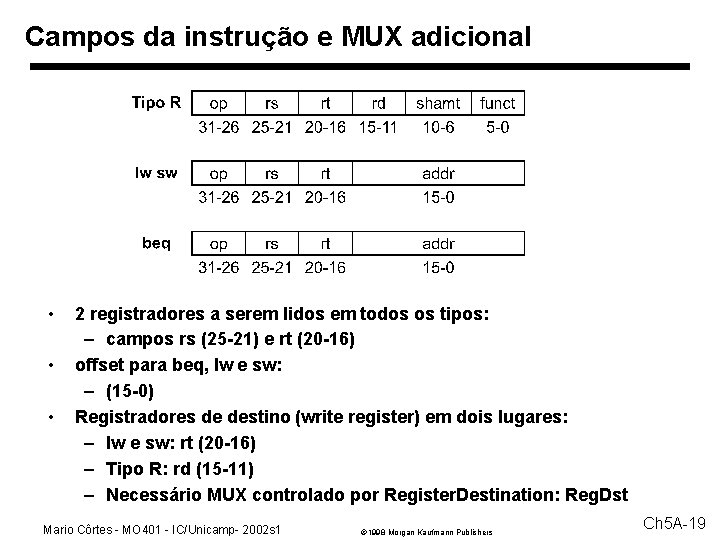

Campos da instrução e MUX adicional • • • 2 registradores a serem lidos em todos os tipos: – campos rs (25 -21) e rt (20 -16) offset para beq, lw e sw: – (15 -0) Registradores de destino (write register) em dois lugares: – lw e sw: rt (20 -16) – Tipo R: rd (15 -11) – Necessário MUX controlado por Register. Destination: Reg. Dst Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-19

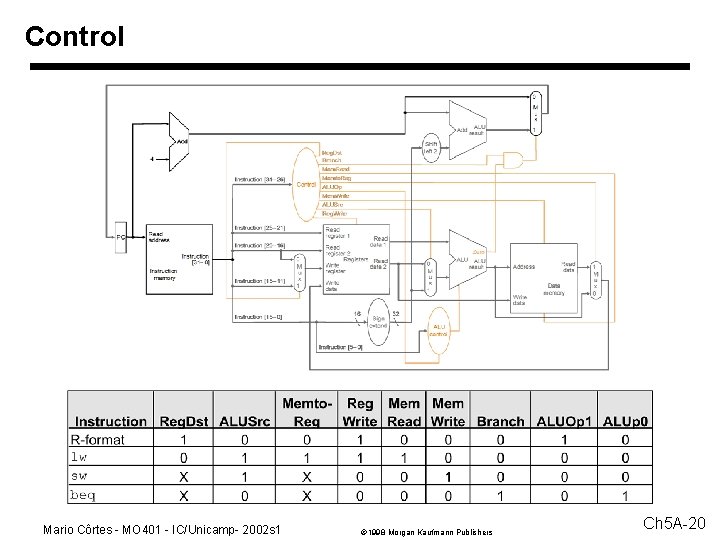

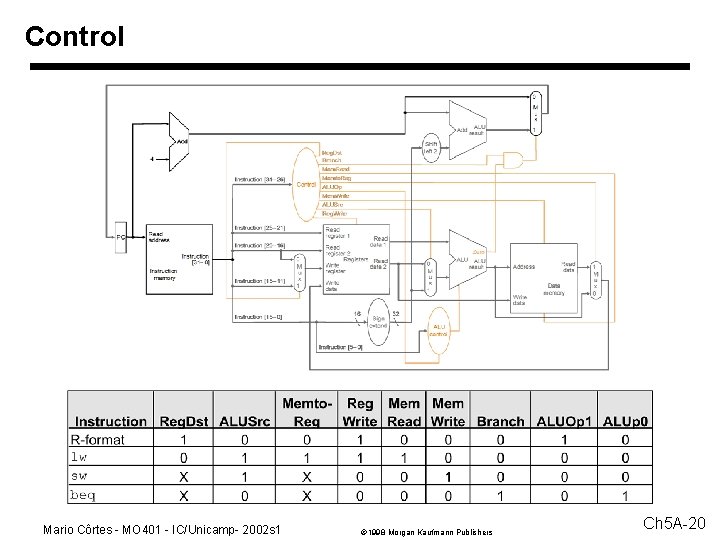

Control Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-20

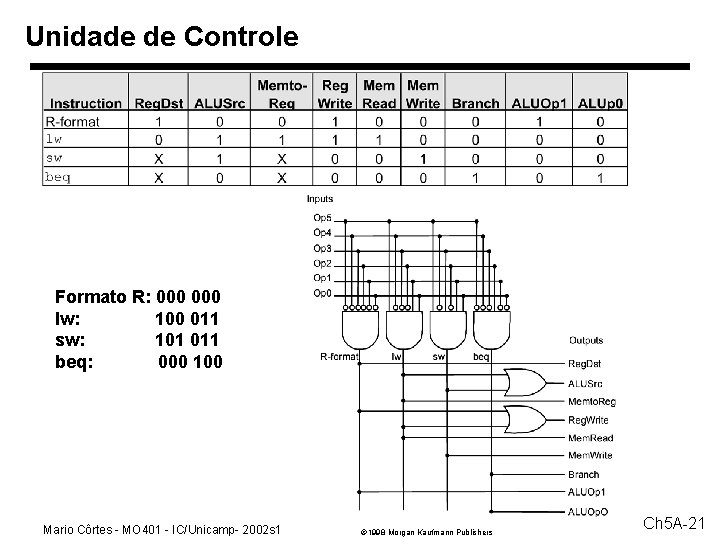

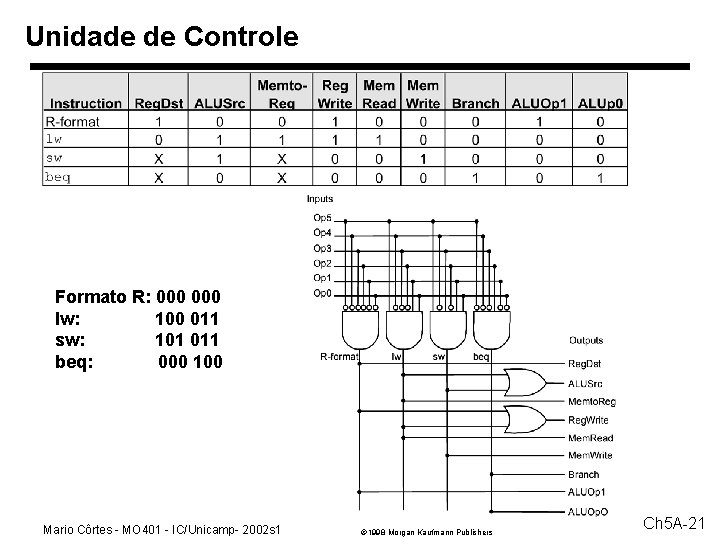

Unidade de Controle Formato R: 000 lw: 100 011 sw: 101 011 beq: 000 100 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-21

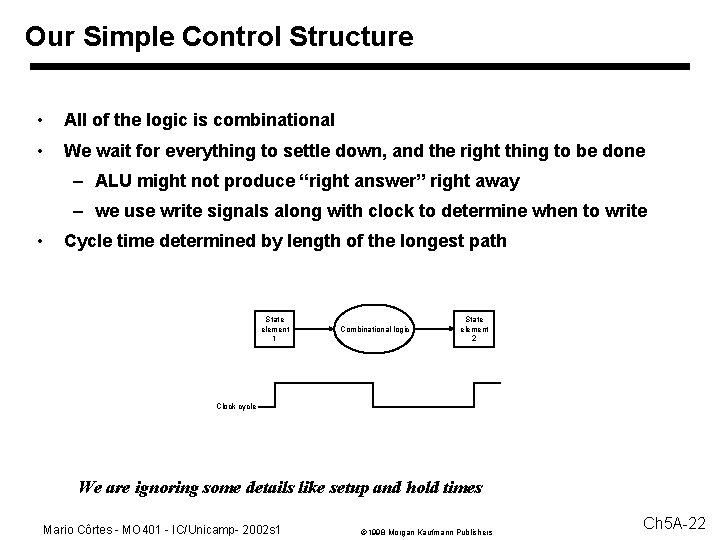

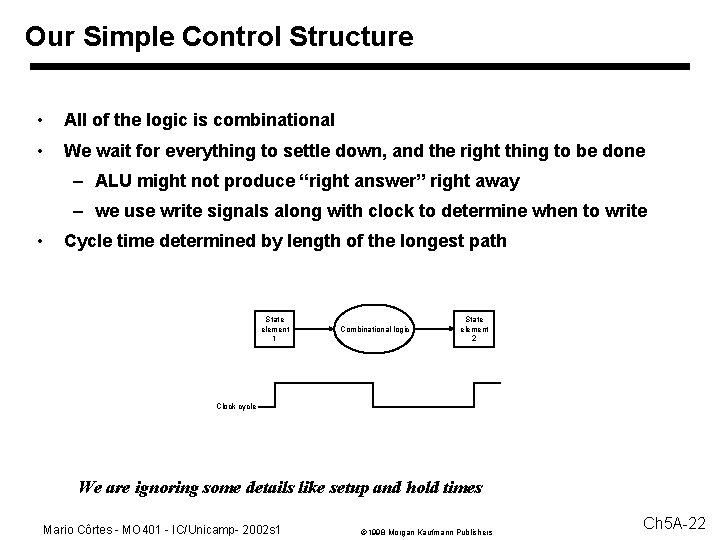

Our Simple Control Structure • All of the logic is combinational • We wait for everything to settle down, and the right thing to be done – ALU might not produce “right answer” right away – we use write signals along with clock to determine when to write • Cycle time determined by length of the longest path State element 1 Combinational logic State element 2 Clock cycle We are ignoring some details like setup and hold times Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-22

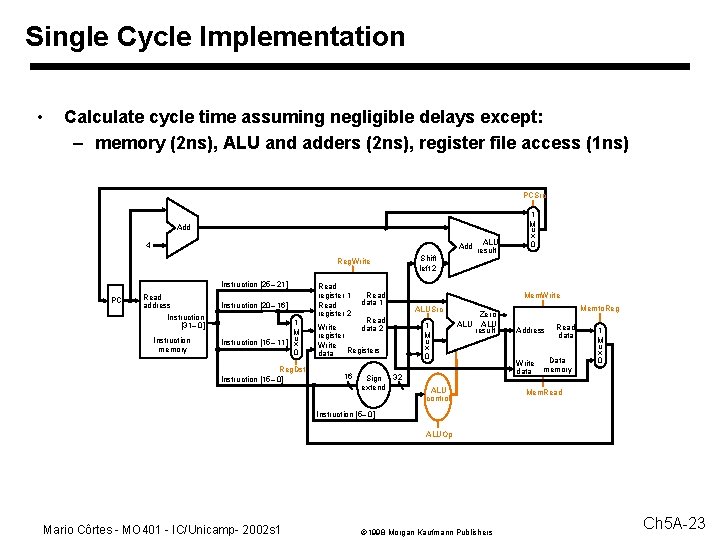

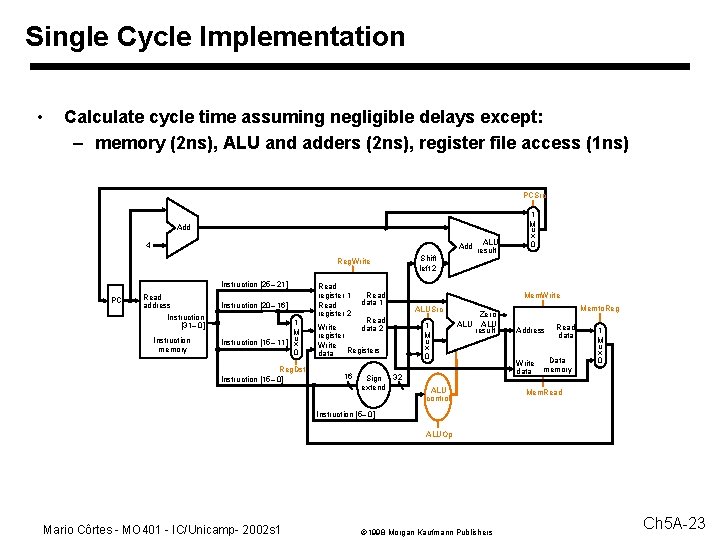

Single Cycle Implementation • Calculate cycle time assuming negligible delays except: – memory (2 ns), ALU and adders (2 ns), register file access (1 ns) PCSrc Add 4 Shift left 2 Reg. Write Instruction [25– 21] PC Read address Instruction [31– 0] Instruction memory Instruction [20– 16] 1 M u Instruction [15– 11] x 0 Reg. Dst Instruction [15– 0] Read register 1 Read register 2 Read data 1 Mem. Write ALUSrc Read data 2 1 M u x 0 Write register Write Registers data 16 Sign extend ALU Add result 1 M u x 0 Zero ALU result 32 ALU control Memto. Reg Address Write data Read data Data memory 1 M u x 0 Mem. Read Instruction [5– 0] ALUOp Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-23

![Adicionando a instrução jump Instruction 25 0 26 Shift left 2 Jump address 31 Adicionando a instrução jump Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/e24867c9810ae3d13a3f919cecd92f42/image-24.jpg)

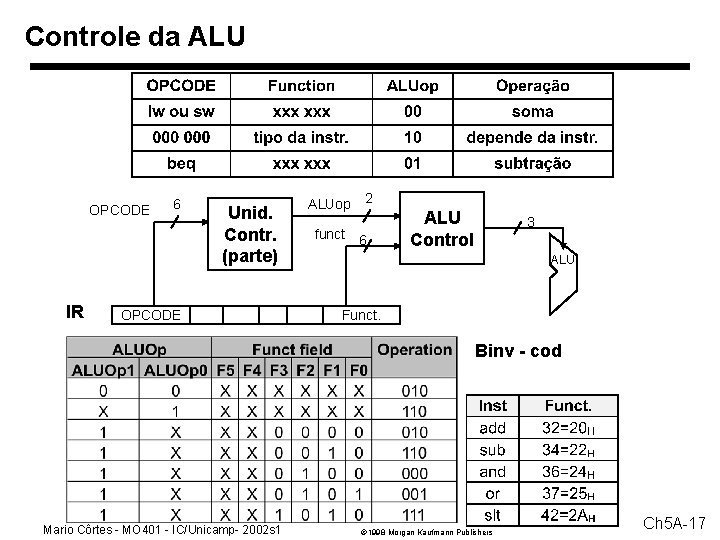

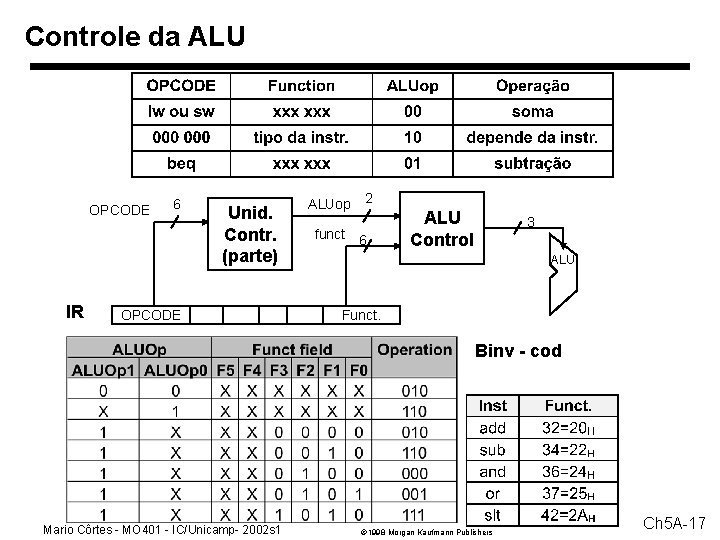

Adicionando a instrução jump Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 0 1 M u x ALU Add result 1 0 Zero ALU result Address PC+4 [31– 28] Add Shift left 2 Reg. Dst Jump 4 Branch Mem. Read Instruction [31– 26] Control Memto. Reg ALUOp Mem. Write ALUSrc Reg. Write PC Instruction [25– 21] Read address Read register 1 Instruction [20– 16] Instruction [31– 0] Instruction memory 0 M u x 1 Instruction [15– 11] Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data 16 Instruction [15– 0] Sign extend Read data Data memory 1 M u x 0 32 ALU control Instruction [5– 0] 2 address 31 -26 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 25 -0 1998 Morgan Kaufmann Publishers Ch 5 A-24

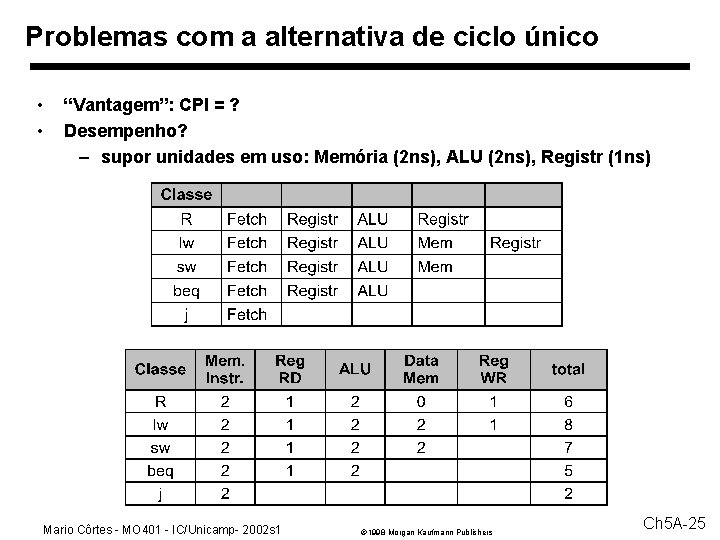

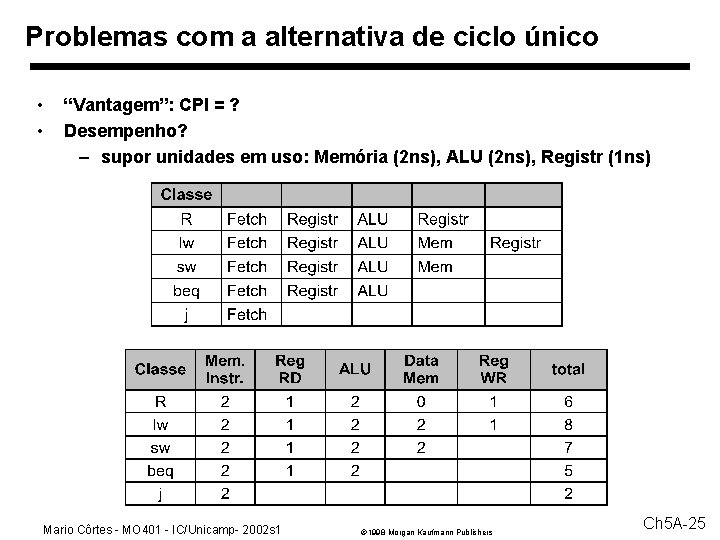

Problemas com a alternativa de ciclo único • • “Vantagem”: CPI = ? Desempenho? – supor unidades em uso: Memória (2 ns), ALU (2 ns), Registr (1 ns) Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-25

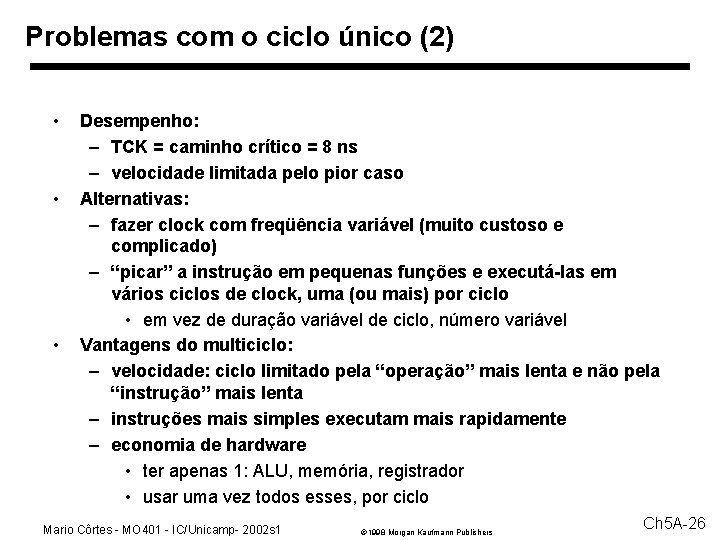

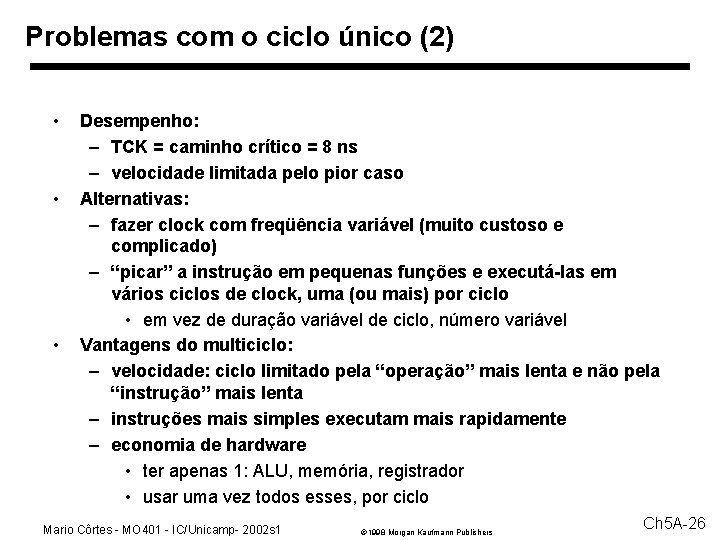

Problemas com o ciclo único (2) • • • Desempenho: – TCK = caminho crítico = 8 ns – velocidade limitada pelo pior caso Alternativas: – fazer clock com freqüência variável (muito custoso e complicado) – “picar” a instrução em pequenas funções e executá-las em vários ciclos de clock, uma (ou mais) por ciclo • em vez de duração variável de ciclo, número variável Vantagens do multiciclo: – velocidade: ciclo limitado pela “operação” mais lenta e não pela “instrução” mais lenta – instruções mais simples executam mais rapidamente – economia de hardware • ter apenas 1: ALU, memória, registrador • usar uma vez todos esses, por ciclo Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 A-26