Arquiteturas Reconfigurveis e GARP Karina Zupo de Oliveira

- Slides: 18

Arquiteturas Reconfiguráveis e GARP Karina Zupo de Oliveira - RA 028520 MO 401 – Prof. Rodoldo Novembro 2005

Agenda n n n GARP – Objetivos ISACs, FPGAs Arquiteturas Reconfiguráveis GARP – Arquitetura GARP – Software GARPCC

GARP - Objetivos n n Melhorar desempenho do processador Colorário: 10% do código (kernel) executa por 90% do tempo Uso de FPGAs Arquitetura reconfigurável em computador desktop

ISACs n n n Circuitos integráveis com lógica para aplicações específicas Programados e elaborados em fábrica Rápidos e altamente otimizados Caros Computadores desktop: não fazem sentido utilizar

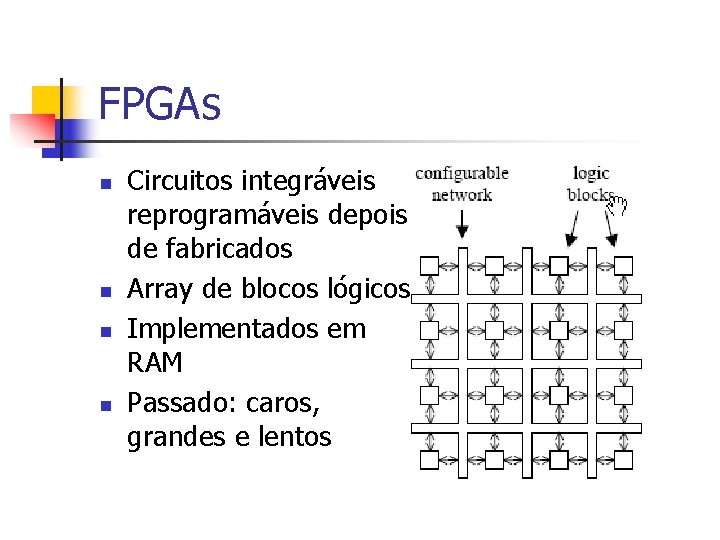

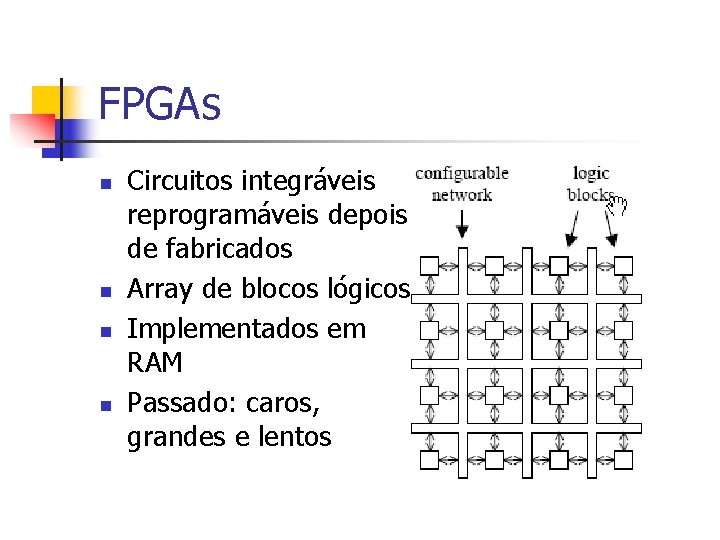

FPGAs n n Circuitos integráveis reprogramáveis depois de fabricados Array de blocos lógicos Implementados em RAM Passado: caros, grandes e lentos

Arquiteturas Reconfiguráveis n n Aplicações específicas Sequenciamento de genoma, tratamento de imagens, etc Splash-2 DECPe. RLe

Arquiteturas Reconfiguráveis 2 n n n Granularidade Fora do chip do processador: PRISM Dentro do datapath do processador: Chimaera, PRISC Conectado ao processador: Garp, Spyder Somente FPGA: DISC

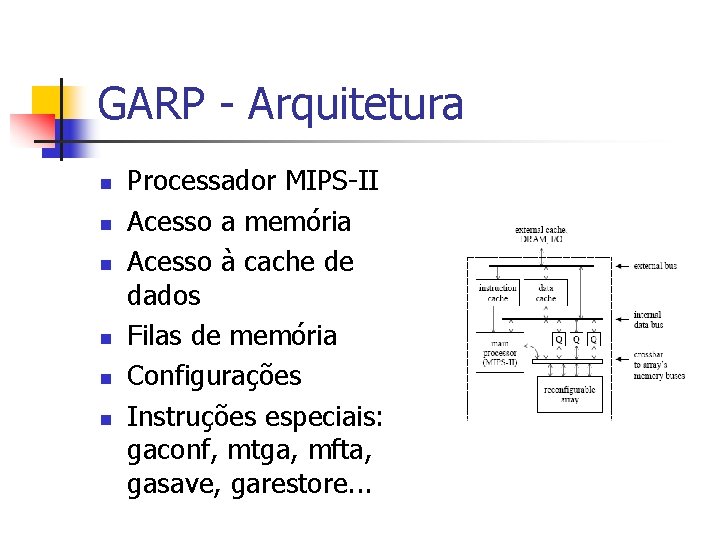

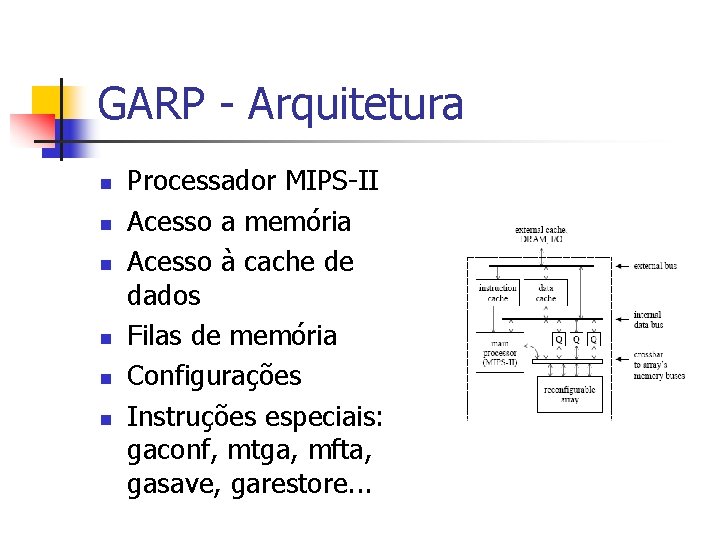

GARP - Arquitetura n n n Processador MIPS-II Acesso a memória Acesso à cache de dados Filas de memória Configurações Instruções especiais: gaconf, mtga, mfta, gasave, garestore. . .

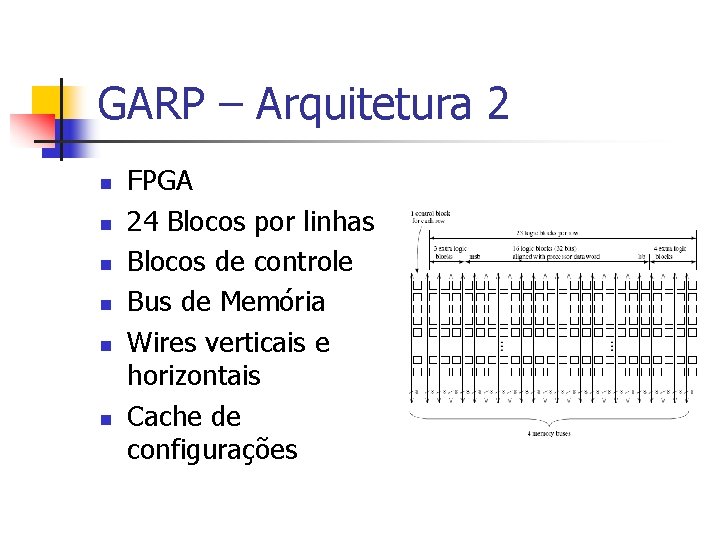

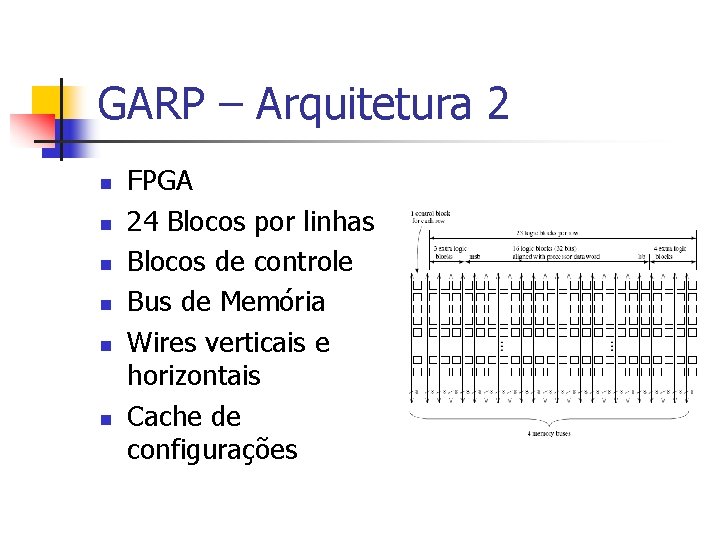

GARP – Arquitetura 2 n n n FPGA 24 Blocos por linhas Blocos de controle Bus de Memória Wires verticais e horizontais Cache de configurações

GARP – Arquitetura 4 n n n Definição de ciclo de clock Compatibilidade binária de FPGA Contador de clock: defini quantos passos dura uma execução do FPGA Quando contador = 0 o FPGA para Processador define contador através de instruções específicas

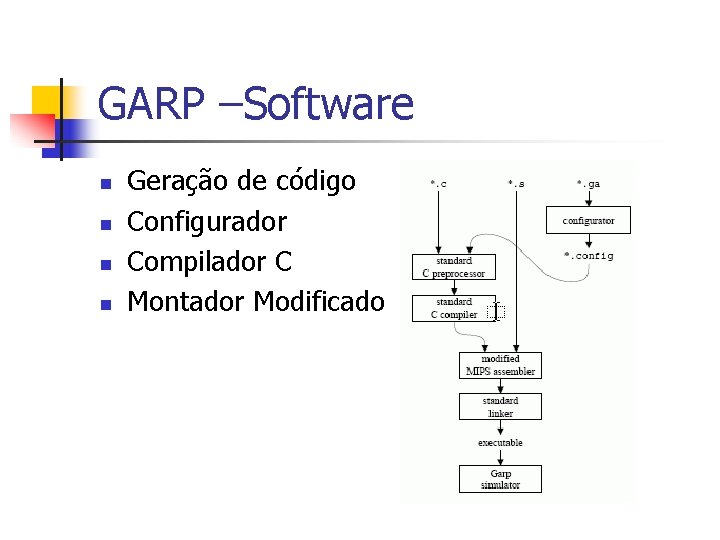

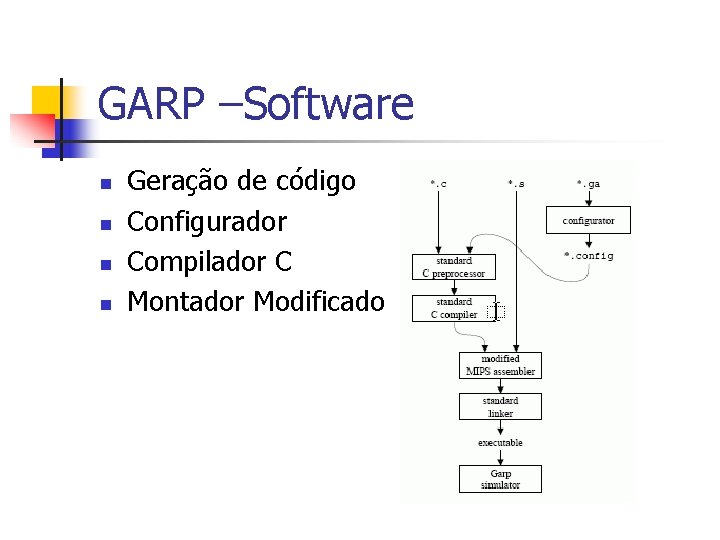

GARP –Software n n Geração de código Configurador Compilador C Montador Modificado

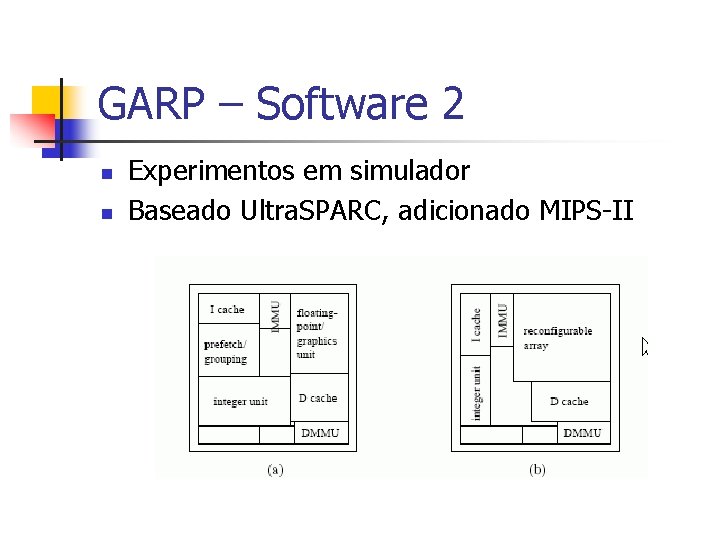

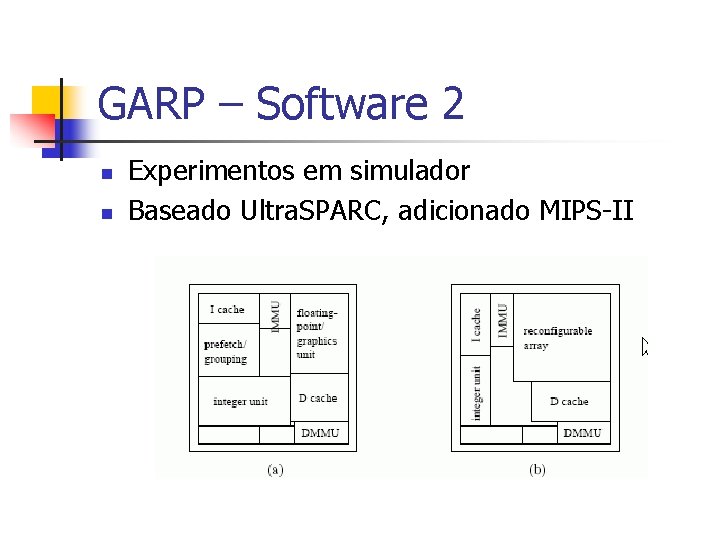

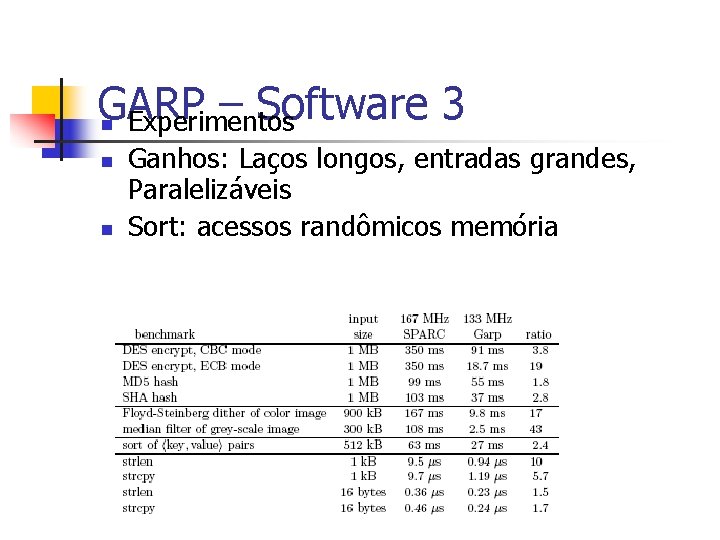

GARP – Software 2 n n Experimentos em simulador Baseado Ultra. SPARC, adicionado MIPS-II

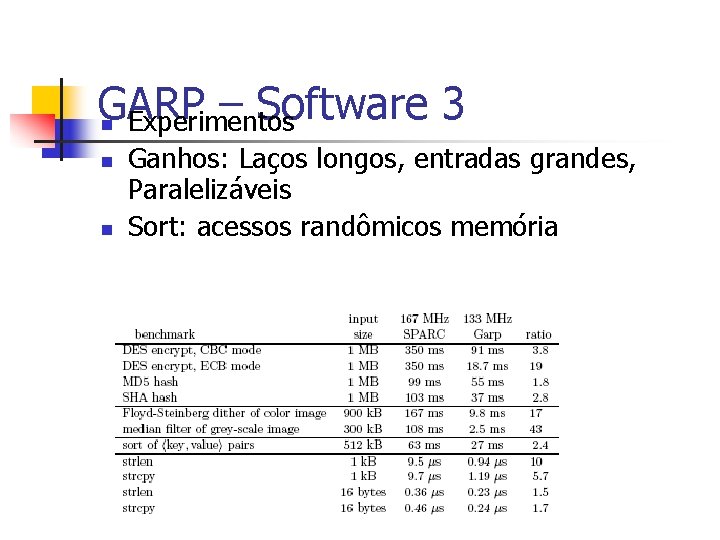

GARP – Software 3 Experimentos n n n Ganhos: Laços longos, entradas grandes, Paralelizáveis Sort: acessos randômicos memória

GARPCC n n n Compilador SUIF Técnicas de VLIW e uso de hiperblocos Profiling para achar melhor blocos Loads especulativos Pipelining de iterações de laços Uso extensivo de filas de memória

GARPCC - 2 n n n Problemas Falhas de acesso ao cache Bibliotecas C Melhor seleção dos laços Aplicações genéricas: desempenho não muito melhor que computadores comuns

Conclusão n n n Estudo: FPGA integrado com MIPS-II Foco: computadores desktop Ganho: programas paralelizáveis Compilador garpcc: ainda não é o suficiente Meta: ganhos reais em aplicações de uso genérico Realidade daqui 10 -15 anos?

Referências n n n http: //brass. cs. berkeley. edu/garp. html Site do GARP na Universidade de Berkeley Garp: A MIPS Processor with a Reconfigurable Coprocessor John R. Hauser and John Wawrzynek, IEEE Symposium on Field. Programmable Custom Computing Machines (FCCM '97, April 16 -18, 1997) The Garp Architecture and C Compiler Timothy J. Callahan, John R. Hauser, and John Wawrzynek, IEEE Computer, April 2000 Augmenting a Microprocessor with Reconfigurable Hardware John Reid Hauser, Ph. D. Thesis, December 2000 Automatic Compilation of C for Hybrid Reconfigurable Architectures Timothy John Callahan, Ph. D. Thesis, Fall 2002

Perguntas n e-mail: karinazupo@yahoo. com. br