Arquitectura y Organizacin de Computadores Introduccin a los

- Slides: 30

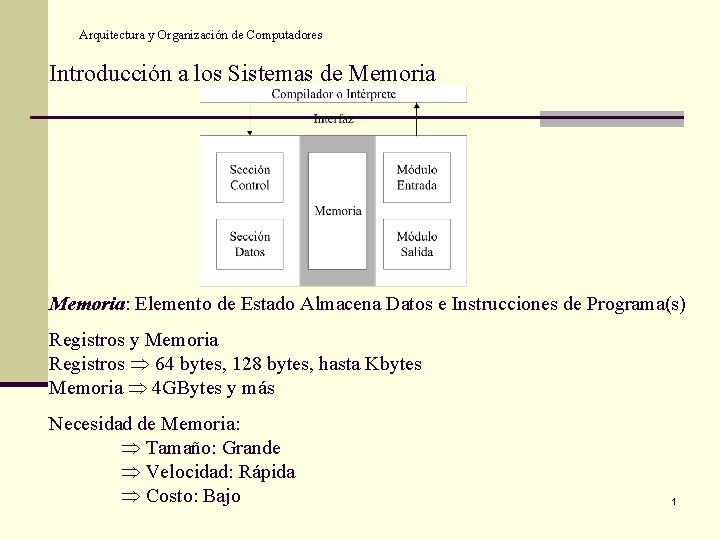

Arquitectura y Organización de Computadores Introducción a los Sistemas de Memoria: Elemento de Estado Almacena Datos e Instrucciones de Programa(s) Registros y Memoria Registros Þ 64 bytes, 128 bytes, hasta Kbytes Memoria Þ 4 GBytes y más Necesidad de Memoria: Þ Tamaño: Grande Þ Velocidad: Rápida Þ Costo: Bajo 1

Arquitectura y Organización de Computadores El Concepto de Localidad Espacial: Si una Dirección D es Accesada en Tiempo t = t 0, es Probable que se Accesen Direcciones Cercanas a D en un Futuro Próximo Localidad Temporal: Si una dirección D es Accesada en Tiempo t = t 0, es Probable que esa Misma Dirección Sea Accesada en un Futuro Cercano En Otras Palabras, Un Conjunto Pequeño de Instrucciones y Datos son Utilizados en una Ventana de Tiempo Definida. El Contenido del Conjunto Varían Durante el Tiempo, Luego No es Necesario Tener Todos los Datos e Instrucciones en una Memoria Rápida Jerarquías de Memoria Diseño Implica Optimizar la Organización del Sistema de Memoria Con el Fin de Minimizar el Tiempo Medio de Acceso a Memoria para una Carga de Trabajo Típica. O sea, Se Deben Generar Varios Niveles de Memoria, Tamaño y Velocidad Memoria Grande y Lenta: Almacena Instrucciones y Datos de Programas Memoria Rápida y Pequeña: Almacena el Conjunto de Instrucciones y Datos Más Utilizado por los Programas 2

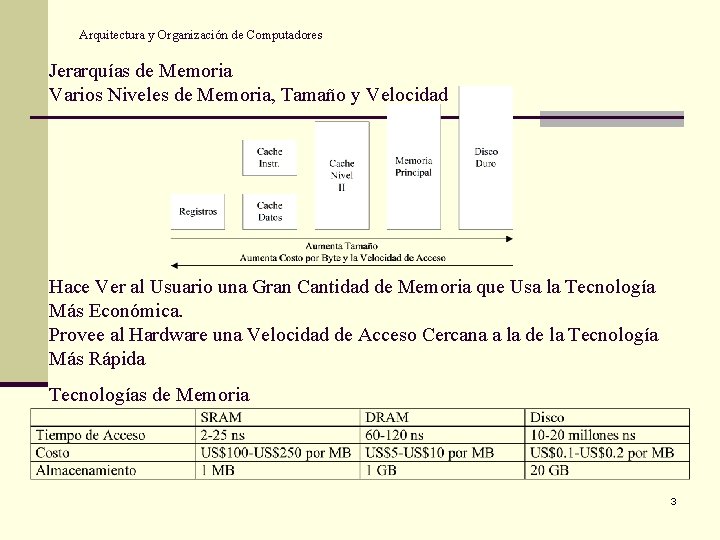

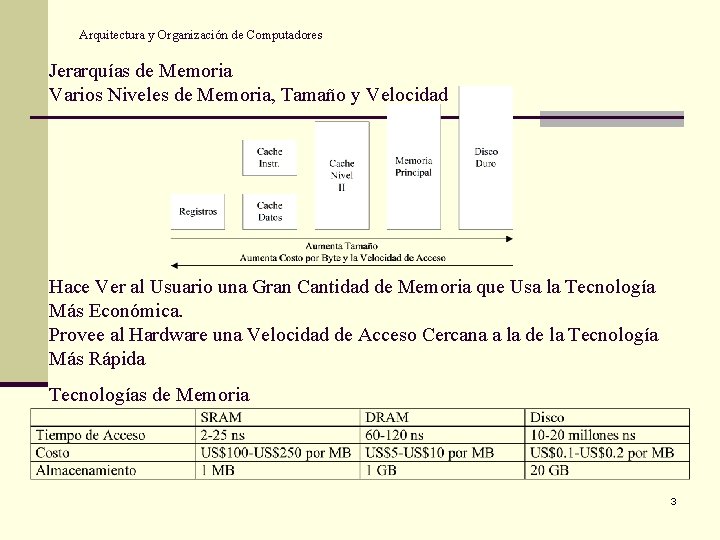

Arquitectura y Organización de Computadores Jerarquías de Memoria Varios Niveles de Memoria, Tamaño y Velocidad Hace Ver al Usuario una Gran Cantidad de Memoria que Usa la Tecnología Más Económica. Provee al Hardware una Velocidad de Acceso Cercana a la de la Tecnología Más Rápida Tecnologías de Memoria 3

SRAM- RAM Estática n Los bits se almacenan como interruptores n n n encendidos o apagados Construcciones más complejas Más grandes por bit Más cara No necesita circuitos de refrescado Más rápida Usualmente es la caché 4

DRAM – RAM Dinámica n Los bits se almacenan como carga en capacitores n Los condensadores tienden a descargarse n Requieren refrescos periódicos para mantener n n n almacenados los datos Construcción sencilla Más pequeña por bit Más econónica Necesita circuitos de refrescado Más lenta Usualmente es la memoria principal 5

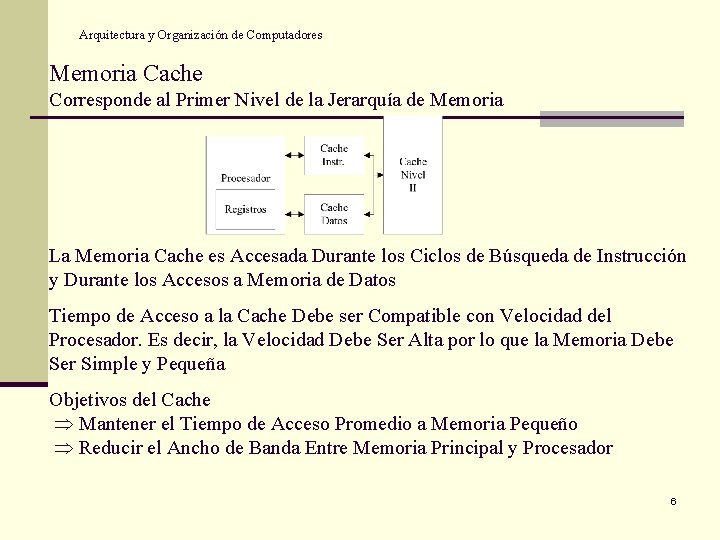

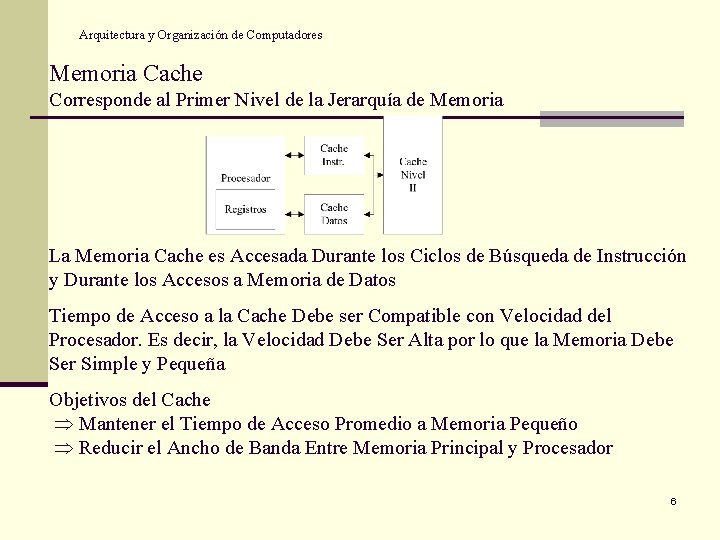

Arquitectura y Organización de Computadores Memoria Cache Corresponde al Primer Nivel de la Jerarquía de Memoria La Memoria Cache es Accesada Durante los Ciclos de Búsqueda de Instrucción y Durante los Accesos a Memoria de Datos Tiempo de Acceso a la Cache Debe ser Compatible con Velocidad del Procesador. Es decir, la Velocidad Debe Ser Alta por lo que la Memoria Debe Ser Simple y Pequeña Objetivos del Cache Þ Mantener el Tiempo de Acceso Promedio a Memoria Pequeño Þ Reducir el Ancho de Banda Entre Memoria Principal y Procesador 6

Arquitectura y Organización de Computadores Forma de Operar de una Cache 1. Dirección Generada por el Procesador es Comparada Con Datos Almacenados en el Cache 2. Si Dato Está Presente, el Procesador lo Lee Desde el Cache 3. Si Dato Está Ausente, se Transfiere Desde la Memoria Principal al Cache 4. Si es Necesario se Reemplaza Uno de los Datos Presentes en el Cache Bloque: Es La Unidad Mínima de Transferencia Entre Cache y Memoria. Corresponde a un Conjunto de Palabras Contiguas en Memoria Terminología Acierto: Palabra Buscada Pertenece a Bloque Presente en Cache Desacierto: Palabra Buscada Pertenece a Bloque Ausente de Cache Razón de Acierto: Tasa de Referencias a Memoria que Producen Aciertos Razón de Desacierto: 1 - (Razón de Acierto) Tiempo de Acierto: Tiempo en Leer un Dato del Cache Penalidad de Desacierto: (Tiempo en Reemplazar Bloque) + (Tiempo de Lectura de Dato al Procesador) Tiempo de Acceso Promedio a Memoria: (Razón de Acierto) * (Tiempo de Acierto) + (Razón de Desacierto) * (Penalidad de Desacierto) 7

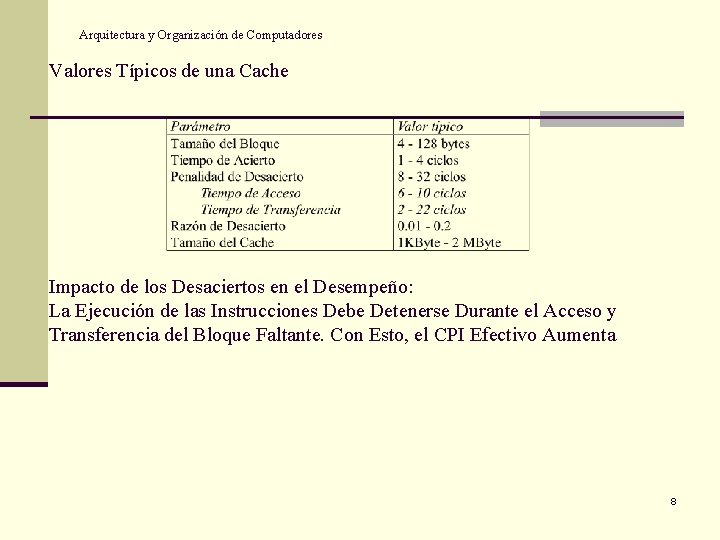

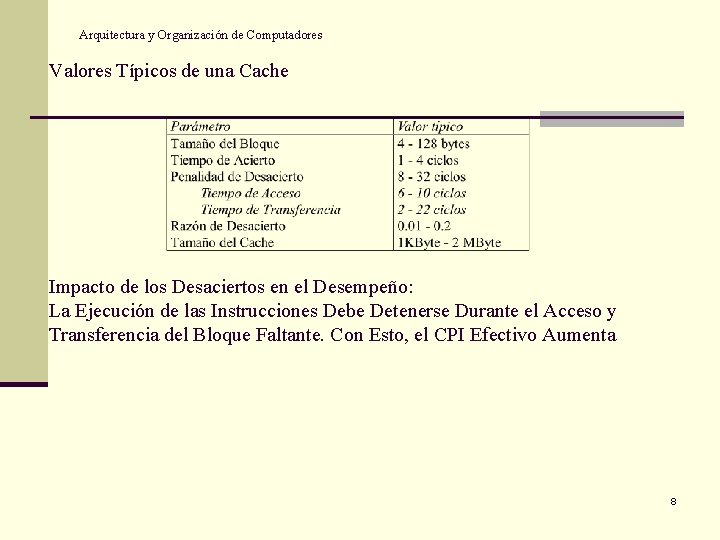

Arquitectura y Organización de Computadores Valores Típicos de una Cache Impacto de los Desaciertos en el Desempeño: La Ejecución de las Instrucciones Debe Detenerse Durante el Acceso y Transferencia del Bloque Faltante. Con Esto, el CPI Efectivo Aumenta 8

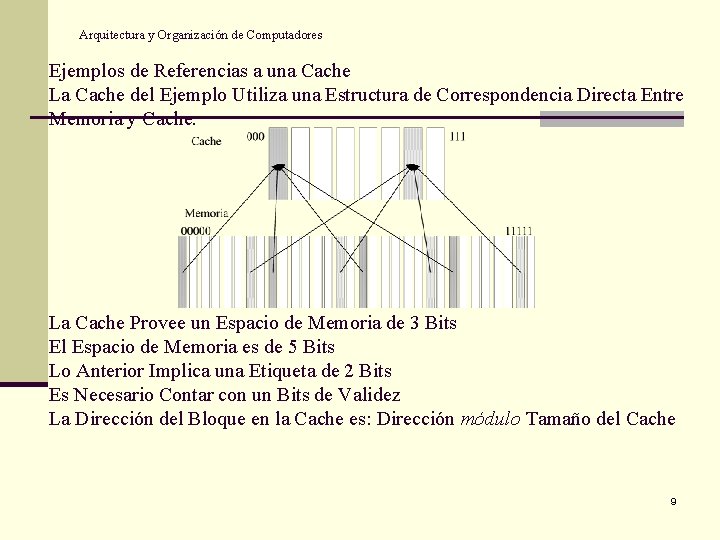

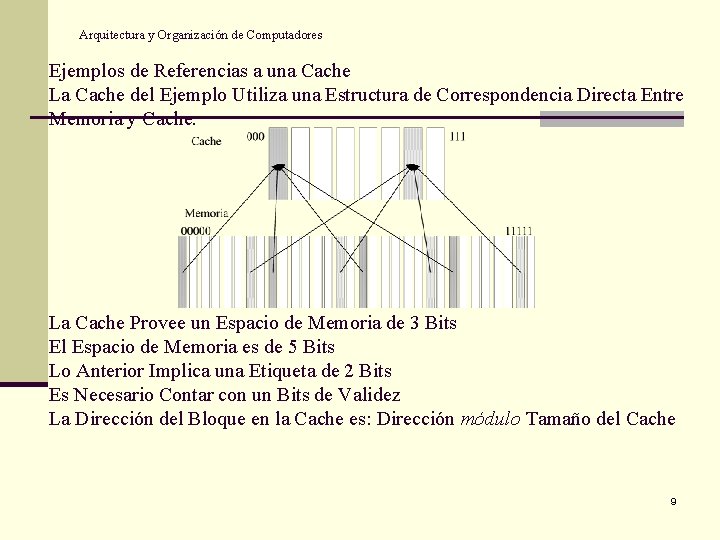

Arquitectura y Organización de Computadores Ejemplos de Referencias a una Cache La Cache del Ejemplo Utiliza una Estructura de Correspondencia Directa Entre Memoria y Cache. La Cache Provee un Espacio de Memoria de 3 Bits El Espacio de Memoria es de 5 Bits Lo Anterior Implica una Etiqueta de 2 Bits Es Necesario Contar con un Bits de Validez La Dirección del Bloque en la Cache es: Dirección módulo Tamaño del Cache 9

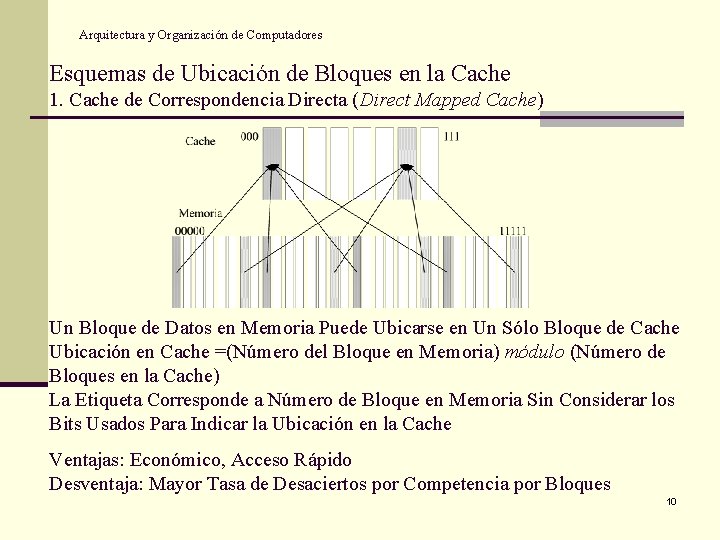

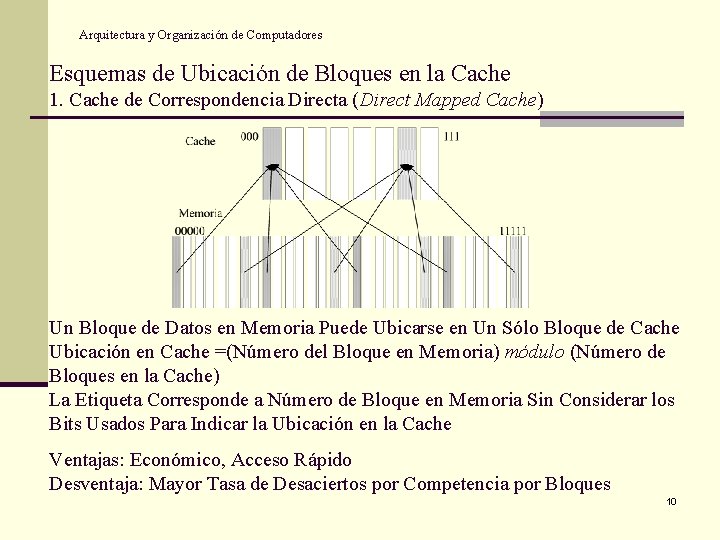

Arquitectura y Organización de Computadores Esquemas de Ubicación de Bloques en la Cache 1. Cache de Correspondencia Directa (Direct Mapped Cache) Un Bloque de Datos en Memoria Puede Ubicarse en Un Sólo Bloque de Cache Ubicación en Cache =(Número del Bloque en Memoria) módulo (Número de Bloques en la Cache) La Etiqueta Corresponde a Número de Bloque en Memoria Sin Considerar los Bits Usados Para Indicar la Ubicación en la Cache Ventajas: Económico, Acceso Rápido Desventaja: Mayor Tasa de Desaciertos por Competencia por Bloques 10

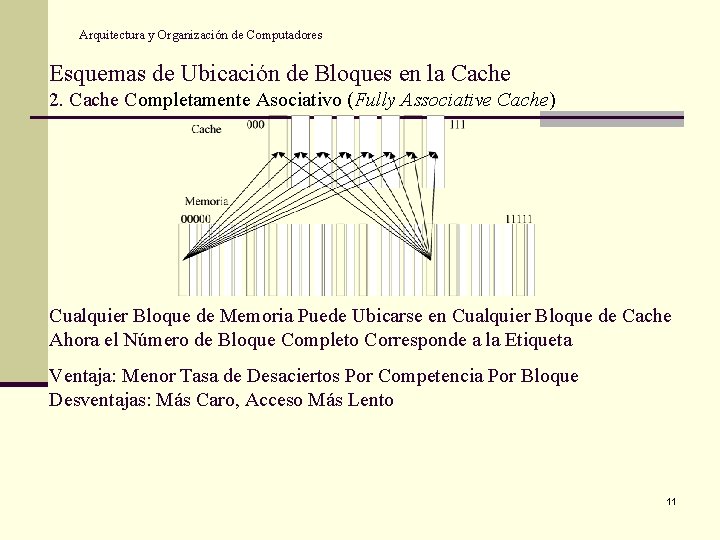

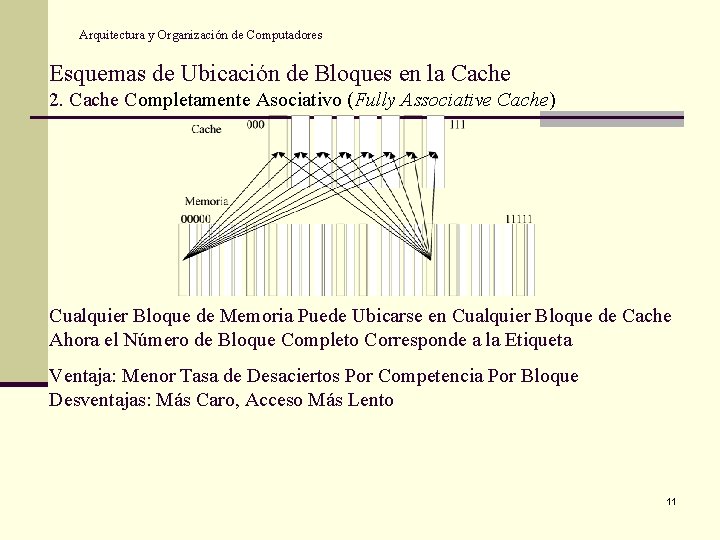

Arquitectura y Organización de Computadores Esquemas de Ubicación de Bloques en la Cache 2. Cache Completamente Asociativo (Fully Associative Cache) Cualquier Bloque de Memoria Puede Ubicarse en Cualquier Bloque de Cache Ahora el Número de Bloque Completo Corresponde a la Etiqueta Ventaja: Menor Tasa de Desaciertos Por Competencia Por Bloque Desventajas: Más Caro, Acceso Más Lento 11

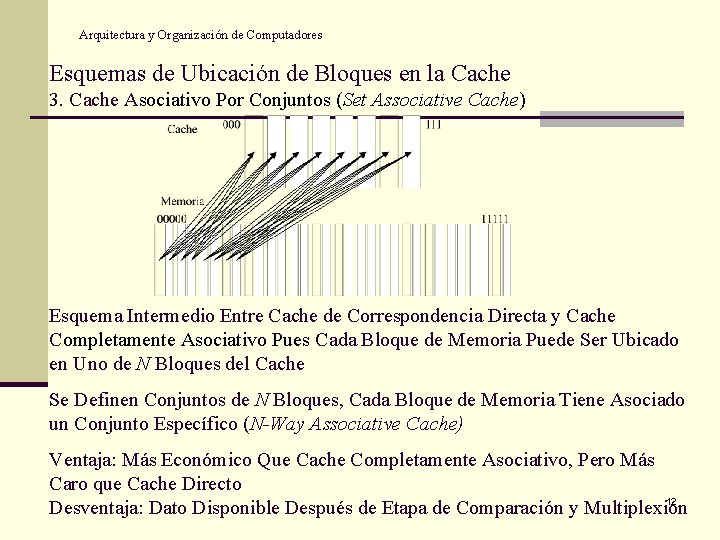

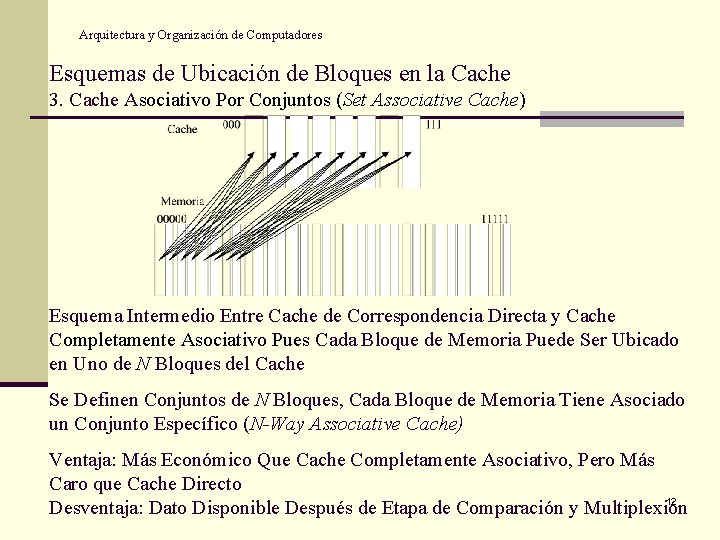

Arquitectura y Organización de Computadores Esquemas de Ubicación de Bloques en la Cache 3. Cache Asociativo Por Conjuntos (Set Associative Cache) Esquema Intermedio Entre Cache de Correspondencia Directa y Cache Completamente Asociativo Pues Cada Bloque de Memoria Puede Ser Ubicado en Uno de N Bloques del Cache Se Definen Conjuntos de N Bloques, Cada Bloque de Memoria Tiene Asociado un Conjunto Específico (N-Way Associative Cache) Ventaja: Más Económico Que Cache Completamente Asociativo, Pero Más Caro que Cache Directo 12 Desventaja: Dato Disponible Después de Etapa de Comparación y Multiplexión

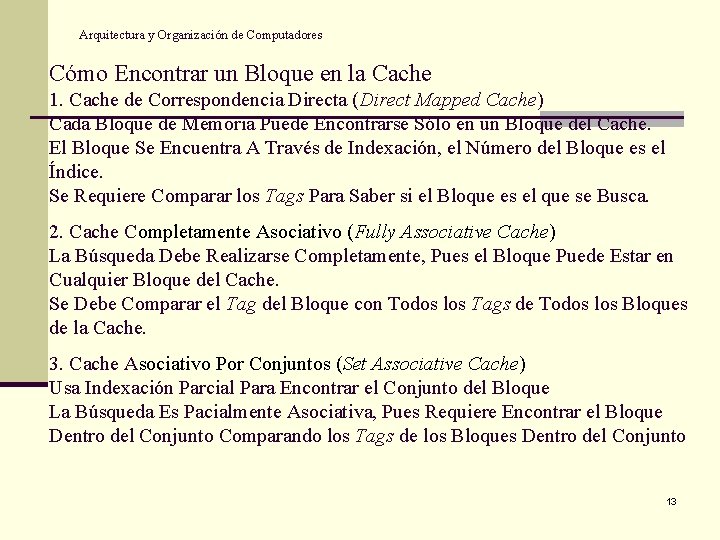

Arquitectura y Organización de Computadores Cómo Encontrar un Bloque en la Cache 1. Cache de Correspondencia Directa (Direct Mapped Cache) Cada Bloque de Memoria Puede Encontrarse Sólo en un Bloque del Cache. El Bloque Se Encuentra A Través de Indexación, el Número del Bloque es el Índice. Se Requiere Comparar los Tags Para Saber si el Bloque es el que se Busca. 2. Cache Completamente Asociativo (Fully Associative Cache) La Búsqueda Debe Realizarse Completamente, Pues el Bloque Puede Estar en Cualquier Bloque del Cache. Se Debe Comparar el Tag del Bloque con Todos los Tags de Todos los Bloques de la Cache. 3. Cache Asociativo Por Conjuntos (Set Associative Cache) Usa Indexación Parcial Para Encontrar el Conjunto del Bloque La Búsqueda Es Pacialmente Asociativa, Pues Requiere Encontrar el Bloque Dentro del Conjunto Comparando los Tags de los Bloques Dentro del Conjunto 13

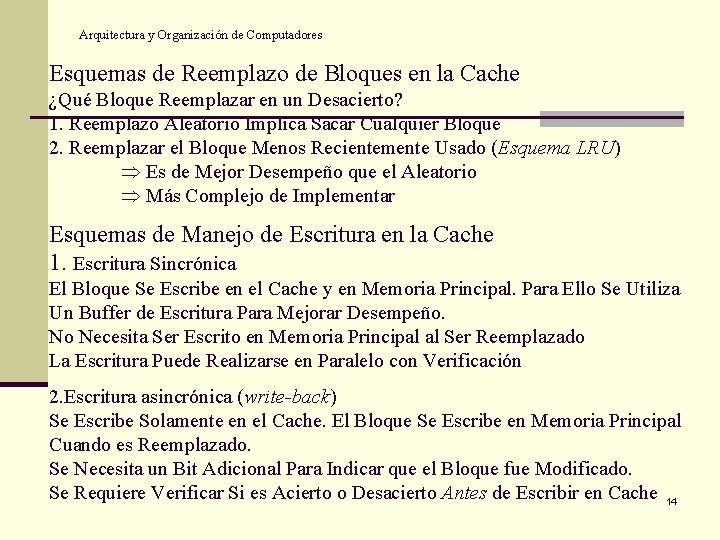

Arquitectura y Organización de Computadores Esquemas de Reemplazo de Bloques en la Cache ¿Qué Bloque Reemplazar en un Desacierto? 1. Reemplazo Aleatorio Implica Sacar Cualquier Bloque 2. Reemplazar el Bloque Menos Recientemente Usado (Esquema LRU) Þ Es de Mejor Desempeño que el Aleatorio Þ Más Complejo de Implementar Esquemas de Manejo de Escritura en la Cache 1. Escritura Sincrónica El Bloque Se Escribe en el Cache y en Memoria Principal. Para Ello Se Utiliza Un Buffer de Escritura Para Mejorar Desempeño. No Necesita Ser Escrito en Memoria Principal al Ser Reemplazado La Escritura Puede Realizarse en Paralelo con Verificación 2. Escritura asincrónica (write-back) Se Escribe Solamente en el Cache. El Bloque Se Escribe en Memoria Principal Cuando es Reemplazado. Se Necesita un Bit Adicional Para Indicar que el Bloque fue Modificado. Se Requiere Verificar Si es Acierto o Desacierto Antes de Escribir en Cache 14

Arquitectura y Organización de Computadores Organización de Memoria Para Soporte de Cache Es Necesario Reducir la Penalidad de un Desacierto y a la Vez Es Necesario Aumentar la Velocidad de Transferencia de Bloques Entre Memoria y Cache 1. Memorias de una Palabra de Ancho Þ Requiere Varios Accesos a Memoria Þ Memoria Requiere ser Muy Rápida Þ Es Una Solución Cara 15

Arquitectura y Organización de Computadores Organización de Memoria Para Soporte de Cache 2. Memorias de Varias Palabras de Ancho Þ Ancho de Palabra Mayor Þ Bus Ancho Permite Transferir Bloque Completo en un Acceso Þ Costo Alto 16

Arquitectura y Organización de Computadores Organización de Memoria Para Soporte de Cache 3. Memorias Entrelazadas Þ Memoria Ancha Þ Bus de Ancho Normal Þ Lectura Simultánea a las Memorias Þ Acceso Segmentado Para la Transferencia 17

Arquitectura y Organización de Computadores Memoria Virtual Problemas de la Memoria Principal Þ Cada Programa Maneja un Espacio de Memoria Independiente Þ La Suma de los Espacios de Memoria Activos es Muy Grande Motivaciones Para Estudiar la Memoria Virtual 1. Permitir Compartir Eficientemente la Memoria Entre Diversos Programas 2. Eliminar los Problemas que Presenta una Memoria Pequeña y Limitada Memoria Virtual Hace Creer a los Programas que Existe una Memoria Principal de Gran Tamaño Explota Localidad de Acceso A Través de la Jerarquía de Memoria Simplifica el Manejo de Memoria Ventajas Principales de la Memoria Virtual 1. Permite una Traducción de Direcciones Simple y Eficiente 2. Permite Crear Instancias de Memoria Compartida 3. Permite Establecer Esquemas de Protección de Memoria 18

Arquitectura y Organización de Computadores Funcionamiento de la Memoria Virtual La Memoria Principal Almacena Sólo los Datos/Instrucciones Más Utilizados El Resto de los Datos/Instrucciones Residen en Memoria Secundaria (Disco) O Sea, la Memoria Actúa Como Cache de la Información Residente en el Disco Para Tomar Ventaja de la Localidad Espacial, la Memoria es Dividida en Bloques, que en la Terminología de Memoria Virtual Se Llaman Páginas Todas las Transferencias Entre Memoria Real y Disco Se Hacen Con Páginas 19

Arquitectura y Organización de Computadores Funcionamiento de la Memoria Virtual Hay Dos Tipos de Direcciones: las de Memoria Virtual y las de Memoria Física Por lo Tanto, Se Hace Necesaria una Traducción de Direcciones. Estos Tipos de Direcciones Permiten que los Programas Posean Espacios de Memoria Independientes. Así: 1. Las Direcciones Generadas por Programas en Ejecución son Direcciones Virtuales 2. Estas Direcciones Son Traducidas a Direcciones de Memoria Real 20

Arquitectura y Organización de Computadores Funcionamiento de la Memoria Virtual La Traducción de Direcciones Se Realiza A Través de Tablas de Páginas Estas Tablas Indican: 1. Si la Página Está en Memoria Real o Hay que Traerla de Disco 2. Cual es la Dirección en Memoria Real 3. Establecen Algunos Permisos de Acceso Para un Mejor Desempeño las Tablas de Páginas Residen en Memoria La Traducción y Validación de Acceso Es Realizada por Hardware en la Unidad de Manejo de Memoria (Memory Management Unit) 21

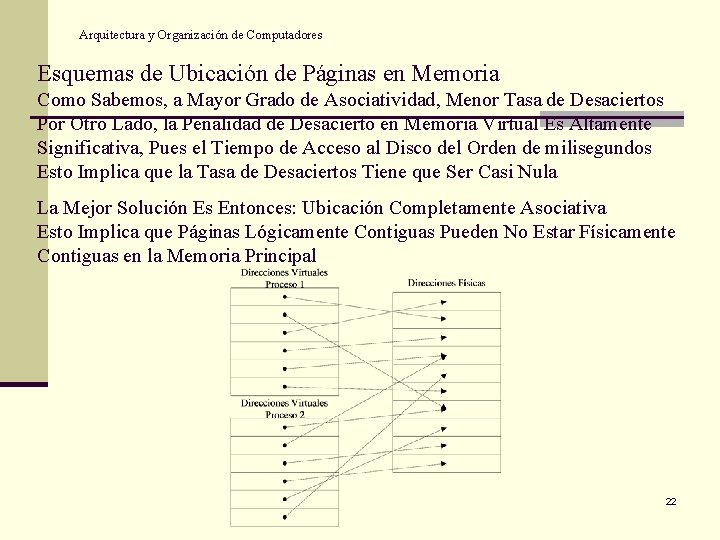

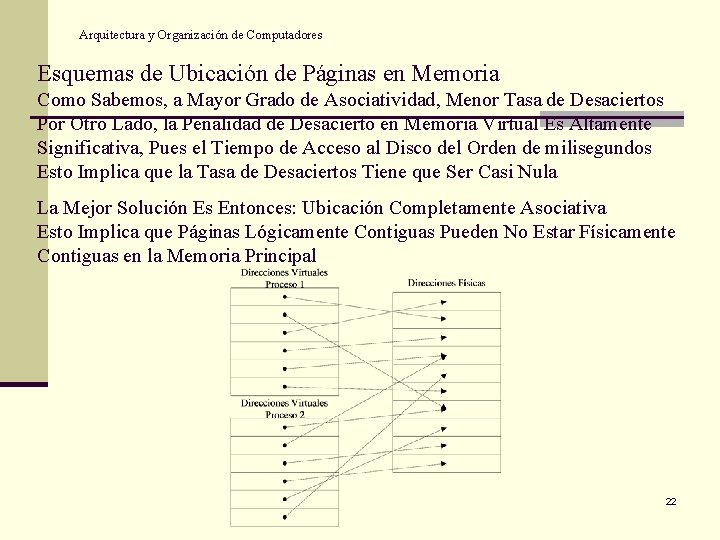

Arquitectura y Organización de Computadores Esquemas de Ubicación de Páginas en Memoria Como Sabemos, a Mayor Grado de Asociatividad, Menor Tasa de Desaciertos Por Otro Lado, la Penalidad de Desacierto en Memoria Virtual Es Altamente Significativa, Pues el Tiempo de Acceso al Disco del Orden de milisegundos Esto Implica que la Tasa de Desaciertos Tiene que Ser Casi Nula La Mejor Solución Es Entonces: Ubicación Completamente Asociativa Esto Implica que Páginas Lógicamente Contiguas Pueden No Estar Físicamente Contiguas en la Memoria Principal 22

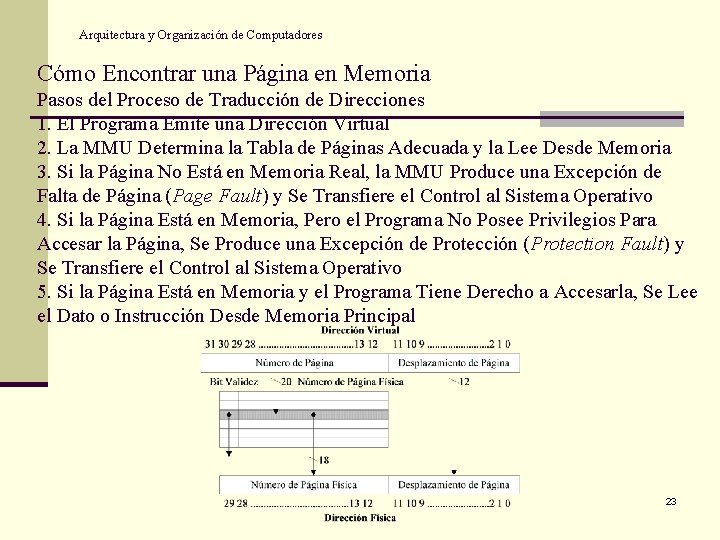

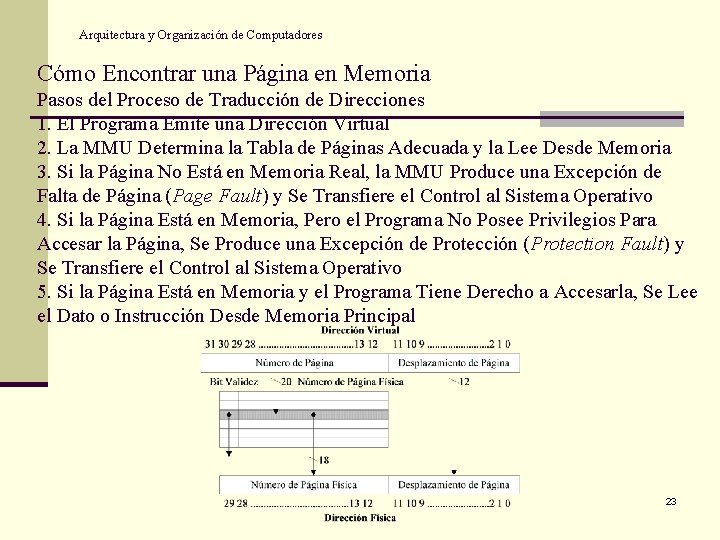

Arquitectura y Organización de Computadores Cómo Encontrar una Página en Memoria Pasos del Proceso de Traducción de Direcciones 1. El Programa Emite una Dirección Virtual 2. La MMU Determina la Tabla de Páginas Adecuada y la Lee Desde Memoria 3. Si la Página No Está en Memoria Real, la MMU Produce una Excepción de Falta de Página (Page Fault) y Se Transfiere el Control al Sistema Operativo 4. Si la Página Está en Memoria, Pero el Programa No Posee Privilegios Para Accesar la Página, Se Produce una Excepción de Protección (Protection Fault) y Se Transfiere el Control al Sistema Operativo 5. Si la Página Está en Memoria y el Programa Tiene Derecho a Accesarla, Se Lee el Dato o Instrucción Desde Memoria Principal 23

Arquitectura y Organización de Computadores Esquemas de Reemplazo de Páginas en Memoria Como la Penalidad de Desacierto es Tan Grande, Es Crítico Elegir la Página que Causará la Menor Tasa de Desaciertos Algoritmos Utilizados 1. Página Menos Recientemente Usada (LRU) Es una Buena Aproximación al Óptimo, Pues la Página Menos Recientemente Utilizada Probablemente No Será Referenciada en el Futuro Cercano. Esta Solución Requiere Mantener una Lista de Páginas en Memoria Ordenada Por Tiempo de Última Referencia lo que es Difícil de Implementar por Hardware 2. Primera en Entrar, Primera en Salir (FIFO) Implica Reemplazar la Página Más Antigua, lo que es Fácil de Implementar, Pero Tiene el Inconveniente de que no Reconoce la Localidad Temporal 3. Página No Recientemente Usada (NRU) Implica Tener un Bit de Referencia Asociado a Cada Página y Manejado por la MMU. Se Coloca el Bit en 1 Cada Vez que la Página es Referenciada y Cada Cierto Tiempo Todos los Bits de Referencia se Ponen en 0. La Página a Reemplazar es la que Tiene el Bit de Referencia en 0 24

Arquitectura y Organización de Computadores Esquemas de Manejo de Escritura en Memoria Al Igual que en las Caches Existen Dos Alternativas 1. Escritura Sincronizada (Write-Through): Escribir en Memoria y en Disco Cada Vez que se Hace una Escritura 2. Escritura Asincrónica (Write-Back): Escribir Sólo en Memoria y Respaldar en el Disco al Reemplazar la Página La Opción Elegida en Memoria Virtual es la Escritura Asincrónica Como el Acceso al Disco es Tan Lento, No Resulta Práctico Ejecutar una Copia Sincronizada del Contenido de la Memoria. Además, el Acceso a Disco Se Realiza Siempre por Bloques, lo que Hace Más Cómoda la Escritura Asincrónica Requerimientos de la Escritura Asincrónica El Sistema Operativo Debe Conocer Cuándo los Contenidos de una Página que Está en Memoria Han Sido Modificados Pues Éstos Deben Ser Escritos en el Disco Antes de Reemplazar la Página. Se Agrega un Bit de Modificación (Dirty Bit) por Cada Página en Memoria, que Mantenido por la MMU. El Bit de Modificación Es Puesto en 1 Cada Vez que el 25 Programa Escribe en la Página

Arquitectura y Organización de Computadores Implementación Hardware de la Traducción de Direcciones El Costo en Memoria de las Tabla de Páginas Puede Llegar a Ser Bastante Alto Ejemplo: Se Tienen Direcciones Virtuales de 32 Bits, Con Páginas de 4 Kbytes ¿Cuál es la Cantidad de Bytes Utilizada Por la Tabla de Páginas? Pero se Debe Recordar que los Programas No Ocupan Todo el Espacio de Memoria Virtual. Lo Típico, Es que se Utilicen Algunas Páginas de Direcciones Bajas y Algunas Páginas de Direcciones Altas. Existen Básicamente Tres Soluciones Utilizadas. 1. Tabla de Páginas Invertida En Vez de Tener una Entrada por Cada Página Virtual, Se Tiene una Entrada Por Cada Página de Memoria Real Cada Entrada Contiene Bits de Referencia, de Modificación, los Permisos y el Número de Página Virtual Correspondiente Esta Tabla Está Organizada Como una Tabla Hash y es Indexada Por el Número de Página Virtual 26

Arquitectura y Organización de Computadores Implementación Hardware de la Traducción de Direcciones 2. Segmentar el Espacio de Direcciones Virtuales Esto es Dividir el Espacio de Memoria Virtual en Dos Segmentos: a) Direcciones Altas: Identificadas por Bit Más Significativo de Dirección en 1 b) Direcciones Bajas: Identificadas por Bit Más Significativo de Dirección en 0 Se Mantiene Una Tabla de Páginas Por Segmento y Estas Tablas Son del Tamaño Real del Segmento Con Esto, el Espacio Ocupado Por la Tabla Corresponde Sólo a Memoria Efectivamente Usada por Programa 27

Arquitectura y Organización de Computadores Implementación Hardware de la Traducción de Direcciones 3. Tablas de Páginas Jerárquicas Existen Tablas de Páginas Raíz en el Espacio de Memoria Real que Apuntan a Tablas de Segundo Nivel en el Espacio de Memoria Virtual del Sistema Operativo Las Tablas de Segundo Nivel Contienen Información de Páginas. Todas las Tablas, Excepto las Tablas Raíz Pueden Ser Paginadas a Disco Las Tablas Más Utilizadas Permanecen en Memoria Principal El Acceso a Tabla de Segundo Nivel También Puede Provocar una Segunda Falta de Página, Por lo que es Necesario Tomar Precauciones Para Evitar una Cadena de Faltas de Página 28

Arquitectura y Organización de Computadores Desempeño de la Traducción de Direcciones Cada Traducción de Direcciones Implica al Menos un Acceso a Memoria Adicional, Producto del Acceso a Tablas de Páginas y al Retardo Asociado a la Formación de la Dirección Real y Detección de un Acierto o Desacierto Los Esquemas Más Sofisticados Incrementan Aún Más la Cantidad de Accesos Adicionales a Memoria Con Todo Esto el CPI Aumenta y Se Degrada Considerablemente el Desempeño Pero Se Puede Utilizar la Localidad de la Traducción de Direcciones Para Mejorar el Desempeño: Buffer de Direcciones (TLB) El Concepto de Buffer de Direcciones (TLB) Implica que Existe una Memoria Cache Especializada que Mantiene la Dirección Real de las Últimas Páginas Virtuales Accesadas El Desempeño del TLB es Crítico Requiere una Alta Razón de Acierto, por lo que Normalmente Se Organiza Completamente Asociativo El Tamaño de un TLB es de: 64 (MIPS R 10000) - 128 (AMD K 5) Entradas 29

Arquitectura y Organización de Computadores Cache y Memoria Virtual ¿Sobre qué Espacio de Direcciones se Proyecta la Cache? 1. Cache Indexada con Direcciones Virtuales Es Accesado con Direcciones Generadas Directamente de las Instrucciones, Por lo que Resulta Ser Más Rápido. Existen Conflictos con Direcciones Virtuales de Diferentes Programas Resulta Necesario Vaciar la Cache al Cambiar de Contexto 2. Cache Indexada con Direcciones Reales Es Accesado con Direcciones a la Salida de TLB, Resulta Ser Más Lento Pues Debe Traducir Antes de Accesar. Las Direcciones Reales no Provocan Conflictos en la Cache y el Esquema es Más Sencillo de Manejar 3. Acceso al TLB Traslapado con Acceso a Cache La Cache es Indexada con una Dirección Virtual, el Tag Incluye la Dirección Real El Acceso a Cache Se Realiza en Paralelo con Acceso a TLB, Usando la Dirección Virtual. Se Compara el Tag y la Dirección Real de Bloque Determina un Acierto o Desacierto 30