Architecture des ordinateurs cours 3 Microinstructions et unit

![change(int v [], int k) { int tmp; tmp = v[k]; v[k] = v[k+1]; change(int v [], int k) { int tmp; tmp = v[k]; v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h/33ab832df812b5512c35e66511aeb1ce/image-19.jpg)

- Slides: 36

Architecture des ordinateurs cours 3 Micro-instructions et unité de contrôle, langage machine, langage d’assemblage, modes d’adressage Agata Savary, IUT de Blois, Département GTR, 1 e année, 2004 -2005 A. SAVARY IUT Blois GTR 1, 2004/05

Micro-instructions Unité de contrôle A. SAVARY IUT Blois GTR 1, 2004/05 2

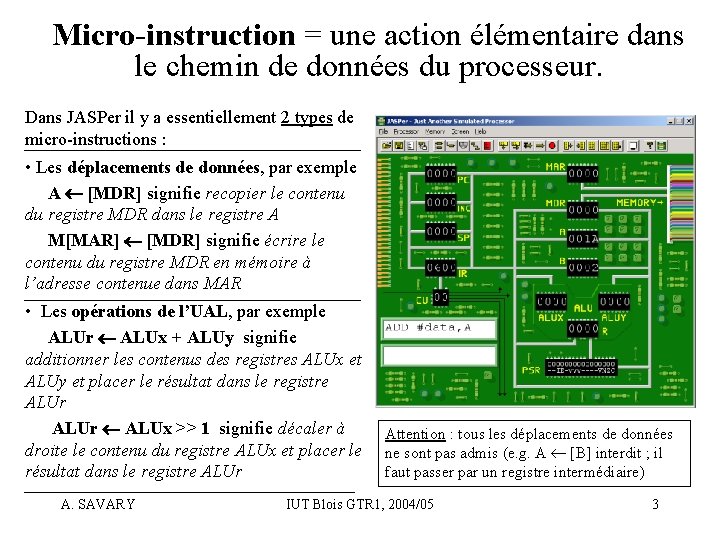

Micro-instruction = une action élémentaire dans le chemin de données du processeur. Dans JASPer il y a essentiellement 2 types de micro-instructions : • Les déplacements de données, par exemple A [MDR] signifie recopier le contenu du registre MDR dans le registre A M[MAR] [MDR] signifie écrire le contenu du registre MDR en mémoire à l’adresse contenue dans MAR • Les opérations de l’UAL, par exemple ALUr ALUx + ALUy signifie additionner les contenus des registres ALUx et ALUy et placer le résultat dans le registre ALUr ALUx >> 1 signifie décaler à droite le contenu du registre ALUx et placer le résultat dans le registre ALUr A. SAVARY Attention : tous les déplacements de données ne sont pas admis (e. g. A [B] interdit ; il faut passer par un registre intermédiaire) IUT Blois GTR 1, 2004/05 3

Les micro-instructions sont provoquées par l’unité de contrôle • L’unité de contrôle analyse le code de l’instruction machine courante (contenue dans le registre IR). • Elle décode cette instruction, i. e. détermine quelles micro-instructions doivent être effectuées dans quel ordre pour exécuter l’instruction courante • Elle envoie des signaux de contrôle au chemin de données pour imposer les micro-instructions nécessaire (par les lignes oranges du cours précédent: Contrôle. UAL, Aou. B, Vers. Aou. B, Ecrire. AB, …) “La mise en oeuvre de l’unité de contrôle est la tâche la plus difficile de toute la conception matérielle” (Patterson, Hennessy Organisation et conception des ordinateurs) … c’est pourquoi nous n’allons pas l’examiner plus en détail pendant ce cours A. SAVARY IUT Blois GTR 1, 2004/05 4

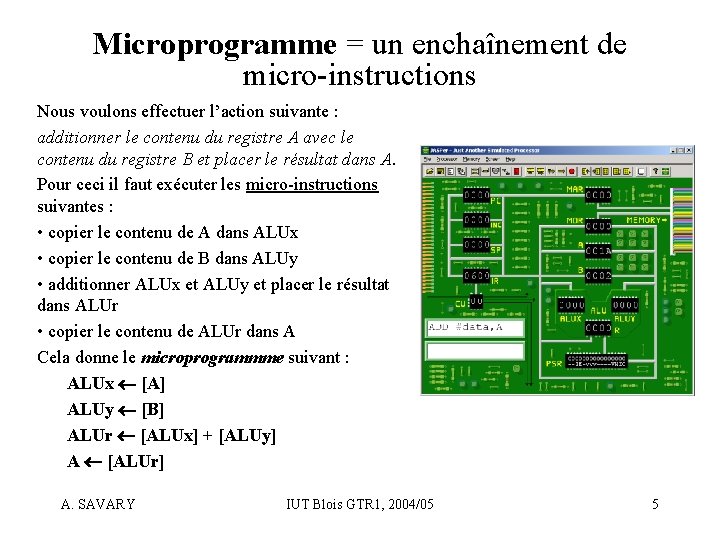

Microprogramme = un enchaînement de micro-instructions Nous voulons effectuer l’action suivante : additionner le contenu du registre A avec le contenu du registre B et placer le résultat dans A. Pour ceci il faut exécuter les micro-instructions suivantes : • copier le contenu de A dans ALUx • copier le contenu de B dans ALUy • additionner ALUx et ALUy et placer le résultat dans ALUr • copier le contenu de ALUr dans A Cela donne le microprogrammme suivant : ALUx [A] ALUy [B] ALUr [ALUx] + [ALUy] A [ALUr] A. SAVARY IUT Blois GTR 1, 2004/05 5

machine language Langage machine et langage d’assemblage assembly language A. SAVARY IUT Blois GTR 1, 2004/05 6

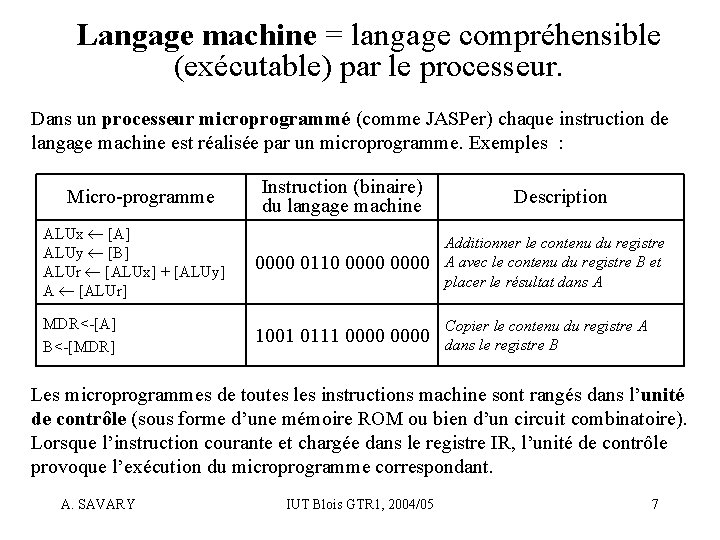

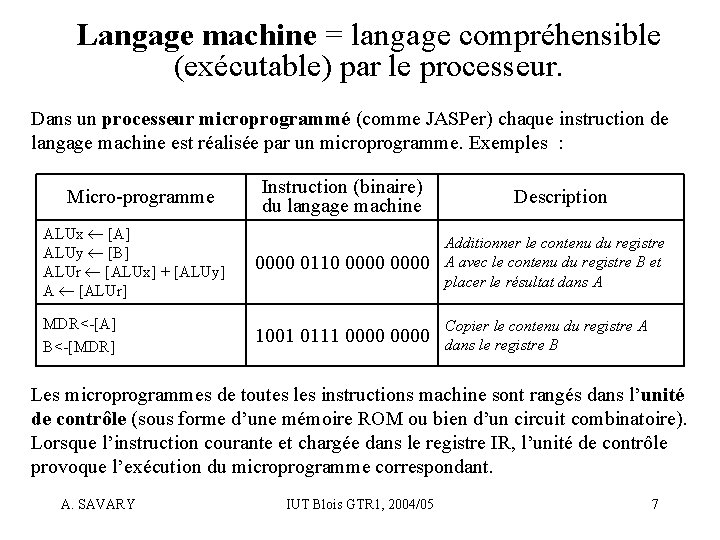

Langage machine = langage compréhensible (exécutable) par le processeur. Dans un processeur microprogrammé (comme JASPer) chaque instruction de langage machine est réalisée par un microprogramme. Exemples : Micro-programme Instruction (binaire) du langage machine Description ALUx [A] ALUy [B] ALUr [ALUx] + [ALUy] A [ALUr] 0000 0110 0000 Additionner le contenu du registre A avec le contenu du registre B et placer le résultat dans A MDR<-[A] B<-[MDR] 1001 0111 0000 Copier le contenu du registre A dans le registre B Les microprogrammes de toutes les instructions machine sont rangés dans l’unité de contrôle (sous forme d’une mémoire ROM ou bien d’un circuit combinatoire). Lorsque l’instruction courante et chargée dans le registre IR, l’unité de contrôle provoque l’exécution du microprogramme correspondant. A. SAVARY IUT Blois GTR 1, 2004/05 7

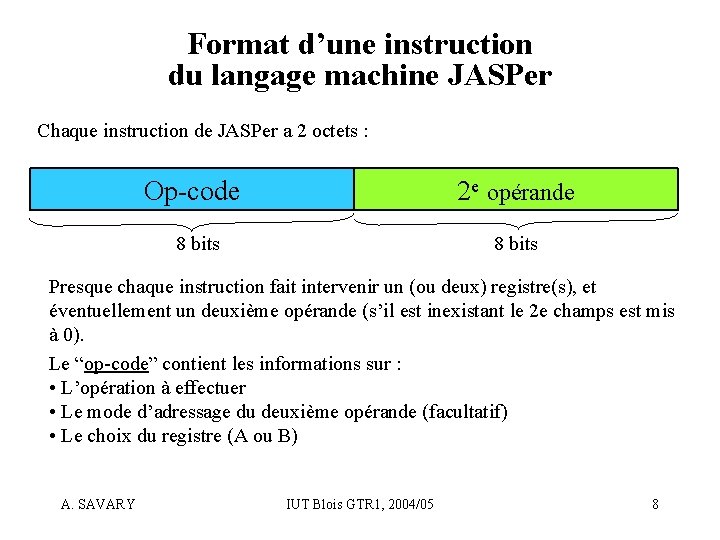

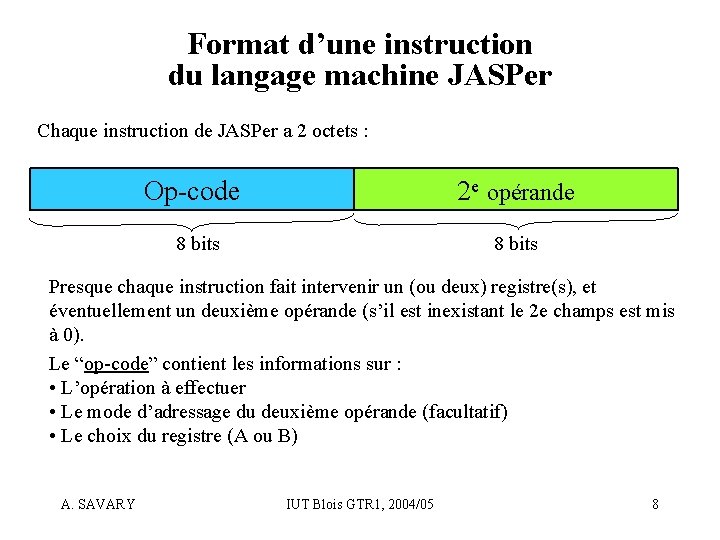

Format d’une instruction du langage machine JASPer Chaque instruction de JASPer a 2 octets : Op-code 2 e opérande 8 bits Presque chaque instruction fait intervenir un (ou deux) registre(s), et éventuellement un deuxième opérande (s’il est inexistant le 2 e champs est mis à 0). Le “op-code” contient les informations sur : • L’opération à effectuer • Le mode d’adressage du deuxième opérande (facultatif) • Le choix du registre (A ou B) A. SAVARY IUT Blois GTR 1, 2004/05 8

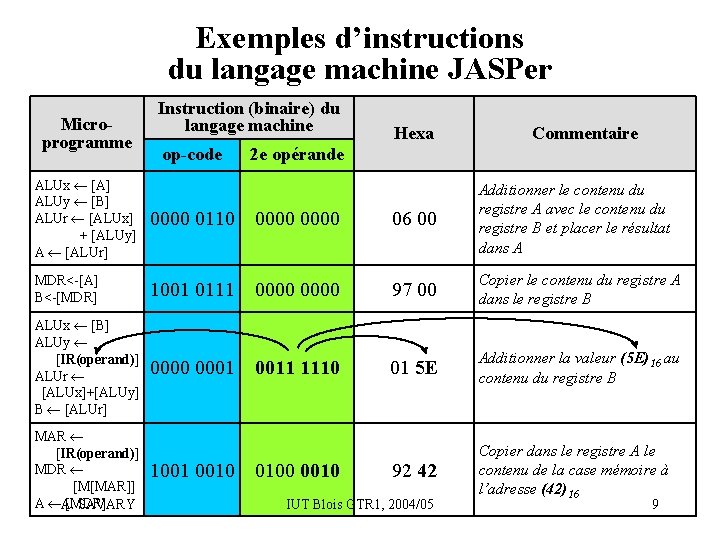

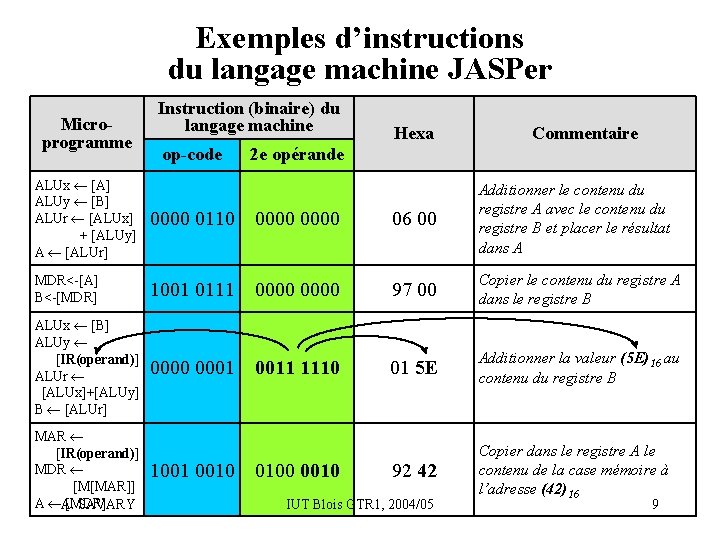

Exemples d’instructions du langage machine JASPer Microprogramme Instruction (binaire) du langage machine op-code Hexa Commentaire 2 e opérande ALUx [A] ALUy [B] ALUr [ALUx] + [ALUy] A [ALUr] 0000 0110 0000 06 00 Additionner le contenu du registre A avec le contenu du registre B et placer le résultat dans A MDR<-[A] B<-[MDR] 1001 0111 0000 97 00 Copier le contenu du registre A dans le registre B ALUx [B] ALUy [IR(operand)] ALUr [ALUx]+[ALUy] B [ALUr] 0000 0001 0011 1110 01 5 E Additionner la valeur (5 E)16 au contenu du registre B 92 42 Copier dans le registre A le contenu de la case mémoire à l’adresse (42)16 MAR [IR(operand)] MDR [M[MAR]] A A. [MDR] SAVARY 1001 0010 0100 0010 IUT Blois GTR 1, 2004/05 9

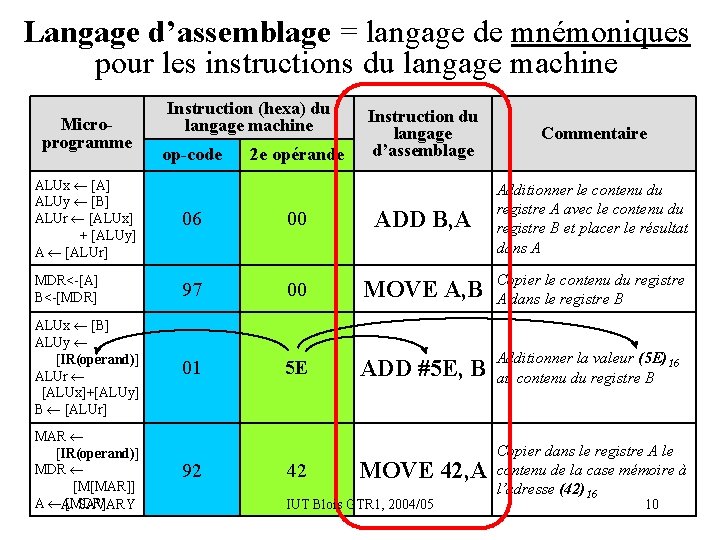

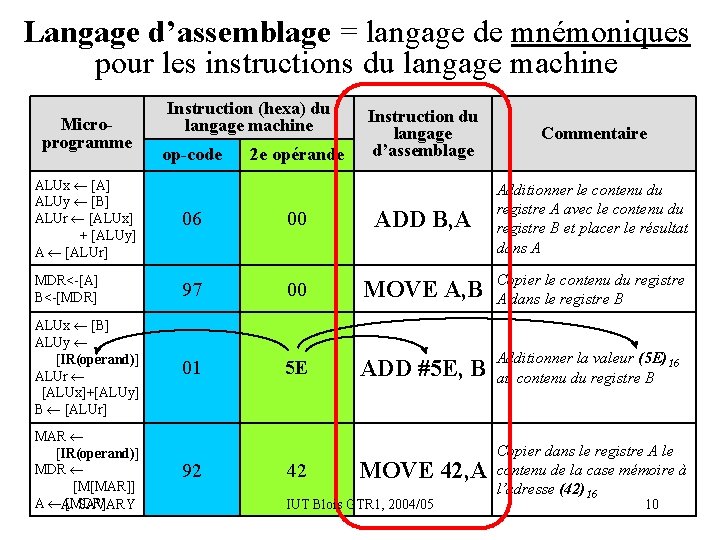

Langage d’assemblage = langage de mnémoniques pour les instructions du langage machine Microprogramme Instruction (hexa) du langage machine op-code 2 e opérande Instruction du langage d’assemblage Commentaire ALUx [A] ALUy [B] ALUr [ALUx] + [ALUy] A [ALUr] 06 00 ADD B, A Additionner le contenu du registre A avec le contenu du registre B et placer le résultat dans A MDR<-[A] B<-[MDR] 97 00 MOVE A, B Copier le contenu du registre A dans le registre B ALUx [B] ALUy [IR(operand)] ALUr [ALUx]+[ALUy] B [ALUr] 01 5 E ADD #5 E, B Additionner la valeur (5 E)16 au contenu du registre B MOVE 42, A Copier dans le registre A le contenu de la case mémoire à l’adresse (42)16 MAR [IR(operand)] MDR [M[MAR]] A A. [MDR] SAVARY 92 42 IUT Blois GTR 1, 2004/05 10

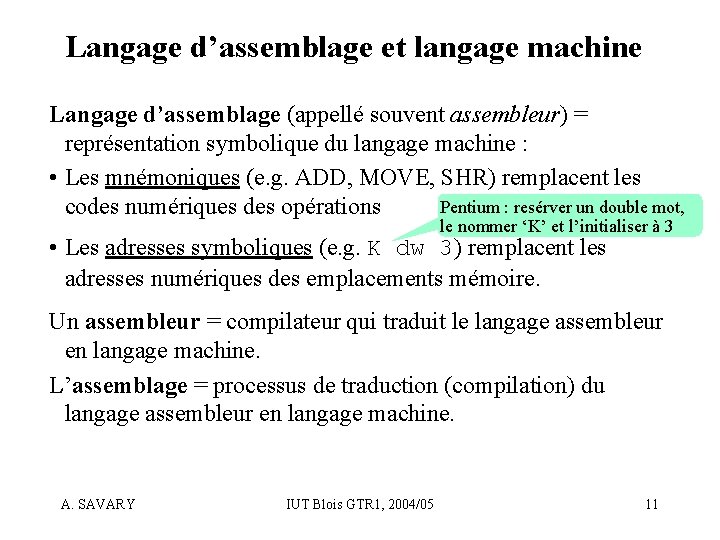

Langage d’assemblage et langage machine Langage d’assemblage (appellé souvent assembleur) = représentation symbolique du langage machine : • Les mnémoniques (e. g. ADD, MOVE, SHR) remplacent les Pentium : resérver un double mot, codes numériques des opérations le nommer ‘K’ et l’initialiser à 3 • Les adresses symboliques (e. g. K dw 3) remplacent les adresses numériques des emplacements mémoire. Un assembleur = compilateur qui traduit le langage assembleur en langage machine. L’assemblage = processus de traduction (compilation) du langage assembleur en langage machine. A. SAVARY IUT Blois GTR 1, 2004/05 11

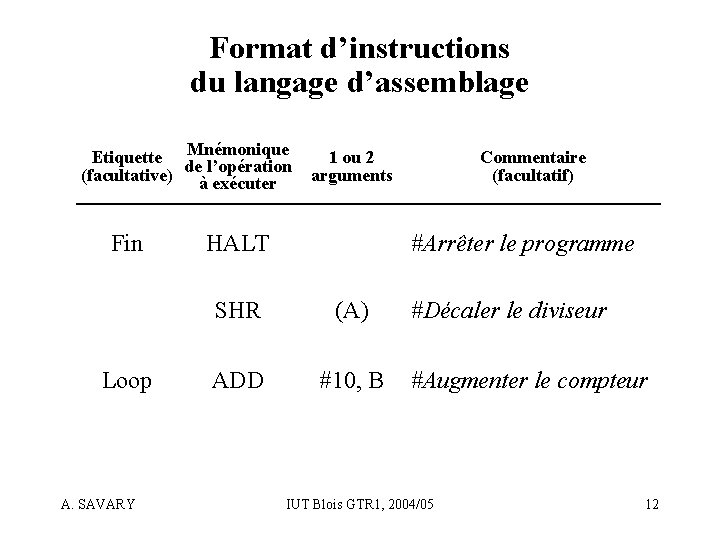

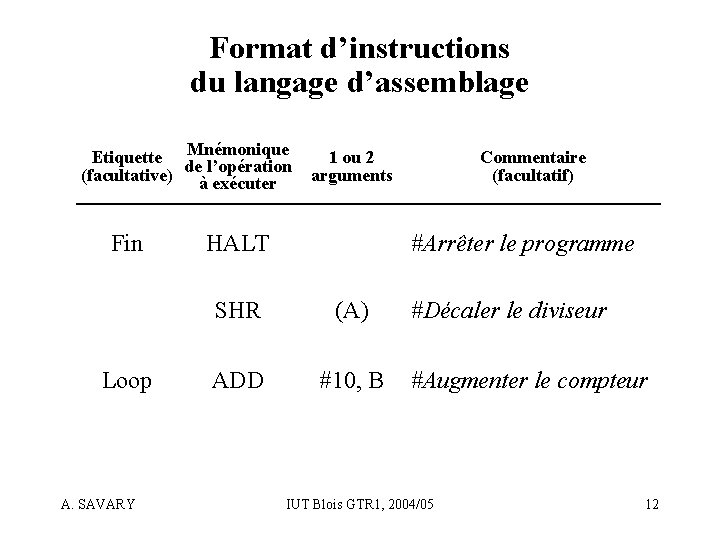

Format d’instructions du langage d’assemblage Mnémonique Etiquette de (facultative) àl’opération exécuter Fin Loop A. SAVARY 1 ou 2 arguments HALT Commentaire (facultatif) #Arrêter le programme SHR (A) ADD #10, B #Décaler le diviseur #Augmenter le compteur IUT Blois GTR 1, 2004/05 12

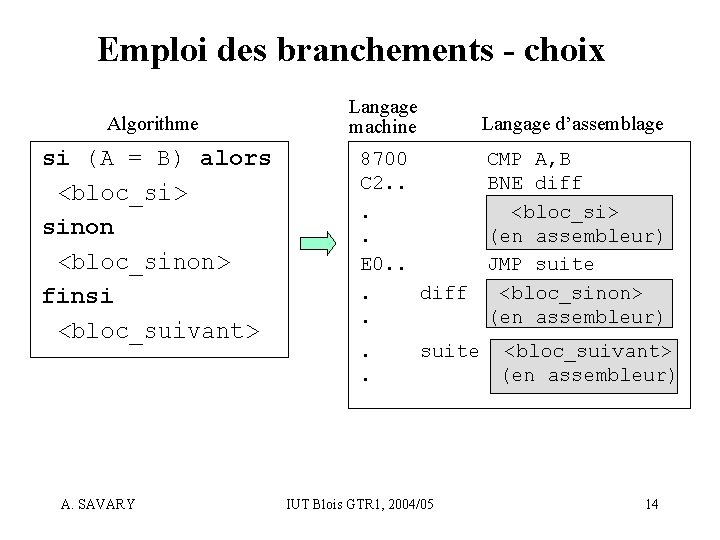

Langage de haut niveau vs. langage d’assemblage. A. SAVARY IUT Blois GTR 1, 2004/05 13

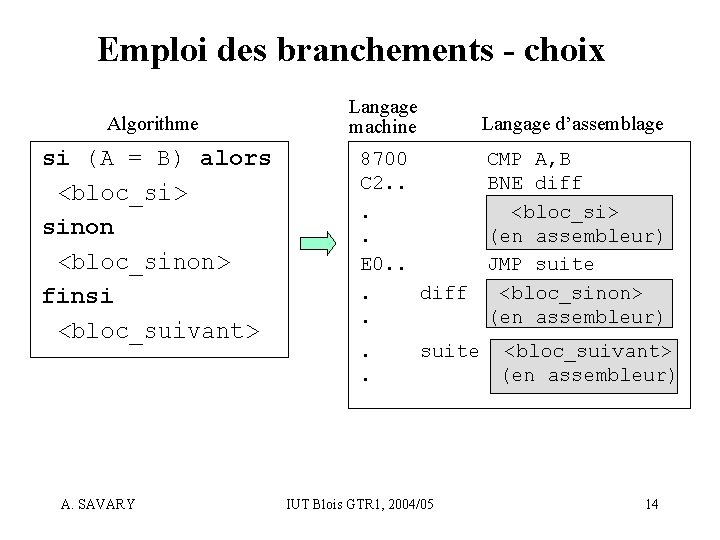

Emploi des branchements - choix Algorithme si (A = B) alors <bloc_si> sinon <bloc_sinon> finsi <bloc_suivant> A. SAVARY Langage machine Langage d’assemblage 8700 CMP A, B C 2. . BNE diff. <bloc_si>. (en assembleur) E 0. . JMP suite. diff <bloc_sinon>. (en assembleur). . suite IUT Blois GTR 1, 2004/05 <bloc_suivant> (en assembleur) 14

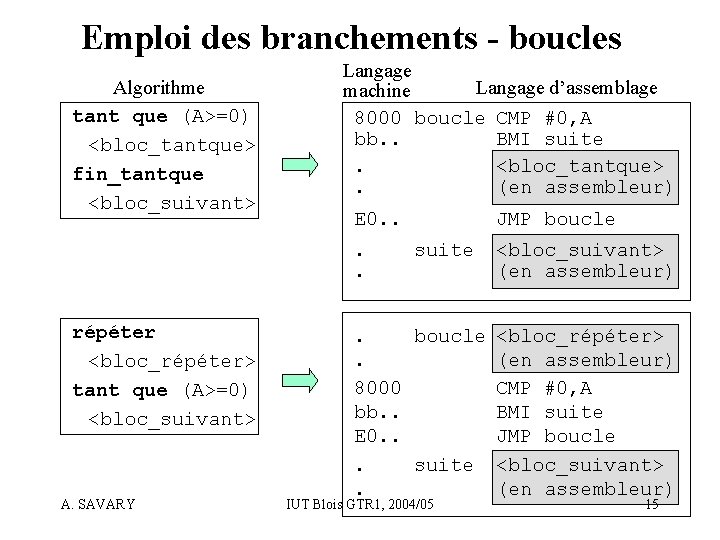

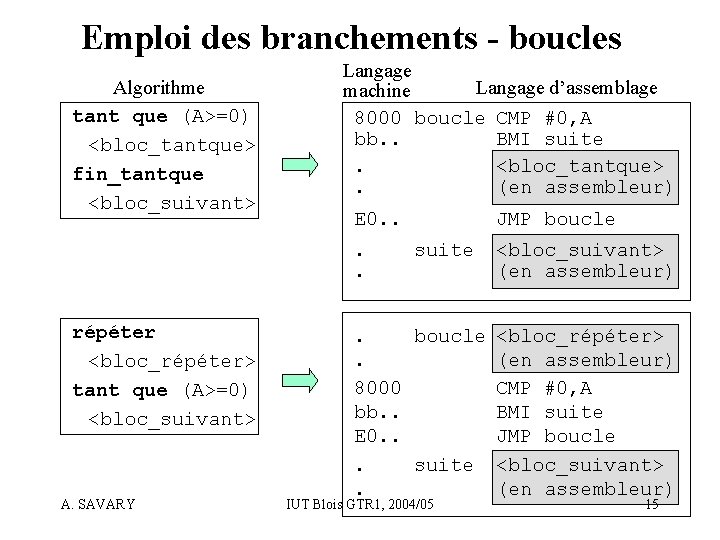

Emploi des branchements - boucles Algorithme tant que (A>=0) <bloc_tantque> fin_tantque <bloc_suivant> Langage d’assemblage machine 8000 boucle CMP #0, A bb. . BMI suite. <bloc_tantque>. (en assembleur) E 0. . répéter <bloc_répéter> tant que (A>=0) <bloc_suivant> A. SAVARY JMP boucle suite <bloc_suivant> (en assembleur) . boucle <bloc_répéter>. (en assembleur) 8000 CMP #0, A bb. . BMI suite E 0. . JMP boucle. suite <bloc_suivant>. (en assembleur) IUT Blois GTR 1, 2004/05 15

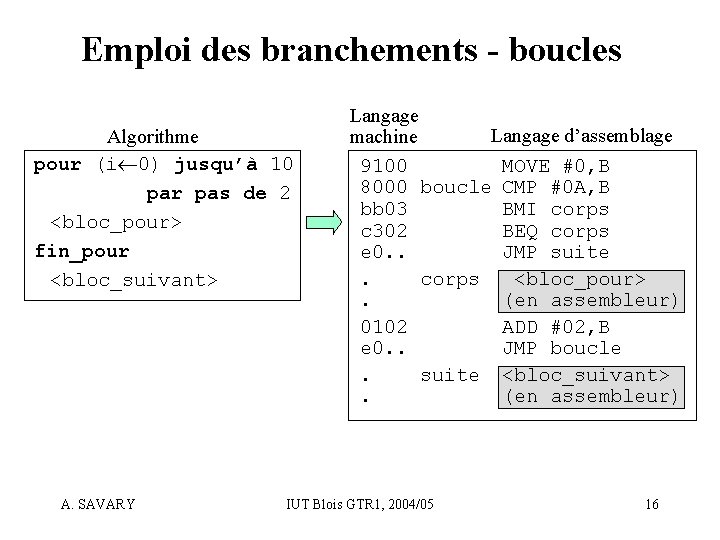

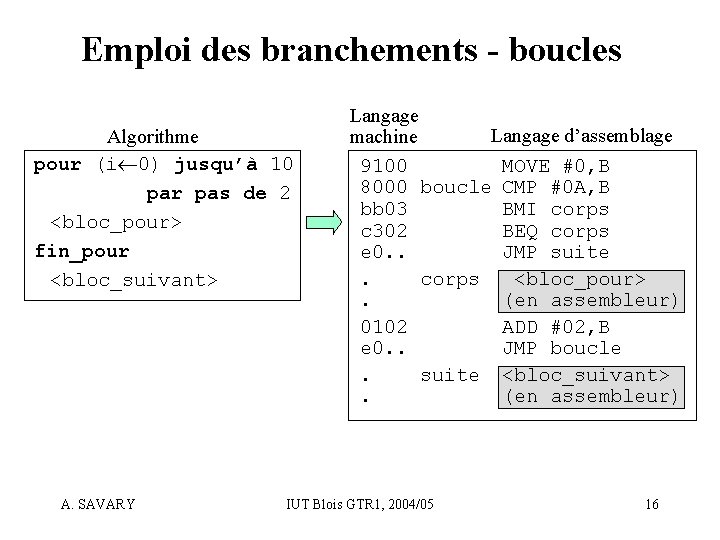

Emploi des branchements - boucles Algorithme pour (i 0) jusqu’à 10 par pas de 2 <bloc_pour> fin_pour <bloc_suivant> A. SAVARY Langage d’assemblage machine 9100 MOVE #0, B 8000 boucle CMP #0 A, B bb 03 BMI corps c 302 BEQ corps e 0. . JMP suite. corps <bloc_pour>. (en assembleur) 0102 ADD #02, B e 0. . JMP boucle. suite <bloc_suivant>. (en assembleur) IUT Blois GTR 1, 2004/05 16

Compilation et compatibilité A. SAVARY IUT Blois GTR 1, 2004/05 17

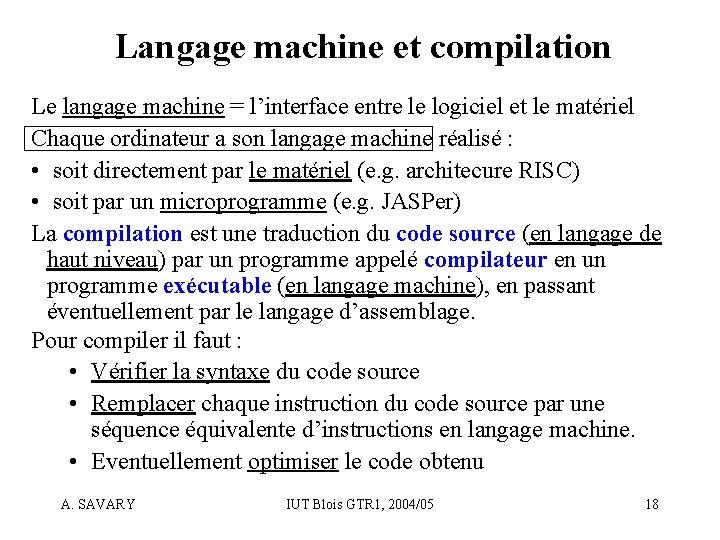

Langage machine et compilation Le langage machine = l’interface entre le logiciel et le matériel Chaque ordinateur a son langage machine réalisé : • soit directement par le matériel (e. g. architecure RISC) • soit par un microprogramme (e. g. JASPer) La compilation est une traduction du code source (en langage de haut niveau) par un programme appelé compilateur en un programme exécutable (en langage machine), en passant éventuellement par le langage d’assemblage. Pour compiler il faut : • Vérifier la syntaxe du code source • Remplacer chaque instruction du code source par une séquence équivalente d’instructions en langage machine. • Eventuellement optimiser le code obtenu A. SAVARY IUT Blois GTR 1, 2004/05 18

![changeint v int k int tmp tmp vk vk vk1 change(int v [], int k) { int tmp; tmp = v[k]; v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h/33ab832df812b5512c35e66511aeb1ce/image-19.jpg)

change(int v [], int k) { int tmp; tmp = v[k]; v[k] = v[k+1]; v[k+1] = tmp; Programme en langage de haut niveau, ici C (le “code source”) } Compilateur C change : MOVE adr_v, A ADD addr_k, A MOVE (A), B ADD #1, A MOVE B, (A) … A. SAVARY Compilateur C Programme en langage assembleur Assembleur IUT Blois GTR 1, 2004/05 Compilation en couches Programme en langage machine (l’“exécutable”) 0100011011010101 0010011110101101010010 1101001010100101111010000100110 …. 19

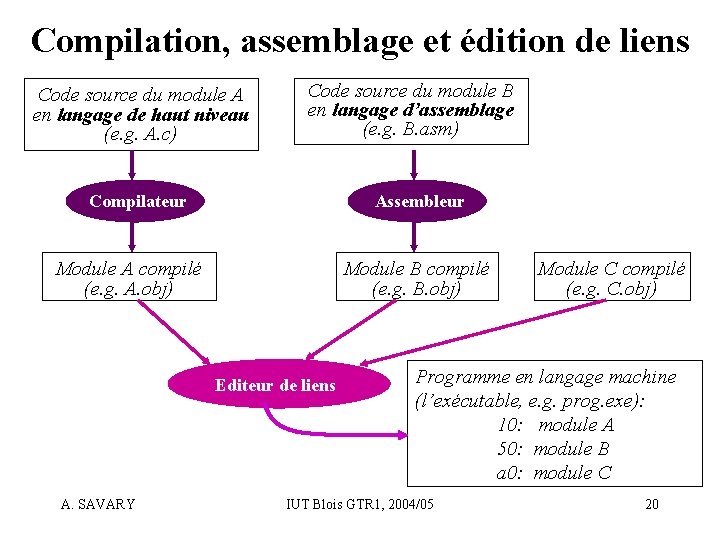

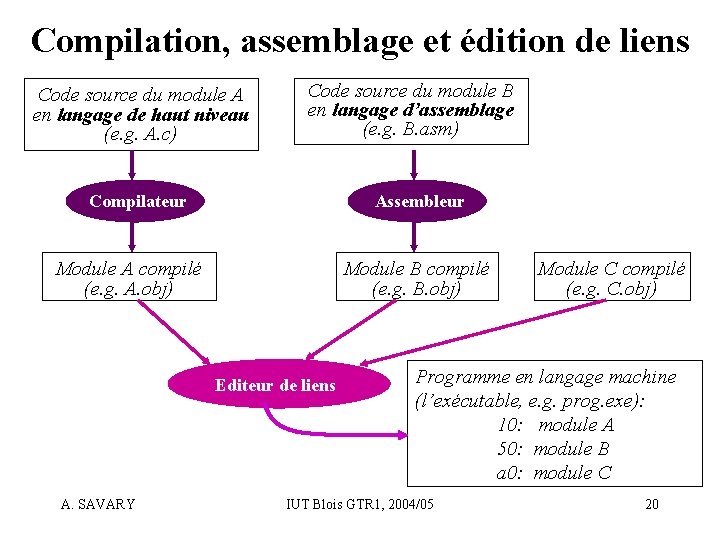

Compilation, assemblage et édition de liens Code source du module A en langage de haut niveau (e. g. A. c) Code source du module B en langage d’assemblage (e. g. B. asm) Compilateur Assembleur Module A compilé (e. g. A. obj) Module B compilé (e. g. B. obj) Editeur de liens A. SAVARY Module C compilé (e. g. C. obj) Programme en langage machine (l’exécutable, e. g. prog. exe): 10: module A 50: module B a 0: module C IUT Blois GTR 1, 2004/05 20

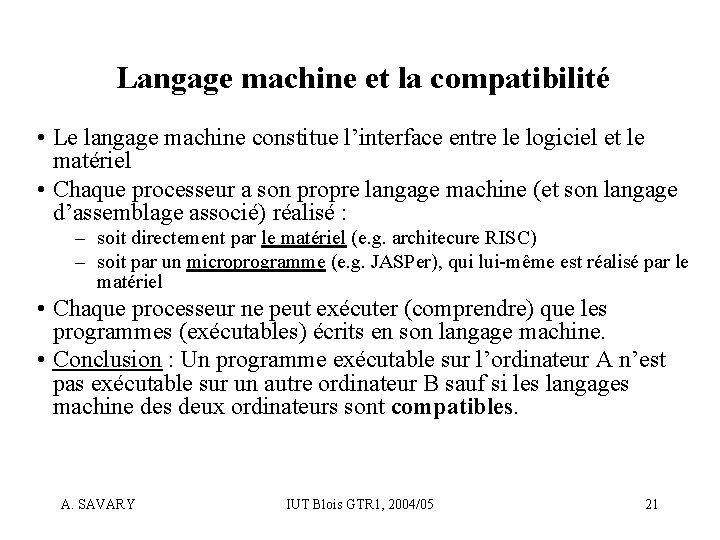

Langage machine et la compatibilité • Le langage machine constitue l’interface entre le logiciel et le matériel • Chaque processeur a son propre langage machine (et son langage d’assemblage associé) réalisé : – soit directement par le matériel (e. g. architecure RISC) – soit par un microprogramme (e. g. JASPer), qui lui-même est réalisé par le matériel • Chaque processeur ne peut exécuter (comprendre) que les programmes (exécutables) écrits en son langage machine. • Conclusion : Un programme exécutable sur l’ordinateur A n’est pas exécutable sur un autre ordinateur B sauf si les langages machine des deux ordinateurs sont compatibles. A. SAVARY IUT Blois GTR 1, 2004/05 21

Compatibilité ascendante des processeurs • Un nouveau processeur (machine) respecte la comptabilité ascendante si les applications qui tournaient sur l’ancienne machine peuvent tourner sur la nouvelle machine sans modification • Pour qu’il y ait comptabilité ascendante le langage machine du nouveau processeur doit au moins contenir toutes les instructions de l’ancien processeur. Elles peuvent être réalisées différemment mais doivent donner les mêmes résultats (i. e. doivent avoir la même interface). • Si manque de comptabilité ascendante, les anciens programmes doivent être soit recompilés (les codes sources doivent être disponibles), soit réécrits (e. g. s’ils ont été écrits en assembleur) Exemple : les processeurs Intel sont compatibles en amont depuis le modèle 8086 (sorti en 1978). A. SAVARY IUT Blois GTR 1, 2004/05 22

Compatibilité ascendante des processeurs La compatibilité ascendante est un poids lourd pour les concepteurs de nouveaux modèles de processeurs : • Il faut tenir compte de tous les choix faits pour la conception des langages machines tout au long de l’histoire de la gamme de machines en question. Ces choix, souvent, ne sont pas cohérents avec les besoins et les possibilités actuelles. • Du coup l’architecture est moins élégante et moins compacte (donc aussi moins performante) que si elle ne tenait compte que du langage machine le plus recent. • C’est pourquoi l’introduction d’une machine totalement nouvelle (malgré son manque de compatibilité ascendante) peut s’avérer très intéressante. Ceci a été le cas de l’architecture RISC qui a proposé un jeu d’instructions très simples, peu nombreuses et exécutables très rapidement, ce qui a provoqué un gain très important de performances. A. SAVARY IUT Blois GTR 1, 2004/05 23

Modes d’adressage A. SAVARY IUT Blois GTR 1, 2004/05 24

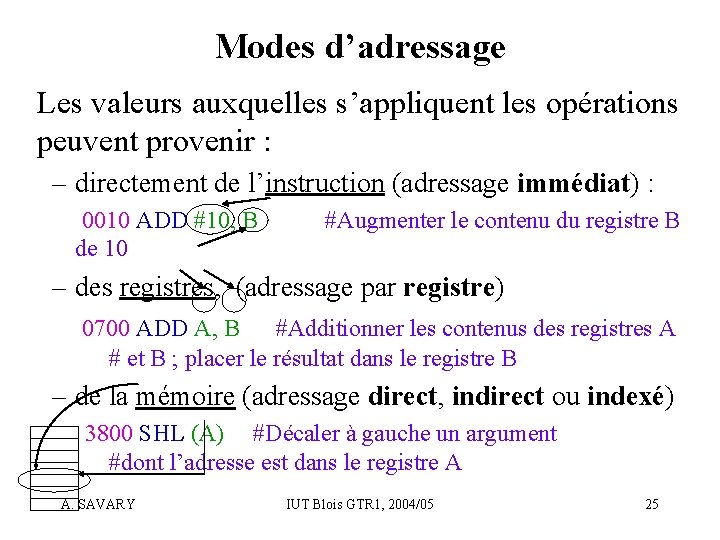

Modes d’adressage Les valeurs auxquelles s’appliquent les opérations peuvent provenir : – directement de l’instruction (adressage immédiat) : 0010 ADD #10, B de 10 #Augmenter le contenu du registre B – des registres, (adressage par registre) 0700 ADD A, B #Additionner les contenus des registres A # et B ; placer le résultat dans le registre B – de la mémoire (adressage direct, indirect ou indexé) 3800 SHL (A) #Décaler à gauche un argument #dont l’adresse est dans le registre A A. SAVARY IUT Blois GTR 1, 2004/05 25

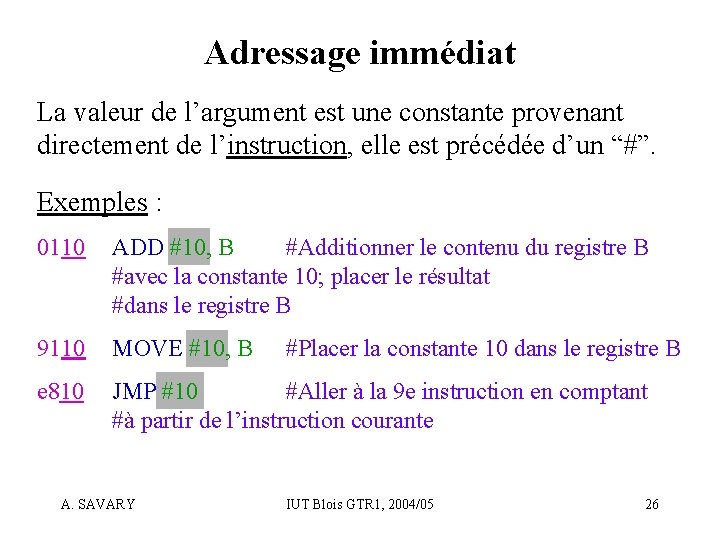

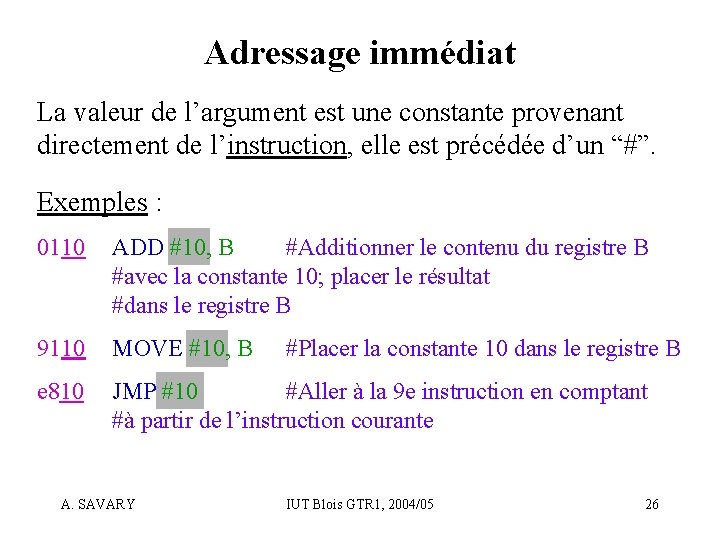

Adressage immédiat La valeur de l’argument est une constante provenant directement de l’instruction, elle est précédée d’un “#”. Exemples : 0110 ADD #10, B #Additionner le contenu du registre B #avec la constante 10; placer le résultat #dans le registre B 9110 MOVE #10, B e 810 JMP #10 #Aller à la 9 e instruction en comptant #à partir de l’instruction courante A. SAVARY #Placer la constante 10 dans le registre B IUT Blois GTR 1, 2004/05 26

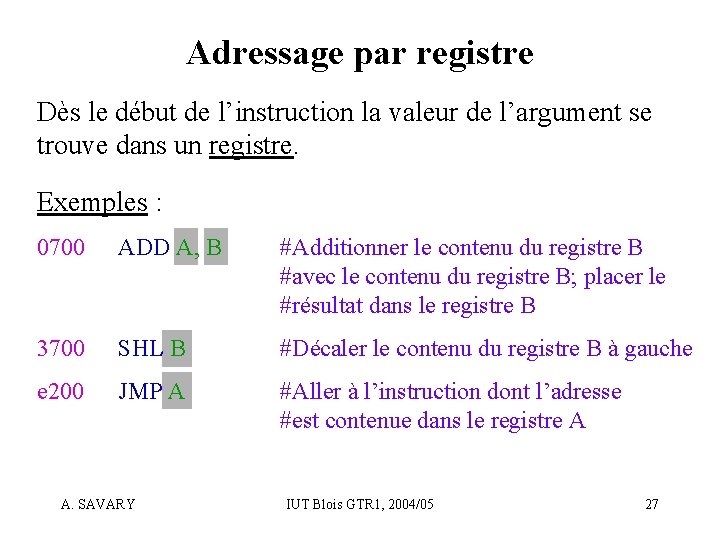

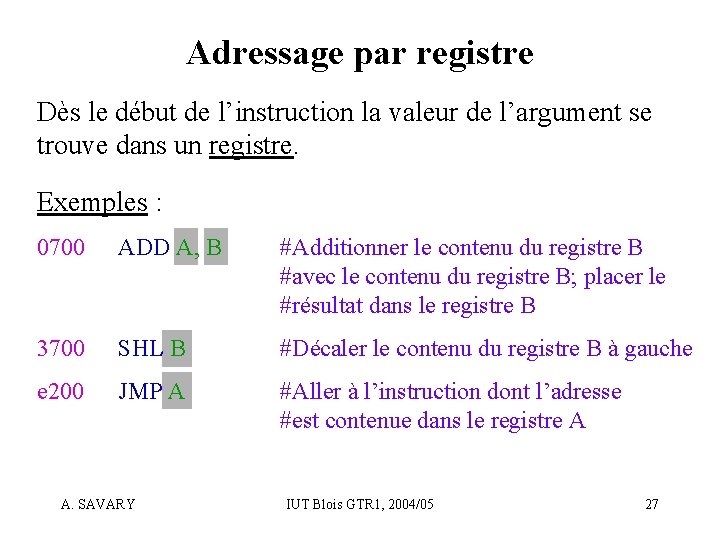

Adressage par registre Dès le début de l’instruction la valeur de l’argument se trouve dans un registre. Exemples : 0700 ADD A, B #Additionner le contenu du registre B #avec le contenu du registre B; placer le #résultat dans le registre B 3700 SHL B #Décaler le contenu du registre B à gauche e 200 JMP A #Aller à l’instruction dont l’adresse #est contenue dans le registre A A. SAVARY IUT Blois GTR 1, 2004/05 27

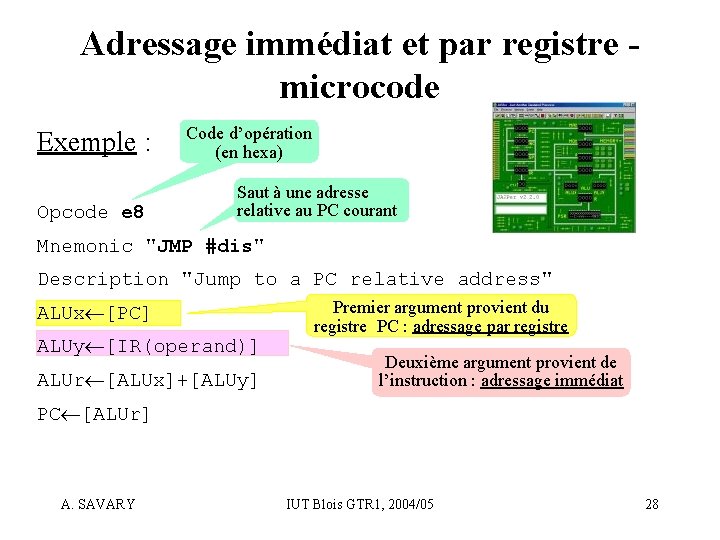

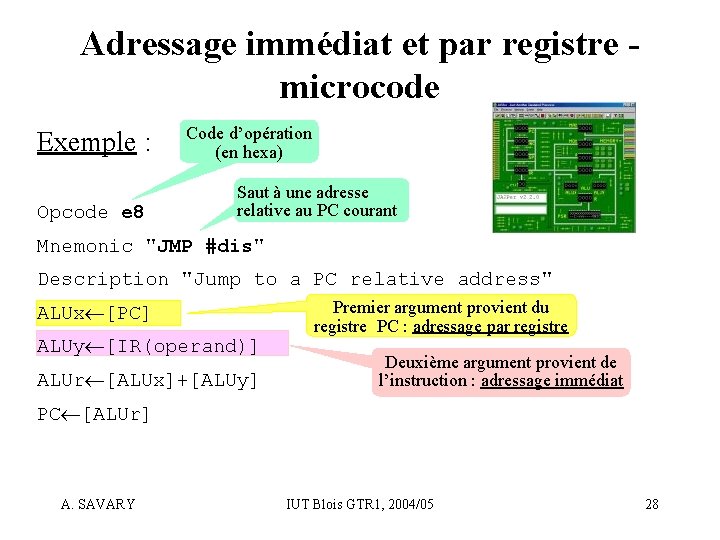

Adressage immédiat et par registre microcode Exemple : Opcode e 8 Code d’opération (en hexa) Saut à une adresse relative au PC courant Mnemonic "JMP #dis" Description "Jump to a PC relative address" ALUx [PC] ALUy [IR(operand)] ALUr [ALUx]+[ALUy] Premier argument provient du registre PC : adressage par registre Deuxième argument provient de l’instruction : adressage immédiat PC [ALUr] A. SAVARY IUT Blois GTR 1, 2004/05 28

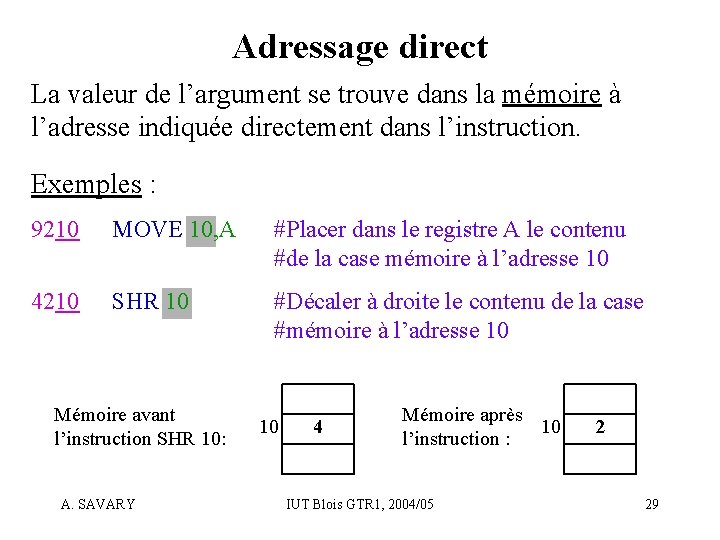

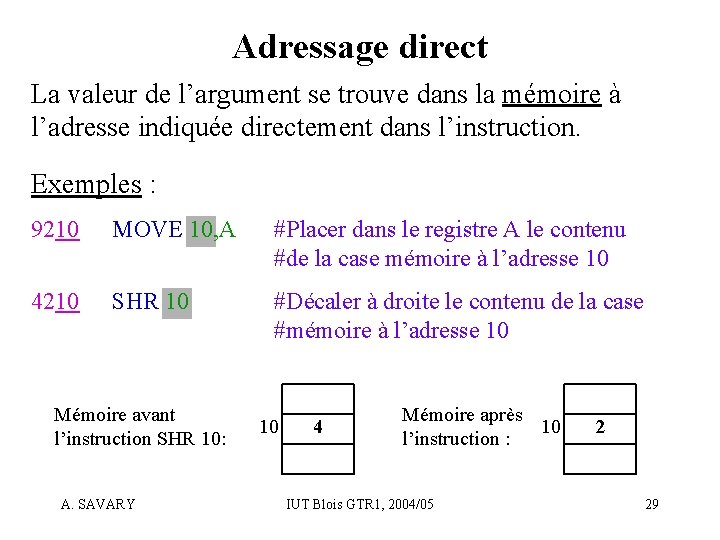

Adressage direct La valeur de l’argument se trouve dans la mémoire à l’adresse indiquée directement dans l’instruction. Exemples : 9210 MOVE 10, A #Placer dans le registre A le contenu #de la case mémoire à l’adresse 10 4210 SHR 10 #Décaler à droite le contenu de la case #mémoire à l’adresse 10 Mémoire avant l’instruction SHR 10: A. SAVARY 10 4 Mémoire après 10 l’instruction : IUT Blois GTR 1, 2004/05 2 29

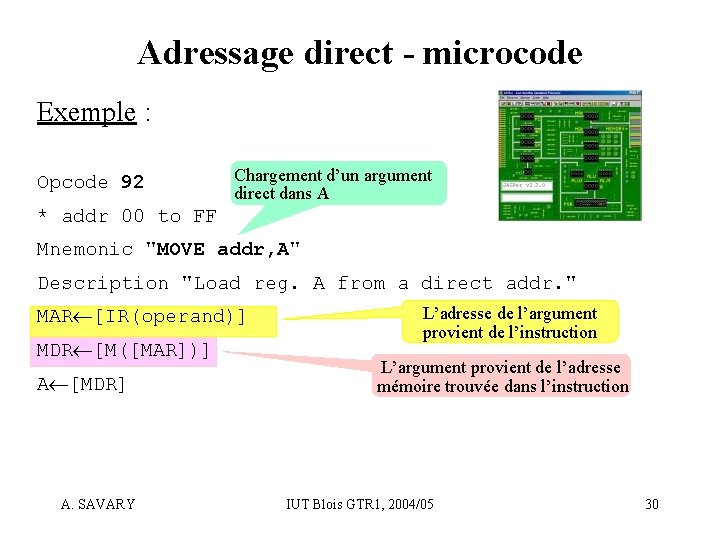

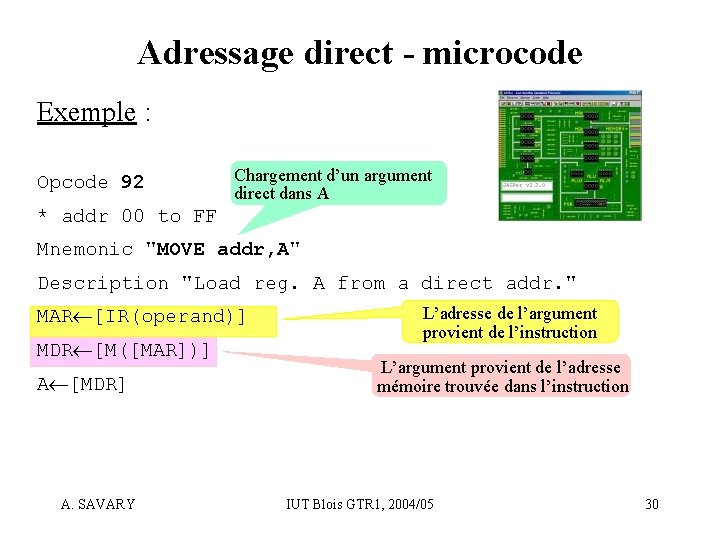

Adressage direct - microcode Exemple : Opcode 92 Chargement d’un argument direct dans A * addr 00 to FF Mnemonic "MOVE addr, A" Description "Load reg. A from a direct addr. " MAR [IR(operand)] MDR [M([MAR])] A [MDR] A. SAVARY L’adresse de l’argument provient de l’instruction L’argument provient de l’adresse mémoire trouvée dans l’instruction IUT Blois GTR 1, 2004/05 30

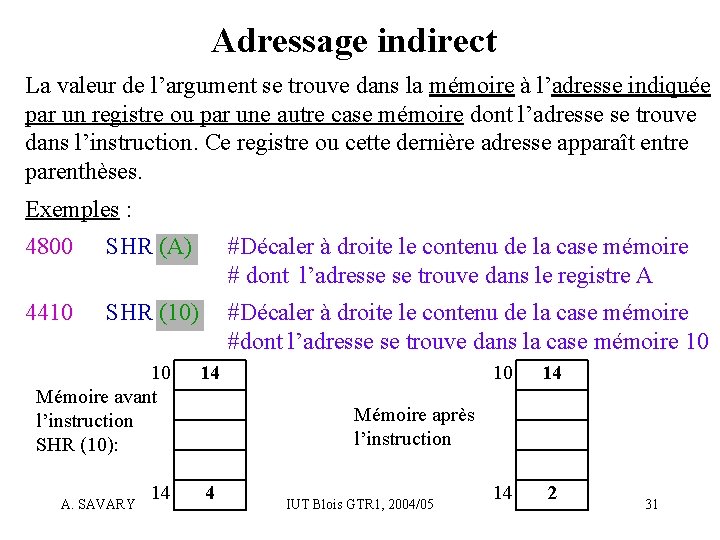

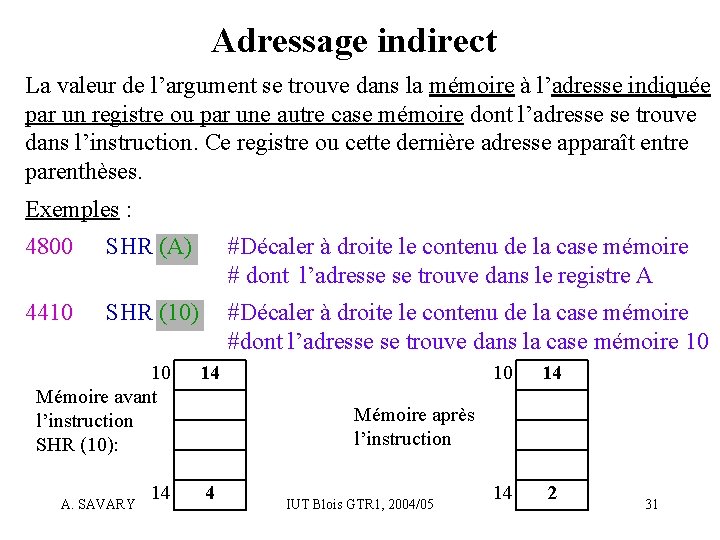

Adressage indirect La valeur de l’argument se trouve dans la mémoire à l’adresse indiquée par un registre ou par une autre case mémoire dont l’adresse se trouve dans l’instruction. Ce registre ou cette dernière adresse apparaît entre parenthèses. Exemples : 4800 SHR (A) #Décaler à droite le contenu de la case mémoire # dont l’adresse se trouve dans le registre A 4410 SHR (10) #Décaler à droite le contenu de la case mémoire #dont l’adresse se trouve dans la case mémoire 10 10 Mémoire avant l’instruction SHR (10): 14 14 4 A. SAVARY 10 14 14 2 Mémoire après l’instruction IUT Blois GTR 1, 2004/05 31

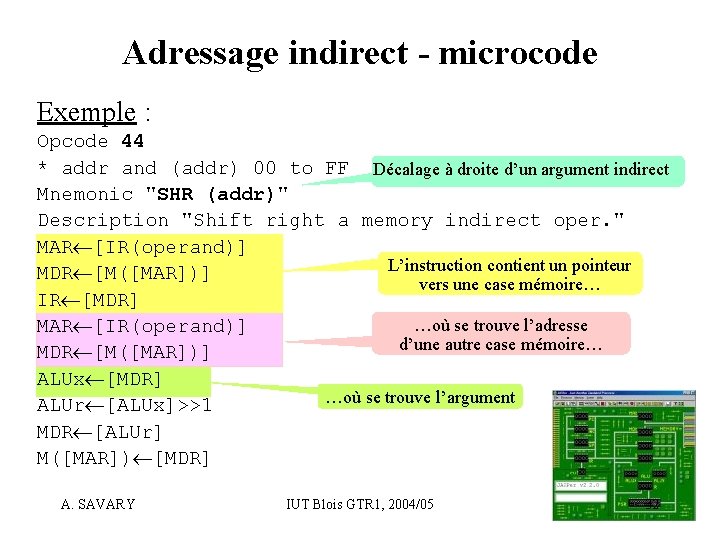

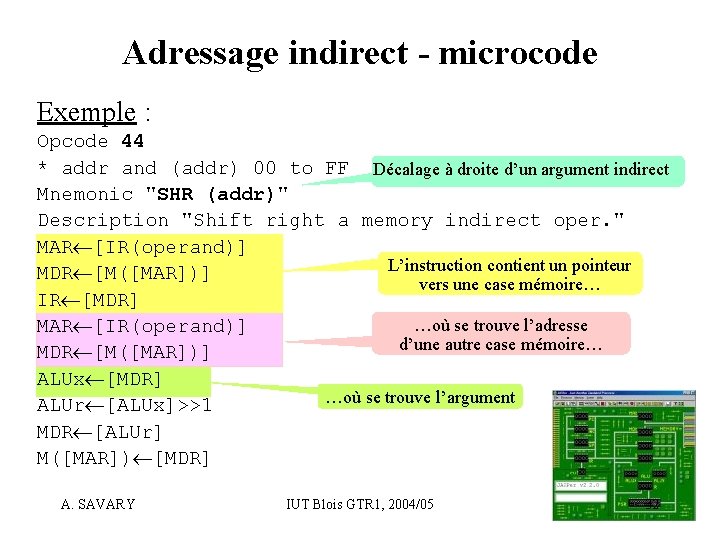

Adressage indirect - microcode Exemple : Opcode 44 * addr and (addr) 00 to FF Décalage à droite d’un argument indirect Mnemonic "SHR (addr)" Description "Shift right a memory indirect oper. " MAR [IR(operand)] L’instruction contient un pointeur MDR [M([MAR])] vers une case mémoire… IR [MDR] …où se trouve l’adresse MAR [IR(operand)] d’une autre case mémoire… MDR [M([MAR])] ALUx [MDR] …où se trouve l’argument ALUr [ALUx]>>1 MDR [ALUr] M([MAR]) [MDR] A. SAVARY IUT Blois GTR 1, 2004/05 32

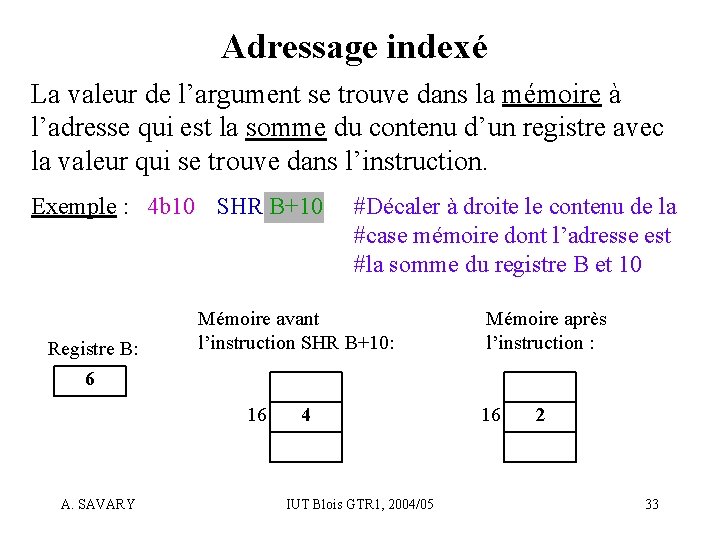

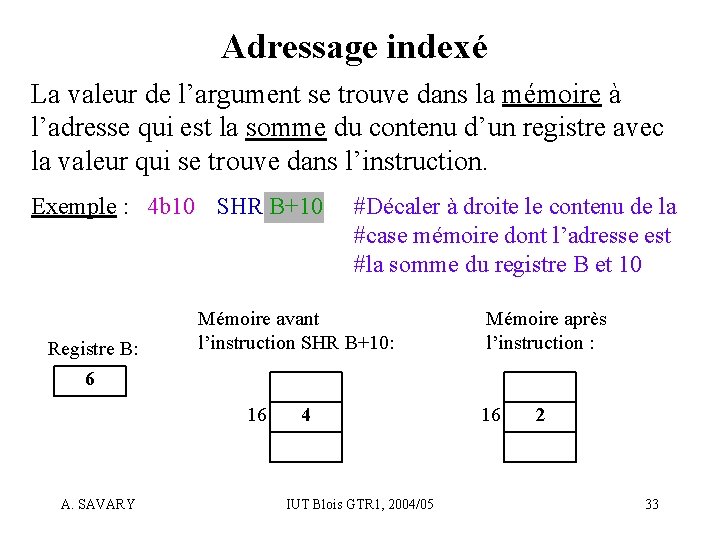

Adressage indexé La valeur de l’argument se trouve dans la mémoire à l’adresse qui est la somme du contenu d’un registre avec la valeur qui se trouve dans l’instruction. Exemple : 4 b 10 SHR B+10 Registre B: 6 Mémoire avant l’instruction SHR B+10: 16 A. SAVARY #Décaler à droite le contenu de la #case mémoire dont l’adresse est #la somme du registre B et 10 4 IUT Blois GTR 1, 2004/05 Mémoire après l’instruction : 16 2 33

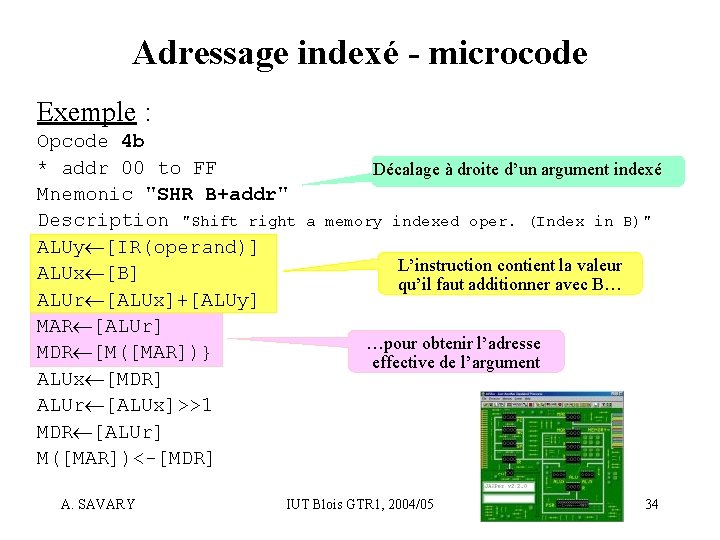

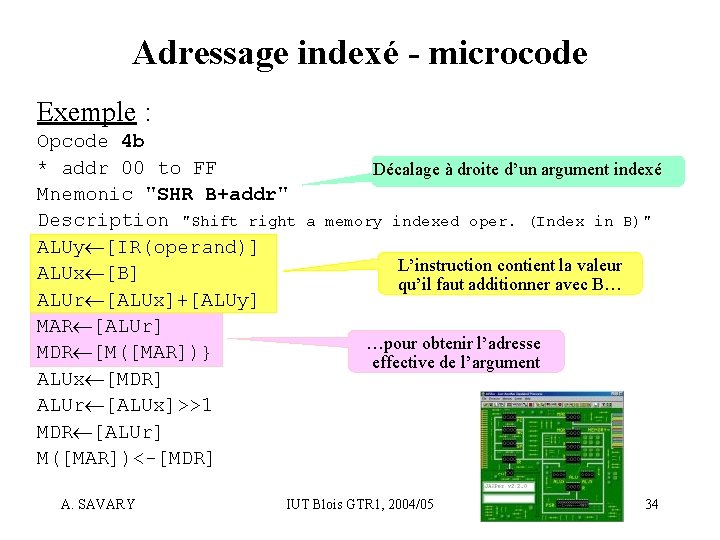

Adressage indexé - microcode Exemple : Opcode 4 b * addr 00 to FF Mnemonic "SHR B+addr" Description "Shift right ALUy [IR(operand)] ALUx [B] ALUr [ALUx]+[ALUy] MAR [ALUr] MDR [M([MAR])} ALUx [MDR] ALUr [ALUx]>>1 MDR [ALUr] M([MAR])<-[MDR] A. SAVARY Décalage à droite d’un argument indexé a memory indexed oper. (Index in B)" L’instruction contient la valeur qu’il faut additionner avec B… …pour obtenir l’adresse effective de l’argument IUT Blois GTR 1, 2004/05 34

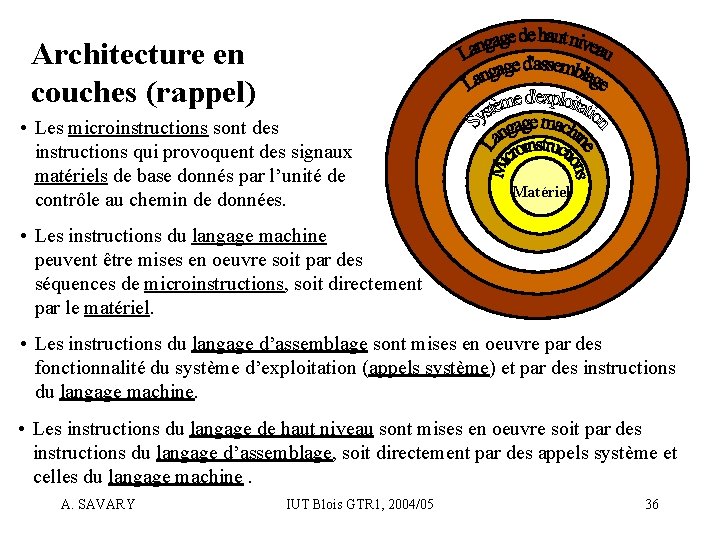

Résumé - architecture en couches A. SAVARY IUT Blois GTR 1, 2004/05 35

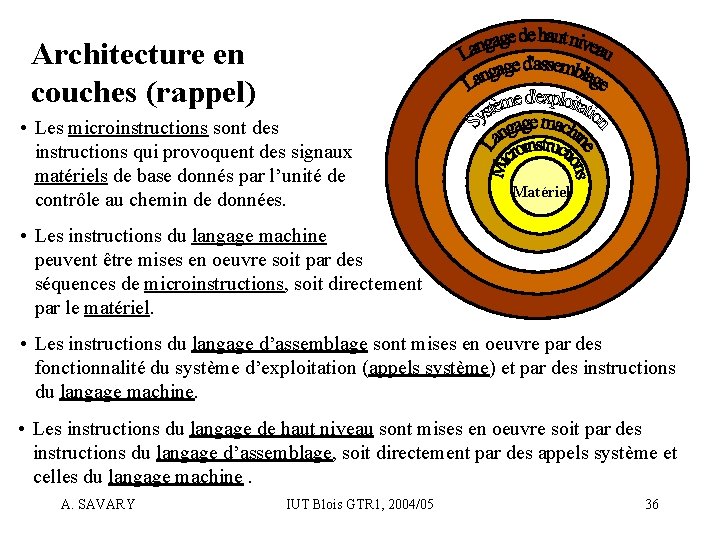

Architecture en couches (rappel) • Les microinstructions sont des instructions qui provoquent des signaux matériels de base donnés par l’unité de contrôle au chemin de données. Matériel • Les instructions du langage machine peuvent être mises en oeuvre soit par des séquences de microinstructions, soit directement par le matériel. • Les instructions du langage d’assemblage sont mises en oeuvre par des fonctionnalité du système d’exploitation (appels système) et par des instructions du langage machine. • Les instructions du langage de haut niveau sont mises en oeuvre soit par des instructions du langage d’assemblage, soit directement par des appels système et celles du langage machine. A. SAVARY IUT Blois GTR 1, 2004/05 36