A DSPBased Ramp Test for OnChip HighResolution ADC

A DSP-Based Ramp Test for On-Chip High-Resolution ADC Wei Jiang and Vishwani D. Agrawal Auburn university

Motivation • Testing analog-to-digital converter (ADC) – Linear ramp to cover full range of ADC – Slow slope for static testing – Histogram-based non-linearity error • Proposed DSP-based ramp test – Characterizing ADC using linear function – Estimating coefficients of the function ICIT'11 2

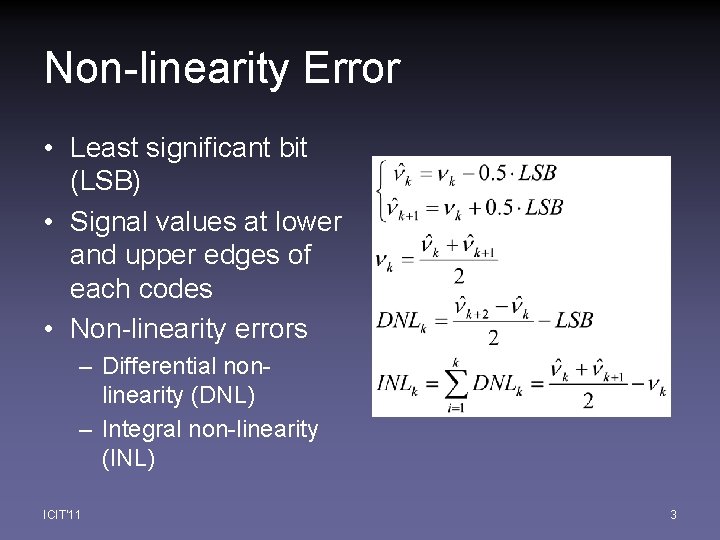

Non-linearity Error • Least significant bit (LSB) • Signal values at lower and upper edges of each codes • Non-linearity errors – Differential nonlinearity (DNL) – Integral non-linearity (INL) ICIT'11 3

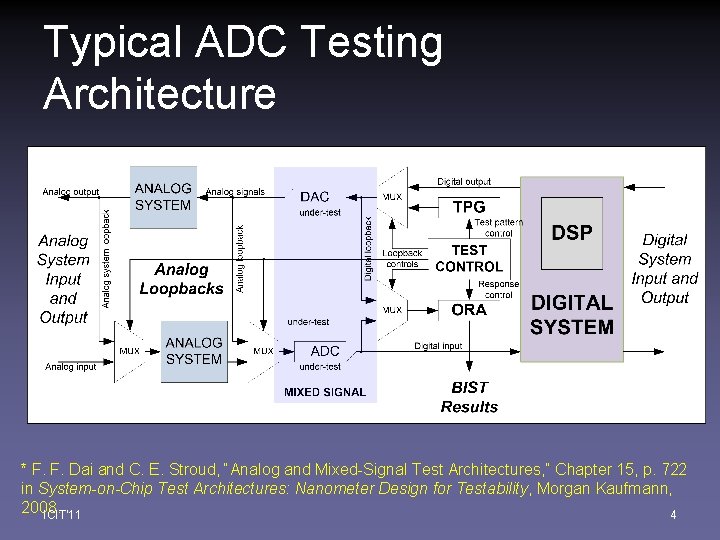

Typical ADC Testing Architecture * F. F. Dai and C. E. Stroud, “Analog and Mixed-Signal Test Architectures, ” Chapter 15, p. 722 in System-on-Chip Test Architectures: Nanometer Design for Testability, Morgan Kaufmann, 2008. ICIT'11 4

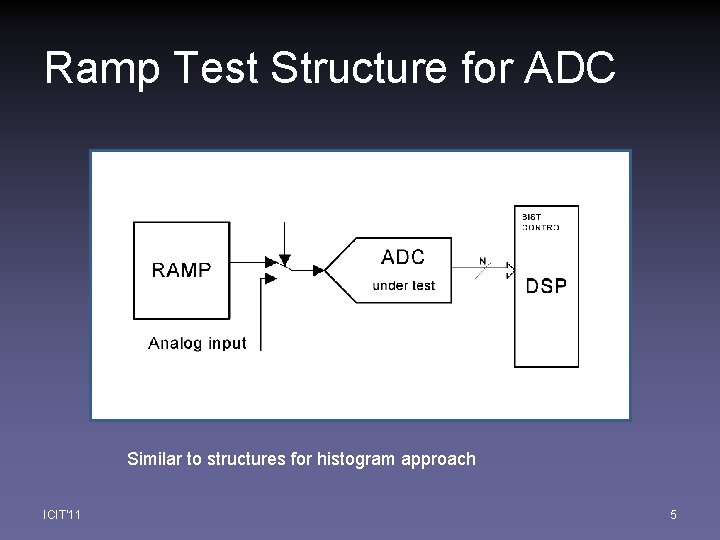

Ramp Test Structure for ADC Similar to structures for histogram approach ICIT'11 5

Ramp Test • Histogram Test for high-resolution ADC – A large amount of code to be tested – Multiple samples for each code – Very low-slope ramp testing signals required • Comparable to thermal noise • Proposed Approach – Linear function to characterize ADC – Coefficients of the function are easy to calculate – Only part of codes measured; speed up testing time ICIT'11 6

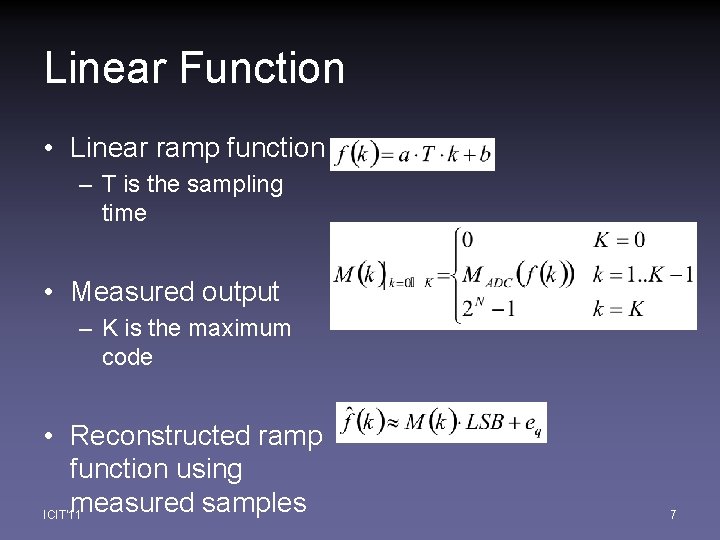

Linear Function • Linear ramp function – T is the sampling time • Measured output – K is the maximum code • Reconstructed ramp function using measured samples ICIT'11 7

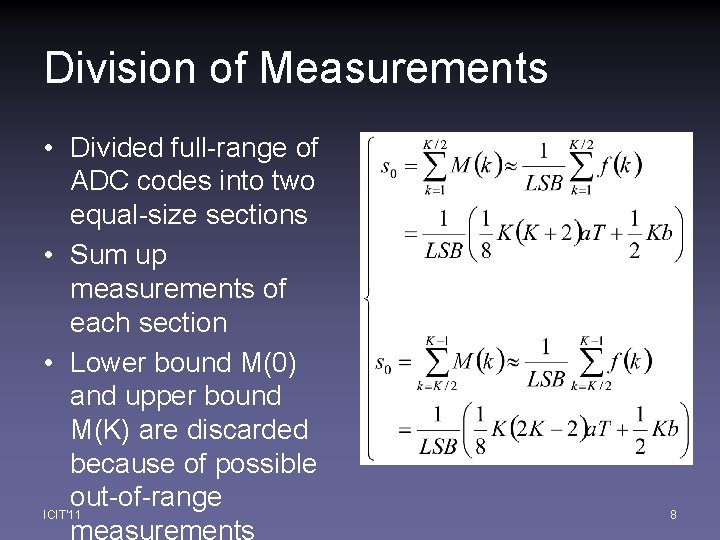

Division of Measurements • Divided full-range of ADC codes into two equal-size sections • Sum up measurements of each section • Lower bound M(0) and upper bound M(K) are discarded because of possible out-of-range ICIT'11 measurements 8

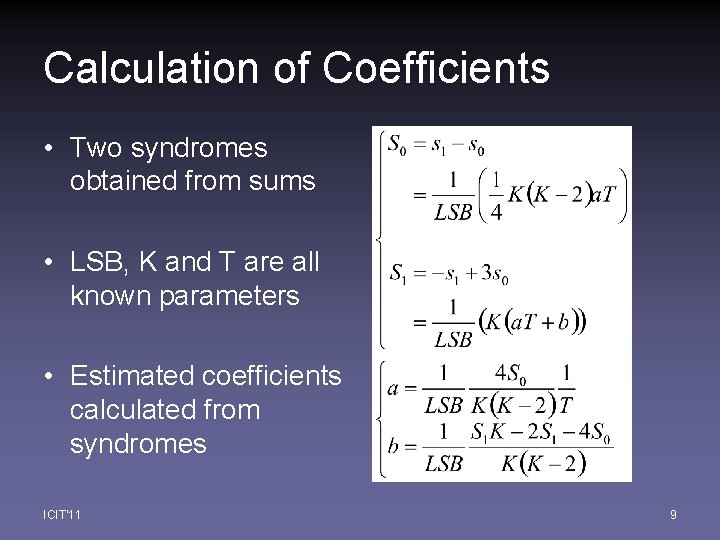

Calculation of Coefficients • Two syndromes obtained from sums • LSB, K and T are all known parameters • Estimated coefficients calculated from syndromes ICIT'11 9

BIST Steps - measurements • Reset ramp testing signal generator • Detect first non-zero ADC output (lowerbound of samples) • Measure all subsequent samples • Stop at the maximum ADC output (upperbound of samples) • DSP collects all valid measurements and start to processing data ICIT'11 10

BIST Steps – processing data • Divide measured samples into two equalsize parts • Accumulate measurements of each part to obtain two sums • Calculate two syndromes from two sums • Calculate two estimated coefficients of the linear ramp function • (Optional) Compare each measured data to estimated one from ramp function ICIT'11 11

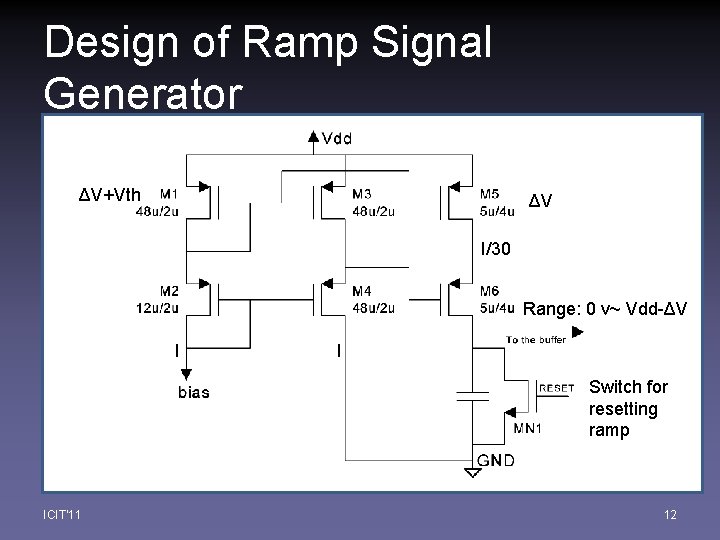

Design of Ramp Signal Generator ΔV+Vth ΔV I/30 Range: 0 v~ Vdd-ΔV I I Switch for resetting ramp ICIT'11 12

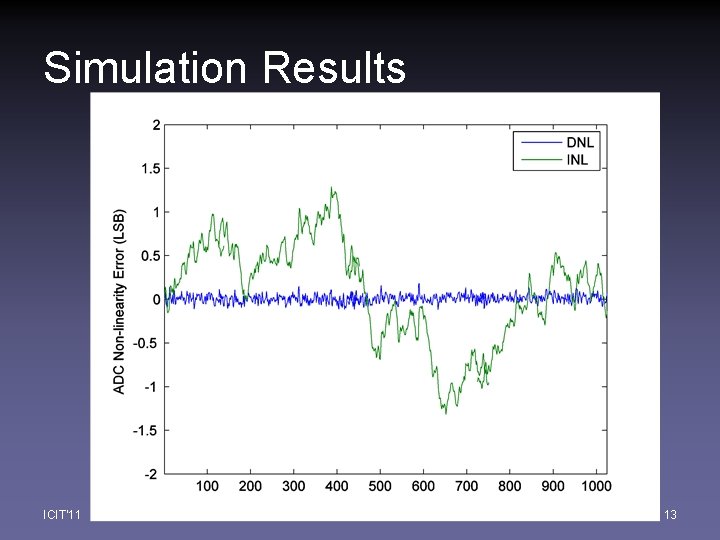

Simulation Results ICIT'11 13

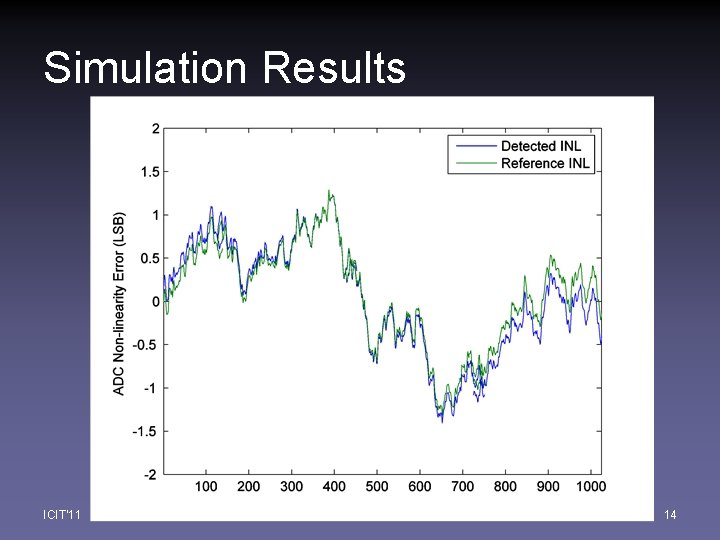

Simulation Results ICIT'11 14

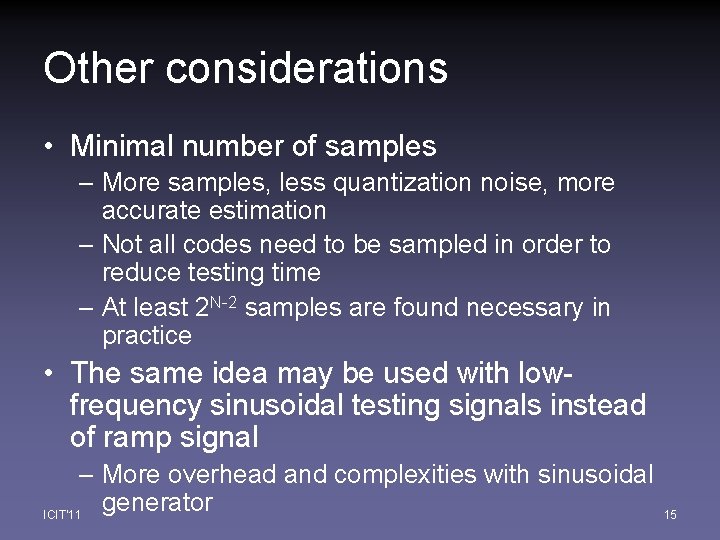

Other considerations • Minimal number of samples – More samples, less quantization noise, more accurate estimation – Not all codes need to be sampled in order to reduce testing time – At least 2 N-2 samples are found necessary in practice • The same idea may be used with lowfrequency sinusoidal testing signals instead of ramp signal – More overhead and complexities with sinusoidal generator ICIT'11 15

Conclusion • Proposed Approach – For high-resolution ADC – Less samples required comparing to histogram approach – Simple algorithm to calculate coefficients and make estimation ICIT'11 16

THANK YOU ICIT'11 17

- Slides: 17