RAMP Architecture Language Compiler http ramp eecs berkeley

RAMP: Architecture, Language & Compiler http: //ramp. eecs. berkeley. edu Greg Gibeling, Andrew Schultz, Krste Asanovic Contact: gdgib@berkeley. edu RAMP Retreat, BWRC, 20 January 2006 9/4/2021 RAMP Architecture, Language & Compiler 1

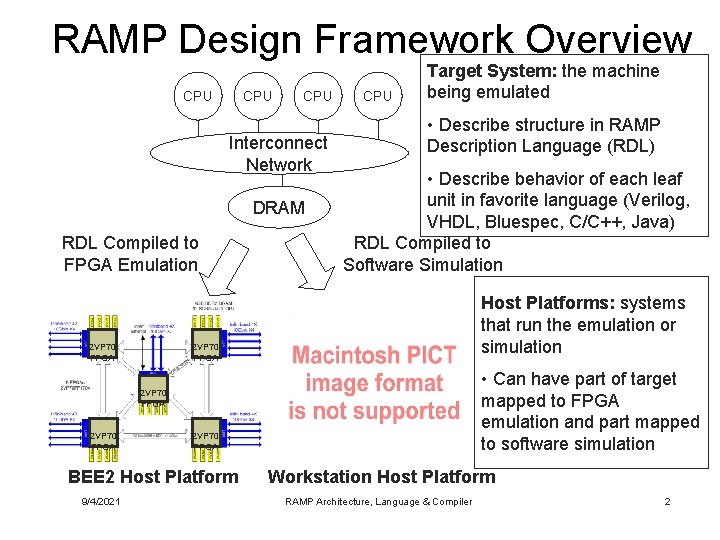

RAMP Design Framework Overview CPU CPU Interconnect Network DRAM RDL Compiled to FPGA Emulation CPU Target System: the machine being emulated • Describe structure in RAMP Description Language (RDL) • Describe behavior of each leaf unit in favorite language (Verilog, VHDL, Bluespec, C/C++, Java) RDL Compiled to Software Simulation Host Platforms: systems that run the emulation or simulation 2 VP 70 FPGA • Can have part of target mapped to FPGA emulation and part mapped to software simulation 2 VP 70 FPGA BEE 2 Host Platform 9/4/2021 Workstation Host Platform RAMP Architecture, Language & Compiler 2

RAMP Target Model (1) Units communicating over channels n Units ¡ Large pieces of functionality, >10, 000 Gates n e. g. , ¡ Processor + L 1$ Leaf units implemented in a “host” language n Channels ¡ ¡ Unidirectional Point-to-point FIFO semantics Unknown latency and buffering (fixed when system instantiated) 9/4/2021 RAMP Architecture, Language & Compiler 3

RAMP Target Model (2) n Transaction-style semantics for unit ¡ ¡ 9/4/2021 Read 0/1 messages from each input Perform some action Write 0/1 messages to each output Units MUST be latency insensitive RAMP Architecture, Language & Compiler 4

Target Model - Units Inside edge n Ports connect units to channels ¡ ¡ n FIFO signaling Hardware or Software Target cycle control ¡ ¡ ¡ __Start __Done Allows for variable number of host cycles per target cycle 9/4/2021 RAMP Architecture, Language & Compiler 5

Target Model – Channel (1) n Channel semantics ¡ ¡ 9/4/2021 Each channel carries arbitrary set of message types, statically determined Ordered delivery Debugging through monitoring & injection Provides for cross-platform simulations RAMP Architecture, Language & Compiler 6

Target Model – Channel (2) n Channel parameters for timing-accurate simulations ¡ ¡ ¡ n Bitwidth (in bits per target clock cycle) Latency (in target clock cycles) Buffering (in either fragments or messages) Fragments (one target clock cycle’s worth of data) ¡ ¡ 9/4/2021 Smaller than messages Convey the simulation time through idles RAMP Architecture, Language & Compiler 7

Target Model – Channel (3) Fragmentation n Messages may be larger than fragments n Channels carry (per target cycle): Timing Model n Zero fragments still indicates passage of time n Implement outside of the units ¡ Zero or one fragments ¡ Between zero and one messages 9/4/2021 RAMP Architecture, Language & Compiler 8

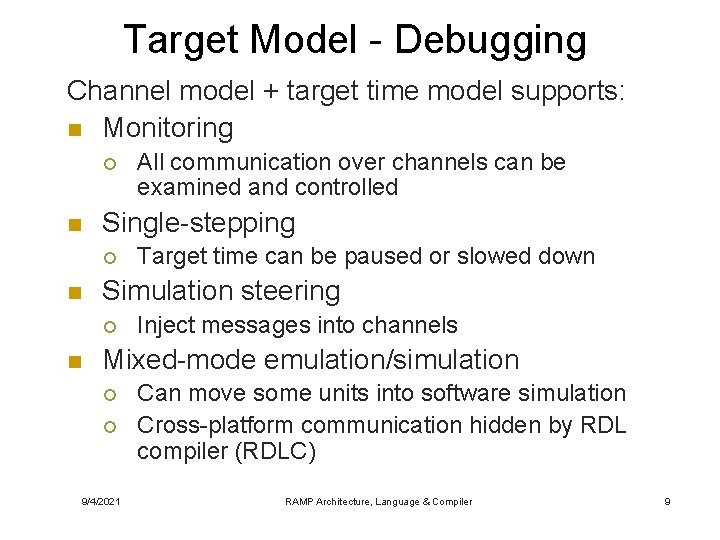

Target Model - Debugging Channel model + target time model supports: n Monitoring ¡ n Single-stepping ¡ n Target time can be paused or slowed down Simulation steering ¡ n All communication over channels can be examined and controlled Inject messages into channels Mixed-mode emulation/simulation ¡ ¡ 9/4/2021 Can move some units into software simulation Cross-platform communication hidden by RDL compiler (RDLC) RAMP Architecture, Language & Compiler 9

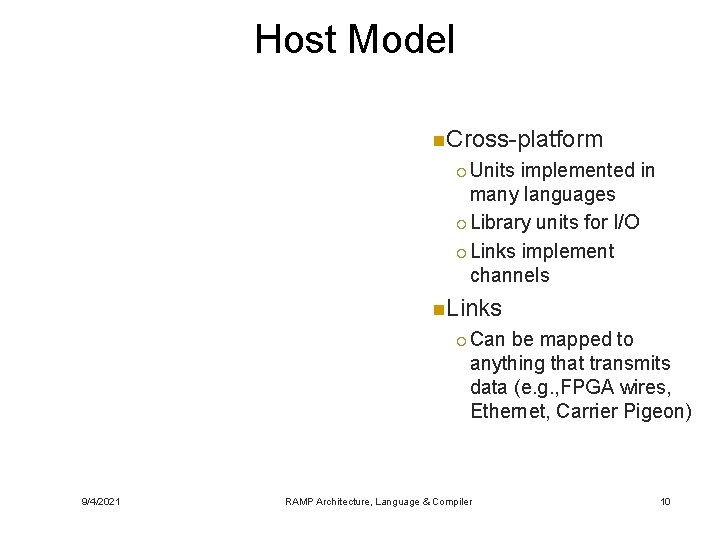

Host Model n. Cross-platform ¡ Units implemented in many languages ¡ Library units for I/O ¡ Links implement channels n. Links ¡ Can be mapped to anything that transmits data (e. g. , FPGA wires, Ethernet, Carrier Pigeon) 9/4/2021 RAMP Architecture, Language & Compiler 10

Host Model – Wrapper (1) 9/4/2021 RAMP Architecture, Language & Compiler 11

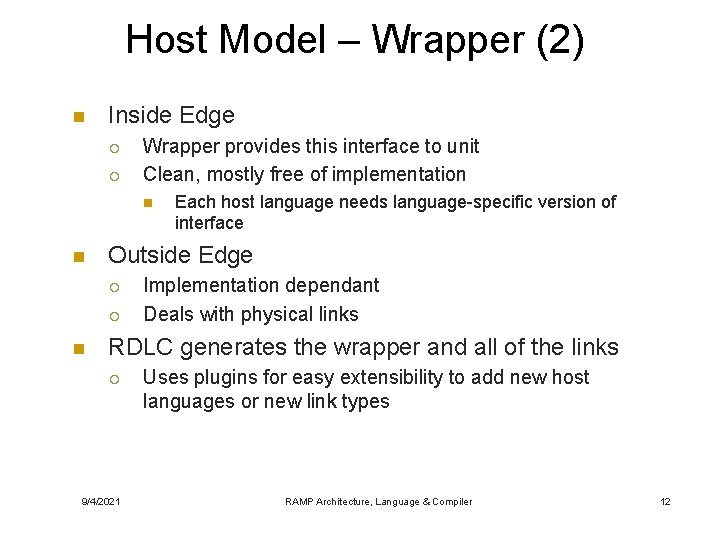

Host Model – Wrapper (2) n Inside Edge ¡ ¡ Wrapper provides this interface to unit Clean, mostly free of implementation n n Outside Edge ¡ ¡ n Each host language needs language-specific version of interface Implementation dependant Deals with physical links RDLC generates the wrapper and all of the links ¡ 9/4/2021 Uses plugins for easy extensibility to add new host languages or new link types RAMP Architecture, Language & Compiler 12

Host Model - Link n Typically Three Components ¡ ¡ ¡ 9/4/2021 Packing & Unpacking Timing Model Physical Transport RAMP Architecture, Language & Compiler 13

RDL (1) n n n “RAMP Description Language” General process network system description language Compiler includes back-end extensibility ¡ n Links, other toolflows, external signals Does NOT include or examine the functionality of leaf units! 9/4/2021 RAMP Architecture, Language & Compiler 14

RDL (2) n Hierarchical Namespaces ¡ ¡ ¡ n RDL Target Constructs ¡ ¡ n Channels, Messages and Port types Units include instances, inputs, outputs and connections RDL Host Constructs ¡ ¡ ¡ n Declarations can be external to a namespace Replaces “preprocessing” Allows for communal development One platform per board or computer Platforms include an implementation language Hierarchy allows for, eg. A board with many FPGAs RDL Mappings ¡ ¡ Hierarchy allows for “compile one, run many” Allows specific units and channels to be precisely mapped 9/4/2021 RAMP Architecture, Language & Compiler 15

RDL Example (1) n Up/Down Counter ¡ ¡ n Push button input 4 -bit LED output Utility as example ¡ ¡ ¡ 9/4/2021 Proof of concept Simple language example Hands on demo RAMP Architecture, Language & Compiler 16

![RDL Example (2) unit { input bit[1] Up. Down; output bit[32] Count; } Counter; RDL Example (2) unit { input bit[1] Up. Down; output bit[32] Count; } Counter;](http://slidetodoc.com/presentation_image_h2/86a02e06e7532bb71ee61310b955ee50/image-17.jpg)

RDL Example (2) unit { input bit[1] Up. Down; output bit[32] Count; } Counter; 9/4/2021 RAMP Architecture, Language & Compiler 17

RDL Example (3) 9/4/2021 RAMP Architecture, Language & Compiler 18

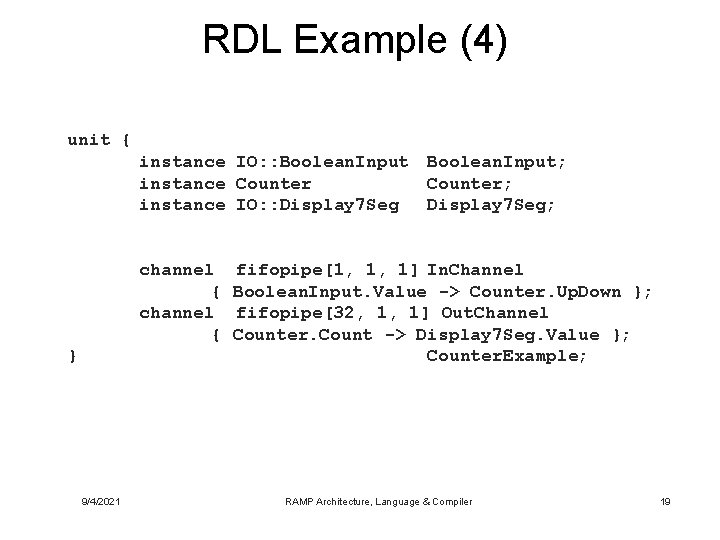

RDL Example (4) unit { instance IO: : Boolean. Input; instance Counter; instance IO: : Display 7 Seg; channel { } 9/4/2021 fifopipe[1, 1, 1] In. Channel Boolean. Input. Value -> Counter. Up. Down }; fifopipe[32, 1, 1] Out. Channel Counter. Count -> Display 7 Seg. Value }; Counter. Example; RAMP Architecture, Language & Compiler 19

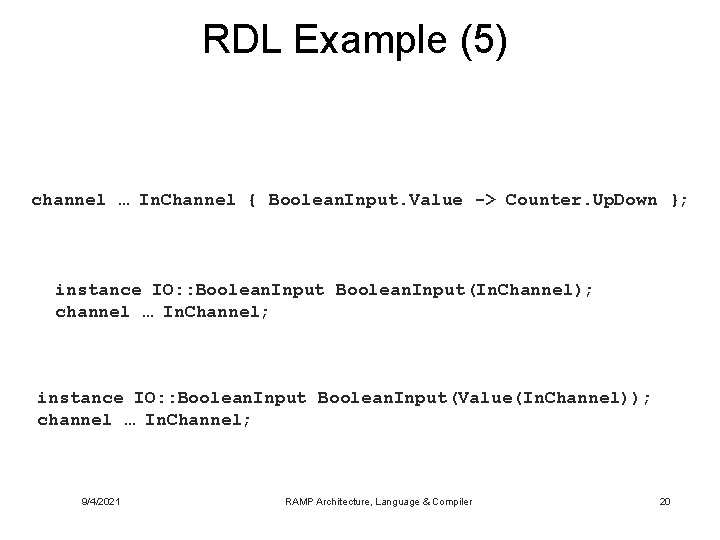

RDL Example (5) channel … In. Channel { Boolean. Input. Value -> Counter. Up. Down }; instance IO: : Boolean. Input(In. Channel); channel … In. Channel; instance IO: : Boolean. Input(Value(In. Channel)); channel … In. Channel; 9/4/2021 RAMP Architecture, Language & Compiler 20

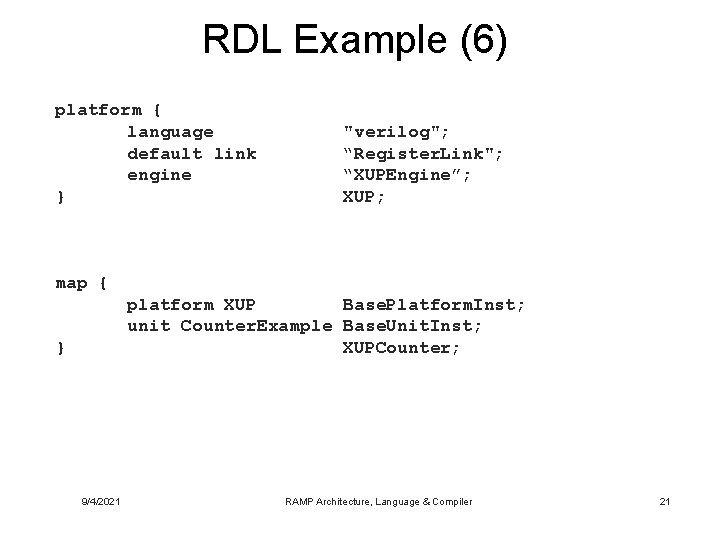

RDL Example (6) platform { language default link engine } "verilog"; “Register. Link"; “XUPEngine”; XUP; map { platform XUP Base. Platform. Inst; unit Counter. Example Base. Unit. Inst; XUPCounter; } 9/4/2021 RAMP Architecture, Language & Compiler 21

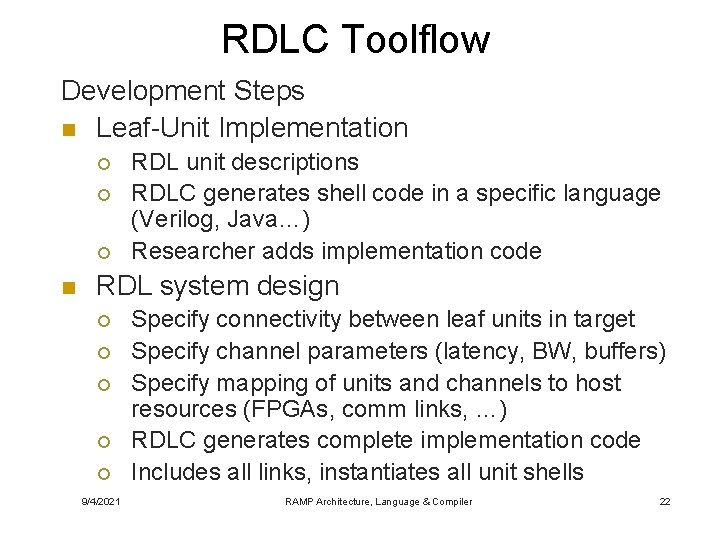

RDLC Toolflow Development Steps n Leaf-Unit Implementation ¡ ¡ ¡ n RDL unit descriptions RDLC generates shell code in a specific language (Verilog, Java…) Researcher adds implementation code RDL system design ¡ ¡ ¡ 9/4/2021 Specify connectivity between leaf units in target Specify channel parameters (latency, BW, buffers) Specify mapping of units and channels to host resources (FPGAs, comm links, …) RDLC generates complete implementation code Includes all links, instantiates all unit shells RAMP Architecture, Language & Compiler 22

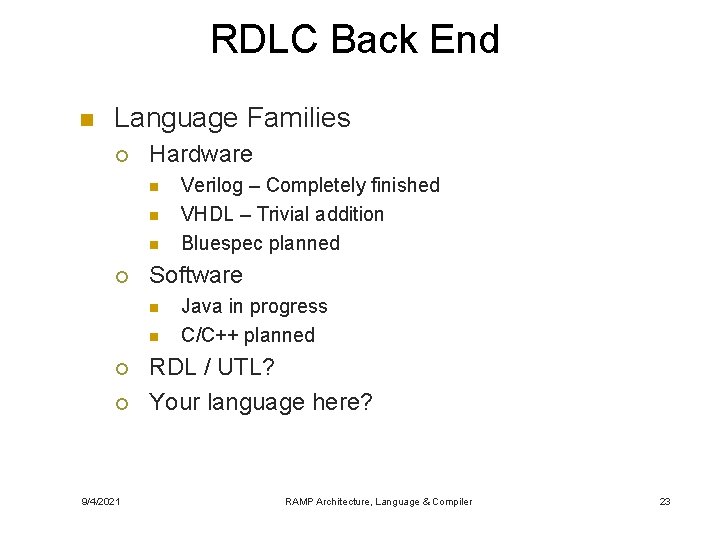

RDLC Back End n Language Families ¡ Hardware n n n ¡ Software n n ¡ ¡ 9/4/2021 Verilog – Completely finished VHDL – Trivial addition Bluespec planned Java in progress C/C++ planned RDL / UTL? Your language here? RAMP Architecture, Language & Compiler 23

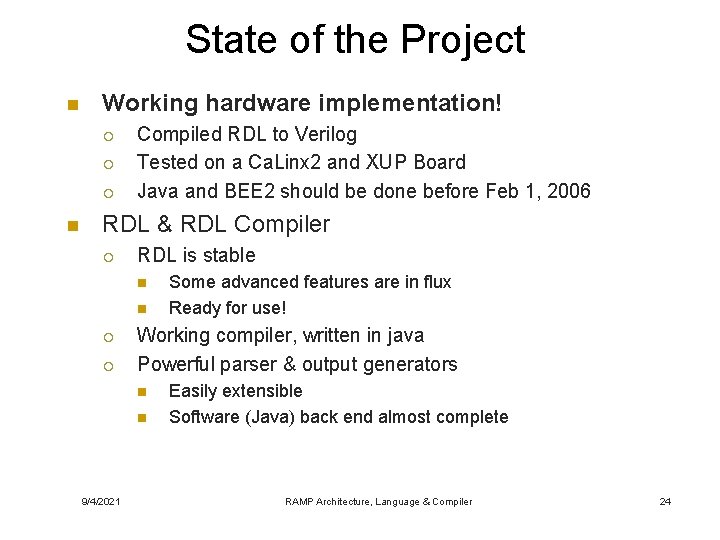

State of the Project n Working hardware implementation! ¡ ¡ ¡ n Compiled RDL to Verilog Tested on a Ca. Linx 2 and XUP Board Java and BEE 2 should be done before Feb 1, 2006 RDL & RDL Compiler ¡ RDL is stable n n ¡ ¡ Working compiler, written in java Powerful parser & output generators n n 9/4/2021 Some advanced features are in flux Ready for use! Easily extensible Software (Java) back end almost complete RAMP Architecture, Language & Compiler 24

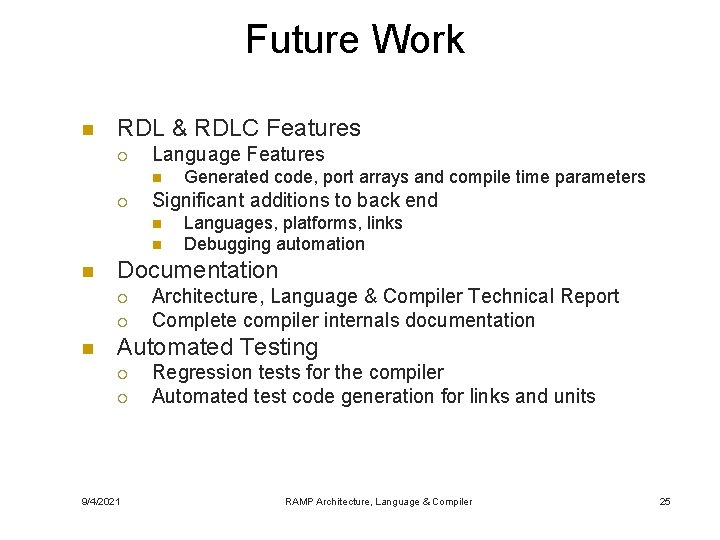

Future Work n RDL & RDLC Features ¡ Language Features n ¡ Significant additions to back end n n n Languages, platforms, links Debugging automation Documentation ¡ ¡ n Generated code, port arrays and compile time parameters Architecture, Language & Compiler Technical Report Complete compiler internals documentation Automated Testing ¡ ¡ 9/4/2021 Regression tests for the compiler Automated test code generation for links and units RAMP Architecture, Language & Compiler 25

Website & Community n n http: //ramp. eecs. berkeley. edu Planned Features ¡ ¡ n Wiki – Certainly not JSPWiki CVS Repository Mailing list control and archives Communal project listings Ideas, Comments & Requests ¡ 9/4/2021 gdgib@berkeley. edu, CC: krste@mit. edu RAMP Architecture, Language & Compiler 26

- Slides: 26