inst eecs berkeley educs 61 c UC Berkeley

inst. eecs. berkeley. edu/~cs 61 c UC Berkeley CS 61 C : Machine Structures Lecture 26 – Combinational Logic Blocks Senior Lecturer SOE Dan Garcia www. cs. berkeley. edu/~ddgarcia Mine. Craft Logic Gates Using redstone circuits, which are “structures that can be built to active or control mechamisms”, you can create all the logic gates using Mine. Craft. minecraft. gamepedia. com/Tutorials/Basic_Logic_Gates CS 61 C L 26 Combinational Logic Blocks (1) Garcia, Fall 2014 © UCB

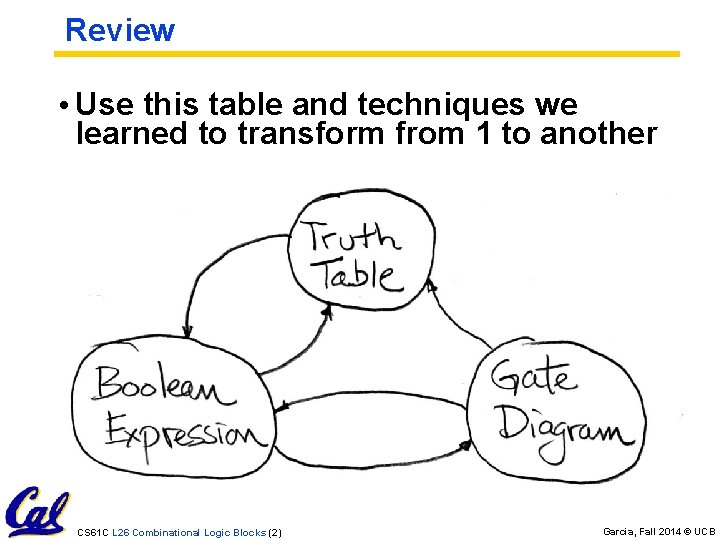

Review • Use this table and techniques we learned to transform from 1 to another CS 61 C L 26 Combinational Logic Blocks (2) Garcia, Fall 2014 © UCB

Today • Data Multiplexors • Arithmetic and Logic Unit • Adder/Subtractor CS 61 C L 26 Combinational Logic Blocks (3) Garcia, Fall 2014 © UCB

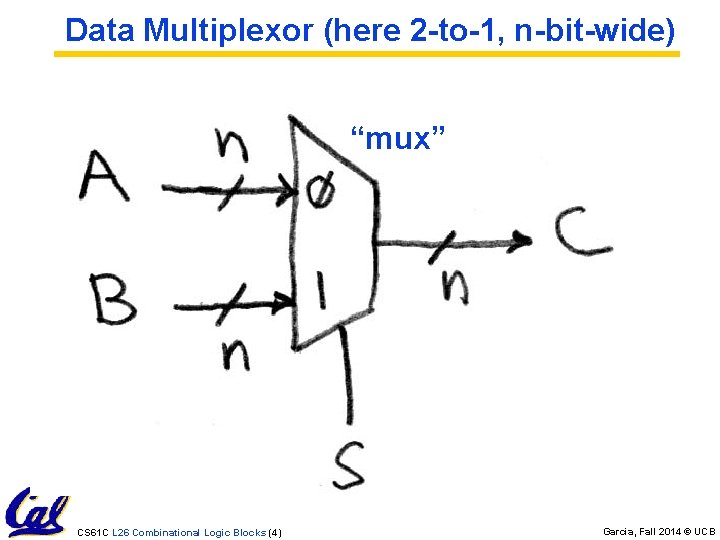

Data Multiplexor (here 2 -to-1, n-bit-wide) “mux” CS 61 C L 26 Combinational Logic Blocks (4) Garcia, Fall 2014 © UCB

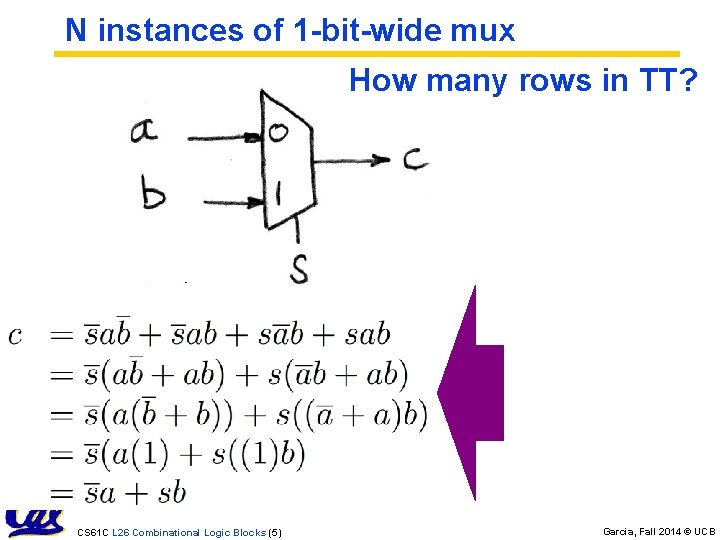

N instances of 1 -bit-wide mux How many rows in TT? CS 61 C L 26 Combinational Logic Blocks (5) Garcia, Fall 2014 © UCB

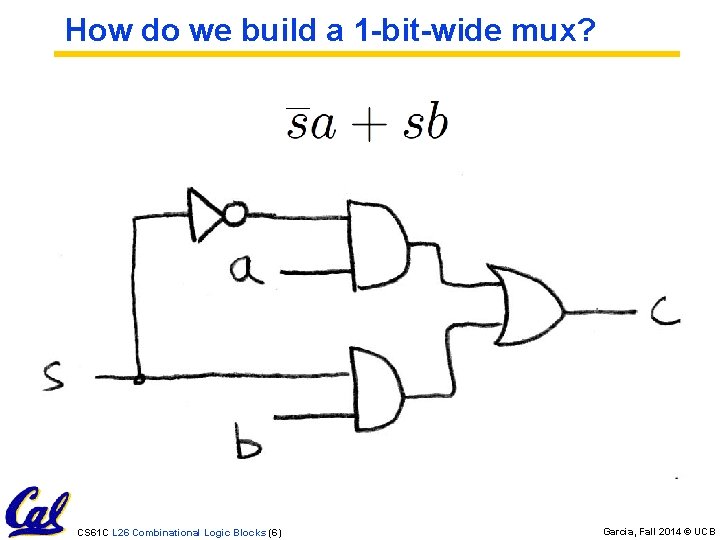

How do we build a 1 -bit-wide mux? CS 61 C L 26 Combinational Logic Blocks (6) Garcia, Fall 2014 © UCB

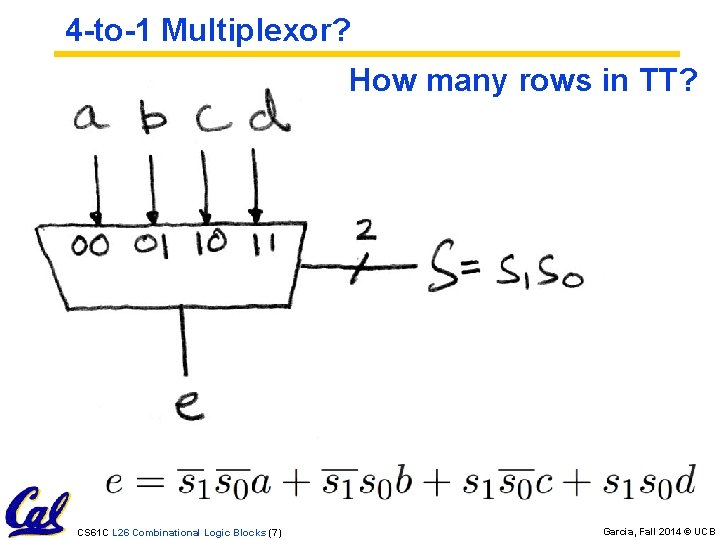

4 -to-1 Multiplexor? How many rows in TT? CS 61 C L 26 Combinational Logic Blocks (7) Garcia, Fall 2014 © UCB

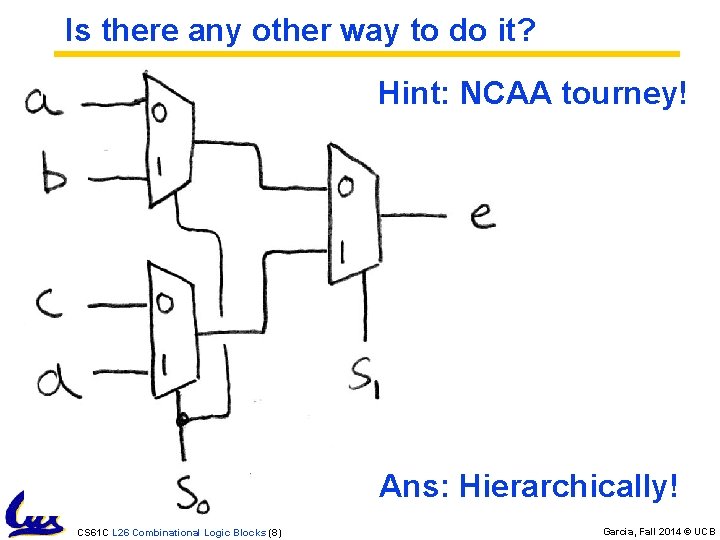

Is there any other way to do it? Hint: NCAA tourney! Ans: Hierarchically! CS 61 C L 26 Combinational Logic Blocks (8) Garcia, Fall 2014 © UCB

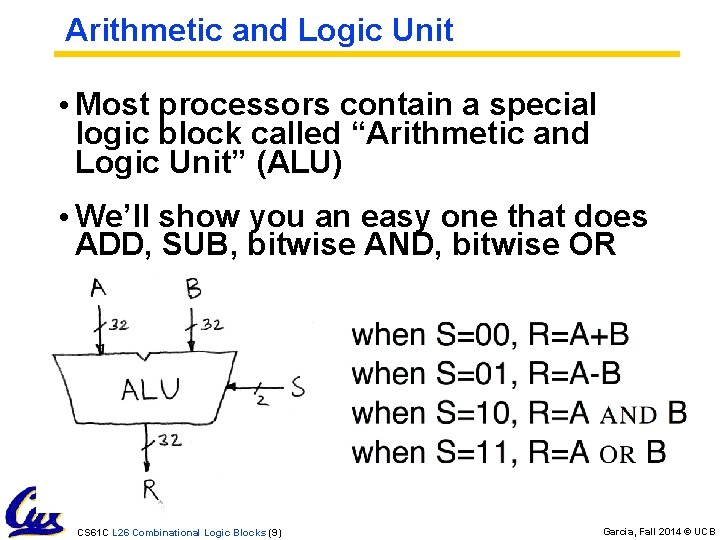

Arithmetic and Logic Unit • Most processors contain a special logic block called “Arithmetic and Logic Unit” (ALU) • We’ll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR CS 61 C L 26 Combinational Logic Blocks (9) Garcia, Fall 2014 © UCB

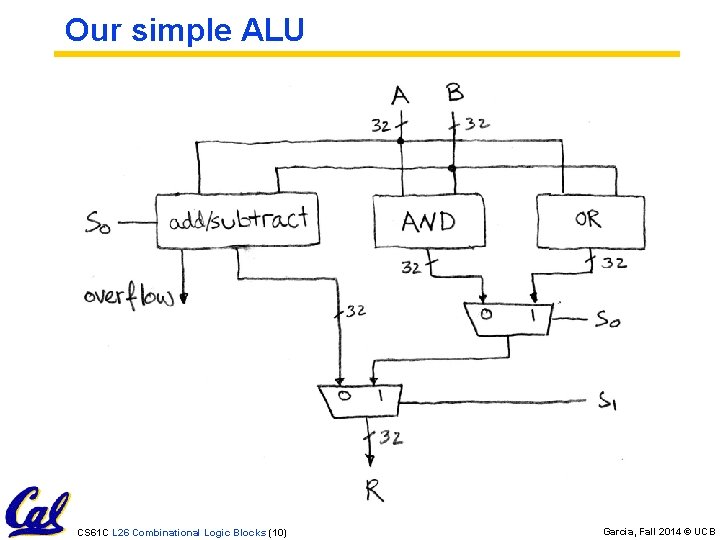

Our simple ALU CS 61 C L 26 Combinational Logic Blocks (10) Garcia, Fall 2014 © UCB

Administrivia • How did you find project 2? a) b) c) d) e) Hated it Disliked it Neutral Liked it Loved it CS 61 C L 26 Combinational Logic Blocks (11) Garcia, Fall 2014 © UCB

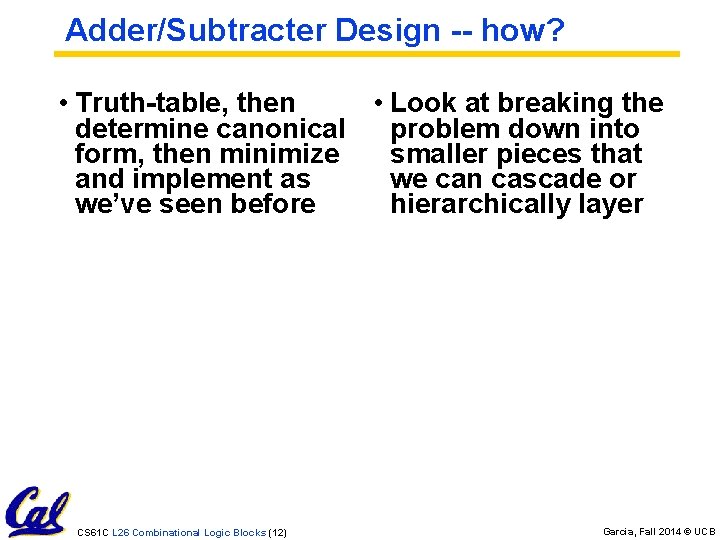

Adder/Subtracter Design -- how? • Truth-table, then • Look at breaking the determine canonical problem down into form, then minimize smaller pieces that and implement as we can cascade or we’ve seen before hierarchically layer CS 61 C L 26 Combinational Logic Blocks (12) Garcia, Fall 2014 © UCB

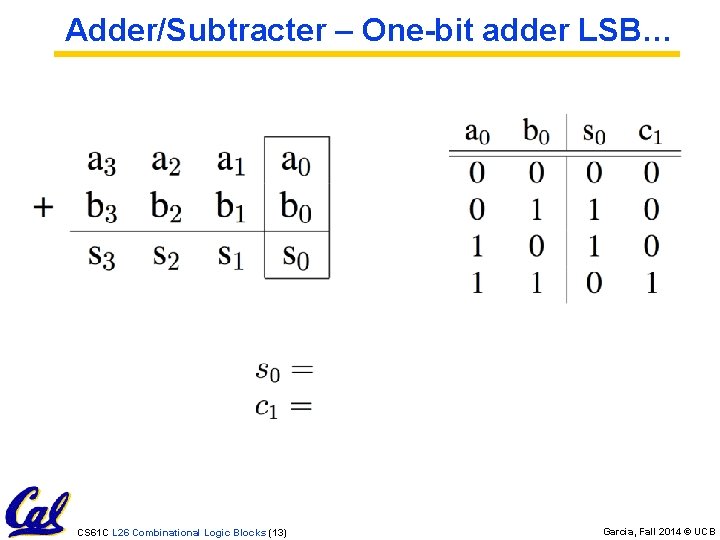

Adder/Subtracter – One-bit adder LSB… CS 61 C L 26 Combinational Logic Blocks (13) Garcia, Fall 2014 © UCB

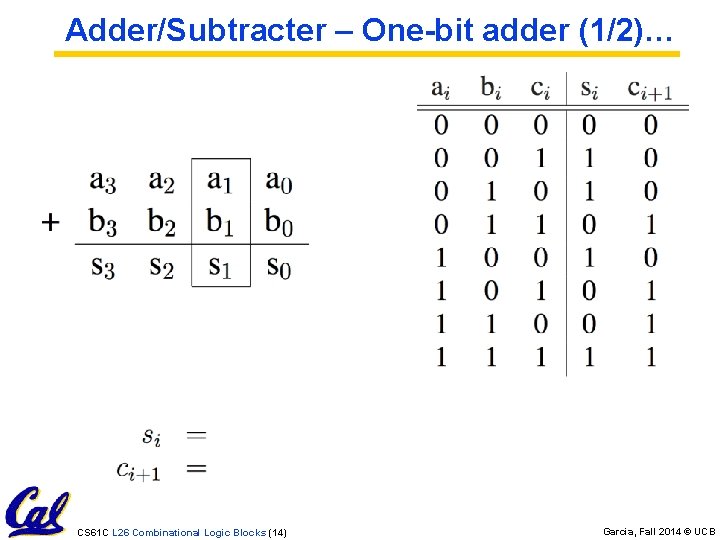

Adder/Subtracter – One-bit adder (1/2)… CS 61 C L 26 Combinational Logic Blocks (14) Garcia, Fall 2014 © UCB

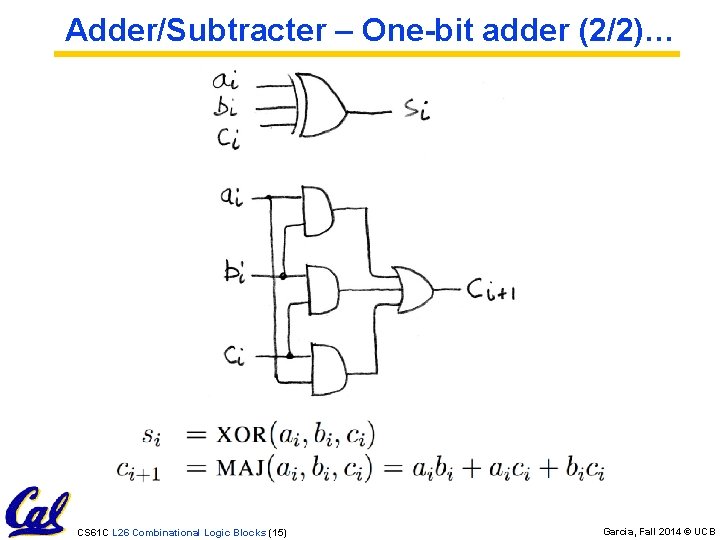

Adder/Subtracter – One-bit adder (2/2)… CS 61 C L 26 Combinational Logic Blocks (15) Garcia, Fall 2014 © UCB

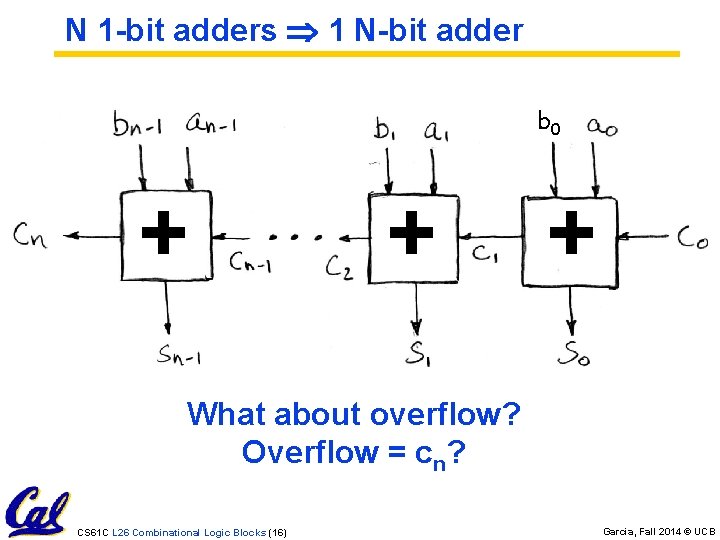

N 1 -bit adders 1 N-bit adder b 0 + + + What about overflow? Overflow = cn? CS 61 C L 26 Combinational Logic Blocks (16) Garcia, Fall 2014 © UCB

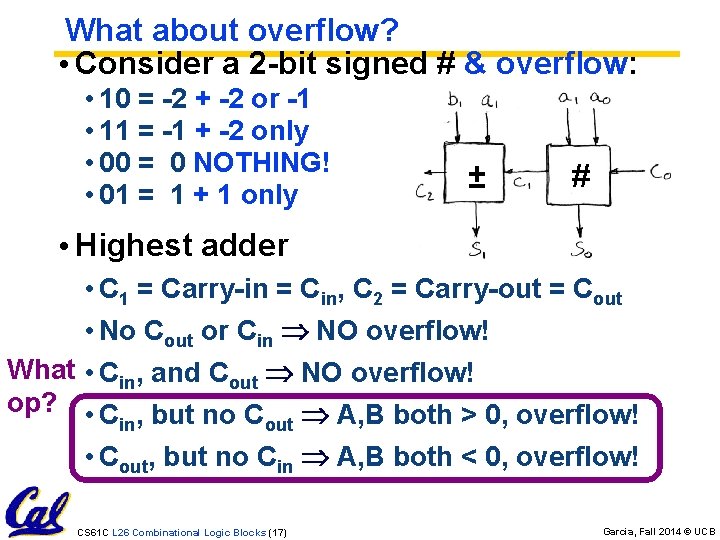

What about overflow? • Consider a 2 -bit signed # & overflow: • 10 = -2 + -2 or -1 • 11 = -1 + -2 only • 00 = 0 NOTHING! • 01 = 1 + 1 only ± # • Highest adder • C 1 = Carry-in = Cin, C 2 = Carry-out = Cout • No Cout or Cin NO overflow! What • Cin, and Cout NO overflow! op? • C , but no C A, B both > 0, overflow! in out • Cout, but no Cin A, B both < 0, overflow! CS 61 C L 26 Combinational Logic Blocks (17) Garcia, Fall 2014 © UCB

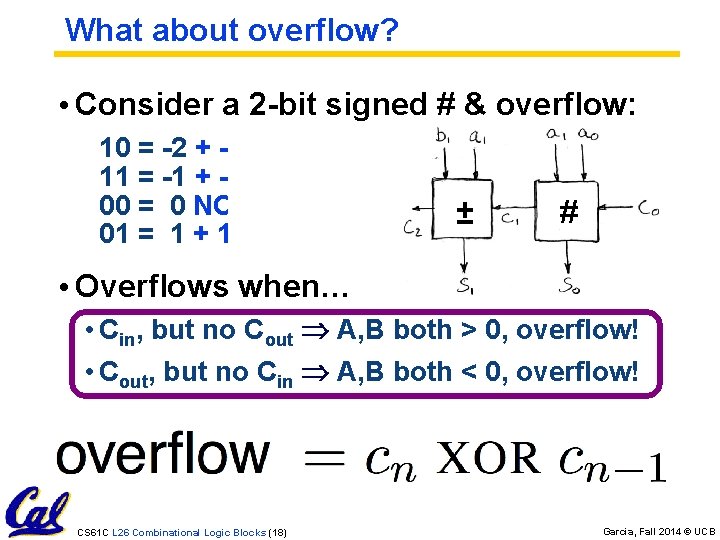

What about overflow? • Consider a 2 -bit signed # & overflow: 10 = -2 + -2 or -1 11 = -1 + -2 only 00 = 0 NOTHING! 01 = 1 + 1 only ± # • Overflows when… • Cin, but no Cout A, B both > 0, overflow! • Cout, but no Cin A, B both < 0, overflow! CS 61 C L 26 Combinational Logic Blocks (18) Garcia, Fall 2014 © UCB

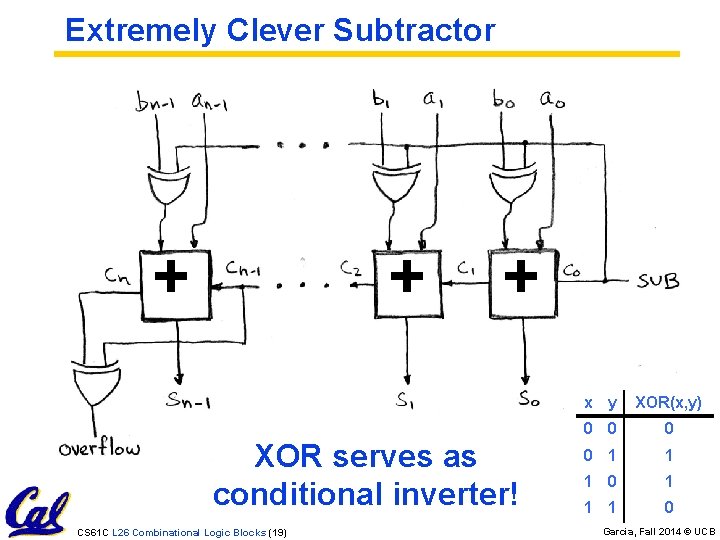

Extremely Clever Subtractor + + + XOR serves as conditional inverter! CS 61 C L 26 Combinational Logic Blocks (19) x y XOR(x, y) 0 0 1 1 1 0 Garcia, Fall 2014 © UCB

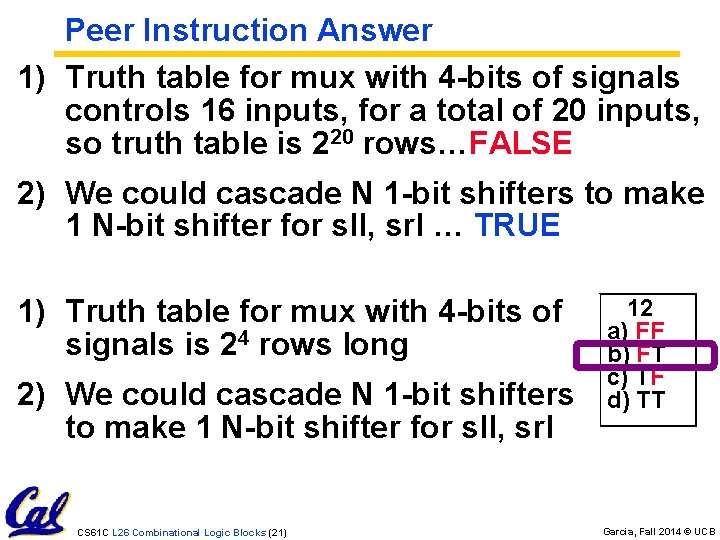

Peer Instruction 1) Truth table for mux with 4 -bits of signals has 24 rows 2) We could cascade N 1 -bit shifters to make 1 N-bit shifter for sll, srl CS 61 C L 26 Combinational Logic Blocks (20) 12 a) FF b) FT c) TF d) TT Garcia, Fall 2014 © UCB

Peer Instruction Answer 1) Truth table for mux with 4 -bits of signals controls 16 inputs, for a total of 20 inputs, so truth table is 220 rows…FALSE 2) We could cascade N 1 -bit shifters to make 1 N-bit shifter for sll, srl … TRUE 1) Truth table for mux with 4 -bits of signals is 24 rows long 2) We could cascade N 1 -bit shifters to make 1 N-bit shifter for sll, srl CS 61 C L 26 Combinational Logic Blocks (21) 12 a) FF b) FT c) TF d) TT Garcia, Fall 2014 © UCB

“And In conclusion…” • Use muxes to select among input • S input bits selects 2 S inputs • Each input can be n-bits wide, indep of S • Can implement muxes hierarchically • ALU can be implemented using a mux • Coupled with basic block elements • N-bit adder-subtractor done using N 1 bit adders with XOR gates on input • XOR serves as conditional inverter CS 61 C L 26 Combinational Logic Blocks (22) Garcia, Fall 2014 © UCB

- Slides: 22