14 332 331 Computer Architecture and Assembly Language

14: 332: 331 Computer Architecture and Assembly Language Fall 2003 Week 9 Building a Single-Cycle Datapath [Adapted from Dave Patterson’s UCB CS 152 slides and Mary Jane Irwin’s PSU CSE 331 slides] 331 W 9. 1 Spring 2005

Head’s Up q This week’s material l Building a MIPS single-cycle datapath - Reading assignment – PH 5. 4 331 W 9. 2 Spring 2005

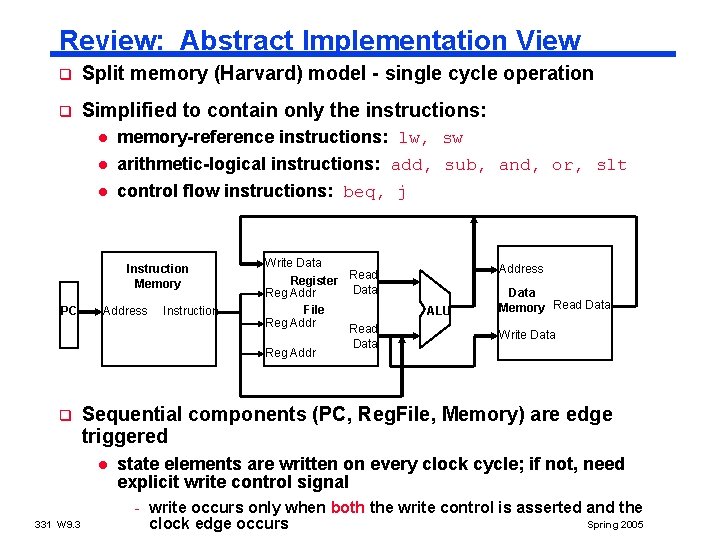

Review: Abstract Implementation View q Split memory (Harvard) model - single cycle operation q Simplified to contain only the instructions: l l l memory-reference instructions: lw, sw arithmetic-logical instructions: add, sub, and, or, slt control flow instructions: beq, j Instruction Memory PC q Address Register Read Data Reg Addr File Reg Addr Read Data Reg Address ALU Data Memory Read Data Write Data Sequential components (PC, Reg. File, Memory) are edge triggered l 331 W 9. 3 Instruction Write Data state elements are written on every clock cycle; if not, need explicit write control signal - write occurs only when both the write control is asserted and the Spring 2005 clock edge occurs

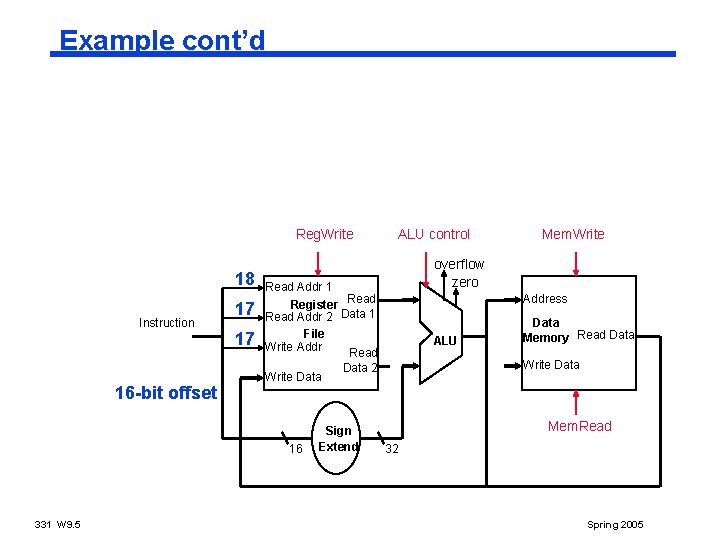

Example q Let’s modify the ISA and remove the ability to specify an offset for memory access instructions. Specifically, the load-store instructions would contain only two registers. In other words, all MIPS load-store instructions with offsets would become pseudoinstructions and would be implemented using two instructions: lw $t 0, 104($t 1) => 331 W 9. 4 Spring 2005

Example cont’d Reg. Write 18 Instruction 16 -bit offset 17 17 Write Data Address ALU Data Memory Read Data Write Data 2 Sign Extend Mem. Write overflow zero Read Addr 1 Register Read Addr 2 Data 1 File Write Addr Read 16 331 W 9. 5 ALU control Mem. Read 32 Spring 2005

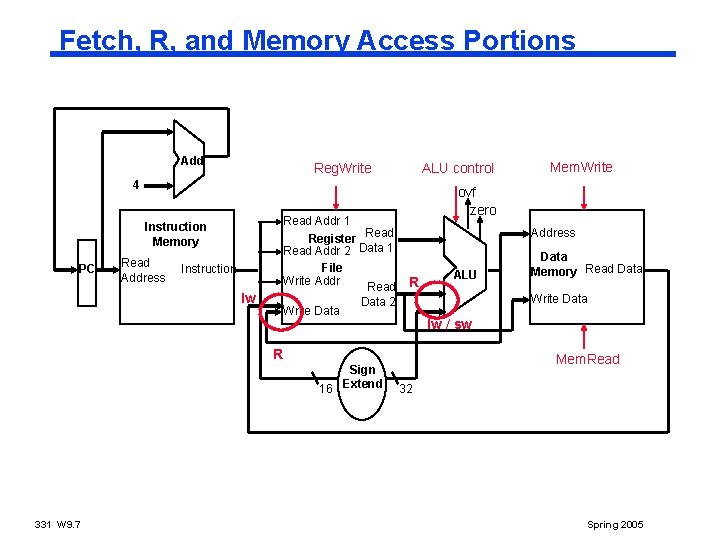

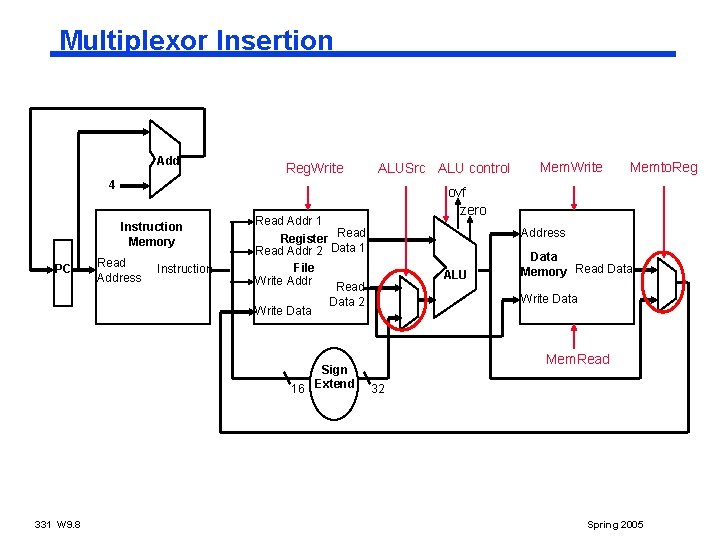

Creating a Single Datapath from the Parts q Assemble the datapath segments from the last lecture, add control lines as needed, and design the control path q Fetch, decode and execute each instructions in one clock cycle – single cycle design q 331 W 9. 6 l no datapath resource can be used more than once per instruction, so some must be duplicated (e. g. , why we have a separate Instruction Memory and Data Memory) l to share datapath elements between two different instruction classes will need multiplexors at the input of the shared elements with control lines to do the selection Cycle time is determined by length of the longest path Spring 2005

Fetch, R, and Memory Access Portions Add Reg. Write ALU control 4 Read Addr 1 Register Read Addr 2 Data 1 File Write Addr Read Instruction Memory PC Read Address Instruction lw Write Data ovf zero Address R Data Memory Read Data Write Data lw / sw R 331 W 9. 7 ALU Data 2 Sign 16 Extend Mem. Write Mem. Read 32 Spring 2005

Multiplexor Insertion Add Reg. Write ALUSrc ALU control 4 Instruction Memory PC Read Address Instruction 331 W 9. 8 Address ALU Data Memory Read Data Write Data 2 Sign 16 Extend Memto. Reg ovf zero Read Addr 1 Register Read Addr 2 Data 1 File Write Addr Read Write Data Mem. Write Mem. Read 32 Spring 2005

Adding the Branch Portion Branch not taken, R, lw /sw Add 4 Reg. Write Instruction Memory PC Add Shift left 2 Read Address Instruction ALUSrc ALU control ovf zero Read Addr 1 Register Read Addr 2 Data 1 File R Write Addr Read Write Data PCSrc ALU Data lw Memory Read Data Write Data R lw / sw 331 W 9. 9 Memto. Reg Address Data 2 Sign 16 Extend Mem. Write Mem. Read 32 Spring 2005

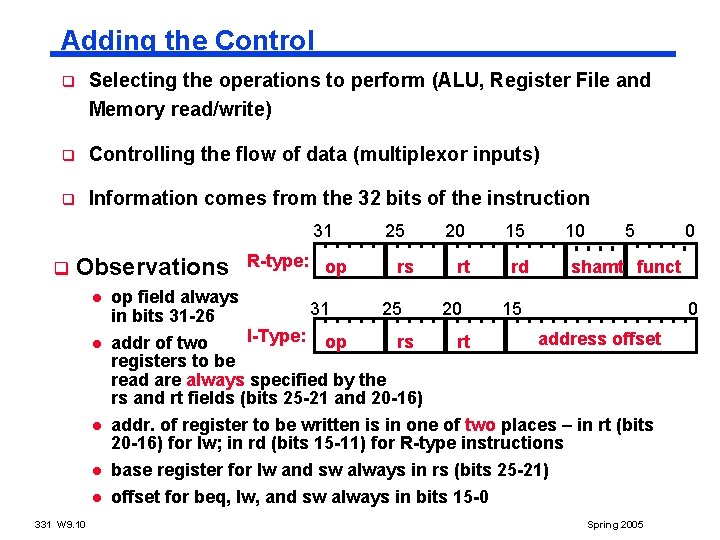

Adding the Control q Selecting the operations to perform (ALU, Register File and Memory read/write) q Controlling the flow of data (multiplexor inputs) q Information comes from the 32 bits of the instruction 31 q Observations l l l 331 W 9. 10 R-type: op 25 rs 20 15 rt rd 10 5 0 shamt funct op field always 31 25 20 15 in bits 31 -26 I-Type: op address offset rs rt addr of two registers to be read are always specified by the rs and rt fields (bits 25 -21 and 20 -16) addr. of register to be written is in one of two places – in rt (bits 20 -16) for lw; in rd (bits 15 -11) for R-type instructions base register for lw and sw always in rs (bits 25 -21) offset for beq, lw, and sw always in bits 15 -0 Spring 2005 0

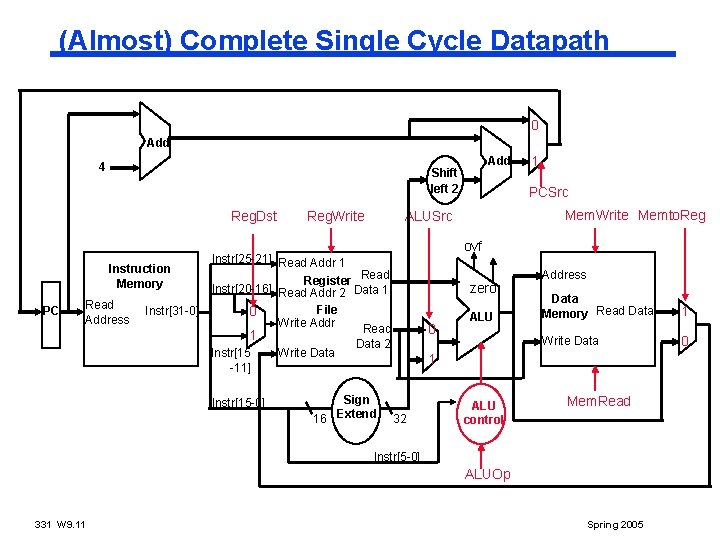

(Almost) Complete Single Cycle Datapath 0 Add 4 Reg. Dst Instruction Memory PC Add Shift left 2 Read Address Instr[31 -0] Reg. Write Instr[15 -0] Write Data Mem. Write Memto. Reg ovf Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[15 -11] PCSrc ALUSrc Instr[25 -21] Read Addr 1 1 1 zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Mem. Read Instr[5 -0] ALUOp 331 W 9. 11 Spring 2005

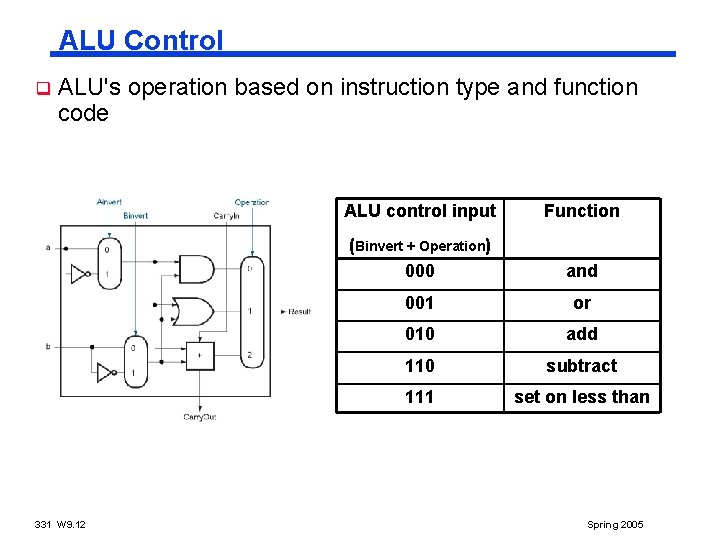

ALU Control q ALU's operation based on instruction type and function code 331 W 9. 12 ALU control input Function (Binvert + Operation) 000 and 001 or 010 add 110 subtract 111 set on less than Spring 2005

ALU Control, Con’t q Controlling the ALU makes use of multiple levels of decoding l main control unit generates the ALUOp bits l ALU control unit generates ALU control inputs Instr op 331 W 9. 13 funct ALUOp lw xxxxxx 00 desired action add ALU control input 0010 sw xxxxxx 00 add 0010 beq xxxxxx 01 sub 0110 add 100000 10 add 0010 subt 100010 10 subtract 0110 and 100100 10 and 0000 or 100101 10 or 0001 slt 101010 10 slt 0111 Spring 2005

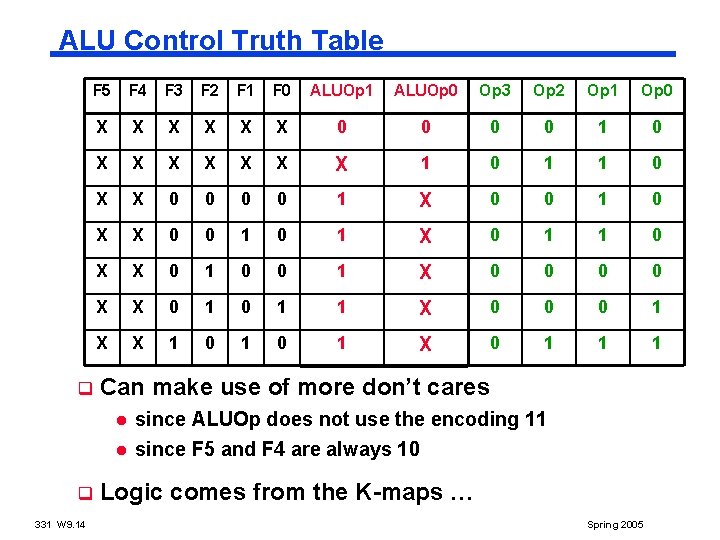

ALU Control Truth Table F 5 F 4 F 3 F 2 F 1 F 0 ALUOp 1 ALUOp 0 Op 3 Op 2 Op 1 Op 0 X X X 0 0 1 0 X X X X 1 0 1 1 0 X X 0 0 1 0 X X 0 0 1 X 0 1 1 0 X X 0 1 0 0 1 X 0 0 X X 0 1 1 X 0 0 0 1 X X 1 0 1 X 0 1 1 1 q Can make use of more don’t cares l l q 331 W 9. 14 since ALUOp does not use the encoding 11 since F 5 and F 4 are always 10 Logic comes from the K-maps … Spring 2005

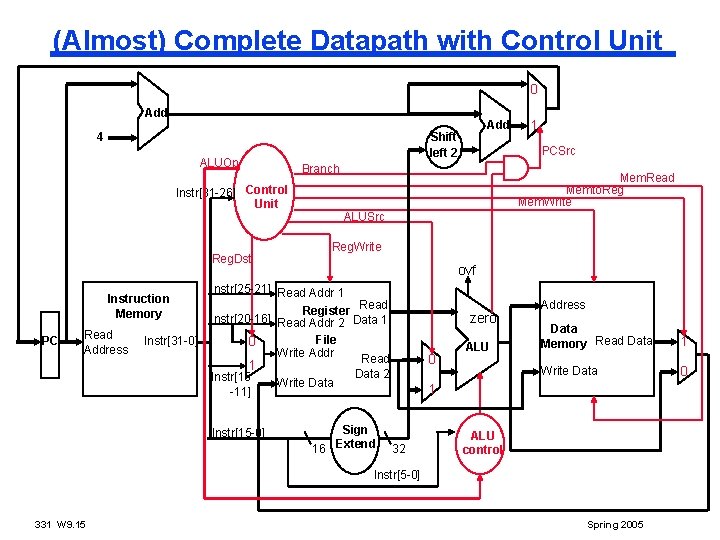

(Almost) Complete Datapath with Control Unit 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 15 Spring 2005

![R-type Instruction Data/Control Flow 0 Add ALUOp Instr[31 -26] Control Unit PC Read Address R-type Instruction Data/Control Flow 0 Add ALUOp Instr[31 -26] Control Unit PC Read Address](http://slidetodoc.com/presentation_image_h2/1784a5639c756b75b6f51467e292c78f/image-16.jpg)

R-type Instruction Data/Control Flow 0 Add ALUOp Instr[31 -26] Control Unit PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Reg. Dst Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 16 Spring 2005

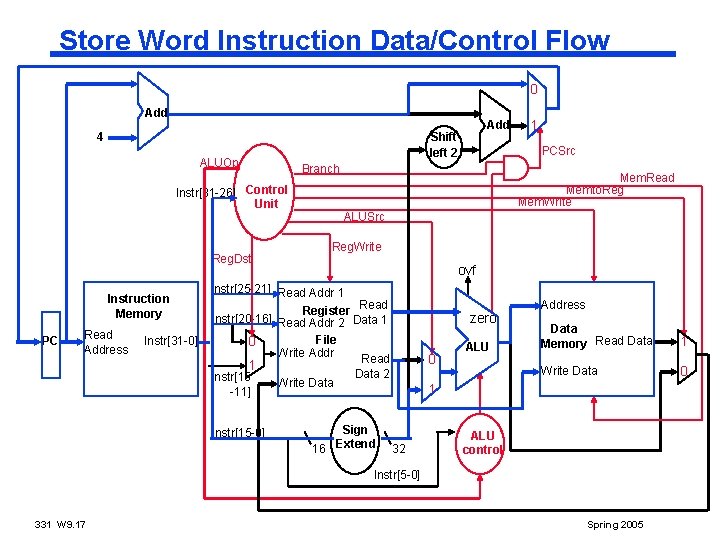

Store Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 17 Spring 2005

Load Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] PC Read Address Instr[31 -0] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 18 Spring 2005

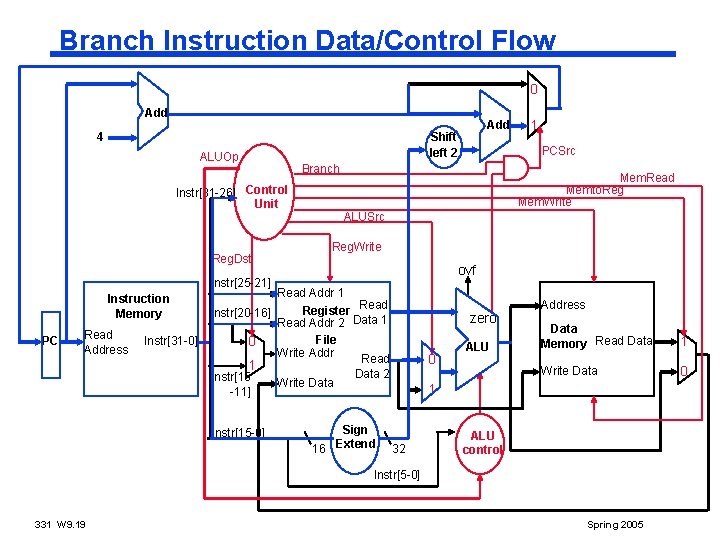

Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] PC Read Address Instr[31 -0] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 19 Spring 2005

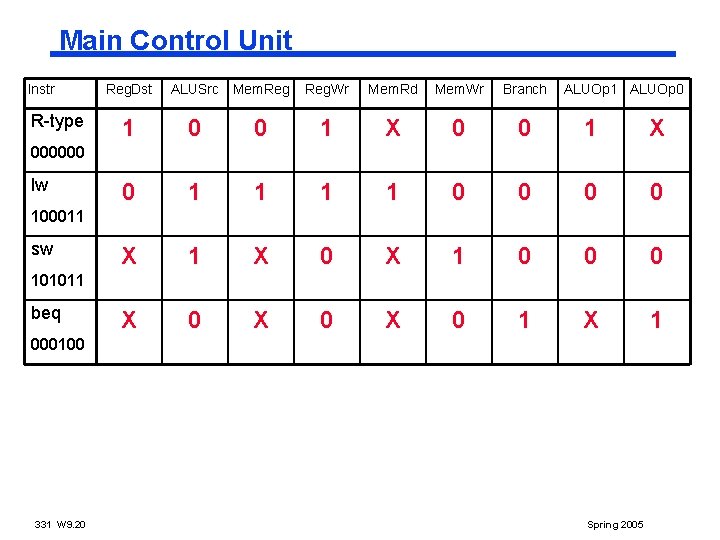

Main Control Unit Instr R-type Reg. Dst ALUSrc Mem. Reg. Wr Mem. Rd Mem. Wr Branch ALUOp 1 ALUOp 0 1 0 0 1 X 0 1 1 0 0 X 1 X 0 X 1 0 0 0 X 0 X 0 1 X 1 000000 lw 100011 sw 101011 beq 000100 331 W 9. 20 Spring 2005

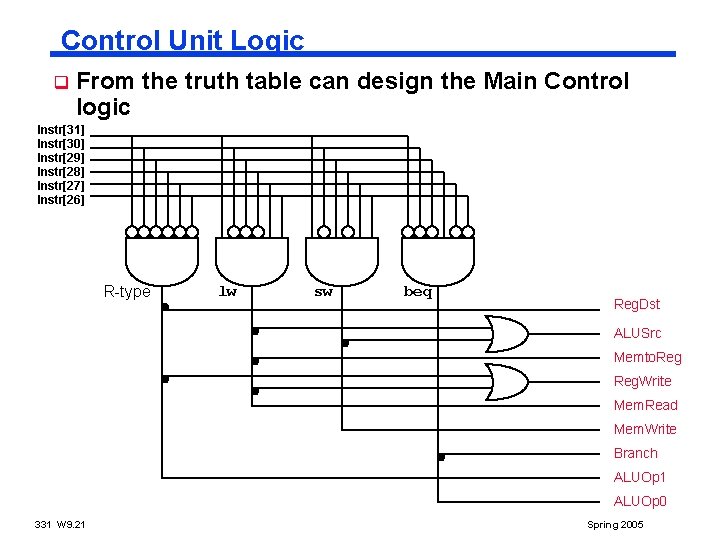

Control Unit Logic q From the truth table can design the Main Control logic Instr[31] Instr[30] Instr[29] Instr[28] Instr[27] Instr[26] R-type lw sw beq Reg. Dst ALUSrc Memto. Reg. Write Mem. Read Mem. Write Branch ALUOp 1 ALUOp 0 331 W 9. 21 Spring 2005

![Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0 Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0](http://slidetodoc.com/presentation_image_h2/1784a5639c756b75b6f51467e292c78f/image-22.jpg)

Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] 0 Add ALUOp Branch Instr[31 -26] Control Unit Reg. Dst Instruction Memory PC Read Address Instr[31 -0] Jump PCSrc ALUSrc Reg. Write ovf 1 Instr[15 -0] 1 Mem. Read Memto. Reg Mem. Write Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[15 -11] Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 22 Spring 2005

Single Cycle Implementation Cycle Time q Unfortunately, though simple, the single cycle approach is not used because it is inefficient q Clock cycle must have the same length for every instruction q What is the longest path (slowest instruction)? 331 W 9. 23 Spring 2005

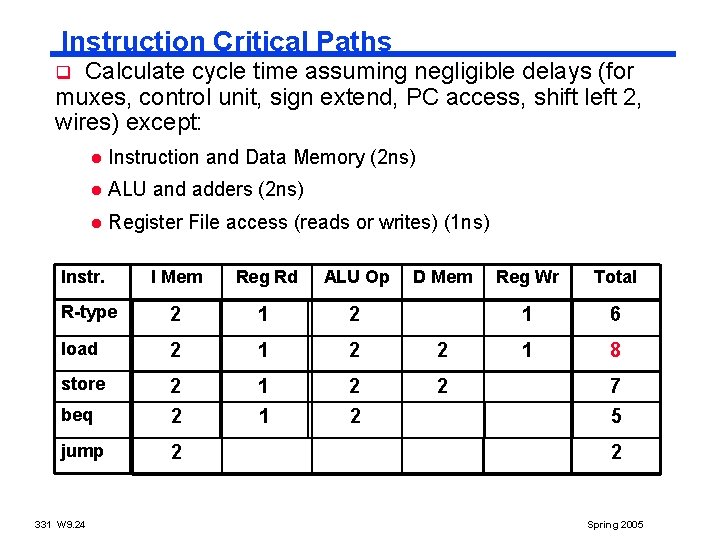

Instruction Critical Paths Calculate cycle time assuming negligible delays (for muxes, control unit, sign extend, PC access, shift left 2, wires) except: q l Instruction and Data Memory (2 ns) l ALU and adders (2 ns) l Register File access (reads or writes) (1 ns) Instr. I Mem Reg Rd ALU Op R-type 2 1 2 load 2 1 2 2 store 1 1 2 2 2 beq 2 2 jump 2 331 W 9. 24 D Mem Reg Wr Total 1 6 1 8 7 5 2 Spring 2005

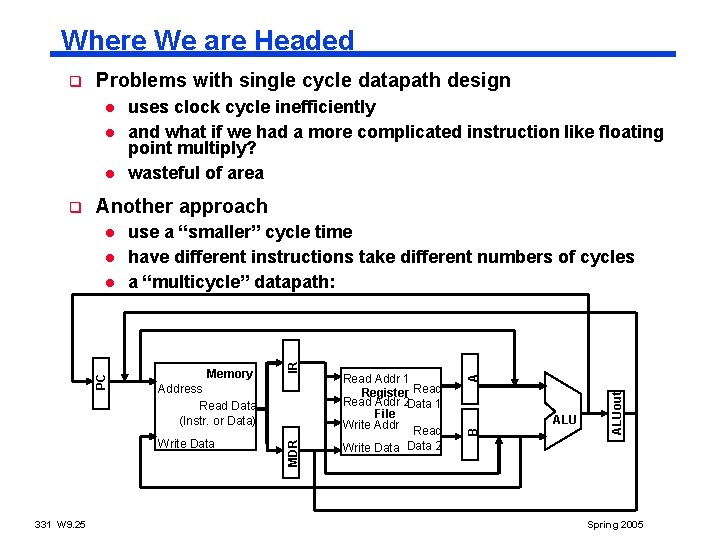

Where We are Headed Problems with single cycle datapath design l l l Another approach Memory Address Read Data (Instr. or Data) Write Data 331 W 9. 25 Read Addr 1 Register Read Addr 2 Data 1 File Write Addr Read Write Data 2 ALUout PC l A l use a “smaller” cycle time have different instructions take different numbers of cycles a “multicycle” datapath: B l IR q uses clock cycle inefficiently and what if we had a more complicated instruction like floating point multiply? wasteful of area MDR q Spring 2005

![Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28]](http://slidetodoc.com/presentation_image_h2/1784a5639c756b75b6f51467e292c78f/image-26.jpg)

Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] 0 Add ALUOp Branch Instr[31 -26] Control Unit Reg. Dst Instruction Memory PC Read Address Instr[31 -0] Jump PCSrc ALUSrc Reg. Write ovf 1 Instr[15 -0] 1 Mem. Read Memto. Reg Mem. Write Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[15 -11] Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 26 Spring 2005

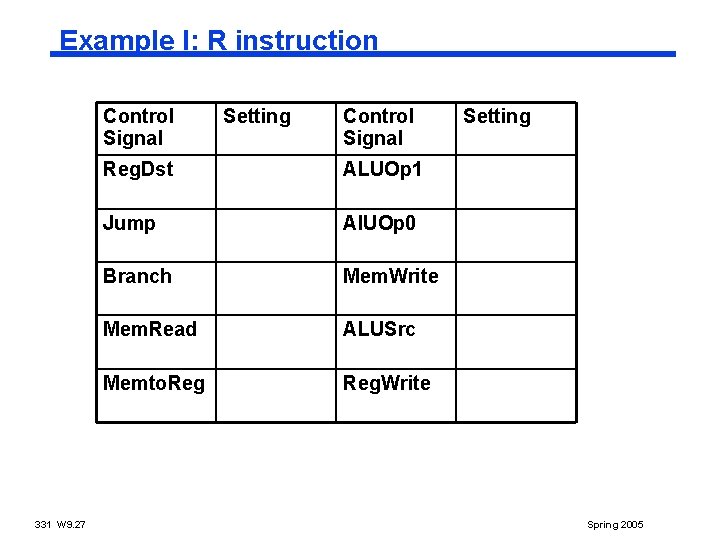

Example I: R instruction Control Signal 331 W 9. 27 Setting Control Signal Reg. Dst ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Setting Spring 2005

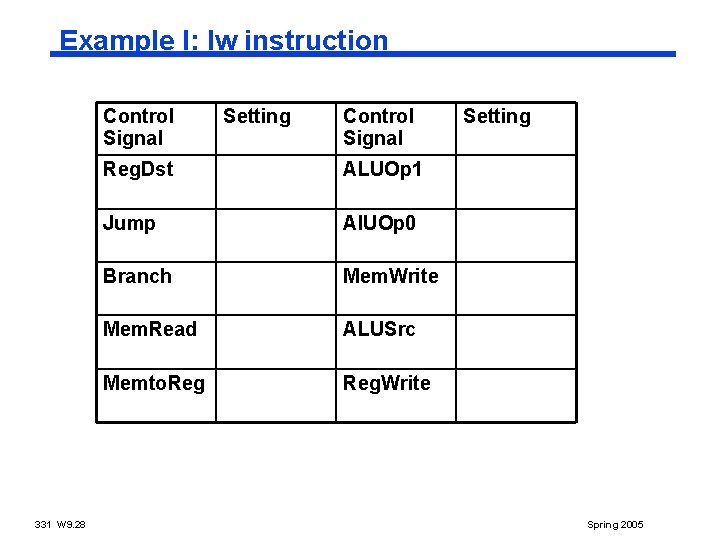

Example I: lw instruction Control Signal 331 W 9. 28 Setting Control Signal Reg. Dst ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Setting Spring 2005

Example I: sw instruction Control Signal 331 W 9. 29 Setting Control Signal Reg. Dst ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Setting Spring 2005

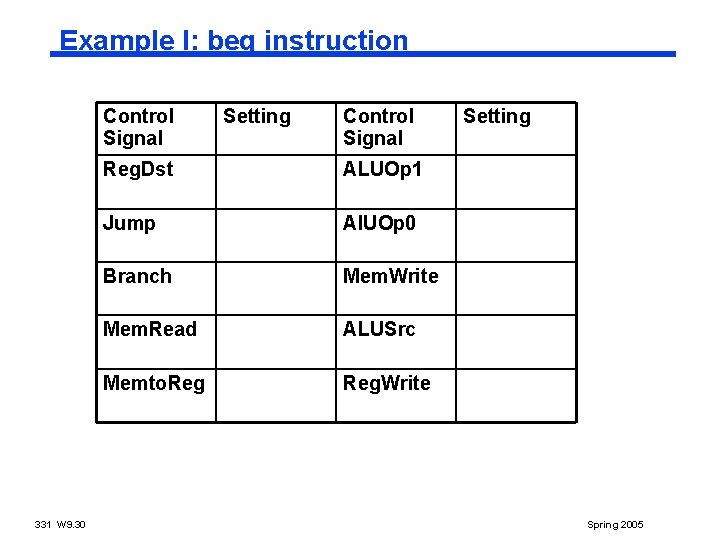

Example I: beq instruction Control Signal 331 W 9. 30 Setting Control Signal Reg. Dst ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Setting Spring 2005

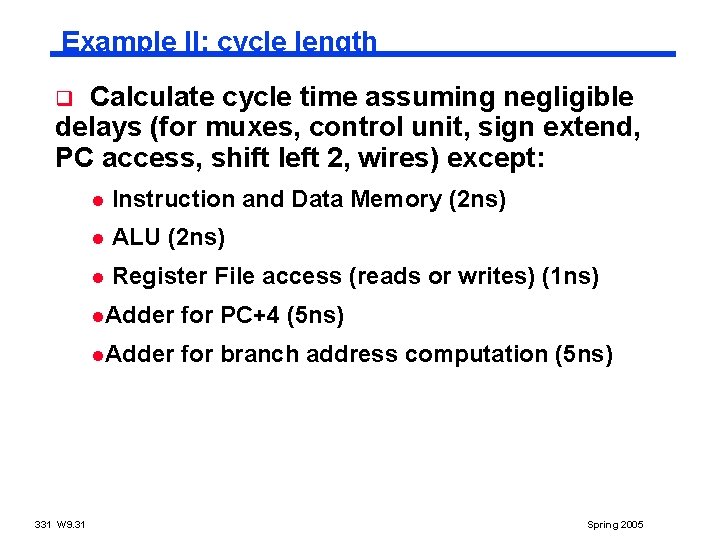

Example II: cycle length Calculate cycle time assuming negligible delays (for muxes, control unit, sign extend, PC access, shift left 2, wires) except: q 331 W 9. 31 l Instruction and Data Memory (2 ns) l ALU (2 ns) l Register File access (reads or writes) (1 ns) l. Adder for PC+4 (5 ns) l. Adder for branch address computation (5 ns) Spring 2005

Example III: q Describe the effect that a single stuck-at-0 fault (I. e. , regardless of what it should be, the signal is always 0) would have on the multiplexors in the single-cycle datapath. Which instruction, if any, would still work? Consider each of the following faults separately: Reg. Dst = 0, ALUSrc = 0, Memto. Reg = 0, Zero = 0; 331 W 9. 32 Spring 2005

Example IV: q We wish to add the instruction addi to the singlecycle datapath. Add any necessary datapaths and control signals. Control Signal Reg. Dst 331 W 9. 33 Setting Control Signal ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Setting Spring 2005

![Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28]](http://slidetodoc.com/presentation_image_h2/1784a5639c756b75b6f51467e292c78f/image-34.jpg)

Complete Datapath Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] 0 Add ALUOp Branch Instr[31 -26] Control Unit Reg. Dst Instruction Memory PC Read Address Instr[31 -0] Jump PCSrc ALUSrc Reg. Write ovf 1 Instr[15 -0] 1 Mem. Read Memto. Reg Mem. Write Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[15 -11] Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 331 W 9. 34 Spring 2005

![Example V: add jal Instr[25 -0] Shift left 2 26 28 1 32 0 Example V: add jal Instr[25 -0] Shift left 2 26 28 1 32 0](http://slidetodoc.com/presentation_image_h2/1784a5639c756b75b6f51467e292c78f/image-35.jpg)

Example V: add jal Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] 0 Add ALUOp Branch Instr[31 -26] Control Unit Reg. Dst 1 Reg. Dst Instr[25 -21] PC Jump PCSrc ALUSrc Reg. Write ovf 1 Instr[15 -0] 1 Mem. Read Memto. Reg Mem. Write Read Addr 1 Instruction Register Read Memory Instr[20 -16] Read Addr 2 Data 1 Instr[31 -0] Read File 0 Address Write Addr 31 Read Instr[15 -11] Add Shift left 2 4 Write Data zero 0 ALU Data 2 1 Sign 16 Extend 32 Memto. Reg 1 Address Data Memory 1 Read Data Write Data 1 0 ALU control Instr[5 -0] 331 W 9. 35 Spring 2005 0

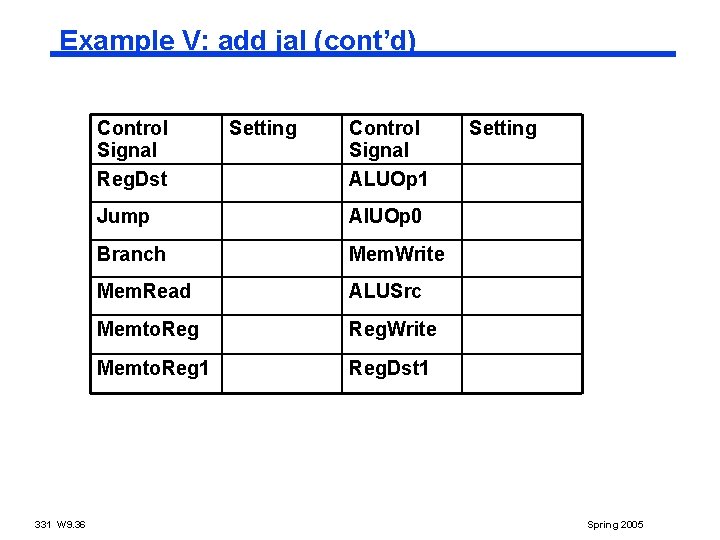

Example V: add jal (cont’d) Control Signal Reg. Dst 331 W 9. 36 Setting Control Signal ALUOp 1 Jump Al. UOp 0 Branch Mem. Write Mem. Read ALUSrc Memto. Reg. Write Memto. Reg 1 Reg. Dst 1 Setting Spring 2005

- Slides: 36