14 332 331 Computer Architecture and Assembly Language

14: 332: 331 Computer Architecture and Assembly Language Spring 06 Week 2 : ISA, MIPS Assembly [Adapted from Dave Patterson’s UCB CS 152 slides and Mary Jane Irwin’s PSU CSE 331 slides] 331 W 02. 1 Spring 06

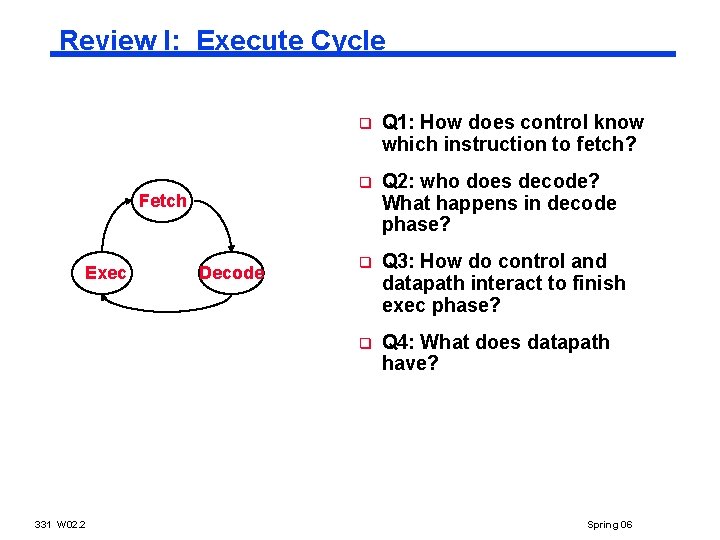

Review I: Execute Cycle Fetch Exec 331 W 02. 2 Decode q Q 1: How does control know which instruction to fetch? q Q 2: who does decode? What happens in decode phase? q Q 3: How do control and datapath interact to finish exec phase? q Q 4: What does datapath have? Spring 06

Review II: word length q What does 32 -bit architecture mean? 331 W 02. 3 Spring 06

Assembly Language q Language of the machine q More primitive than higher level languages q Very restrictive q We’ll be working with the MIPS instruction set architecture e. g. , no sophisticated control flow e. g. , MIPS arithmetic instructions l l l 331 W 02. 4 similar to other architectures developed since the 1980's used by NEC, Nintendo, Silicon Graphics, Sony, … 32 -bit architecture - 32 bit data line and address line - data and addresses are 32 -bit Spring 06

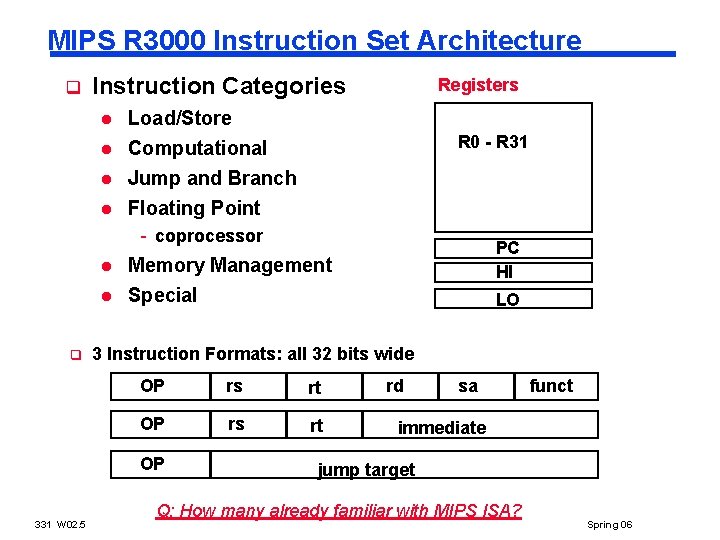

MIPS R 3000 Instruction Set Architecture q Instruction Categories l Load/Store Computational Jump and Branch l Floating Point l l Registers R 0 - R 31 - coprocessor q l Memory Management PC HI l Special LO 3 Instruction Formats: all 32 bits wide OP rs rt OP 331 W 02. 5 rd sa funct immediate jump target Q: How many already familiar with MIPS ISA? Spring 06

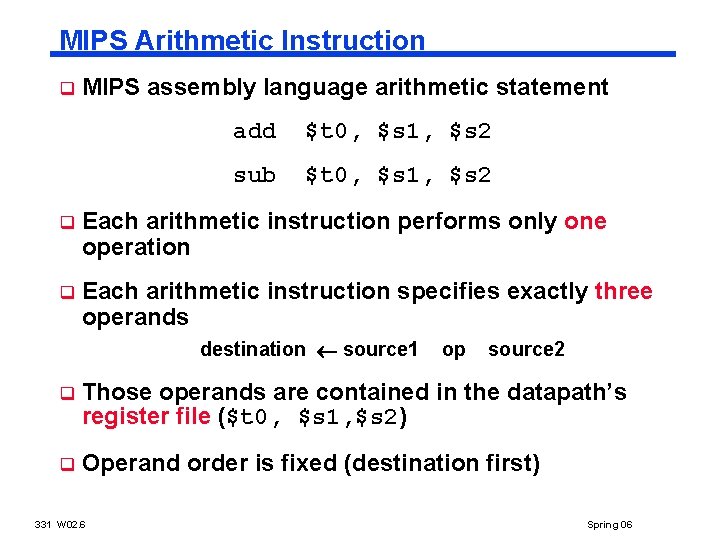

MIPS Arithmetic Instruction q MIPS assembly language arithmetic statement add $t 0, $s 1, $s 2 sub $t 0, $s 1, $s 2 q Each arithmetic instruction performs only one operation q Each arithmetic instruction specifies exactly three operands destination source 1 op source 2 q Those operands are contained in the datapath’s register file ($t 0, $s 1, $s 2) q Operand order is fixed (destination first) 331 W 02. 6 Spring 06

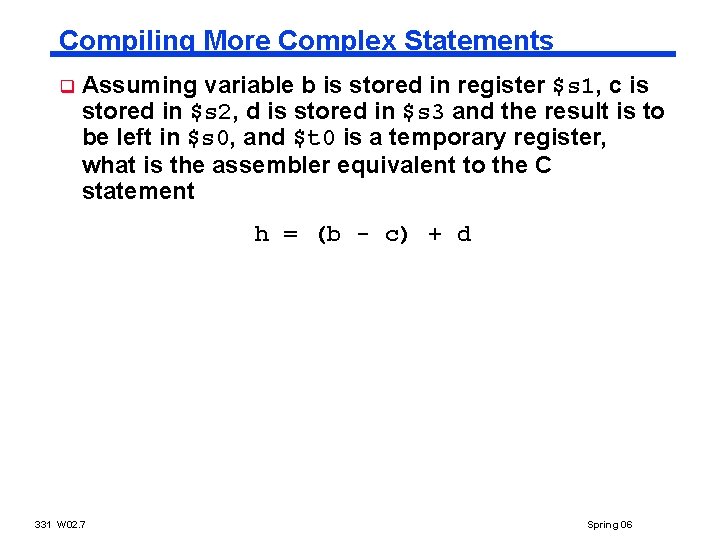

Compiling More Complex Statements q Assuming variable b is stored in register $s 1, c is stored in $s 2, d is stored in $s 3 and the result is to be left in $s 0, and $t 0 is a temporary register, what is the assembler equivalent to the C statement h = (b - c) + d 331 W 02. 7 Spring 06

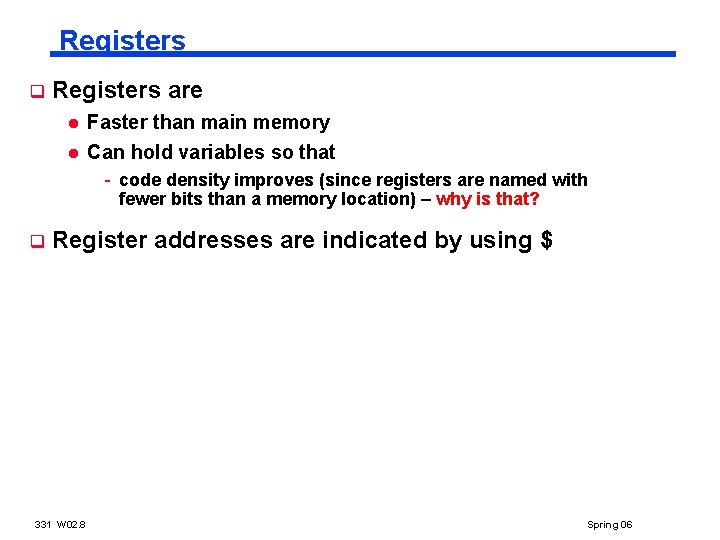

Registers q Registers are l l Faster than main memory Can hold variables so that - code density improves (since registers are named with fewer bits than a memory location) – why is that? q Register addresses are indicated by using $ 331 W 02. 8 Spring 06

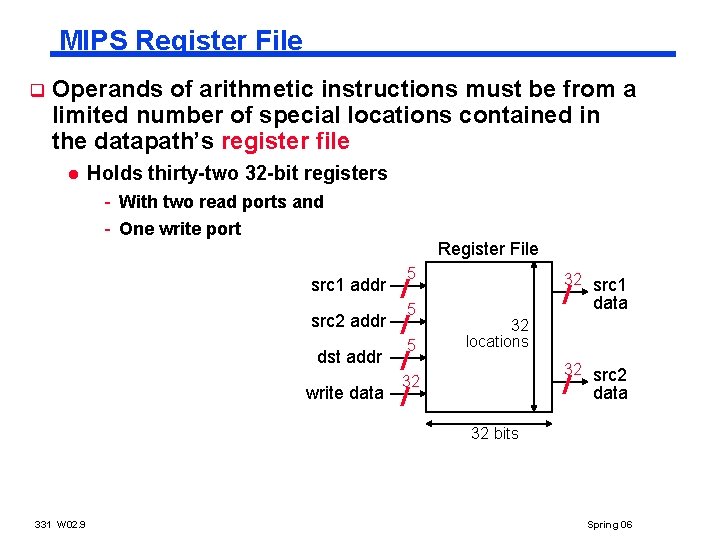

MIPS Register File q Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath’s register file l Holds thirty-two 32 -bit registers - With two read ports and - One write port src 1 addr src 2 addr dst addr write data Register File 5 5 5 32 src 1 data 32 locations 32 src 2 32 data 32 bits 331 W 02. 9 Spring 06

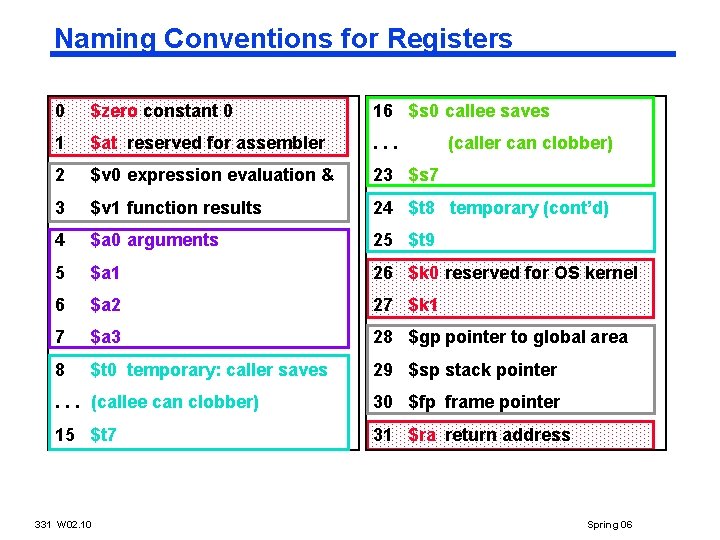

Naming Conventions for Registers 0 $zero constant 0 16 $s 0 callee saves 1 $at reserved for assembler . . . 2 $v 0 expression evaluation & 23 $s 7 3 $v 1 function results 24 $t 8 temporary (cont’d) 4 $a 0 arguments 25 $t 9 5 $a 1 26 $k 0 reserved for OS kernel 6 $a 2 27 $k 1 7 $a 3 28 $gp pointer to global area 8 $t 0 temporary: caller saves 29 $sp stack pointer (caller can clobber) . . . (callee can clobber) 30 $fp frame pointer 15 $t 7 31 $ra return address 331 W 02. 10 Spring 06

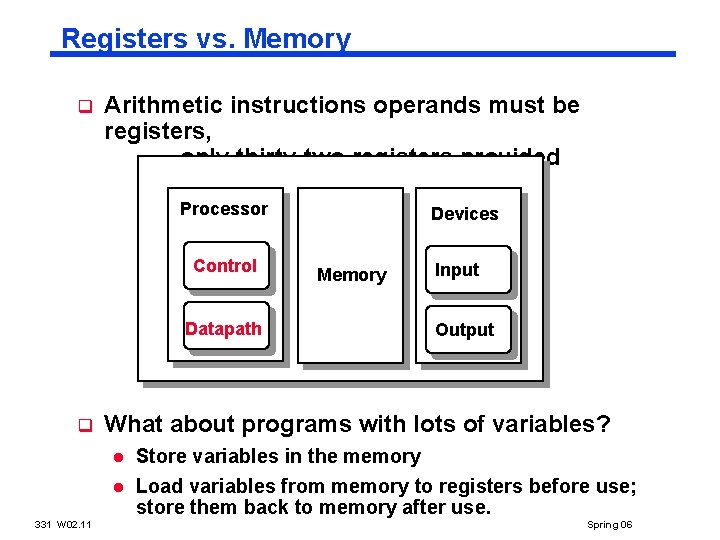

Registers vs. Memory q Arithmetic instructions operands must be registers, — only thirty-two registers provided Processor Control Datapath q Memory Input Output What about programs with lots of variables? l l 331 W 02. 11 Devices Store variables in the memory Load variables from memory to registers before use; store them back to memory after use. Spring 06

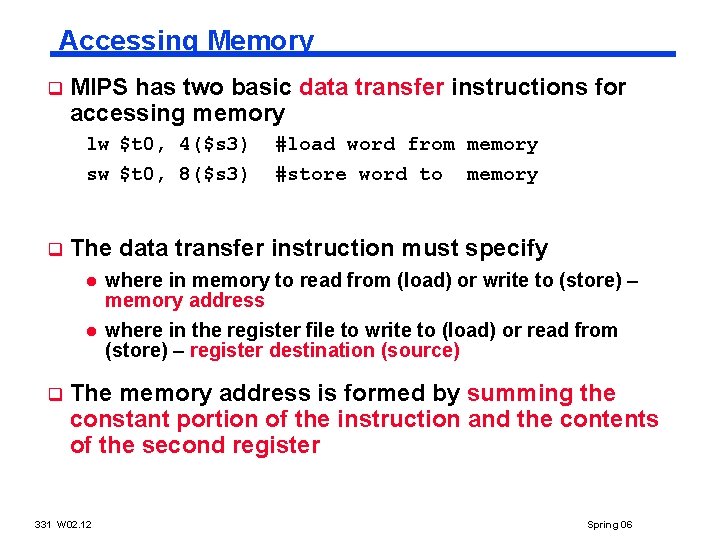

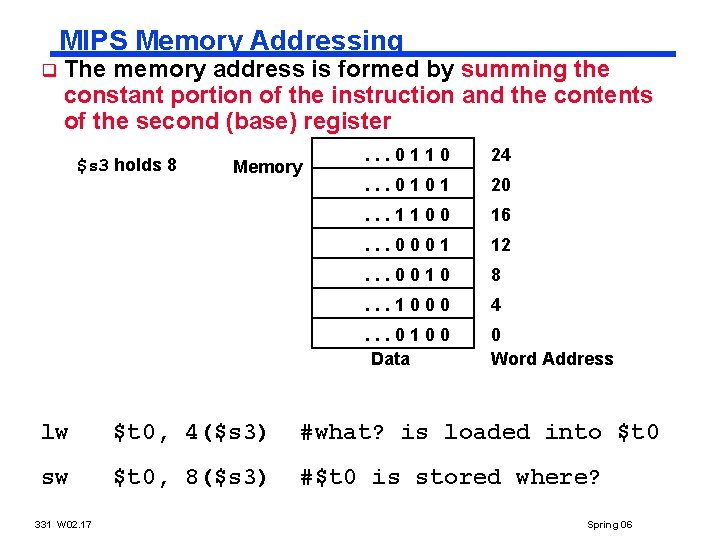

Accessing Memory q MIPS has two basic data transfer instructions for accessing memory lw $t 0, 4($s 3) sw $t 0, 8($s 3) q q #load word from memory #store word to memory The data transfer instruction must specify l where in memory to read from (load) or write to (store) – memory address l where in the register file to write to (load) or read from (store) – register destination (source) The memory address is formed by summing the constant portion of the instruction and the contents of the second register 331 W 02. 12 Spring 06

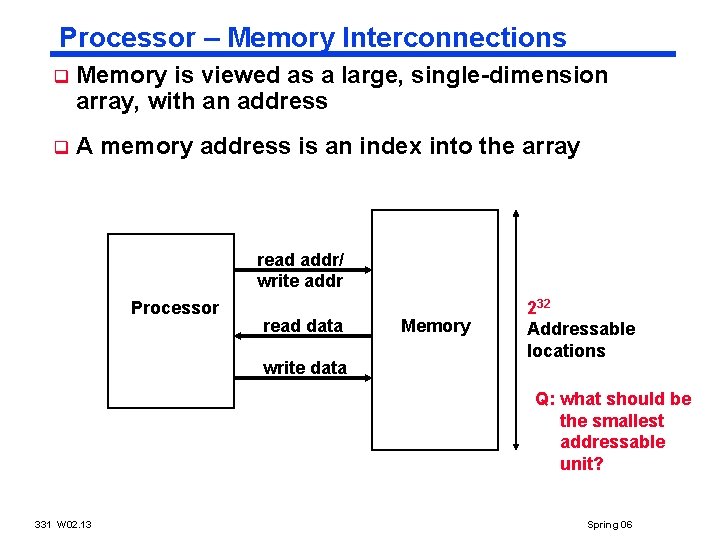

Processor – Memory Interconnections q Memory is viewed as a large, single-dimension array, with an address q A memory address is an index into the array read addr/ write addr Processor read data write data Memory 232 Addressable locations Q: what should be the smallest addressable unit? 331 W 02. 13 Spring 06

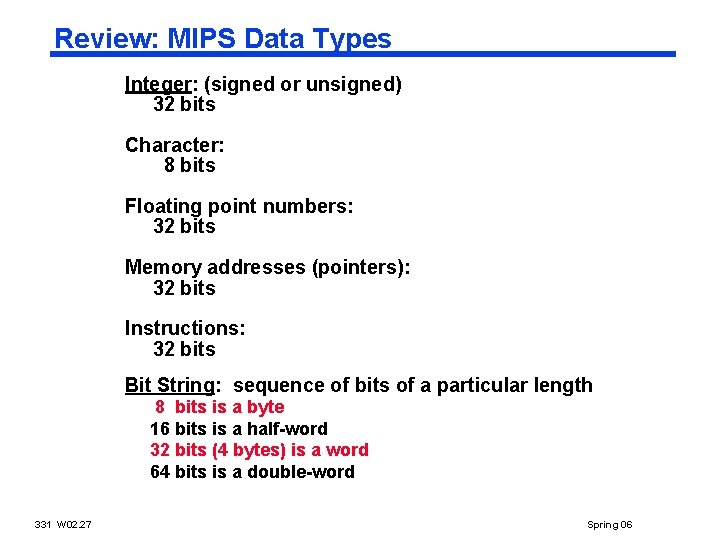

MIPS Data Types Integer: (signed or unsigned) 32 bits Character: 8 bits Floating point numbers: 32 bits Memory addresses (pointers): 32 bits Instructions: 32 bits Bit String: sequence of bits of a particular length 8 bits is a byte 16 bits is a half-word 32 bits (4 bytes) is a word 64 bits is a double-word 331 W 02. 14 Spring 06

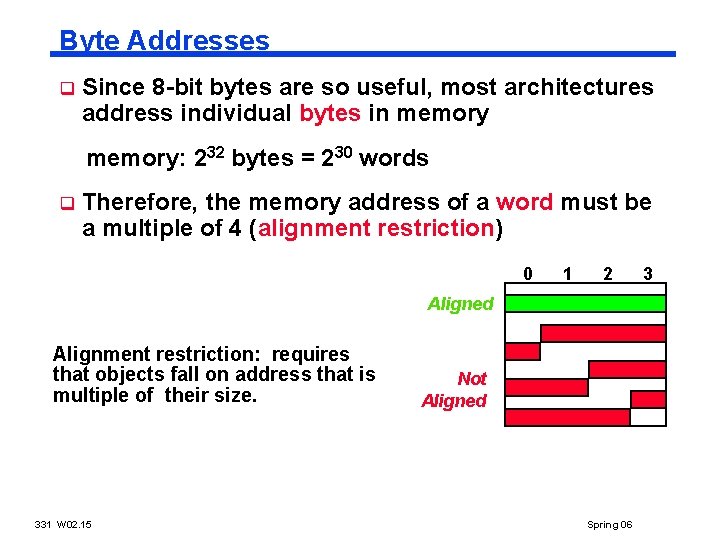

Byte Addresses q Since 8 -bit bytes are so useful, most architectures address individual bytes in memory: 232 bytes = 230 words q Therefore, the memory address of a word must be a multiple of 4 (alignment restriction) 0 1 2 Aligned Alignment restriction: requires that objects fall on address that is multiple of their size. 331 W 02. 15 Not Aligned Spring 06 3

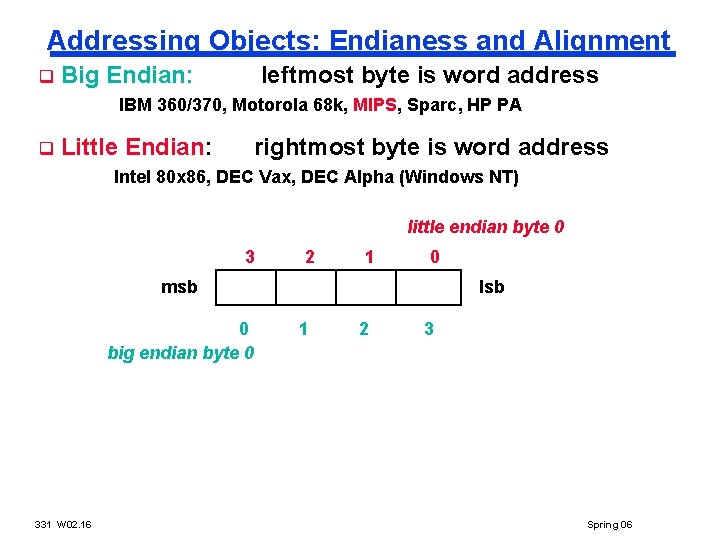

Addressing Objects: Endianess and Alignment q Big Endian: leftmost byte is word address IBM 360/370, Motorola 68 k, MIPS, Sparc, HP PA q Little Endian: rightmost byte is word address Intel 80 x 86, DEC Vax, DEC Alpha (Windows NT) little endian byte 0 3 2 1 0 msb 0 big endian byte 0 331 W 02. 16 lsb 1 2 3 Spring 06

MIPS Memory Addressing q The memory address is formed by summing the constant portion of the instruction and the contents of the second (base) register $s 3 holds 8 Memory . . . 0110 24 . . . 0101 20 . . . 1100 16 . . . 0001 12 . . . 0010 8 . . . 1000 4 . . . 0100 Data 0 Word Address lw $t 0, 4($s 3) #what? is loaded into $t 0 sw $t 0, 8($s 3) #$t 0 is stored where? 331 W 02. 17 Spring 06

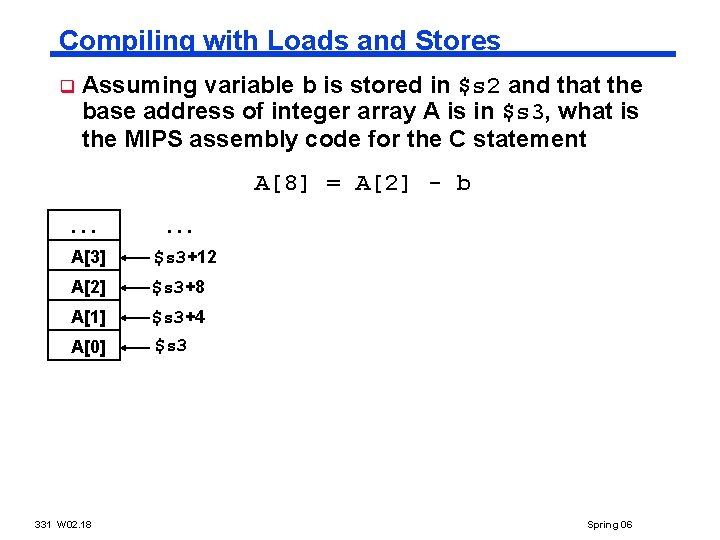

Compiling with Loads and Stores q Assuming variable b is stored in $s 2 and that the base address of integer array A is in $s 3, what is the MIPS assembly code for the C statement A[8] = A[2] - b . . . A[3] $s 3+12 A[2] $s 3+8 A[1] $s 3+4 A[0] $s 3 331 W 02. 18 Spring 06

Compiling with a Variable Array Index q Assuming A is an integer array whose base is in register $s 4, and variables b, c, and i are in $s 1, $s 2, and $s 3, respectively, what is the MIPS assembly code for the C statement c = A[i] - b 331 W 02. 19 Spring 06

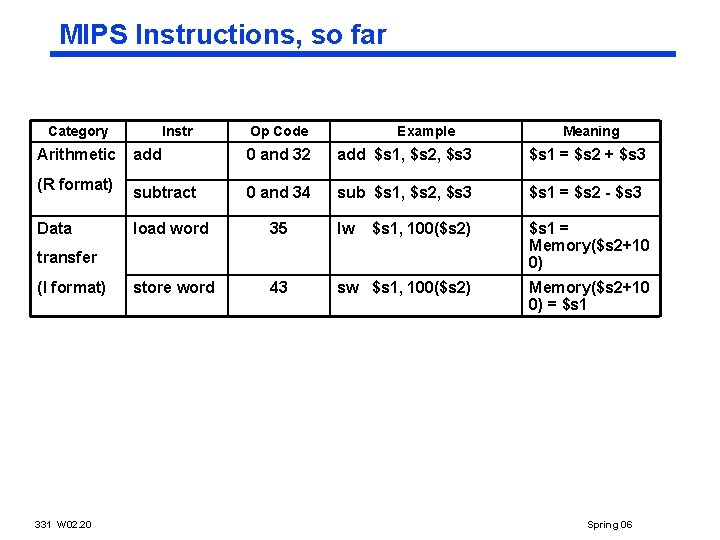

MIPS Instructions, so far Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 (R format) subtract 0 and 34 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 Data load word 35 lw $s 1, 100($s 2) $s 1 = Memory($s 2+10 0) store word 43 sw $s 1, 100($s 2) Memory($s 2+10 0) = $s 1 transfer (I format) 331 W 02. 20 Spring 06

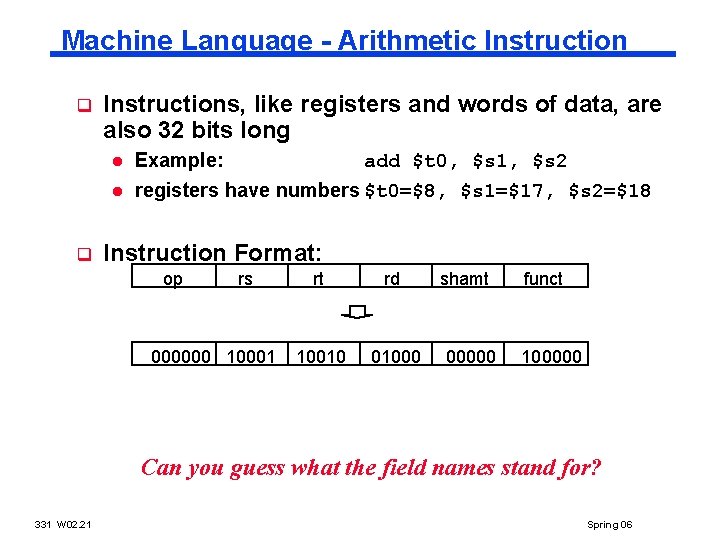

Machine Language - Arithmetic Instruction q Instructions, like registers and words of data, are also 32 bits long l l q Example: add $t 0, $s 1, $s 2 registers have numbers $t 0=$8, $s 1=$17, $s 2=$18 Instruction Format: op rs 000000 10001 rt rd 10010 01000 shamt 00000 funct 100000 Can you guess what the field names stand for? 331 W 02. 21 Spring 06

MIPS Instruction Fields q op q rs q rt q rd q shamt q funct 331 W 02. 22 op rs rt rd shamt 6 bits 5 bits funct 6 bits = 32 bits Spring 06

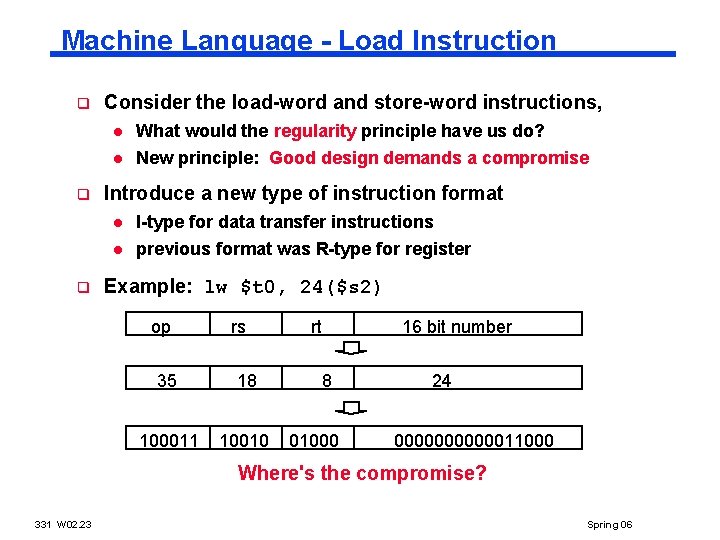

Machine Language - Load Instruction q Consider the load-word and store-word instructions, l l q Introduce a new type of instruction format l l q What would the regularity principle have us do? New principle: Good design demands a compromise I-type for data transfer instructions previous format was R-type for register Example: lw $t 0, 24($s 2) op rs 35 18 100011 10010 rt 16 bit number 8 01000 24 00000011000 Where's the compromise? 331 W 02. 23 Spring 06

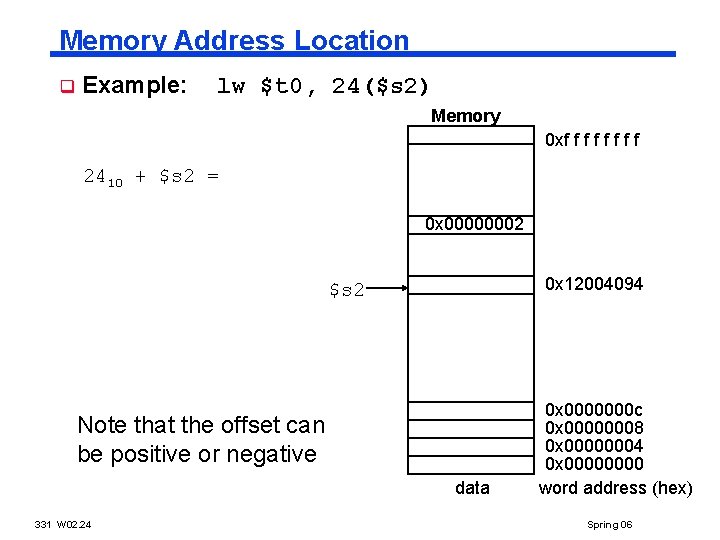

Memory Address Location q Example: lw $t 0, 24($s 2) Memory 0 xf f f f 2410 + $s 2 = 0 x 00000002 0 x 12004094 $s 2 Note that the offset can be positive or negative data 331 W 02. 24 0 x 0000000 c 0 x 00000008 0 x 00000004 0 x 0000 word address (hex) Spring 06

Machine Language - Store Instruction q Example: sw $t 0, 24($s 2) op q 331 W 02. 25 rs 43 18 101011 10010 rt 16 bit number 8 01000 24 00000011000 A 16 -bit address means access is limited to memory locations within a region of 213 or 8, 192 words ( 215 or 32, 768 bytes) of the address in the base register $s 2 Spring 06

![Assembling Code q Remember the assembler code we compiled for the C statement A[8] Assembling Code q Remember the assembler code we compiled for the C statement A[8]](http://slidetodoc.com/presentation_image/18e5b4819903306ca0986508e092c822/image-26.jpg)

Assembling Code q Remember the assembler code we compiled for the C statement A[8] = A[2] - b lw sub sw $t 0, 8($s 3) $t 0, $s 2 $t 0, 32($s 3) #load A[2] into $t 0 #subtract b from A[2] #store result in A[8] Assemble the MIPS object code for these three instructions 331 W 02. 26 Spring 06

Review: MIPS Data Types Integer: (signed or unsigned) 32 bits Character: 8 bits Floating point numbers: 32 bits Memory addresses (pointers): 32 bits Instructions: 32 bits Bit String: sequence of bits of a particular length 8 bits is a byte 16 bits is a half-word 32 bits (4 bytes) is a word 64 bits is a double-word 331 W 02. 27 Spring 06

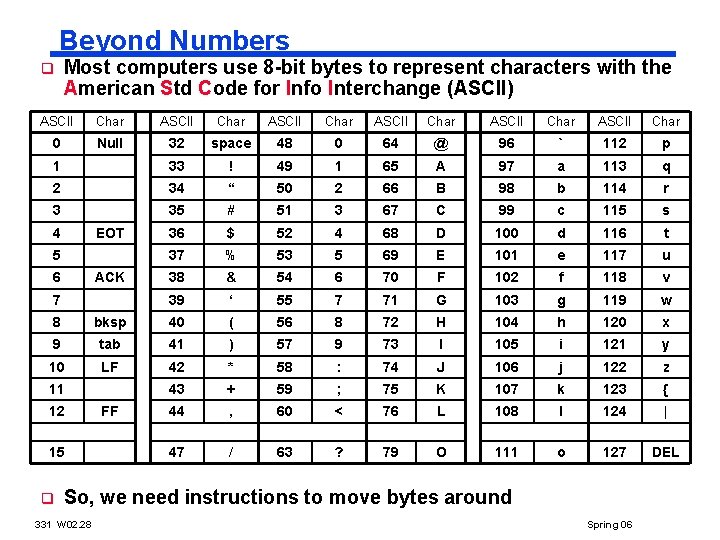

Beyond Numbers q Most computers use 8 -bit bytes to represent characters with the American Std Code for Info Interchange (ASCII) ASCII Char ASCII Char 0 Null 32 space 48 0 64 @ 96 ` 112 p 1 33 ! 49 1 65 A 97 a 113 q 2 34 “ 50 2 66 B 98 b 114 r 3 35 # 51 3 67 C 99 c 115 s 36 $ 52 4 68 D 100 d 116 t 37 % 53 5 69 E 101 e 117 u 38 & 54 6 70 F 102 f 118 v 39 ‘ 55 7 71 G 103 g 119 w 4 EOT 5 6 ACK 7 8 bksp 40 ( 56 8 72 H 104 h 120 x 9 tab 41 ) 57 9 73 I 105 i 121 y 10 LF 42 * 58 : 74 J 106 j 122 z 43 + 59 ; 75 K 107 k 123 { 44 , 60 < 76 L 108 l 124 | 47 / 63 ? 79 O 111 o 127 DEL 11 12 15 q FF So, we need instructions to move bytes around 331 W 02. 28 Spring 06

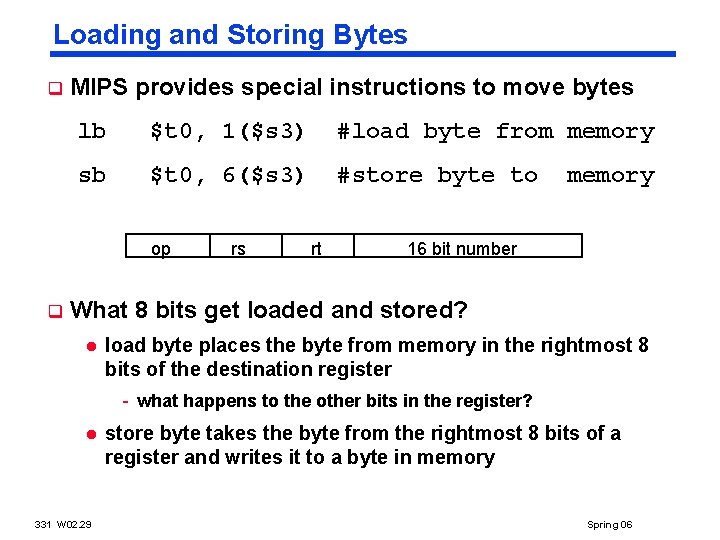

Loading and Storing Bytes q MIPS provides special instructions to move bytes lb $t 0, 1($s 3) #load byte from memory sb $t 0, 6($s 3) #store byte to op q rs rt memory 16 bit number What 8 bits get loaded and stored? l load byte places the byte from memory in the rightmost 8 bits of the destination register - what happens to the other bits in the register? l 331 W 02. 29 store byte takes the byte from the rightmost 8 bits of a register and writes it to a byte in memory Spring 06

Example of Loading and Storing Bytes q Given following code sequence and memory state (contents are given in hexidecimal), what is the state of the memory after executing the code? add $s 3, $zero lb $t 0, 1($s 3) sb $t 0, 6($s 3) Memory 0000 24 0000 20 0000 16 10000010 12 01000402 8 FFFF 4 009012 A 0 0 Data 331 W 02. 30 q q What value is left in $t 0? What if the machine was little Endian? Word Address (Decimal) Spring 06

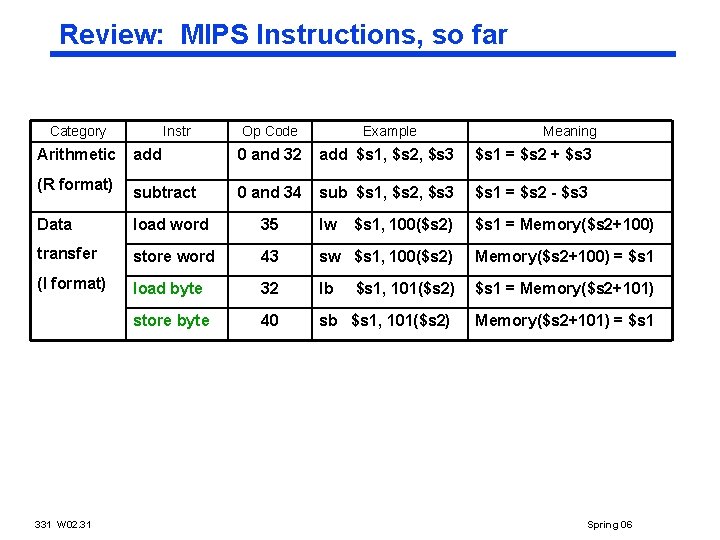

Review: MIPS Instructions, so far Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 (R format) subtract 0 and 34 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 Data load word 35 lw $s 1, 100($s 2) $s 1 = Memory($s 2+100) transfer store word 43 sw $s 1, 100($s 2) Memory($s 2+100) = $s 1 (I format) load byte 32 lb $s 1, 101($s 2) $s 1 = Memory($s 2+101) store byte 40 sb $s 1, 101($s 2) Memory($s 2+101) = $s 1 331 W 02. 31 Spring 06

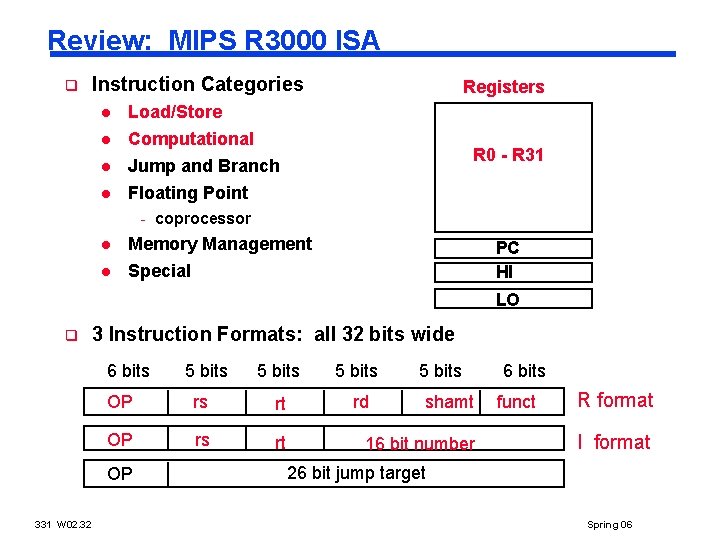

Review: MIPS R 3000 ISA q Instruction Categories l Load/Store l Computational Jump and Branch Floating Point l l Registers R 0 - R 31 - coprocessor l l Memory Management Special PC HI LO q 3 Instruction Formats: all 32 bits wide 6 bits 5 bits rd OP rs rt OP 331 W 02. 32 5 bits shamt 16 bit number 6 bits funct R format I format 26 bit jump target Spring 06

- Slides: 32