14 332 331 Computer Architecture and Assembly Language

14: 332: 331 Computer Architecture and Assembly Language Spring 2005 Week 7 [Adapted from Dave Patterson’s UCB CS 152 slides and Mary Jane Irwin’s PSU CSE 331 slides] Week 7. 1 Spring 2005

MIPS arithmetic instructions Instruction Example Meaning Comments add $1, $2, $3 $1 = $2 + $3 3 operands; exception possible subtract sub $1, $2, $3 $1 = $2 – $3 3 operands; exception possible add immediate addi $1, $2, 100 $1 = $2 + 100 + constant; exception possible add unsigned addu $1, $2, $3 $1 = $2 + $3 3 operands; no exceptions subtract unsigned subu $1, $2, $3 $1 = $2 – $3 3 operands; no exceptions add imm. unsign. addiu $1, $2, 100 $1 = $2 + 100 + constant; no exceptions multiply mult $2, $3 Hi, Lo = $2 x $3 64 -bit signed product multiply unsigned multu$2, $3 Hi, Lo = $2 x $3 64 -bit unsigned product divide div $2, $3 Lo = $2 ÷ $3, Lo = quotient, Hi = remainder Hi = $2 mod $3 divide unsigned divu $2, $3 Lo = $2 ÷ $3, Unsigned quotient & remainder Hi = $2 mod $3 Move from Hi mfhi $1 $1 = Hi Used to get copy of Hi Move from Lo mflo $1 $1 = Lo Used to get copy of Lo Week 7. 2 Spring 2005

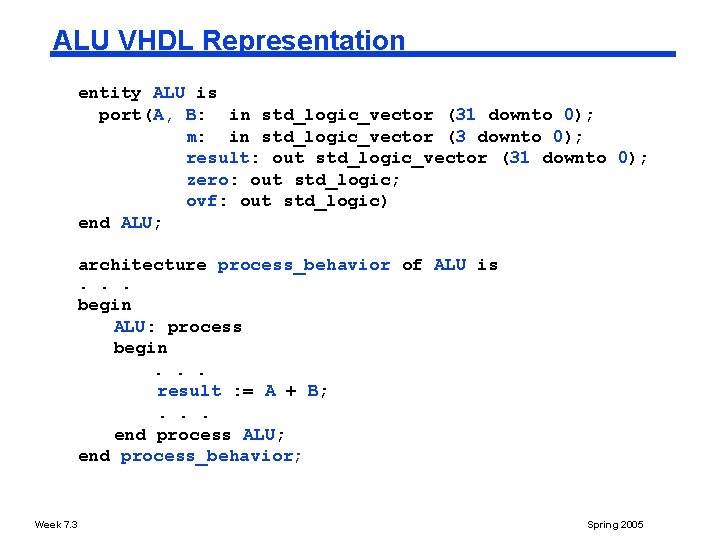

ALU VHDL Representation entity ALU is port(A, B: in std_logic_vector (31 downto 0); m: in std_logic_vector (3 downto 0); result: out std_logic_vector (31 downto 0); zero: out std_logic; ovf: out std_logic) end ALU; architecture process_behavior of ALU is. . . begin ALU: process begin. . . result : = A + B; . . . end process ALU; end process_behavior; Week 7. 3 Spring 2005

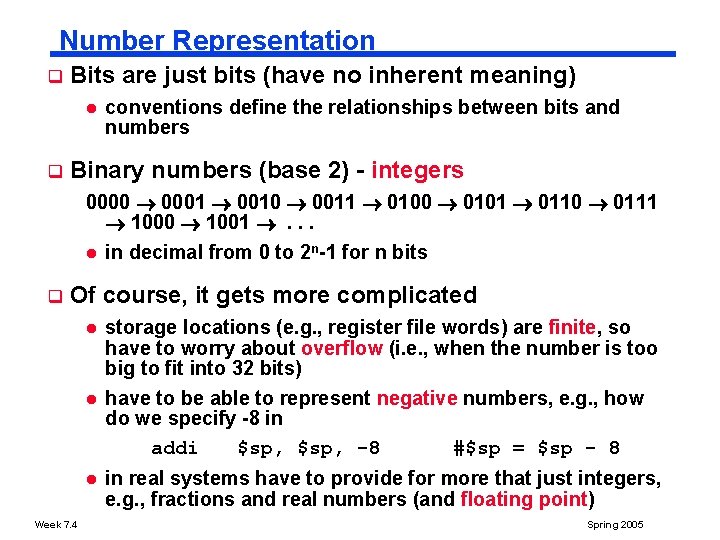

Number Representation q Bits are just bits (have no inherent meaning) l q conventions define the relationships between bits and numbers Binary numbers (base 2) integers 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 . . . l q in decimal from 0 to 2 n 1 for n bits Of course, it gets more complicated l l l Week 7. 4 storage locations (e. g. , register file words) are finite, so have to worry about overflow (i. e. , when the number is too big to fit into 32 bits) have to be able to represent negative numbers, e. g. , how do we specify 8 in addi $sp, -8 #$sp = $sp - 8 in real systems have to provide for more that just integers, e. g. , fractions and real numbers (and floating point) Spring 2005

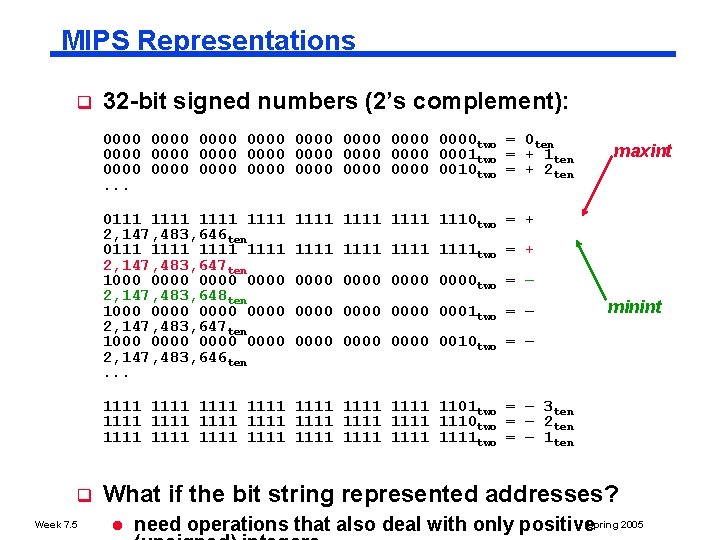

MIPS Representations q 32 bit signed numbers (2’s complement): 0000 0000 two = 0 ten 0000 0000 0001 two = + 1 ten 0000 0000 0010 two = + 2 ten. . . 0111 1111 2, 147, 483, 646 ten 0111 1111 2, 147, 483, 647 ten 1000 0000 2, 147, 483, 648 ten 1000 0000 2, 147, 483, 647 ten 1000 0000 2, 147, 483, 646 ten. . . maxint 1111 1110 two = + 1111 two = + 0000 two = – 0000 0001 two = – minint 0000 0010 two = – 1111 1111 1101 two = – 3 ten 1111 1111 1110 two = – 2 ten 1111 1111 two = – 1 ten q Week 7. 5 What if the bit string represented addresses? l need operations that also deal with only positive. Spring 2005

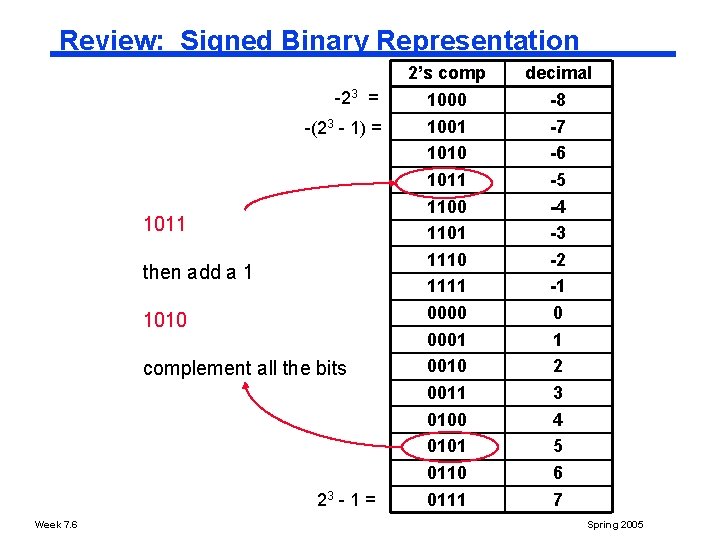

Review: Signed Binary Representation -23 = -(23 - 1) = 1011 then add a 1 1010 complement all the bits 23 - 1 = Week 7. 6 2’s comp 1000 1001 1010 1011 1100 1101 1110 1111 0000 0001 0010 0011 0100 0101 0110 0111 decimal 8 7 6 5 4 3 2 1 0 1 2 3 4 5 6 7 Spring 2005

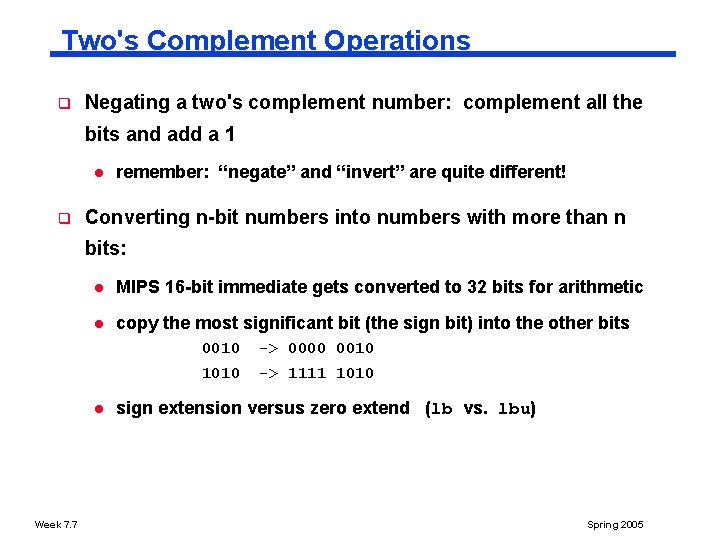

Two's Complement Operations q Negating a two's complement number: complement all the bits and add a 1 l q remember: “negate” and “invert” are quite different! Converting n bit numbers into numbers with more than n bits: l MIPS 16 bit immediate gets converted to 32 bits for arithmetic l copy the most significant bit (the sign bit) into the other bits l Week 7. 7 0010 -> 0000 0010 1010 -> 1111 1010 sign extension versus zero extend (lb vs. lbu) Spring 2005

Goal: Design an ALU for the MIPS ISA q Must support the Arithmetic/Logic operations of the ISA q Tradeoffs of cost and speed based on frequency of occurrence, hardware budget Week 7. 8 Spring 2005

MIPS Arithmetic and Logic Instructions 31 Type ADDI 25 20 R-type: op Rs Rt I-Type: op Rs Rt op funct Type 15 5 Rd 0 funct Immed 16 op funct Type op funct 001000 xx ADD 000000 1000000 101000 ADDIU 001001 xx ADDU 000000 100001 000000 101001 SLTI SUB 000000 100010 SLT 000000 101010 SLTIU 001011 xx SUBU 000000 100011 SLTU 000000 101011 ANDI 001100 xx AND 000000 100100 000000 101100 ORI 001101 xx OR XORI 001110 xx XOR 000000 100110 LUI 001111 xx NOR 000000 100111 q 001010 xx 000000 100101 Signed arithmetic generates overflow, but no carry out Week 7. 9 Spring 2005

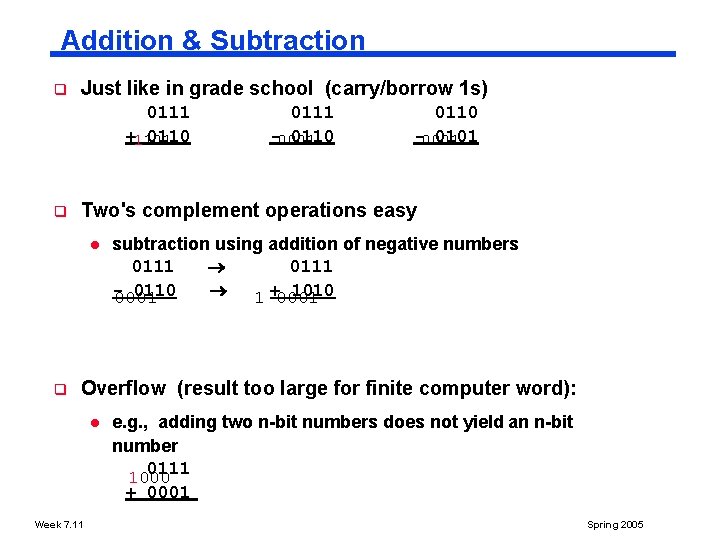

Addition & Subtraction q Just like in grade school (carry/borrow 1 s) 0111 +1101 0110 q 0110 -0001 0101 Two's complement operations easy l q 0111 -0001 0110 subtraction using addition of negative numbers 0111 -0001 0110 1010 1 +0001 Overflow (result too large for finite computer word): l Week 7. 11 e. g. , adding two n bit numbers does not yield an n bit number 0111 1000 + 0001 Spring 2005

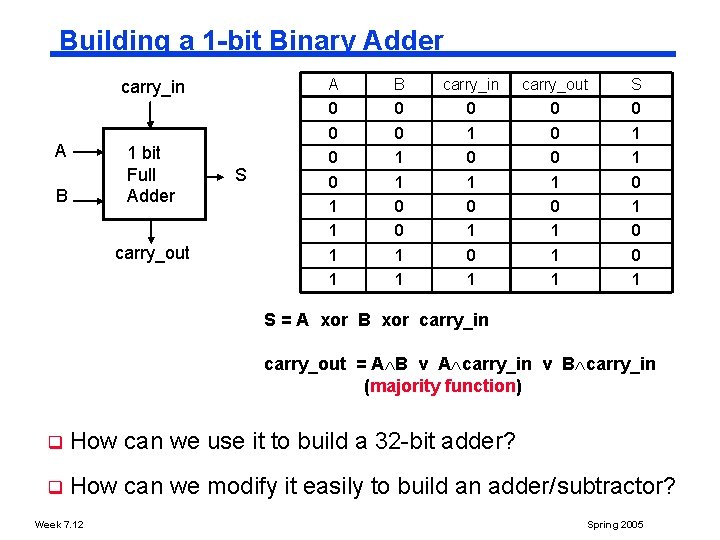

Building a 1 bit Binary Adder carry_in A 1 bit Full Adder B carry_out S A B carry_in carry_out S 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 S = A xor B xor carry_in carry_out = A B v A carry_in v B carry_in (majority function) q How can we use it to build a 32 -bit adder? q How can we modify it easily to build an adder/subtractor? Week 7. 12 Spring 2005

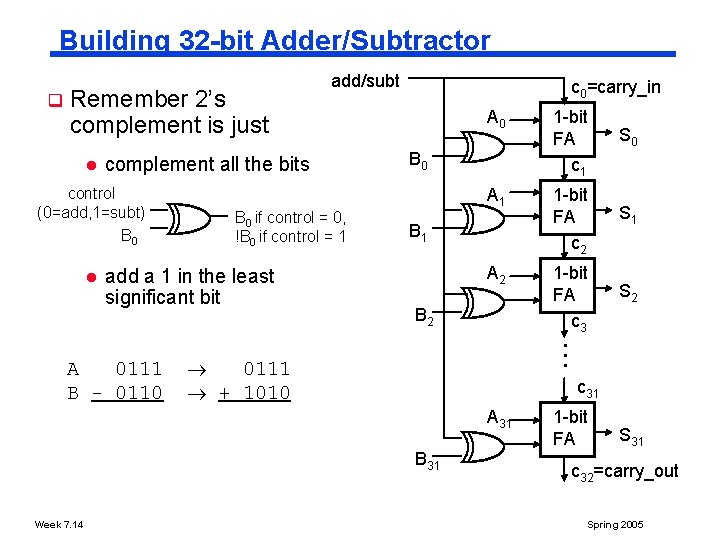

Building 32 bit Adder c 0=carry_in A 0 B 0 A 1 B 1 A 2 S 0 1 -bit FA c 2 S 1 1 -bit FA c 3 S 2 q Just connect the carry-out of the least significant bit FA to the carry-in of the next least significant bit and connect. . . B 2 1 -bit FA c 1 c 31 A 31 B 31 1 -bit FA S 31 c 32=carry_out Week 7. 13 Spring 2005

Building 32 bit Adder/Subtractor Remember 2’s complement is just l complement all the bits control (0=add, 1=subt) B 0 l B 0 if control = 0, !B 0 if control = 1 add a 1 in the least significant bit A 0111 B - 0110 c 0=carry_in A 0 1 -bit FA c 1 S 0 A 1 1 -bit FA c 2 S 1 A 2 1 -bit FA c 3 S 2 B 0 B 1 B 2 . . . q add/subt 0111 + 1010 c 31 A 31 B 31 Week 7. 14 1 -bit FA S 31 c 32=carry_out Spring 2005

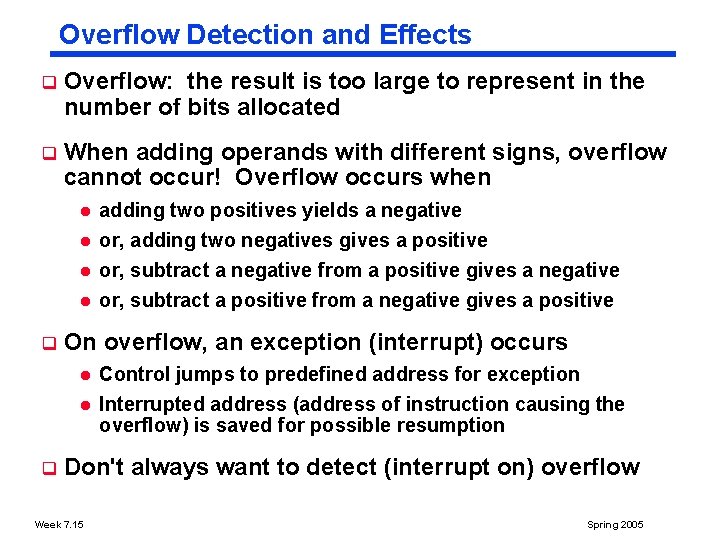

Overflow Detection and Effects q Overflow: the result is too large to represent in the number of bits allocated q When adding operands with different signs, overflow cannot occur! Overflow occurs when q l adding two positives yields a negative l or, adding two negatives gives a positive l or, subtract a negative from a positive gives a negative l or, subtract a positive from a negative gives a positive On overflow, an exception (interrupt) occurs l l q Control jumps to predefined address for exception Interrupted address (address of instruction causing the overflow) is saved for possible resumption Don't always want to detect (interrupt on) overflow Week 7. 15 Spring 2005

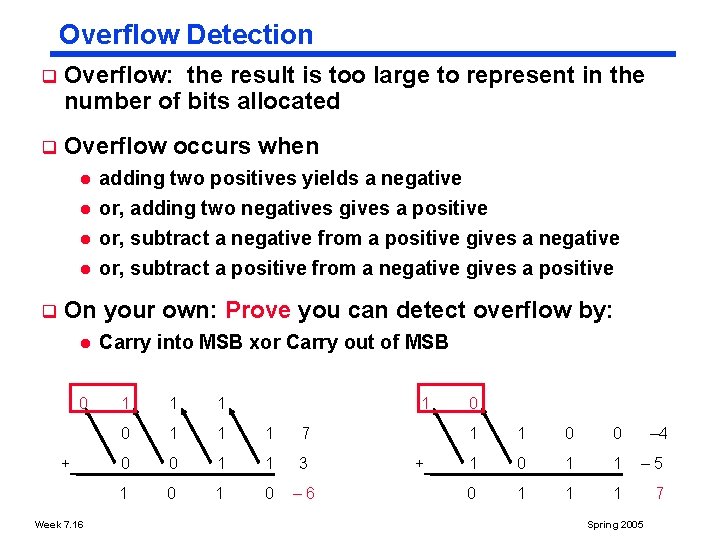

Overflow Detection q Overflow: the result is too large to represent in the number of bits allocated q Overflow occurs when q l adding two positives yields a negative l or, adding two negatives gives a positive l or, subtract a negative from a positive gives a negative l or, subtract a positive from a negative gives a positive On your own: Prove you can detect overflow by: l 0 + Week 7. 16 Carry into MSB xor Carry out of MSB 1 1 0 1 1 1 7 0 0 1 1 3 1 0 – 6 + 0 1 1 0 0 – 4 1 0 1 1 – 5 0 1 1 1 7 Spring 2005

A Simple ALU Cell add/subt carry_in op AND A A and B A and !B A or !B OR XOR A xor B A xor !B result A nor B NOR A nor !B B or !B 1 -bit FA Mux B add/subt Week 7. 17 carry_out A+B A -B Spring 2005

A Simple 32 bit ALU add/sub op Add/ Op A 0 result 0 B 0 + A 1 result 1 B 1 + . . . A 31 subt 0 1 0 1 0 1 000 001 010 011 100 operation A and B A and !B A or !B A xor !B A nor !B A+B A B result 31 B 31 Week 7. 18 + Spring 2005

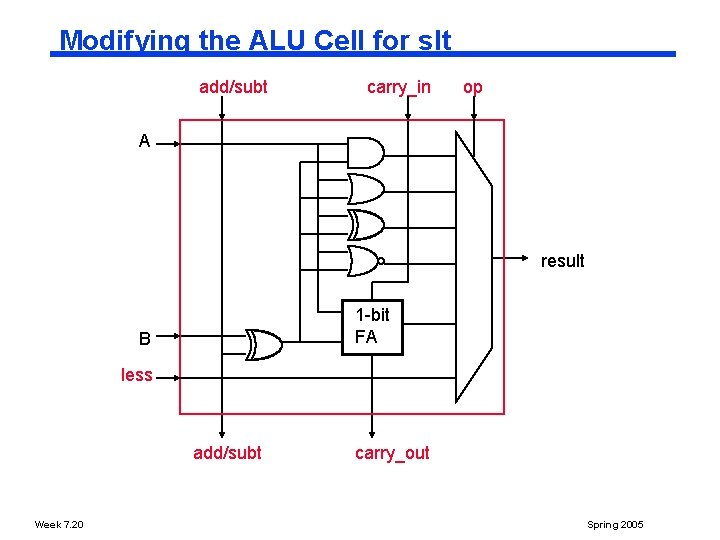

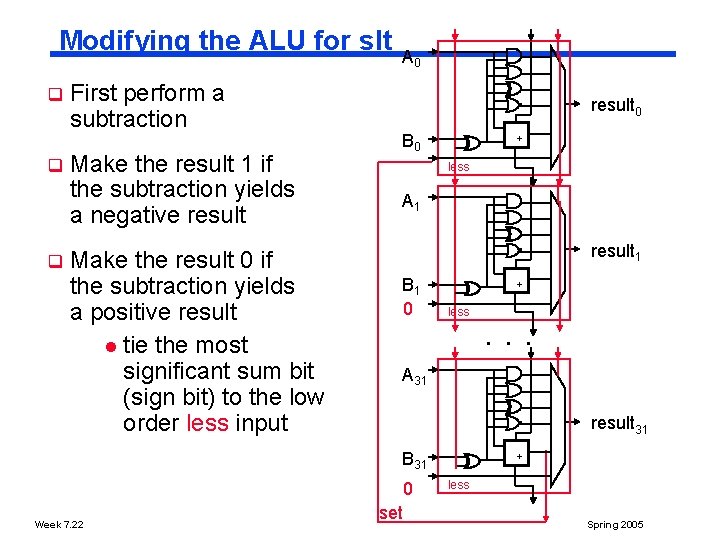

Tailoring the ALU to the MIPS ISA q q Need to support the set on less than instruction (slt) l remember: slt is an arithmetic instruction l produces a 1 if rs < rt and 0 otherwise l use subtraction: (a b) < 0 implies a < b Need to support test for equality (beq) l q Week 7. 19 use subtraction: (a b) = 0 implies a = b Need to add the overflow detection hardware Spring 2005

Modifying the ALU Cell for slt add/subt carry_in op A result 1 -bit FA B less add/subt Week 7. 20 carry_out Spring 2005

Modifying the ALU for slt q q q First perform a subtraction Make the result 1 if the subtraction yields a negative result Make the result 0 if the subtraction yields a positive result l tie the most significant sum bit (sign bit) to the low order less input A 0 result 0 B 0 + less A 1 result 1 B 1 0 + less . . . A 31 result 31 B 31 0 Week 7. 22 set + less Spring 2005

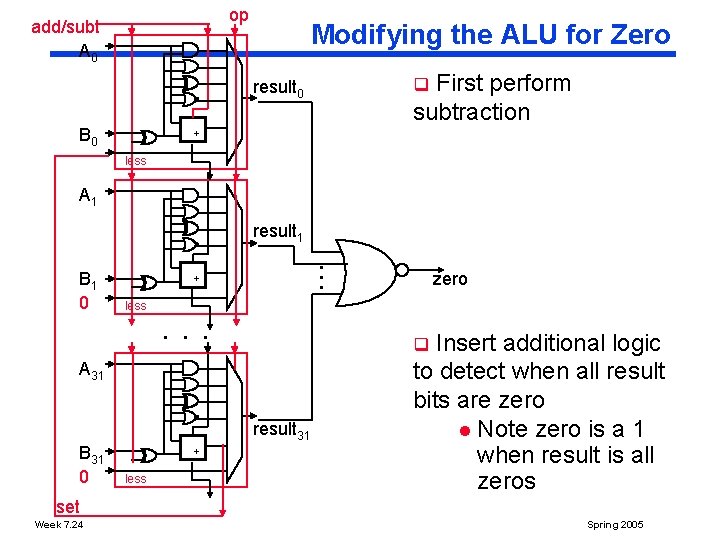

op add/subt A 0 Modifying the ALU for Zero First perform subtraction q result 0 B 0 + less A 1 result 1. . . B 1 0 + less . . . result 31 + less Insert additional logic to detect when all result bits are zero l Note zero is a 1 when result is all zeros q A 31 B 31 0 zero set Week 7. 24 Spring 2005

Review: Overflow Detection q Overflow: the result is too large to represent in the number of bits allocated q Overflow occurs when q l adding two positives yields a negative l or, adding two negatives gives a positive l or, subtract a negative from a positive gives a negative l or, subtract a positive from a negative gives a positive On your own: Prove you can detect overflow by: l 0 + Week 7. 25 Carry into MSB xor Carry out of MSB 1 1 0 1 1 1 7 0 0 1 1 3 1 0 – 6 + 0 1 1 0 0 – 4 1 0 1 1 – 5 0 1 1 1 7 Spring 2005

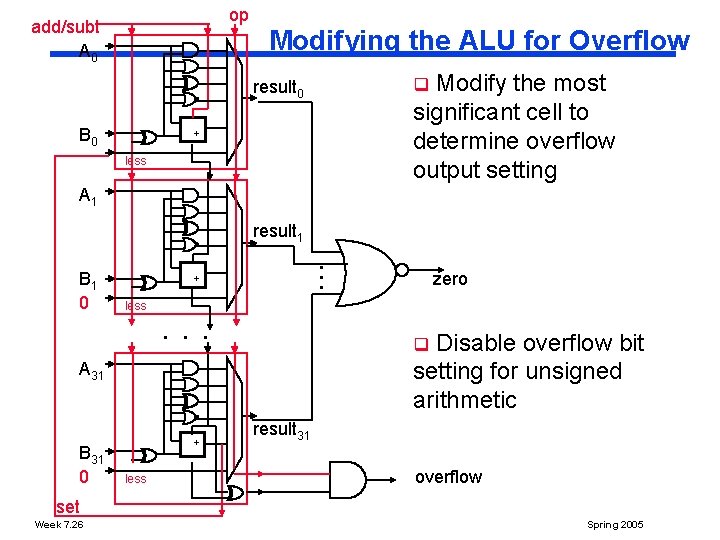

op add/subt A 0 Modifying the ALU for Overflow Modify the most significant cell to determine overflow output setting q result 0 B 0 + less A 1 result 1. . . B 1 0 + less . . . Disable overflow bit setting for unsigned arithmetic q A 31 B 31 0 zero + less result 31 overflow set Week 7. 26 Spring 2005

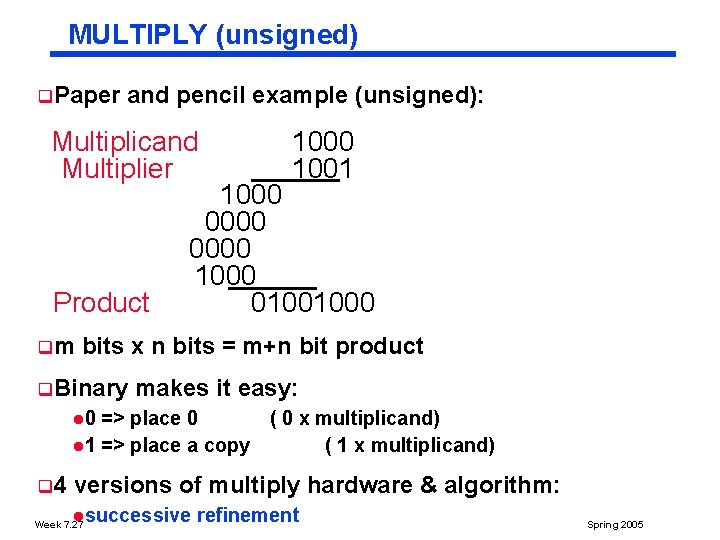

MULTIPLY (unsigned) q. Paper and pencil example (unsigned): Multiplicand Multiplier Product qm 1000 1001 1000 0000 1000 01001000 bits x n bits = m+n bit product q. Binary makes it easy: l 0 => place 0 ( 0 x multiplicand) l 1 => place a copy ( 1 x multiplicand) q 4 versions of multiply hardware & algorithm: lsuccessive Week 7. 27 refinement Spring 2005

Unsigned Combinational Multiplier 0 A 3 A 3 P 7 q. Stage P 6 A 2 A 1 P 5 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 4 B 3 P 2 P 1 P 0 i accumulates A * 2 i if Bi == 1 q. Q: How much hardware for 32 bit multiplier? Critical path? Week 7. 28 Spring 2005

How does it work? 0 0 0 A 3 A 3 P 7 qat P 6 A 2 P 5 A 2 A 1 P 4 0 A 3 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 3 B 0 B 3 P 2 P 1 P 0 each stage shift A left ( x 2) quse next bit of B to determine whether to add in shifted multiplicand qaccumulate Week 7. 29 2 n bit partial product at each stage Spring 2005

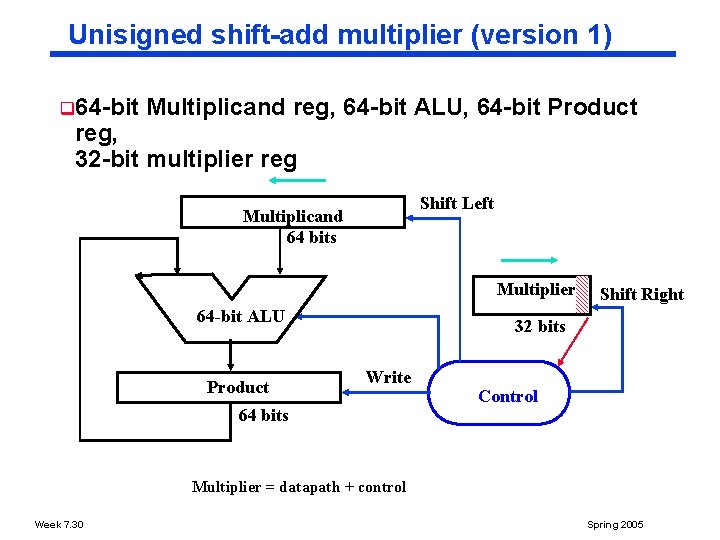

Unisigned shift add multiplier (version 1) q 64 bit Multiplicand reg, 64 bit ALU, 64 bit Product reg, 32 bit multiplier reg Shift Left Multiplicand 64 bits Multiplier 64 -bit ALU Product Shift Right 32 bits Write 64 bits Control Multiplier = datapath + control Week 7. 30 Spring 2005

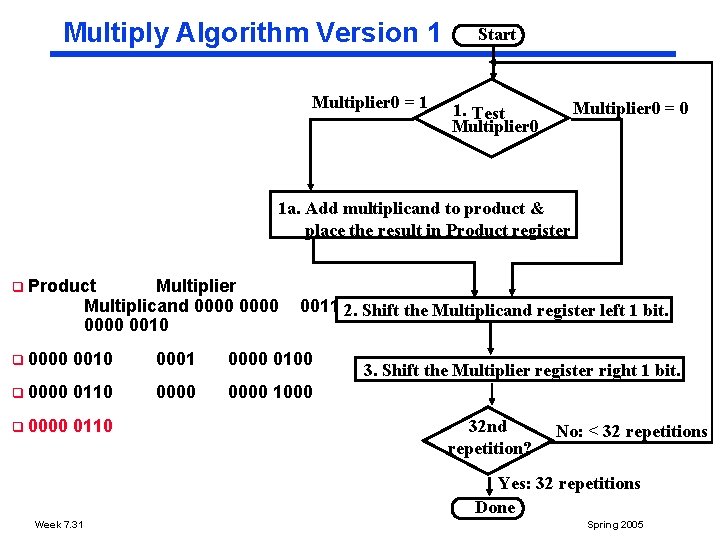

Multiply Algorithm Version 1 Multiplier 0 = 1 Start Multiplier 0 = 0 1. Test Multiplier 0 1 a. Add multiplicand to product & place the result in Product register q Product Multiplier Multiplicand 0000 0011 2. Shift the Multiplicand register left 1 bit. q 0000 0010 0001 0000 0100 q 0000 0110 0000 1000 q 0000 0110 3. Shift the Multiplier register right 1 bit. 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done Week 7. 31 Spring 2005

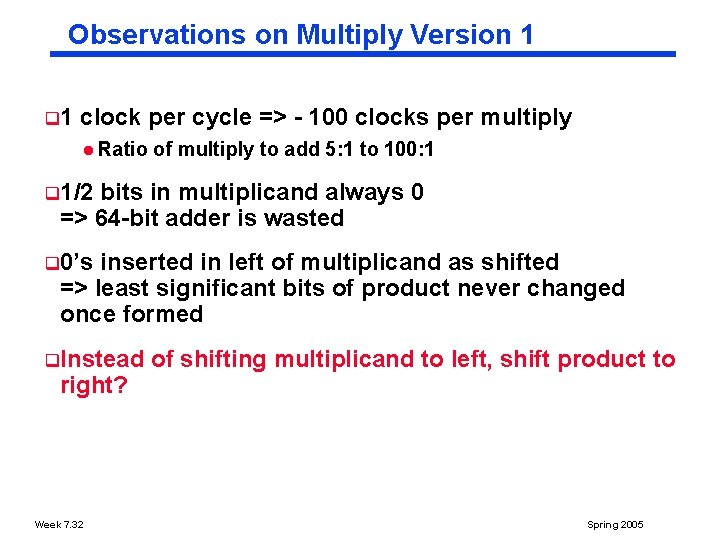

Observations on Multiply Version 1 q 1 clock per cycle => 100 clocks per multiply l Ratio of multiply to add 5: 1 to 100: 1 q 1/2 bits in multiplicand always 0 => 64 bit adder is wasted q 0’s inserted in left of multiplicand as shifted => least significant bits of product never changed once formed q. Instead right? Week 7. 32 of shifting multiplicand to left, shift product to Spring 2005

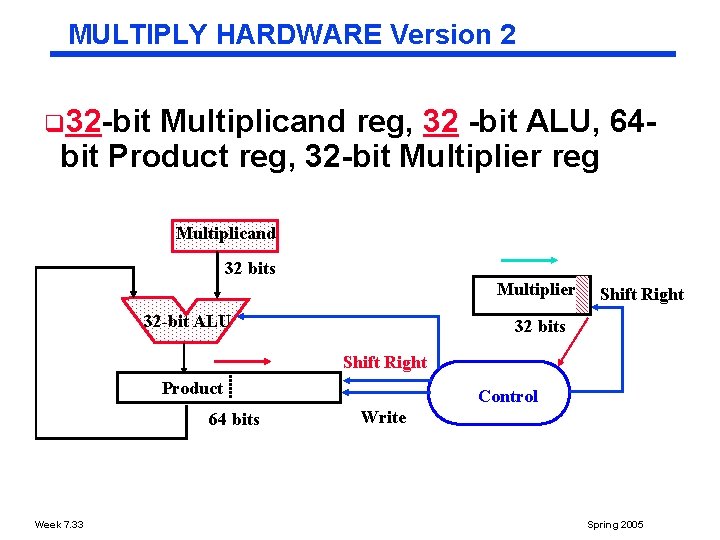

MULTIPLY HARDWARE Version 2 q 32 bit Multiplicand reg, 32 bit ALU, 64 bit Product reg, 32 bit Multiplier reg Multiplicand 32 bits Multiplier 32 -bit ALU Shift Right 32 bits Shift Right Product 64 bits Week 7. 33 Control Write Spring 2005

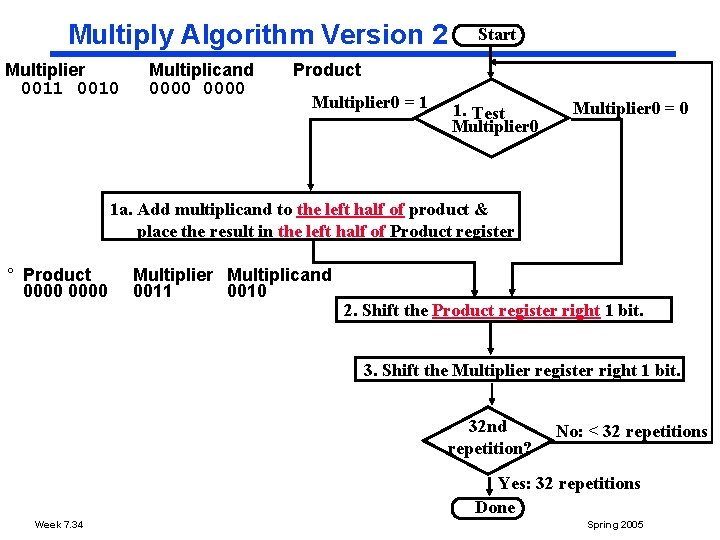

Multiply Algorithm Version 2 Multiplier 0011 0010 Multiplicand 0000 Start Product Multiplier 0 = 1 1. Test Multiplier 0 = 0 1 a. Add multiplicand to the left half of product & place the result in the left half of Product register ° Product 0000 Multiplier Multiplicand 0011 0010 2. Shift the Product register right 1 bit. 3. Shift the Multiplier register right 1 bit. 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done Week 7. 34 Spring 2005

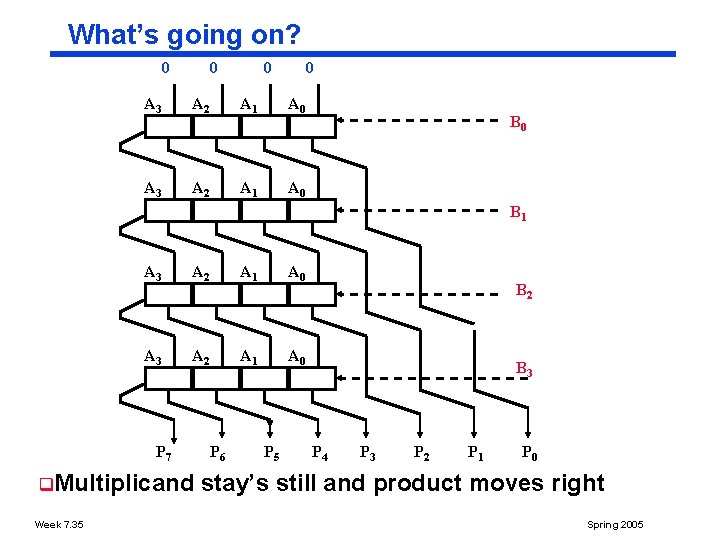

What’s going on? 0 0 A 3 A 2 A 1 A 0 B 0 B 1 A 3 A 2 A 1 A 0 P 7 q. Multiplicand Week 7. 35 P 6 P 5 B 2 B 3 P 4 P 3 P 2 P 1 P 0 stay’s still and product moves right Spring 2005

Observations on Multiply Version 2 q. Product register wastes space that exactly matches size of multiplier => combine Multiplier register and Product register Week 7. 37 Spring 2005

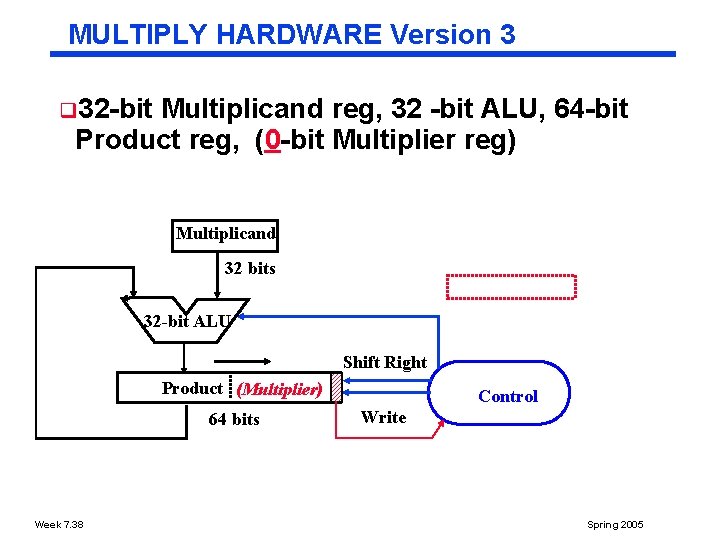

MULTIPLY HARDWARE Version 3 q 32 bit Multiplicand reg, 32 bit ALU, 64 bit Product reg, (0 bit Multiplier reg) Multiplicand 32 bits 32 -bit ALU Shift Right Product (Multiplier) 64 bits Week 7. 38 Control Write Spring 2005

Multiply Algorithm Version 3 Multiplicand 0010 Product 0000 0011 Product 0 = 1 Start 1. Test Product 0 = 0 1 a. Add multiplicand to the left half of product & place the result in the left half of Product register 2. Shift the Product register right 1 bit. 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done Week 7. 39 Spring 2005

Observations on Multiply Version 3 q 2 steps per bit because Multiplier & Product combined q MIPS registers Hi and Lo are left and right half of Product q Gives q How us MIPS instruction Mult. U can you make it faster? q What about signed multiplication? l easiest solution is to make both positive & remember whether to complement product when done (leave out the sign bit, run for 31 steps) l apply definition of 2’s complement - l Booth’s Algorithm is elegant way to multiply signed numbers using same hardware as before and save cycles - Week 7. 40 need to sign extend partial products and subtract at the end can handle multiple bits at a time Spring 2005

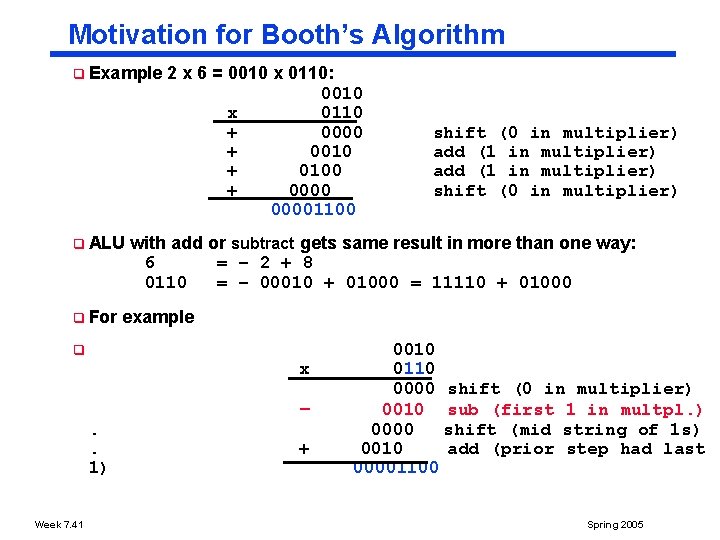

Motivation for Booth’s Algorithm q Example q ALU q For 2 x 6 = 0010 x 0110: 0010 x 0110 + 0000 + 0010 + 0100 + 00001100 with add or subtract gets same result in more than one way: 6 = – 2 + 8 0110 = – 00010 + 01000 = 11110 + 01000 example q x. . 1) Week 7. 41 shift (0 in multiplier) add (1 in multiplier) shift (0 in multiplier) – + 0010 0110 0000 shift (0 in multiplier) 0010 sub (first 1 in multpl. ) 0000 shift (mid string of 1 s) 0010 add (prior step had last 00001100 Spring 2005

Booth’s Algorithm Current Bit to the Right Explanation Example sub 1 0 Begins run of 1 s 0001111000 1 1 Middle of run of 1 s 0 1 End of run of 1 s 0001111000 0 0 Middle of run of 0 s 0001111000 Op none add 0001111000 none Originally for Speed (when shift was faster than add) q Replace a string of 1 s in multiplier with an initial subtract when we first see a one and then later add for the bit after the last one – 1 + 10000 01111 Week 7. 42 Spring 2005

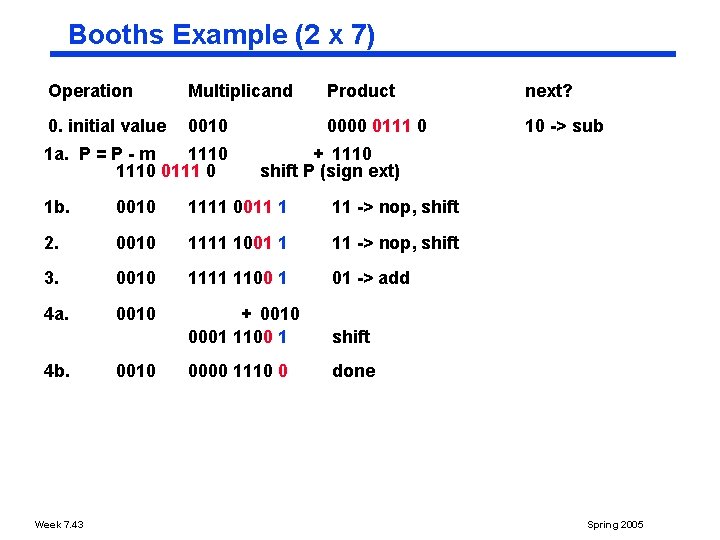

Booths Example (2 x 7) Operation Multiplicand Product next? 0. initial value 0010 0000 0111 0 10 > sub 1 a. P = P m 1110 0111 0 + 1110 shift P (sign ext) 1 b. 0010 1111 0011 1 11 > nop, shift 2. 0010 1111 1001 1 11 > nop, shift 3. 0010 1111 1100 1 01 > add 4 a. 0010 + 0010 0001 1100 1 shift 0000 1110 0 done 4 b. Week 7. 43 0010 Spring 2005

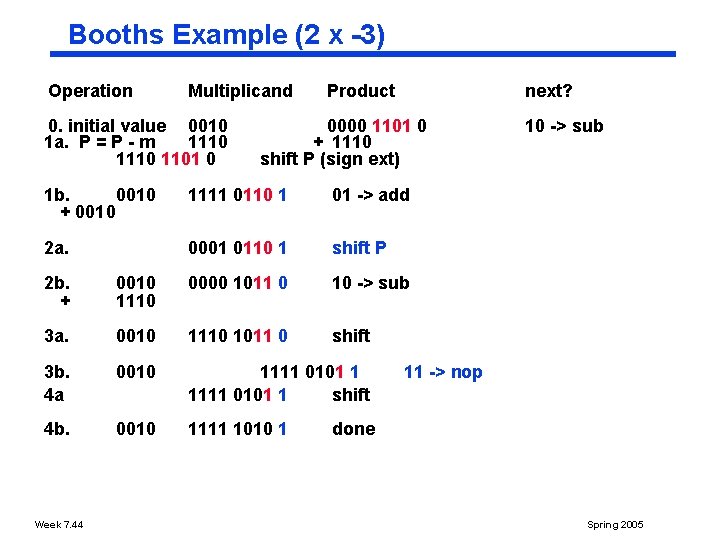

Booths Example (2 x 3) Operation Multiplicand 0. initial value 0010 1 a. P = P m 1110 1101 0 Product next? 0000 1101 0 + 1110 shift P (sign ext) 1 b. 0010 + 0010 1111 0110 1 01 > add 2 a. 0001 0110 1 shift P 2 b. + 0010 1110 0000 1011 0 10 > sub 3 a. 0010 1110 1011 0 shift 3 b. 4 a 0010 1111 0101 1 shift 4 b. 0010 1111 1010 1 Week 7. 44 10 > sub 11 > nop done Spring 2005

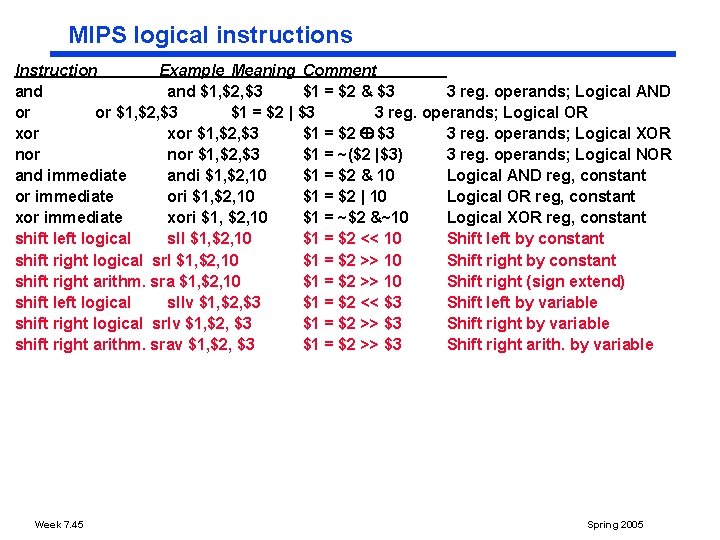

MIPS logical instructions Instruction Example Meaning Comment and $1, $2, $3 $1 = $2 & $3 3 reg. operands; Logical AND or or $1, $2, $3 $1 = $2 | $3 3 reg. operands; Logical OR xor $1, $2, $3 $1 = $2 Å $3 3 reg. operands; Logical XOR nor $1, $2, $3 $1 = ~($2 |$3) 3 reg. operands; Logical NOR and immediate andi $1, $2, 10 $1 = $2 & 10 Logical AND reg, constant or immediate ori $1, $2, 10 $1 = $2 | 10 Logical OR reg, constant xor immediate xori $1, $2, 10 $1 = ~$2 &~10 Logical XOR reg, constant shift left logical sll $1, $2, 10 $1 = $2 << 10 Shift left by constant shift right logical srl $1, $2, 10 $1 = $2 >> 10 Shift right by constant shift right arithm. sra $1, $2, 10 $1 = $2 >> 10 Shift right (sign extend) shift left logical sllv $1, $2, $3 $1 = $2 << $3 Shift left by variable shift right logical srlv $1, $2, $3 $1 = $2 >> $3 Shift right by variable shift right arithm. srav $1, $2, $3 $1 = $2 >> $3 Shift right arith. by variable Week 7. 45 Spring 2005

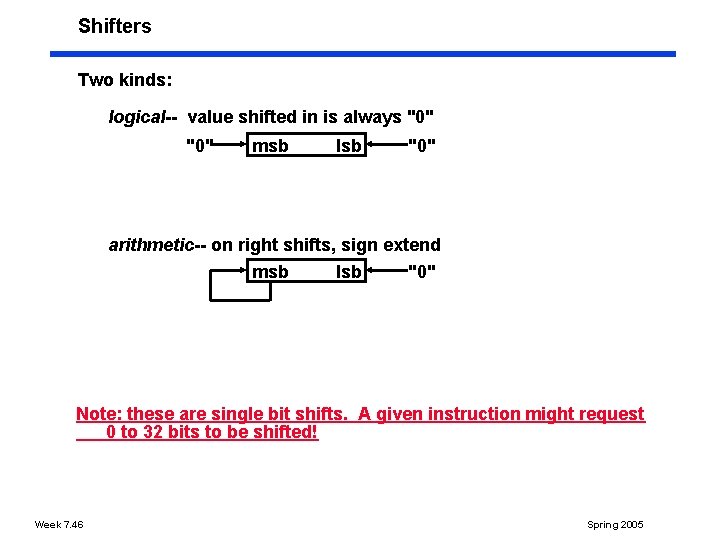

Shifters Two kinds: logical value shifted in is always "0" msb lsb "0" arithmetic on right shifts, sign extend msb lsb "0" Note: these are single bit shifts. A given instruction might request 0 to 32 bits to be shifted! Week 7. 46 Spring 2005

Combinational Shifter from MUXes Basic Building Block sel A B 1 0 D 8 -bit right shifter A 7 q How A 4 A 3 A 2 A 1 S 2 S 1 S 0 A 0 0 1 0 1 0 1 0 1 0 1 0 1 0 R 6 R 5 R 4 R 3 R 2 R 1 R 0 comes in the MSBs? many levels for 32 bit shifter? q What Week 7. 47 A 5 1 R 7 q What A 6 if we use 4 1 Muxes ? Spring 2005

General Shift Right Scheme using 16 bit example S 0 (0, 1) S 1 (0, 2) S 2 (0, 4) S 3 (0, 8) If added Right to left connections could support Rotate (not in MIPS but found in ISAs) Week 7. 48 Spring 2005

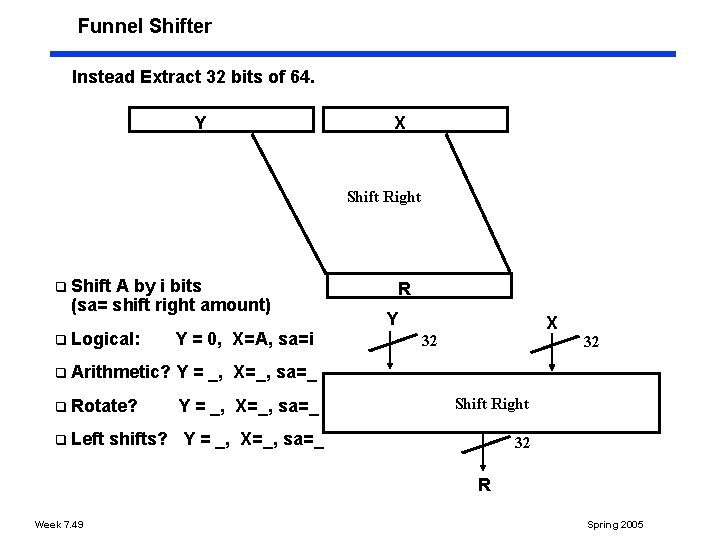

Funnel Shifter Instead Extract 32 bits of 64. Y X Shift Right q Shift A by i bits (sa= shift right amount) q Logical: Y = 0, X=A, sa=i q Arithmetic? Y = _, X=_, sa=_ q Rotate? Y = _, X=_, sa=_ q Left R Y X 32 32 Shift Right shifts? Y = _, X=_, sa=_ 32 R Week 7. 49 Spring 2005

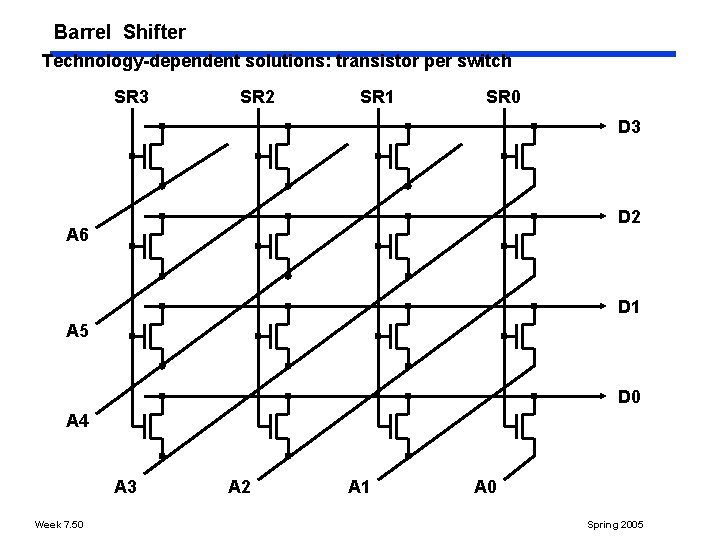

Barrel Shifter Technology dependent solutions: transistor per switch SR 3 SR 2 SR 1 SR 0 D 3 D 2 A 6 D 1 A 5 D 0 A 4 A 3 Week 7. 50 A 2 A 1 A 0 Spring 2005

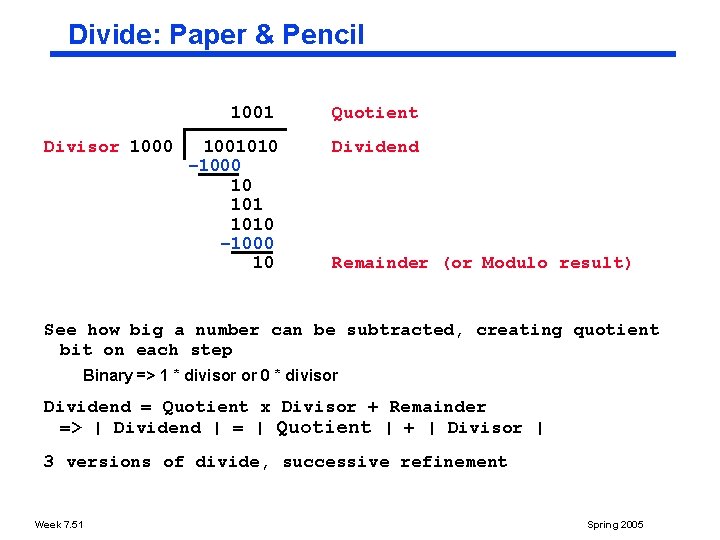

Divide: Paper & Pencil Divisor 1000 1001 Quotient 1001010 – 1000 10 Dividend Remainder (or Modulo result) See how big a number can be subtracted, creating quotient bit on each step Binary => 1 * divisor or 0 * divisor Dividend = Quotient x Divisor + Remainder => | Dividend | = | Quotient | + | Divisor | 3 versions of divide, successive refinement Week 7. 51 Spring 2005

DIVIDE HARDWARE Version 1 q 64 bit Divisor reg, 64 bit ALU, 64 bit Remainder reg, 32 bit Quotient reg Shift Right Divisor 64 bits Quotient 64 -bit ALU Remainder 64 bits Week 7. 52 Shift Left 32 bits Write Control Spring 2005

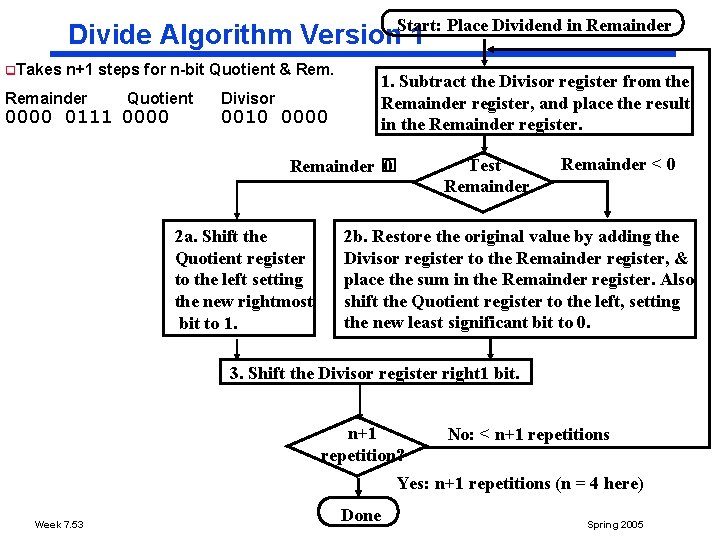

Divide Algorithm Version. Start: 1 Place Dividend in Remainder q. Takes n+1 steps for n bit Quotient & Remainder Quotient 0000 0111 0000 Divisor 0010 0000 1. Subtract the Divisor register from the Remainder register, and place the result in the Remainder register. Remainder � 0 2 a. Shift the Quotient register to the left setting the new rightmost bit to 1. Test Remainder < 0 2 b. Restore the original value by adding the Divisor register to the Remainder register, & place the sum in the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0. 3. Shift the Divisor register right 1 bit. n+1 repetition? No: < n+1 repetitions Yes: n+1 repetitions (n = 4 here) Week 7. 53 Done Spring 2005

Observations on Divide Version 1 q 1/2 bits in divisor always 0 => 1/2 of 64 bit adder is wasted => 1/2 of divisor is wasted q. Instead of shifting divisor to right, shift remainder to left? q 1 st step cannot produce a 1 in quotient bit (otherwise too big) => switch order to shift first and then subtract, can save 1 iteration Week 7. 54 Spring 2005

DIVIDE HARDWARE Version 2 q 32 bit Divisor reg, 32 bit ALU, 64 bit Remainder reg, 32 bit Quotient reg Divisor 32 bits Quotient 32 -bit ALU Shift Left 32 bits Shift Left Remainder 64 bits Week 7. 55 Control Write Spring 2005

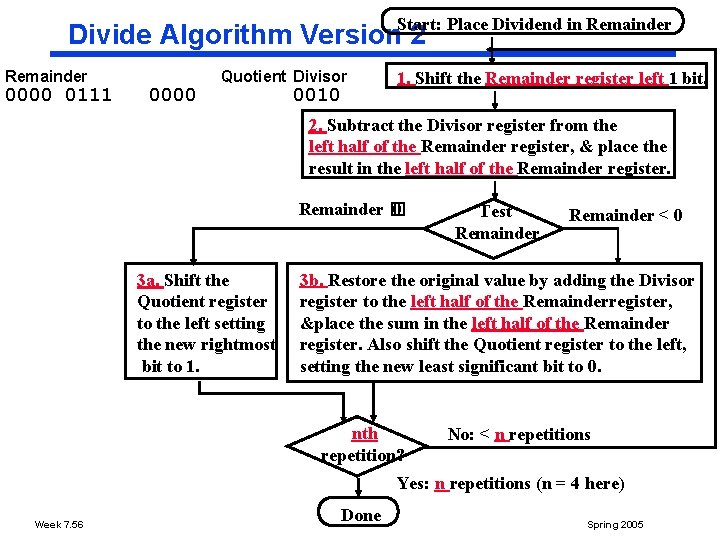

Start: Place Dividend in Remainder Divide Algorithm Version 2 Remainder 0000 0111 0000 Quotient Divisor 0010 1. Shift the Remainder register left 1 bit. 2. Subtract the Divisor register from the left half of the Remainder register, & place the result in the left half of the Remainder register. Remainder � 0 3 a. Shift the Quotient register to the left setting the new rightmost bit to 1. Test Remainder < 0 3 b. Restore the original value by adding the Divisor register to the left half of the Remainderregister, &place the sum in the left half of the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0. nth repetition? No: < n repetitions Yes: n repetitions (n = 4 here) Week 7. 56 Done Spring 2005

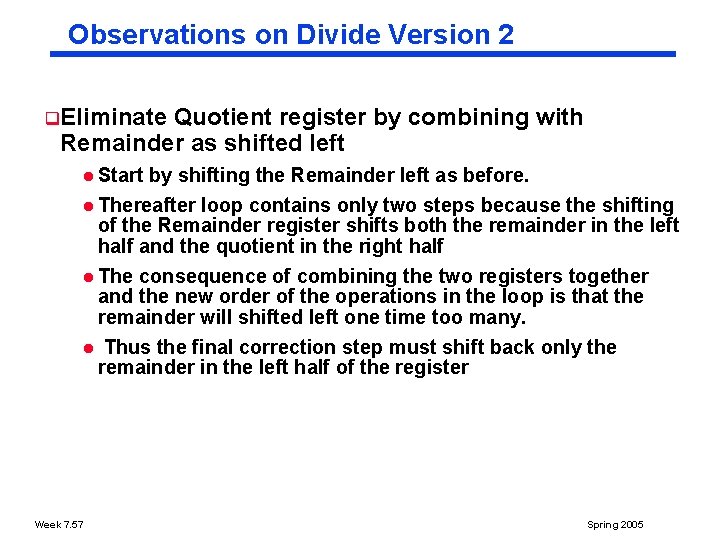

Observations on Divide Version 2 q. Eliminate Quotient register by combining with Remainder as shifted left l Start by shifting the Remainder left as before. l Thereafter loop contains only two steps because the shifting of the Remainder register shifts both the remainder in the left half and the quotient in the right half l The consequence of combining the two registers together and the new order of the operations in the loop is that the remainder will shifted left one time too many. l Week 7. 57 Thus the final correction step must shift back only the remainder in the left half of the register Spring 2005

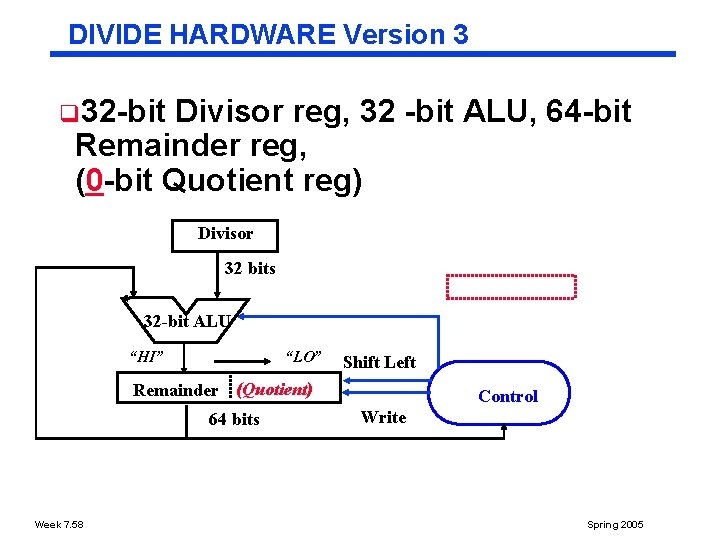

DIVIDE HARDWARE Version 3 q 32 bit Divisor reg, 32 bit ALU, 64 bit Remainder reg, (0 bit Quotient reg) Divisor 32 bits 32 -bit ALU “HI” “LO” Shift Left Remainder (Quotient) 64 bits Week 7. 58 Control Write Spring 2005

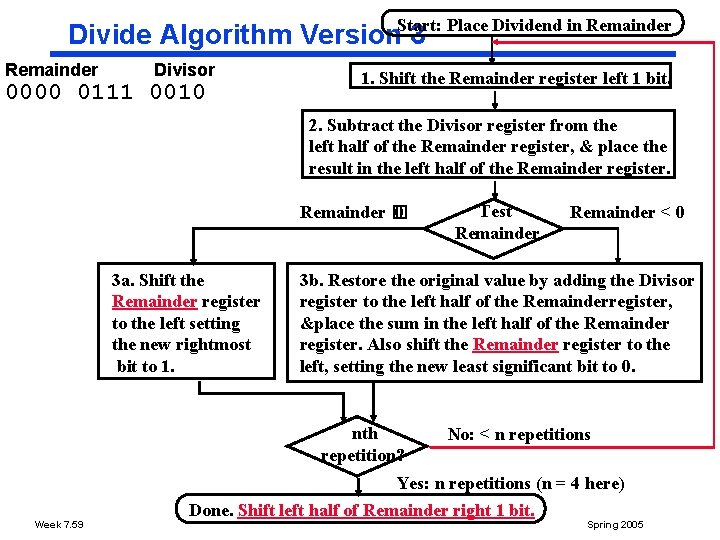

Divide Algorithm Version. Start: 3 Place Dividend in Remainder Divisor 0000 0111 0010 1. Shift the Remainder register left 1 bit. 2. Subtract the Divisor register from the left half of the Remainder register, & place the result in the left half of the Remainder register. Remainder � 0 3 a. Shift the Remainder register to the left setting the new rightmost bit to 1. Test Remainder < 0 3 b. Restore the original value by adding the Divisor register to the left half of the Remainderregister, &place the sum in the left half of the Remainder register. Also shift the Remainder register to the left, setting the new least significant bit to 0. nth repetition? No: < n repetitions Yes: n repetitions (n = 4 here) Week 7. 59 Done. Shift left half of Remainder right 1 bit. Spring 2005

Observations on Divide Version 3 q Same Hardware as Multiply: just need ALU to add or subtract, and 63 bit register to shift left or shift right q Hi and Lo registers in MIPS combine to act as 64 bit register for multiply and divide q Signed Divides: Simplest is to remember signs, make positive, and complement quotient and remainder if necessary l Note: Dividend and Remainder must have same sign l Note: Quotient negated if Divisor sign & Dividend sign disagree e. g. , – 7 ÷ 2 = – 3, remainder = – 1 q Possible for quotient to be too large: if divide 64 bit interger by 1, quotient is 64 bits (“called saturation”) Week 7. 60 Spring 2005

- Slides: 56