14 332 331 Computer Architecture and Assembly Language

14: 332: 331 Computer Architecture and Assembly Language Spring 2006 Week 11: Microprogramming [Adapted from Dave Patterson’s UCB CS 152 slides and Mary Jane Irwin’s PSU CSE 331 slides] Week 11 Spring 2006

Simplifying Control Design q For an implementation of the full MIPS ISA l l instructions can take from 1 clock cycle to 20 clock cycles resulting in finite state machines with hundreds to thousands of states with even more arcs (state sequences) q Graphical representations become impossibly complex q Instead, represent the set of control signals that are asserted during a state as a low-level control “instruction” to be executed by the datapath microinstructions q Week 11 “Executing” the microinstruction is equivalent to asserting the control signals specified by the microinstruction Spring 2006

Microprogramming q Microinstruction has to specify l l q what control signals should be asserted what microinstruction should be executed next Each microinstruction corresponds to one state in the FSM and is assigned a state number (or “address”) 1. 2. 3. Sequential behavior – increment the state (address) of the current microinstruction to get to the state (address) of the next Jump to the microinstruction that begins execution of the next MIPS instruction (state 0) Branch to a microinstruction based on control unit input using dispatch tables - need one for microinstructions following state 1 need another for microinstructions following state 2 The set of microinstructions that define a MPS assembly language instruction (macroinstruction) is its microroutine Week 11 Spring 2006 q

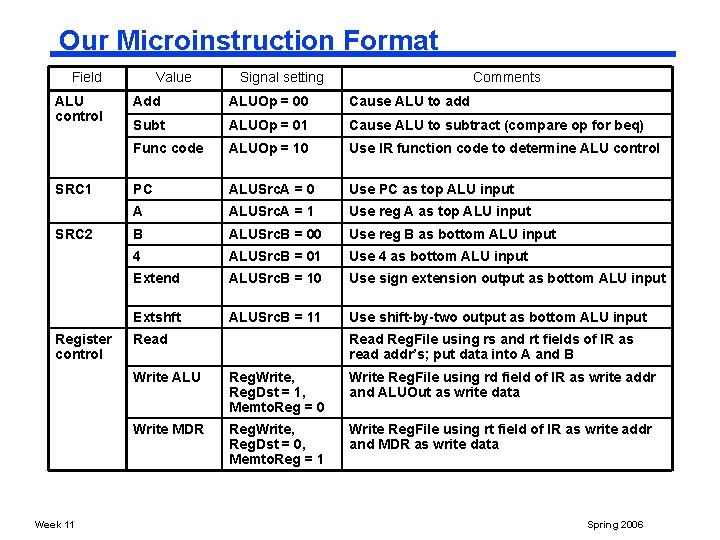

Defining a Microinstruction Format q Format – the fields of the microinstruction and the control signals that are affected by each field l control signals specified by a field usually have functions that are related l format is chosen to simplify the representation and to make it difficult to write inconsistent microinstructions - i. e. , that allow a given control signal be set to two different values q Make each field of the microinstruction responsible for specifying a nonoverlapping set of control signals l l signals that are never asserted simultaneously may share the same field seven fields for our simple machine - ALU control; SRC 1; SRC 2; Register control; Memory; PCWrite control; Sequencing Week 11 Spring 2006

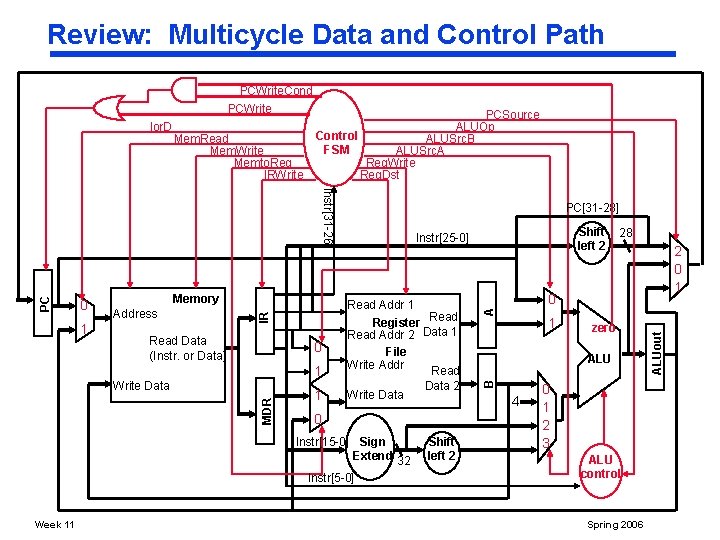

Review: Multicycle Data and Control Path 1 Memory Address Read Data (Instr. or Data) 1 1 Write Data 0 MDR Write Data 2 Shift left 2 28 2 0 1 zero ALU 4 0 Instr[15 -0] Sign Extend 32 Instr[5 -0] Week 11 Shift left 2 Instr[25 -0] Read Addr 1 Register Read Addr 2 Data 1 File Write Addr Read IR PC Instr[31 -26] 0 PC[31 -28] 0 1 2 3 ALU control Spring 2006 ALUout Mem. Read Mem. Write Memto. Reg IRWrite PCSource ALUOp Control ALUSrc. B FSM ALUSrc. A Reg. Write Reg. Dst A Ior. D B PCWrite. Cond PCWrite

Review: Multicycle RTL Summary Step Instr fetch Decode Execute Memory access Writeback Week 11 R-type Mem Ref Branch Jump IR = Memory[PC]; PC = PC + 4; A = Reg[IR[25 -21]]; B = Reg[IR[20 -16]]; ALUOut = PC +(sign-extend(IR[15 -0])<< 2); ALUOut = A op B; ALUOut = A + sign-extend (IR[15 -0]); if (A==B) PC = ALUOut; PC = PC[31 -28] ||(IR[25 -0] << 2); Reg[IR[15 MDR = 11]] = Memory[ALUOut]; ALUOut; or Memory[ALUOut] = B; Reg[IR[20 -16]] = MDR; Spring 2006

Our Microinstruction Format Field ALU control SRC 1 SRC 2 Register control Week 11 Value Signal setting Comments Add ALUOp = 00 Cause ALU to add Subt ALUOp = 01 Cause ALU to subtract (compare op for beq) Func code ALUOp = 10 Use IR function code to determine ALU control PC ALUSrc. A = 0 Use PC as top ALU input A ALUSrc. A = 1 Use reg A as top ALU input B ALUSrc. B = 00 Use reg B as bottom ALU input 4 ALUSrc. B = 01 Use 4 as bottom ALU input Extend ALUSrc. B = 10 Use sign extension output as bottom ALU input Extshft ALUSrc. B = 11 Use shift-by-two output as bottom ALU input Read Reg. File using rs and rt fields of IR as read addr’s; put data into A and B Write ALU Reg. Write, Reg. Dst = 1, Memto. Reg = 0 Write Reg. File using rd field of IR as write addr and ALUOut as write data Write MDR Reg. Write, Reg. Dst = 0, Memto. Reg = 1 Write Reg. File using rt field of IR as write addr and MDR as write data Spring 2006

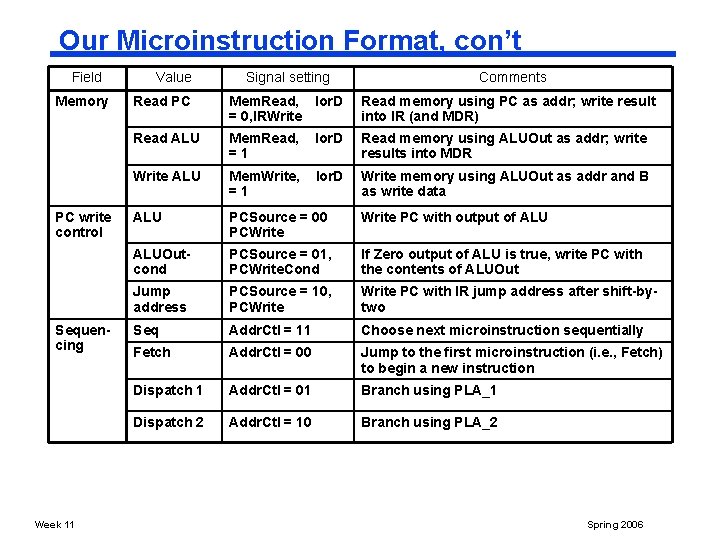

Our Microinstruction Format, con’t Field Memory PC write control Sequencing Week 11 Value Signal setting Comments Read PC Mem. Read, Ior. D = 0, IRWrite Read memory using PC as addr; write result into IR (and MDR) Read ALU Mem. Read, =1 lor. D Read memory using ALUOut as addr; write results into MDR Write ALU Mem. Write, =1 Ior. D Write memory using ALUOut as addr and B as write data ALU PCSource = 00 PCWrite PC with output of ALUOutcond PCSource = 01, PCWrite. Cond If Zero output of ALU is true, write PC with the contents of ALUOut Jump address PCSource = 10, PCWrite PC with IR jump address after shift-bytwo Seq Addr. Ctl = 11 Choose next microinstruction sequentially Fetch Addr. Ctl = 00 Jump to the first microinstruction (i. e. , Fetch) to begin a new instruction Dispatch 1 Addr. Ctl = 01 Branch using PLA_1 Dispatch 2 Addr. Ctl = 10 Branch using PLA_2 Spring 2006

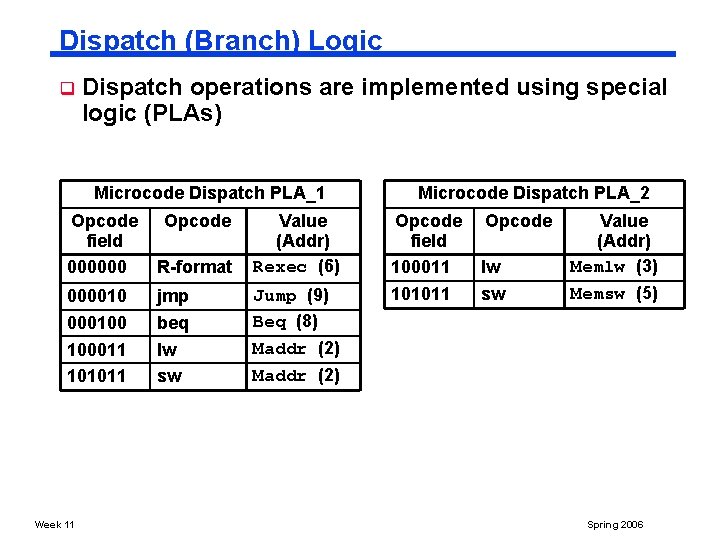

Dispatch (Branch) Logic q Dispatch operations are implemented using special logic (PLAs) Microcode Dispatch PLA_1 Opcode field 000000 R-format Value (Addr) Rexec (6) 0000100 100011 101011 jmp beq lw sw Jump (9) Beq (8) Maddr (2) Week 11 Opcode Microcode Dispatch PLA_2 Opcode field 100011 101011 Opcode lw sw Value (Addr) Memlw (3) Memsw (5) Spring 2006

Creating the Microprogram q Fetch microinstruction Label (Addr) ALU control SRC 1 SRC 2 Fetch (0) Add PC 4 compute PC + 4 Reg control Memory PCWrite control Seq’ing Read PC ALU Seq fetch instr into IR write ALU go to instr 1 output into PC q Label field represents the state (address) of the microinstruction q Fetch microinstruction assigned state (address) 0 Week 11 Spring 2006

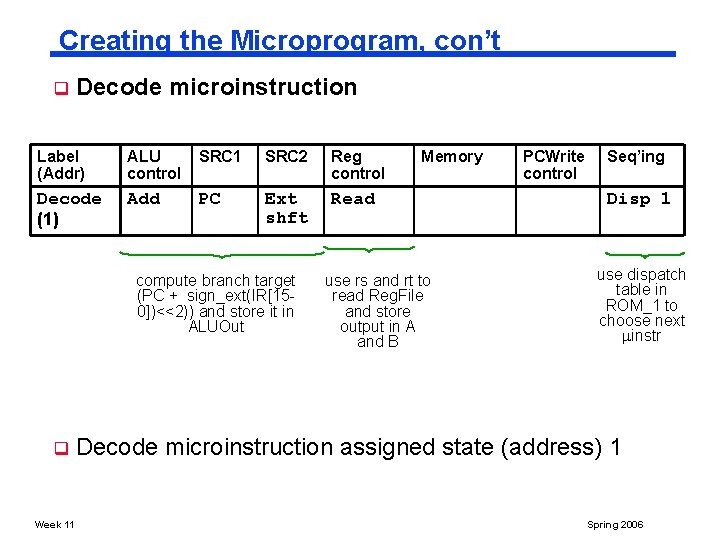

Creating the Microprogram, con’t q Decode microinstruction Label (Addr) ALU control SRC 1 SRC 2 Reg control Decode (1) Add PC Ext shft Read compute branch target (PC + sign_ext(IR[150])<<2)) and store it in ALUOut q Week 11 Memory use rs and rt to read Reg. File and store output in A and B PCWrite control Seq’ing Disp 1 use dispatch table in ROM_1 to choose next instr Decode microinstruction assigned state (address) 1 Spring 2006

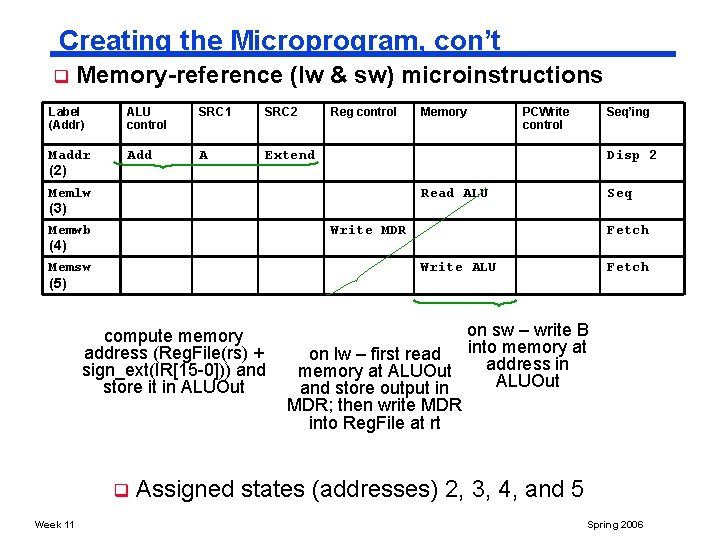

Creating the Microprogram, con’t q Memory-reference (lw & sw) microinstructions Label (Addr) ALU control SRC 1 SRC 2 Maddr (2) Add A Extend Reg control PCWrite control Seq’ing Disp 2 Memlw (3) Read ALU Memwb (4) Seq Write MDR Memsw (5) Fetch Write ALU compute memory address (Reg. File(rs) + sign_ext(IR[15 -0])) and store it in ALUOut q Week 11 Memory Fetch on sw – write B into memory at on lw – first read address in memory at ALUOut and store output in MDR; then write MDR into Reg. File at rt Assigned states (addresses) 2, 3, 4, and 5 Spring 2006

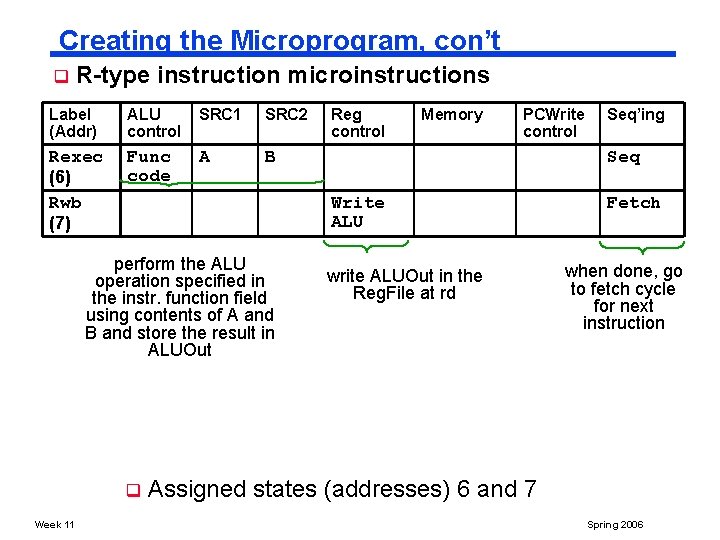

Creating the Microprogram, con’t q R-type instruction microinstructions Label (Addr) ALU control SRC 1 SRC 2 Rexec (6) Rwb (7) Func code A B Memory PCWrite control q Seq’ing Seq Write ALU perform the ALU operation specified in the instr. function field using contents of A and B and store the result in ALUOut Week 11 Reg control write ALUOut in the Reg. File at rd Fetch when done, go to fetch cycle for next instruction Assigned states (addresses) 6 and 7 Spring 2006

Creating the Microprogram, con’t q Branch (beq) and jump microinstructions Label (Addr) ALU control SRC 1 SRC 2 Beq (8) Jump (9) Subt A B for beq – do operand comparison (A - B) to produce Zero output q Week 11 Reg control Memory PCWrite control Seq’ing ALUOutcond Jump address Fetch on beq – load ALUOut into PC if Zero is true Fetch on j – load jump target addr into PC Assigned states (addresses) 8 and 9 Spring 2006

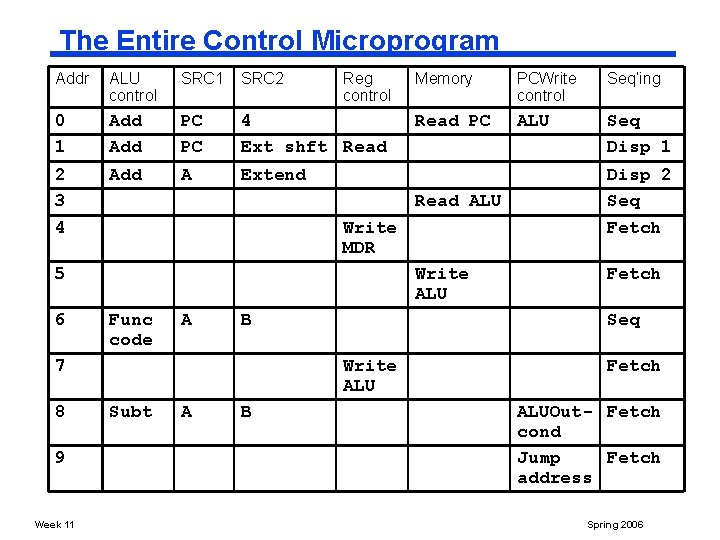

The Entire Control Microprogram Addr ALU control SRC 1 SRC 2 Reg control 0 1 Add PC PC 4 Ext shft Read 2 3 4 Add A Extend 9 Week 11 Seq’ing Read PC ALU Seq Disp 1 Write MDR Write ALU Func code A B 7 8 PCWrite control Read ALU 5 6 Memory A B Fetch Seq Write ALU Subt Disp 2 Seq Fetch ALUOut- Fetch cond Jump Fetch address Spring 2006

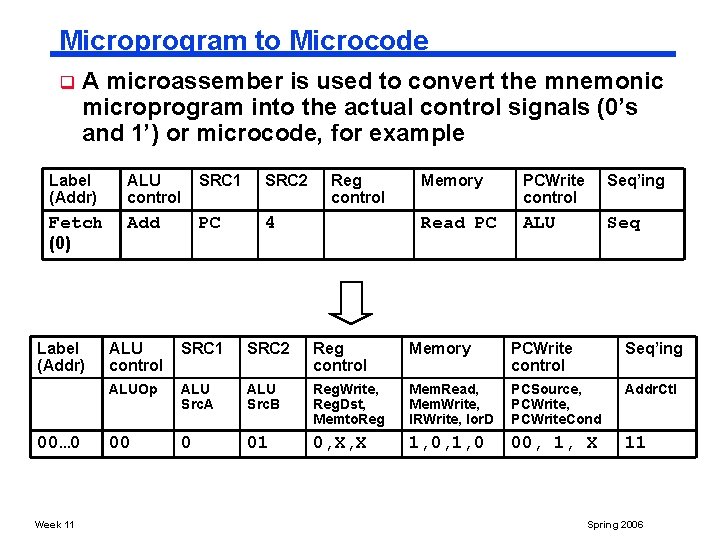

Microprogram to Microcode q A microassember is used to convert the mnemonic microprogram into the actual control signals (0’s and 1’) or microcode, for example Label (Addr) ALU control SRC 1 SRC 2 Fetch (0) Add PC 4 ALU control SRC 1 SRC 2 Reg control Memory PCWrite control Seq’ing ALUOp ALU Src. A ALU Src. B Reg. Write, Reg. Dst, Memto. Reg Mem. Read, Mem. Write, IRWrite, Ior. D PCSource, PCWrite. Cond Addr. Ctl 00 0 01 0, X, X 1, 0, 1, 0 00, 1, X 11 Label (Addr) 00… 0 Week 11 Reg control Memory PCWrite control Seq’ing Read PC ALU Seq Spring 2006

Control PLA 1 Adder Outputs Microcode Implementation PCWrite. Cond Ior. D Mem. Read Mem. Write IRWrite Memto. Reg PCSource ALUOp ALUSource. B ALUSource. A Reg. Write Reg. Dst Addr. Ctl Microprogram Counter System clock Week 11 Op 4 Op 3 Op 2 Op 1 Op 0 Op 5 Addr select logic Inst[31 -26] sequencing control Spring 2006

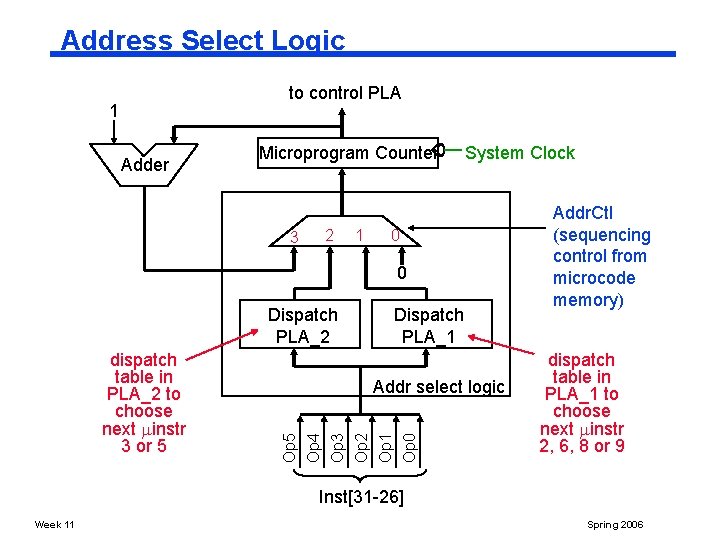

Address Select Logic to control PLA 1 Adder Microprogram Counter 3 2 1 System Clock 0 0 Dispatch PLA_2 Addr select logic Op 5 Op 4 Op 3 Op 2 Op 1 Op 0 dispatch table in PLA_2 to choose next instr 3 or 5 Dispatch PLA_1 Addr. Ctl (sequencing control from microcode memory) dispatch table in PLA_1 to choose next instr 2, 6, 8 or 9 Inst[31 -26] Week 11 Spring 2006

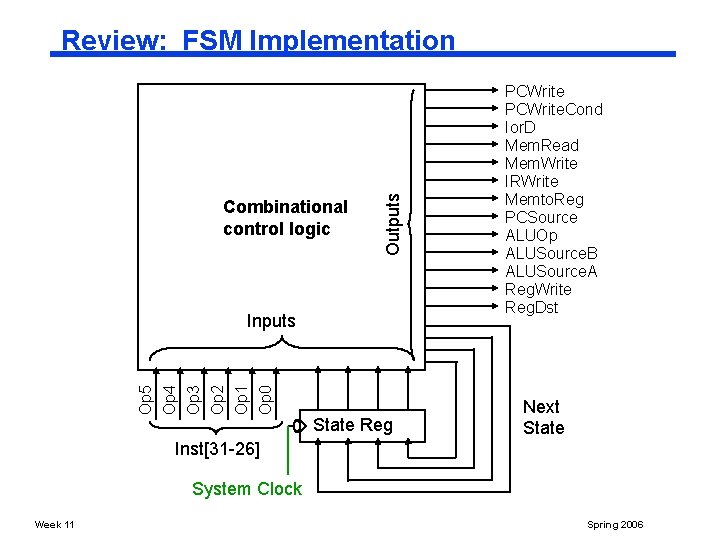

Combinational control logic Outputs Review: FSM Implementation Op 5 Op 4 Op 3 Op 2 Op 1 Op 0 Inputs State Reg PCWrite. Cond Ior. D Mem. Read Mem. Write IRWrite Memto. Reg PCSource ALUOp ALUSource. B ALUSource. A Reg. Write Reg. Dst Next State Inst[31 -26] System Clock Week 11 Spring 2006

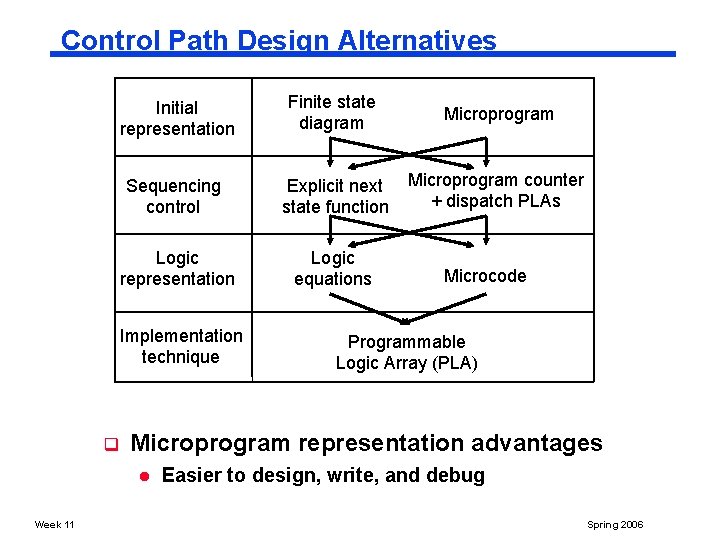

Control Path Design Alternatives Initial representation Finite state diagram Microprogram Sequencing control Explicit next state function Microprogram counter + dispatch PLAs Logic representation Logic equations Implementation technique q Programmable Logic Array (PLA) Microprogram representation advantages l Week 11 Microcode Easier to design, write, and debug Spring 2006

- Slides: 20