VHDL STATUS of CENTROID FINDER ALGORITHM Presentation to

- Slides: 12

VHDL STATUS of CENTROID FINDER ALGORITHM Presentation to DØ STT Meeting @ Stony Brook by Reginald J. Perry, Ph. D. Professor and Chairman Department of Electrical and Computer Engineering (ECE) FAMU-FSU College of Engineering Florida A&M University Florida State University 1/28/2000

Background and Design Objective n n n Contacted in early December 1999 by Dr. Wahl. Recruited two (2) new graduate students to work on project – Shweta Lolage – full-time GRA. – Kishma Meyers – part time – Roberto Brown - part time Discussed initial algorithm with Eric Hazen just before Christmas 1999 – Working documents • Earle, “A State Machine for Input of VTM Data to the Centroid Finder”, 7/20/99 • Earle, “A Flowchart for the Centroid Finder”, 9/3/99 n Initial Design Objective – Complete baseline functional design by today’s meeting • Conservative design, i. e. Ignore timing constraints • No “Bells or Whistles” D 0 STT Meeting at Stony Brook VHDL Status

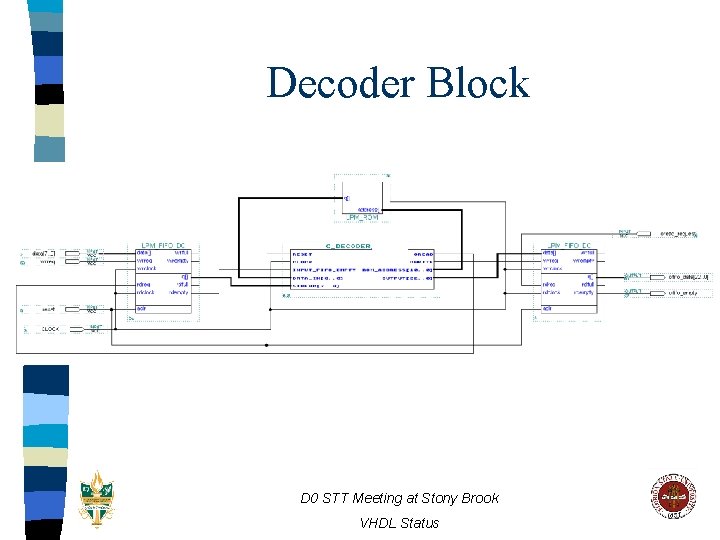

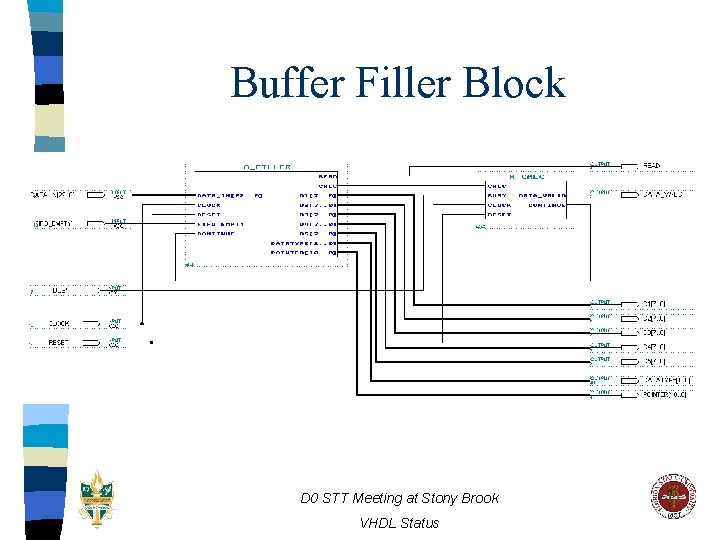

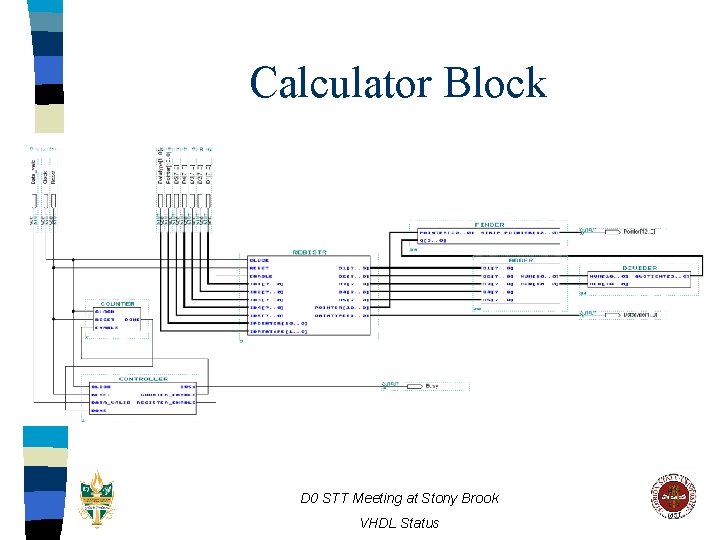

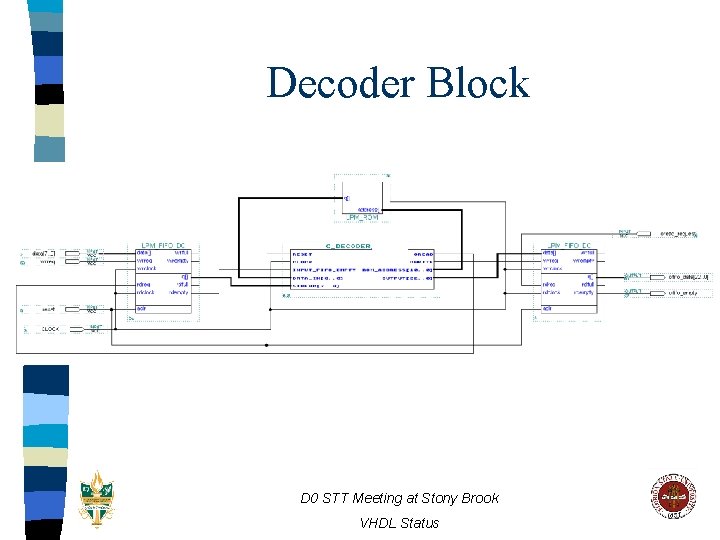

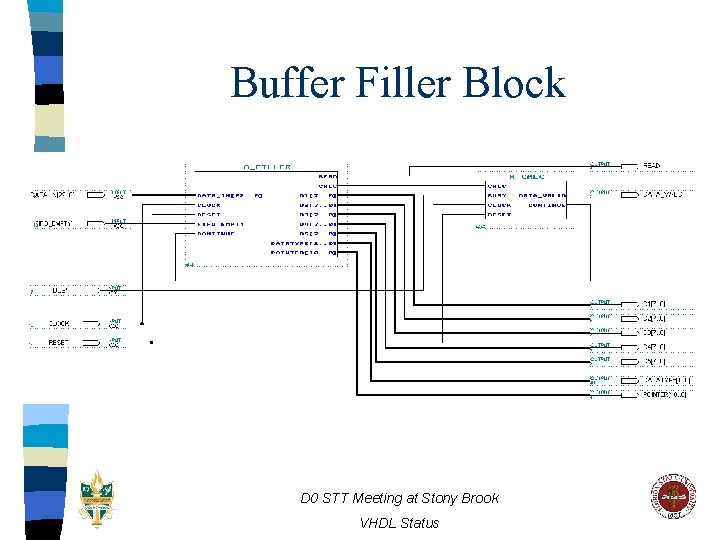

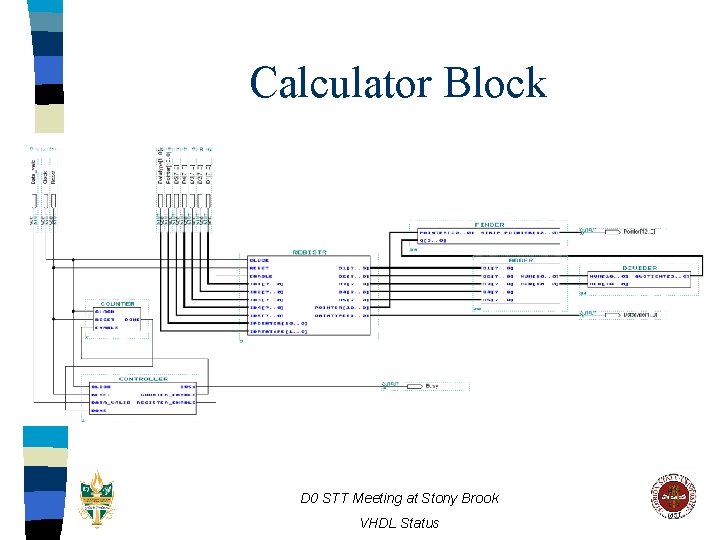

Design Process n n n Altera FPLDs Default Synthesis Settings Partition Design into three parts – 1. Decoder • VTM FIFO • Preprocessor FSM • Centroid Finder FIFO – 2. Buffer Filler • Centroid Finder Algorithm minus “Calculator. ” – 3. Calculator • Computes 13 bit centroid address D 0 STT Meeting at Stony Brook VHDL Status

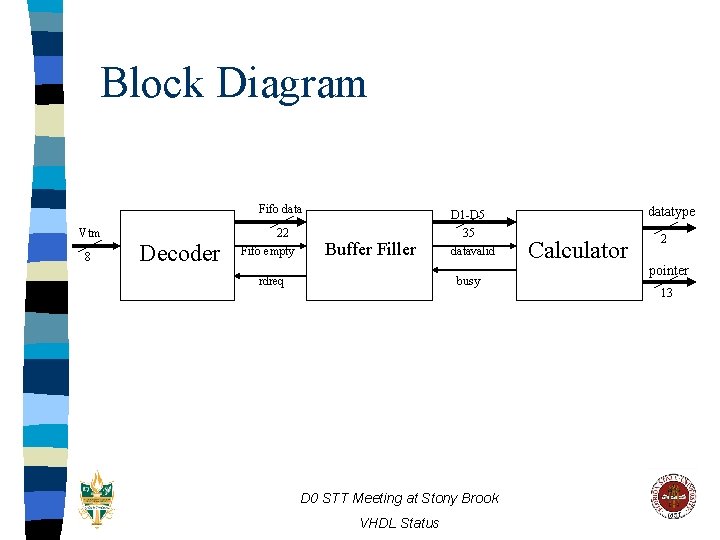

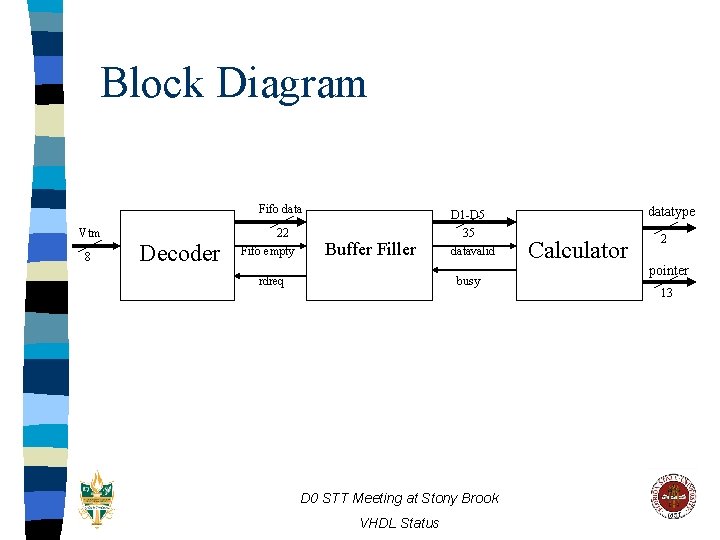

Block Diagram Fifo data Vtm 8 Decoder 22 Fifo empty Buffer Filler rdreq D 1 -D 5 35 datavalid busy D 0 STT Meeting at Stony Brook VHDL Status datatype Calculator 2 pointer 13

Decoder Block D 0 STT Meeting at Stony Brook VHDL Status

Buffer Filler Block D 0 STT Meeting at Stony Brook VHDL Status

Calculator Block D 0 STT Meeting at Stony Brook VHDL Status

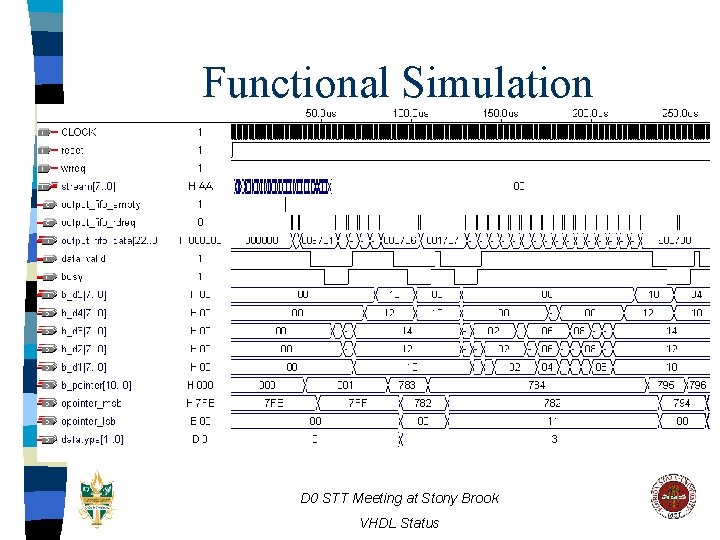

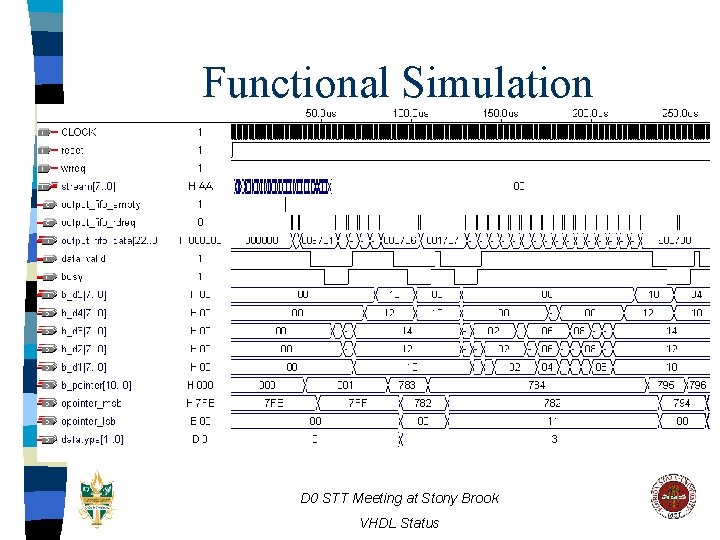

Functional Simulation Assumptions • • 1 MHz Clock Single Chip No Bad Channels No Skipped Channels D 0 STT Meeting at Stony Brook VHDL Status

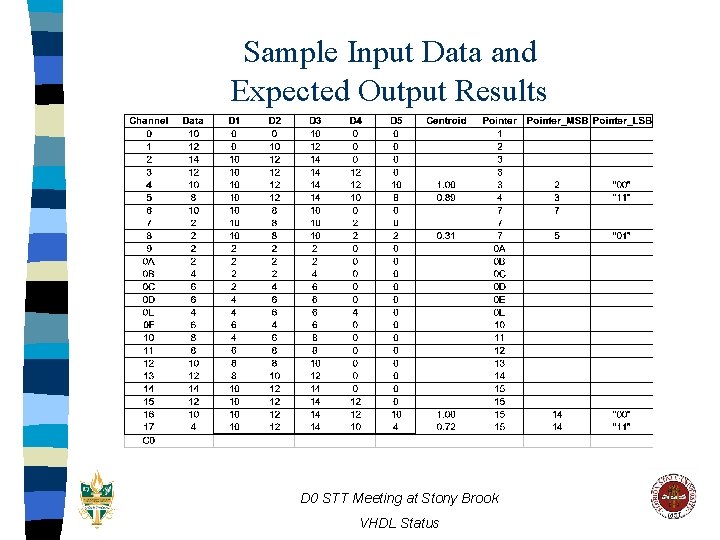

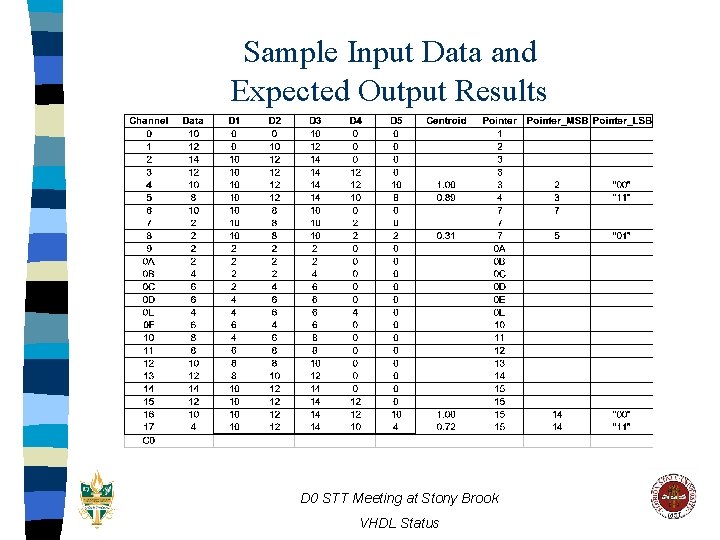

Sample Input Data and Expected Output Results D 0 STT Meeting at Stony Brook VHDL Status

Functional Simulation D 0 STT Meeting at Stony Brook VHDL Status

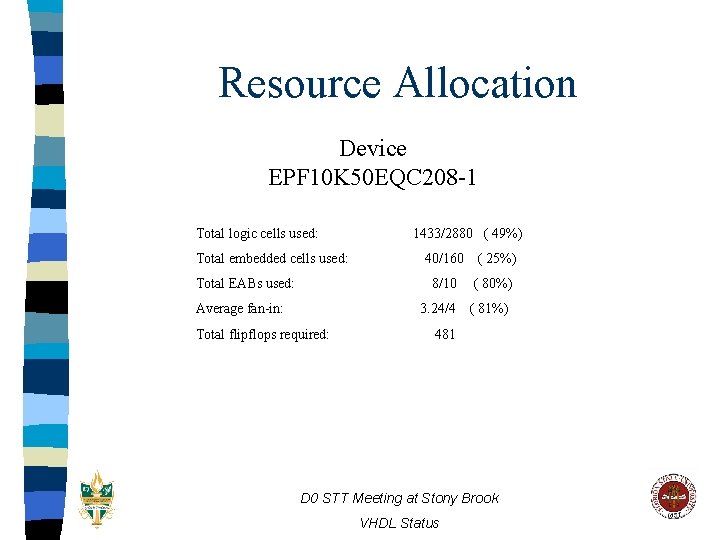

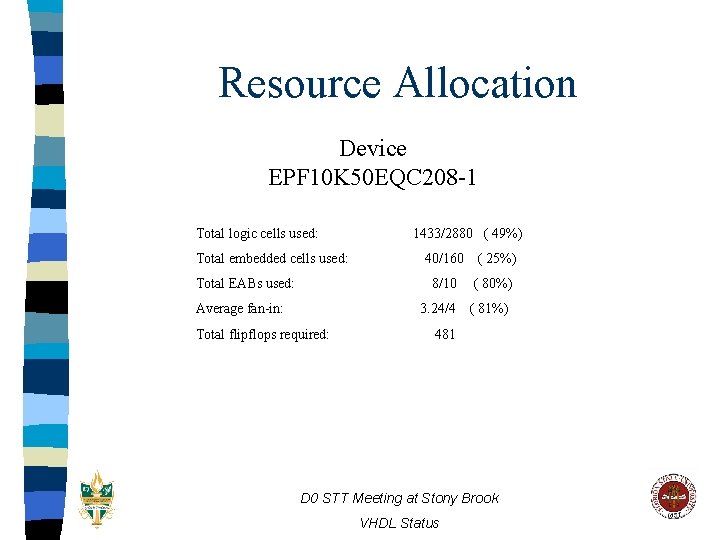

Resource Allocation Device EPF 10 K 50 EQC 208 -1 Total logic cells used: Total embedded cells used: Total EABs used: Average fan-in: 1433/2880 ( 49%) 40/160 ( 25%) 8/10 ( 80%) 3. 24/4 Total flipflops required: ( 81%) 481 D 0 STT Meeting at Stony Brook VHDL Status

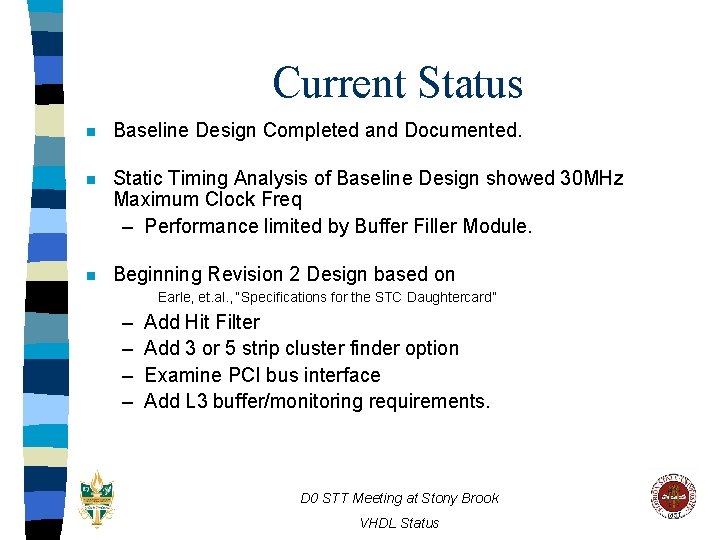

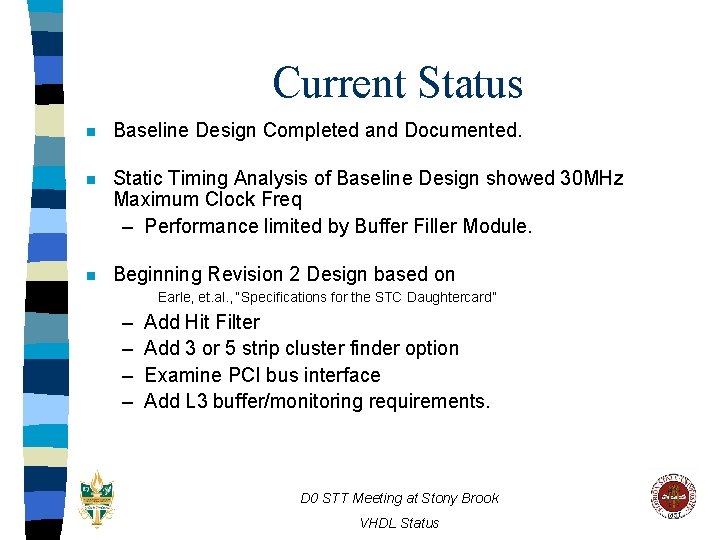

Current Status n Baseline Design Completed and Documented. n Static Timing Analysis of Baseline Design showed 30 MHz Maximum Clock Freq – Performance limited by Buffer Filler Module. n Beginning Revision 2 Design based on Earle, et. al. , “Specifications for the STC Daughtercard” – – Add Hit Filter Add 3 or 5 strip cluster finder option Examine PCI bus interface Add L 3 buffer/monitoring requirements. D 0 STT Meeting at Stony Brook VHDL Status