Univerza v Ljubljani Fakulteta za elektrotehniko GSPV 10

Univerza v Ljubljani Fakulteta za elektrotehniko GSPV (10 -a) HCS 12, časovniki in ECT Stanislav Kovačič http: //vision. fe. uni-lj. si/classes/GSPV

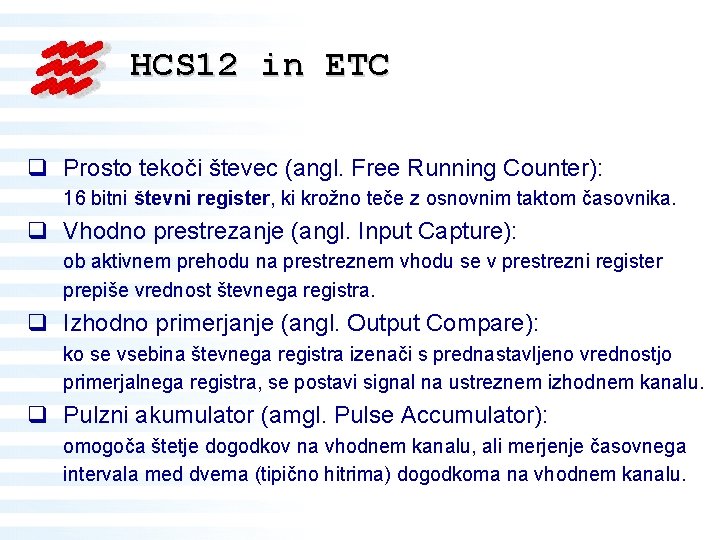

HCS 12 in ETC q Prosto tekoči števec (angl. Free Running Counter): 16 bitni števni register, ki krožno teče z osnovnim taktom časovnika. q Vhodno prestrezanje (angl. Input Capture): ob aktivnem prehodu na prestreznem vhodu se v prestrezni register prepiše vrednost števnega registra. q Izhodno primerjanje (angl. Output Compare): ko se vsebina števnega registra izenači s prednastavljeno vrednostjo primerjalnega registra, se postavi signal na ustreznem izhodnem kanalu. q Pulzni akumulator (amgl. Pulse Accumulator): omogoča štetje dogodkov na vhodnem kanalu, ali merjenje časovnega intervala med dvema (tipično hitrima) dogodkoma na vhodnem kanalu.

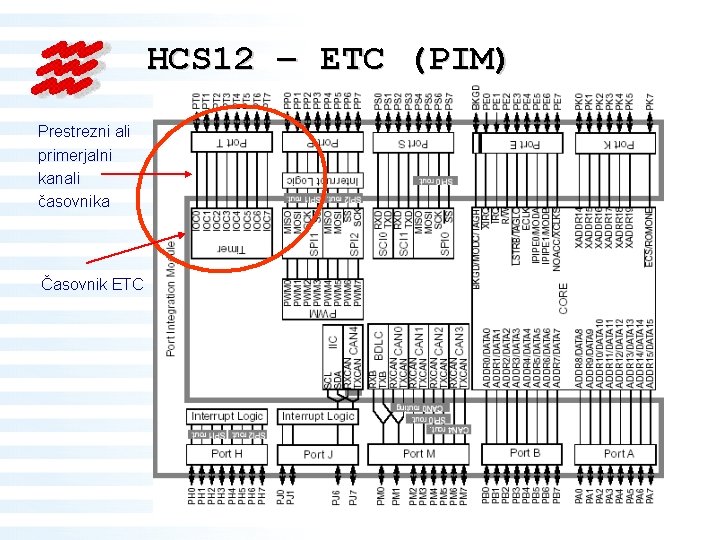

HCS 12 – ETC (PIM) Prestrezni ali primerjalni kanali časovnika Časovnik ETC

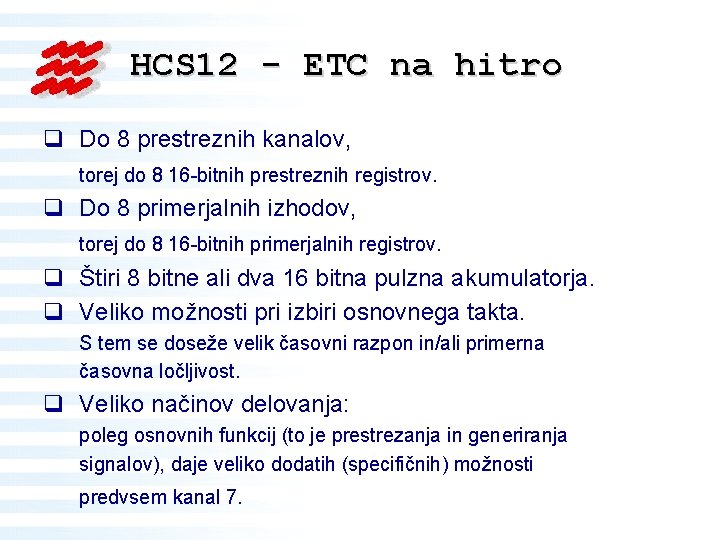

HCS 12 - ETC na hitro q Do 8 prestreznih kanalov, torej do 8 16 -bitnih prestreznih registrov. q Do 8 primerjalnih izhodov, torej do 8 16 -bitnih primerjalnih registrov. q Štiri 8 bitne ali dva 16 bitna pulzna akumulatorja. q Veliko možnosti pri izbiri osnovnega takta. S tem se doseže velik časovni razpon in/ali primerna časovna ločljivost. q Veliko načinov delovanja: poleg osnovnih funkcij (to je prestrezanja in generiranja signalov), daje veliko dodatih (specifičnih) možnosti predvsem kanal 7.

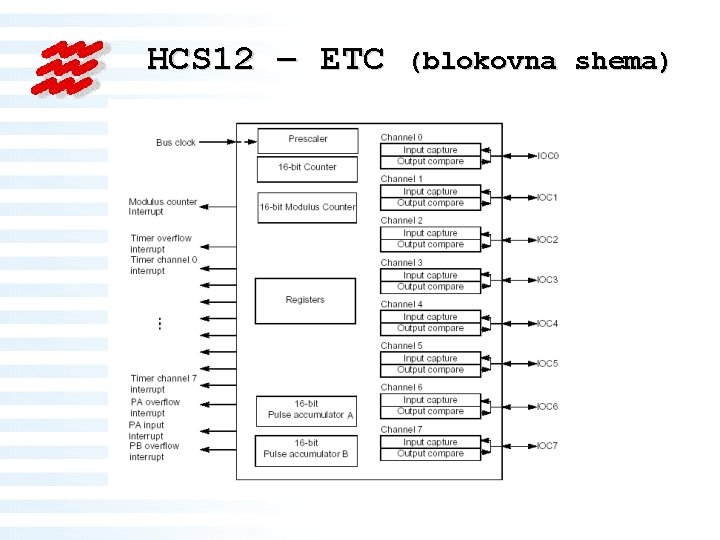

HCS 12 – ETC (blokovna shema)

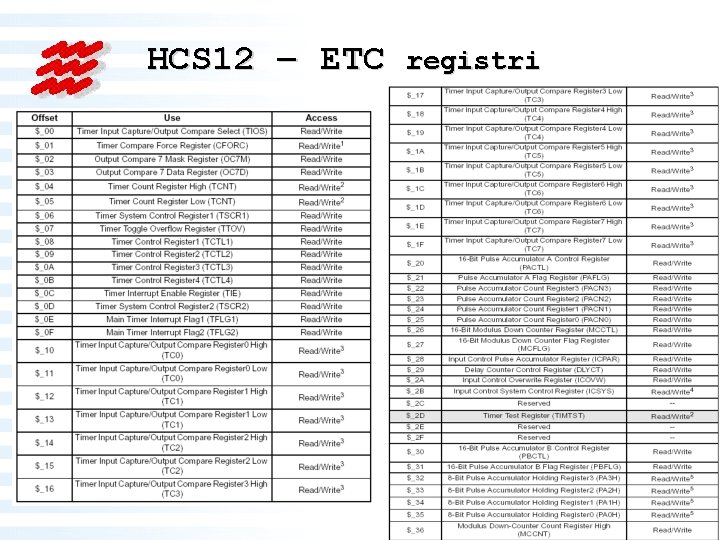

HCS 12 – ETC registri

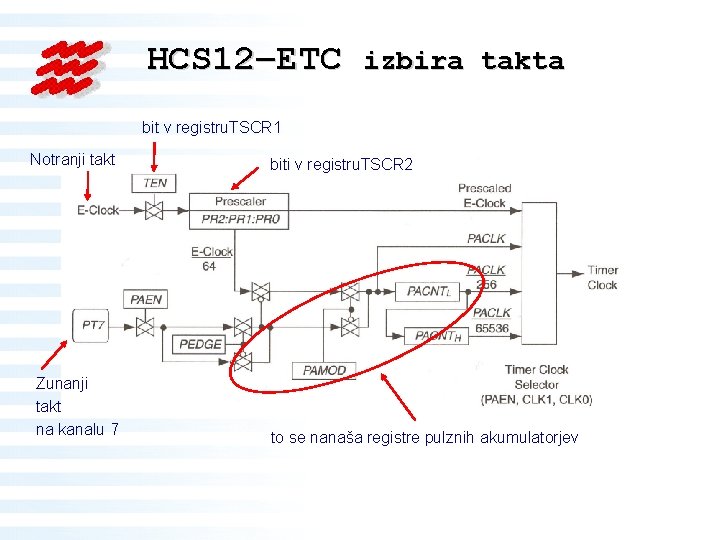

HCS 12–ETC izbira takta bit v registru. TSCR 1 Notranji takt Zunanji takt na kanalu 7 biti v registru. TSCR 2 to se nanaša registre pulznih akumulatorjev

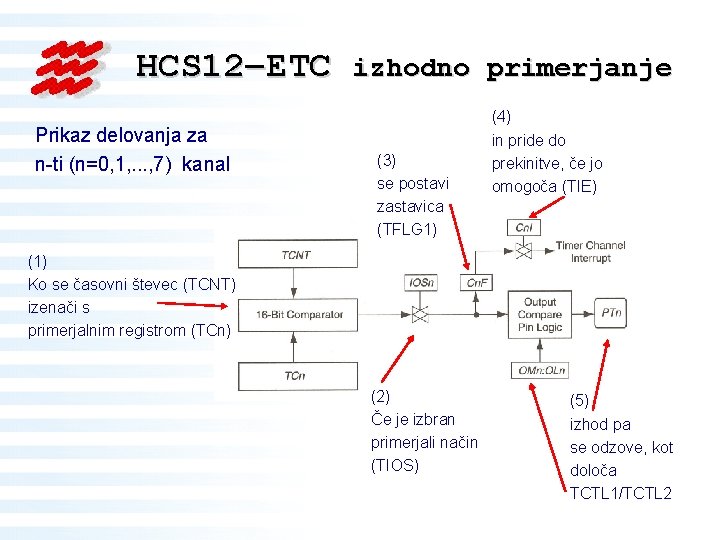

HCS 12–ETC Prikaz delovanja za n-ti (n=0, 1, . . . , 7) kanal izhodno primerjanje (3) se postavi zastavica (TFLG 1) (4) in pride do prekinitve, če jo omogoča (TIE) (1) Ko se časovni števec (TCNT) izenači s primerjalnim registrom (TCn) (2) Če je izbran primerjali način (TIOS) (5) izhod pa se odzove, kot določa TCTL 1/TCTL 2

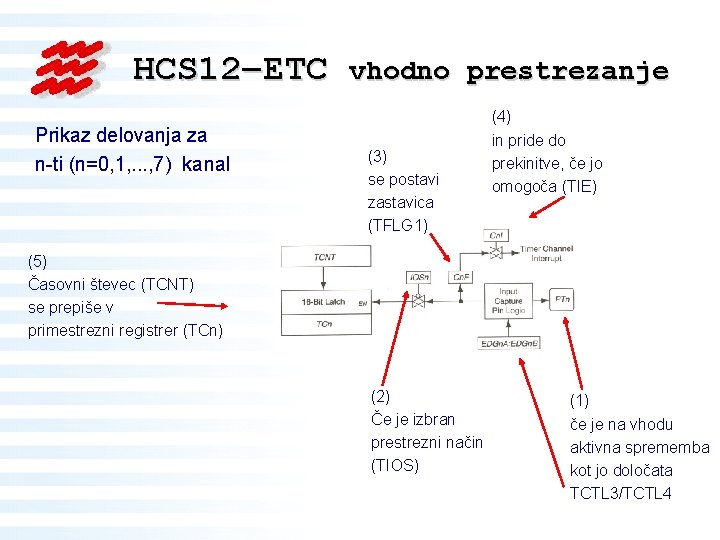

HCS 12–ETC Prikaz delovanja za n-ti (n=0, 1, . . . , 7) kanal vhodno prestrezanje (3) se postavi zastavica (TFLG 1) (4) in pride do prekinitve, če jo omogoča (TIE) (5) Časovni števec (TCNT) se prepiše v primestrezni registrer (TCn) (2) Če je izbran prestrezni način (TIOS) (1) če je na vhodu aktivna sprememba kot jo določata TCTL 3/TCTL 4

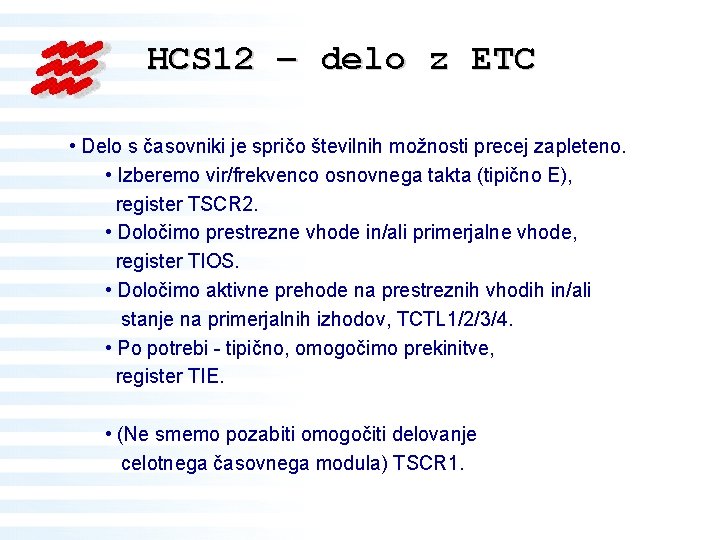

HCS 12 – delo z ETC • Delo s časovniki je spričo številnih možnosti precej zapleteno. • Izberemo vir/frekvenco osnovnega takta (tipično E), register TSCR 2. • Določimo prestrezne vhode in/ali primerjalne vhode, register TIOS. • Določimo aktivne prehode na prestreznih vhodih in/ali stanje na primerjalnih izhodov, TCTL 1/2/3/4. • Po potrebi - tipično, omogočimo prekinitve, register TIE. • (Ne smemo pozabiti omogočiti delovanje celotnega časovnega modula) TSCR 1.

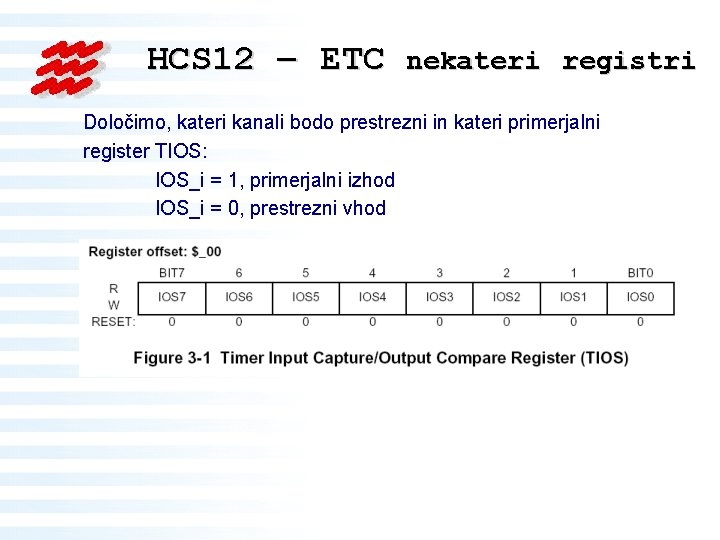

HCS 12 – ETC nekateri registri Določimo, kateri kanali bodo prestrezni in kateri primerjalni register TIOS: IOS_i = 1, primerjalni izhod IOS_i = 0, prestrezni vhod

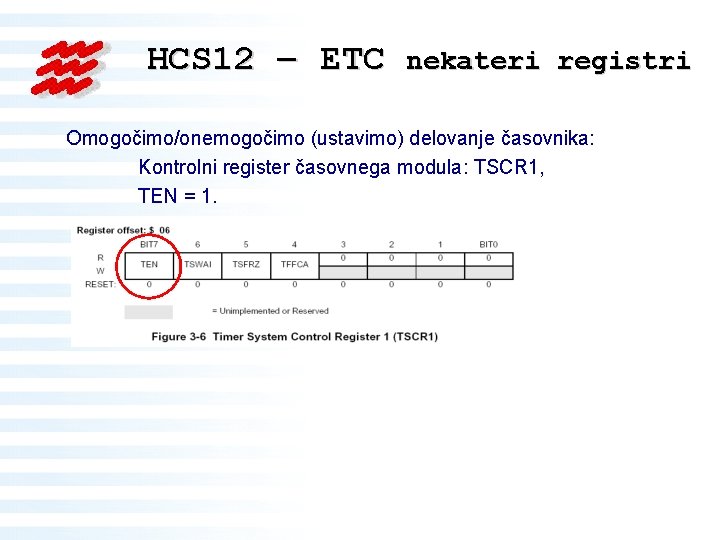

HCS 12 – ETC nekateri registri Omogočimo/onemogočimo (ustavimo) delovanje časovnika: Kontrolni register časovnega modula: TSCR 1, TEN = 1.

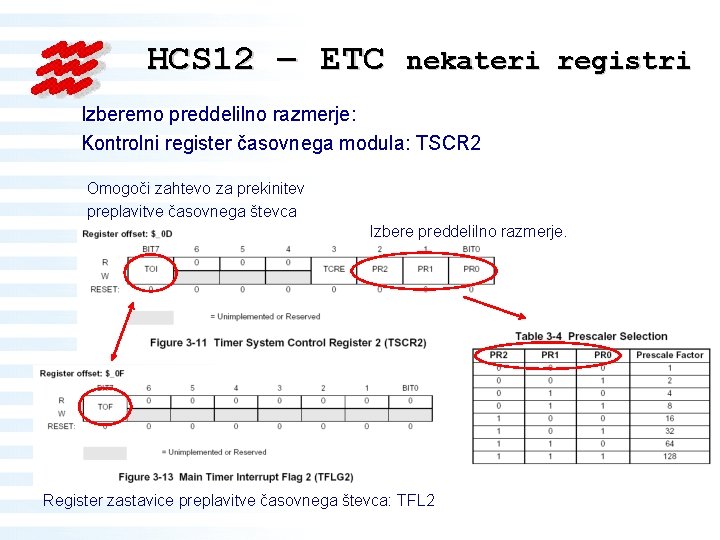

HCS 12 – ETC nekateri registri Izberemo preddelilno razmerje: Kontrolni register časovnega modula: TSCR 2 Omogoči zahtevo za prekinitev preplavitve časovnega števca Izbere preddelilno razmerje. Register zastavice preplavitve časovnega števca: TFL 2

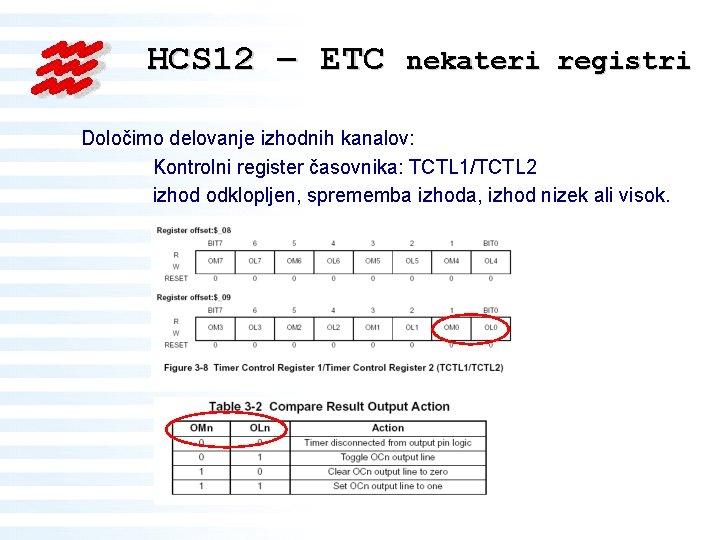

HCS 12 – ETC nekateri registri Določimo delovanje izhodnih kanalov: Kontrolni register časovnika: TCTL 1/TCTL 2 izhod odklopljen, sprememba izhoda, izhod nizek ali visok.

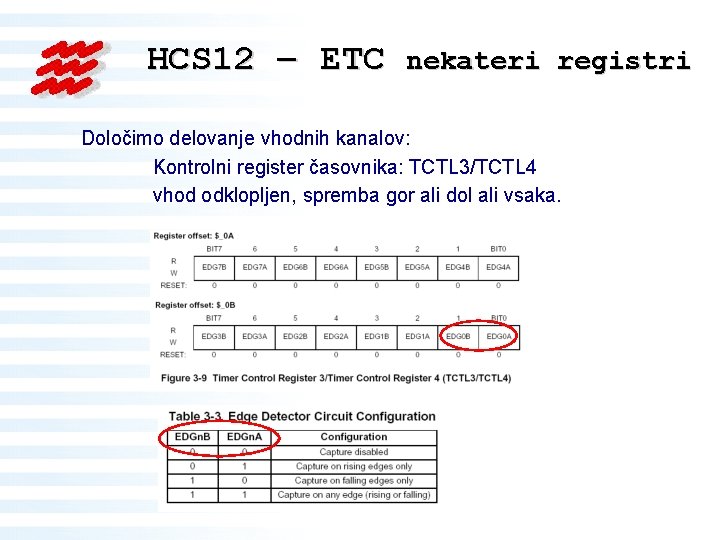

HCS 12 – ETC nekateri registri Določimo delovanje vhodnih kanalov: Kontrolni register časovnika: TCTL 3/TCTL 4 vhod odklopljen, spremba gor ali dol ali vsaka.

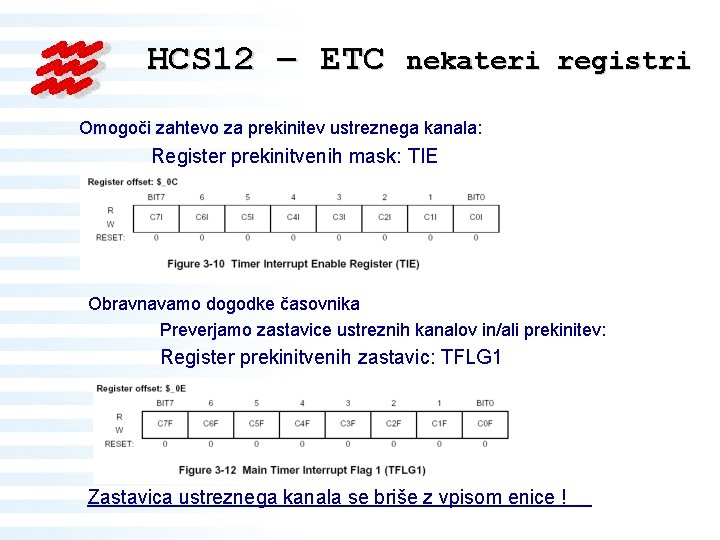

HCS 12 – ETC nekateri registri Omogoči zahtevo za prekinitev ustreznega kanala: Register prekinitvenih mask: TIE Obravnavamo dogodke časovnika Preverjamo zastavice ustreznih kanalov in/ali prekinitev: Register prekinitvenih zastavic: TFLG 1 Zastavica ustreznega kanala se briše z vpisom enice !

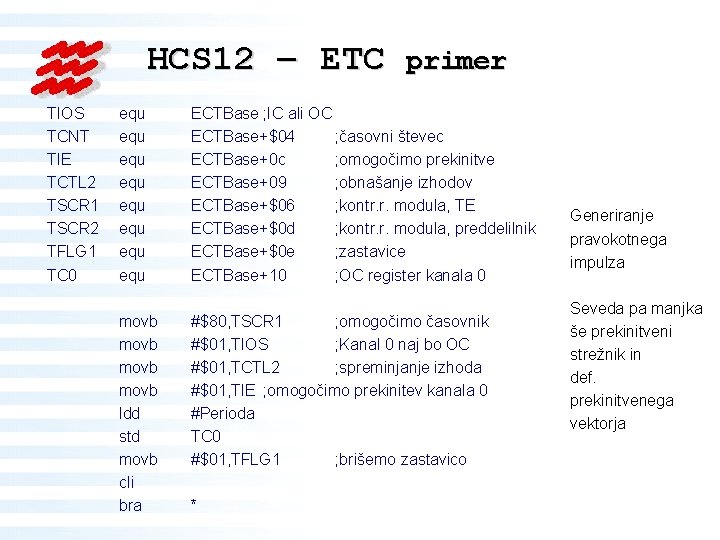

HCS 12 – ETC TIOS TCNT TIE TCTL 2 TSCR 1 TSCR 2 TFLG 1 TC 0 primer equ equ ECTBase ; IC ali OC ECTBase+$04 ; časovni števec ECTBase+0 c ; omogočimo prekinitve ECTBase+09 ; obnašanje izhodov ECTBase+$06 ; kontr. r. modula, TE ECTBase+$0 d ; kontr. r. modula, preddelilnik ECTBase+$0 e ; zastavice ECTBase+10 ; OC register kanala 0 movb ldd std movb cli bra #$80, TSCR 1 ; omogočimo časovnik #$01, TIOS ; Kanal 0 naj bo OC #$01, TCTL 2 ; spreminjanje izhoda #$01, TIE ; omogočimo prekinitev kanala 0 #Perioda TC 0 #$01, TFLG 1 ; brišemo zastavico * Generiranje pravokotnega impulza Seveda pa manjka še prekinitveni strežnik in def. prekinitvenega vektorja

HCS 12 – ETC registri

- Slides: 18