UART JinFu Li Introduction UART modem Universal asynchronous

- Slides: 7

UART Jin-Fu Li

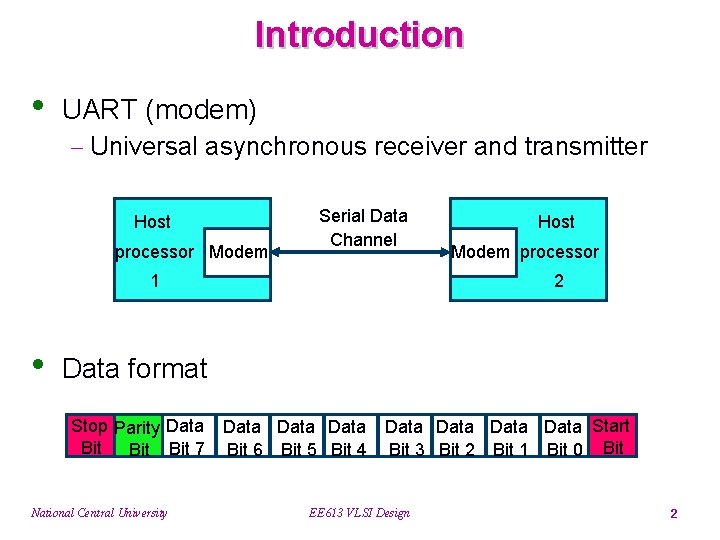

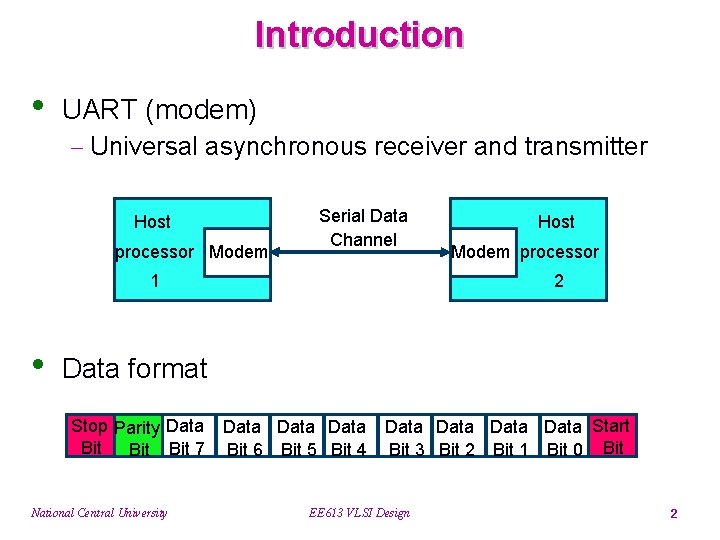

Introduction • UART (modem) - Universal asynchronous receiver and transmitter Host processor Modem Serial Data Channel 1 • Host Modem processor 2 Data format Stop Parity Data Bit Bit 7 National Central University Data Bit 6 Bit 5 Bit 4 Data Start Bit 3 Bit 2 Bit 1 Bit 0 Bit EE 613 VLSI Design 2

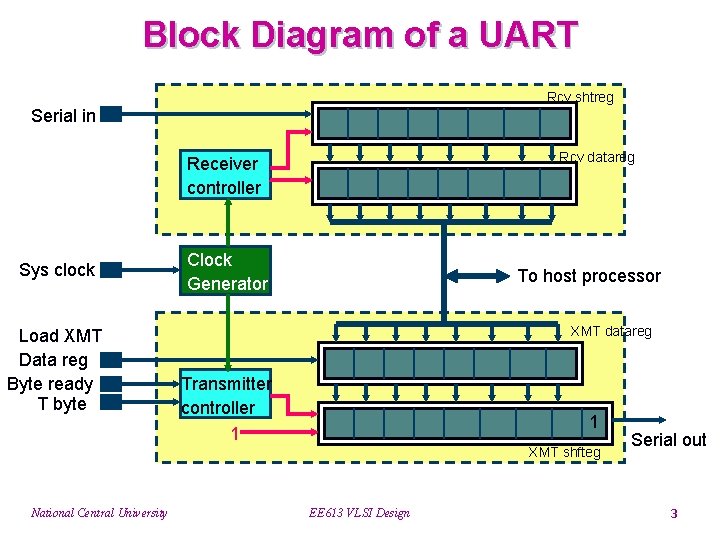

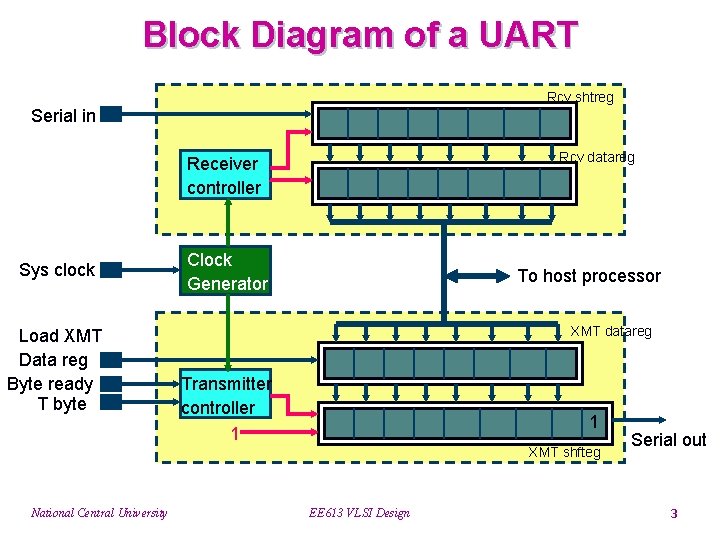

Block Diagram of a UART Rcv shtreg Serial in Rcv datareg Receiver controller Sys clock Load XMT Data reg Byte ready T byte National Central University Clock Generator To host processor XMT datareg Transmitter controller 1 1 XMT shfteg EE 613 VLSI Design Serial out 3

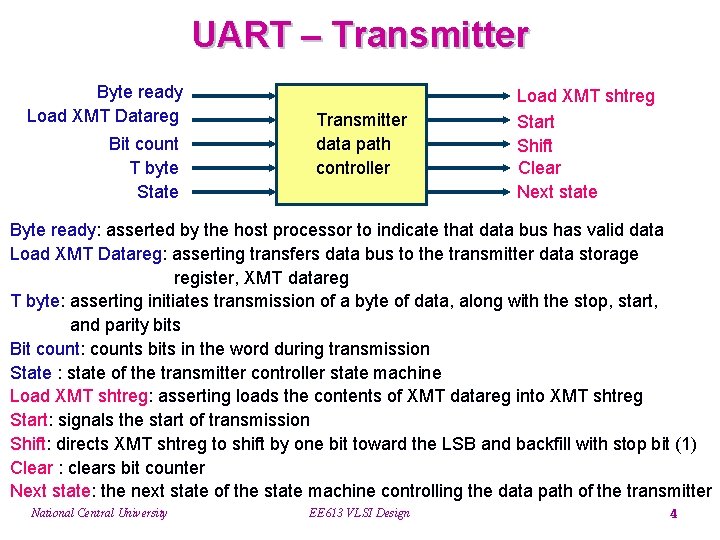

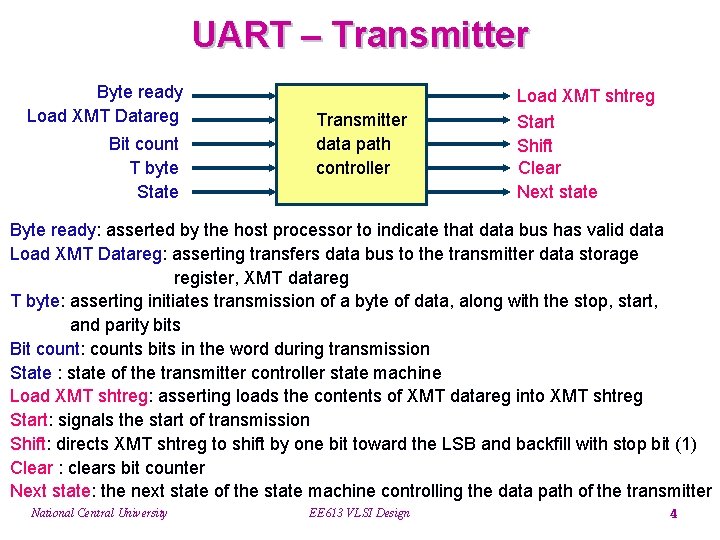

UART – Transmitter Byte ready Load XMT Datareg Bit count T byte State Transmitter data path controller Load XMT shtreg Start Shift Clear Next state Byte ready: asserted by the host processor to indicate that data bus has valid data Load XMT Datareg: asserting transfers data bus to the transmitter data storage register, XMT datareg T byte: asserting initiates transmission of a byte of data, along with the stop, start, and parity bits Bit count: counts bits in the word during transmission State : state of the transmitter controller state machine Load XMT shtreg: asserting loads the contents of XMT datareg into XMT shtreg Start: signals the start of transmission Shift: directs XMT shtreg to shift by one bit toward the LSB and backfill with stop bit (1) Clear : clears bit counter Next state: the next state of the state machine controlling the data path of the transmitter National Central University EE 613 VLSI Design 4

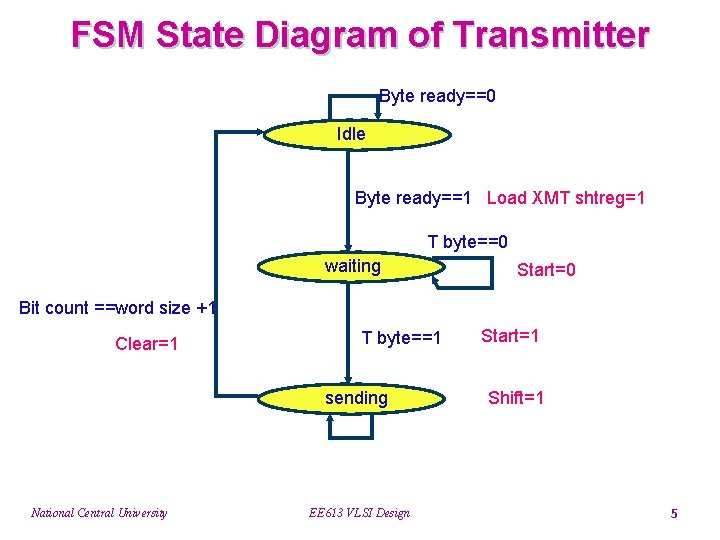

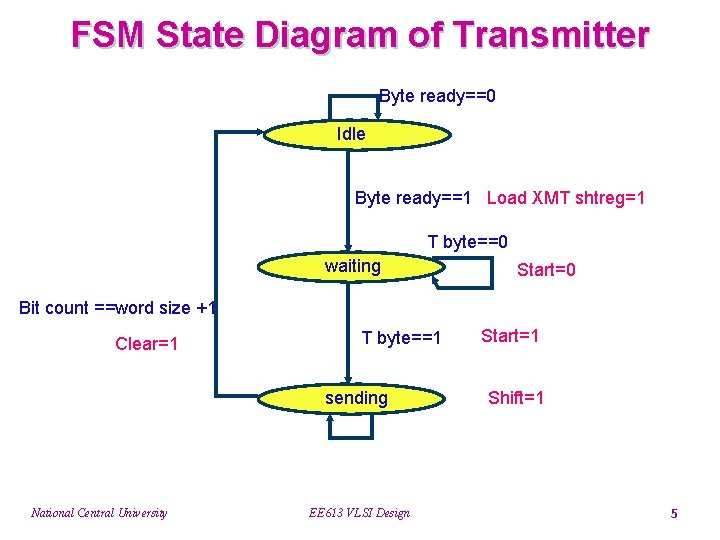

FSM State Diagram of Transmitter Byte ready==0 Idle Byte ready==1 Load XMT shtreg=1 T byte==0 waiting Start=0 Bit count ==word size +1 Clear=1 T byte==1 sending National Central University EE 613 VLSI Design Start=1 Shift=1 5

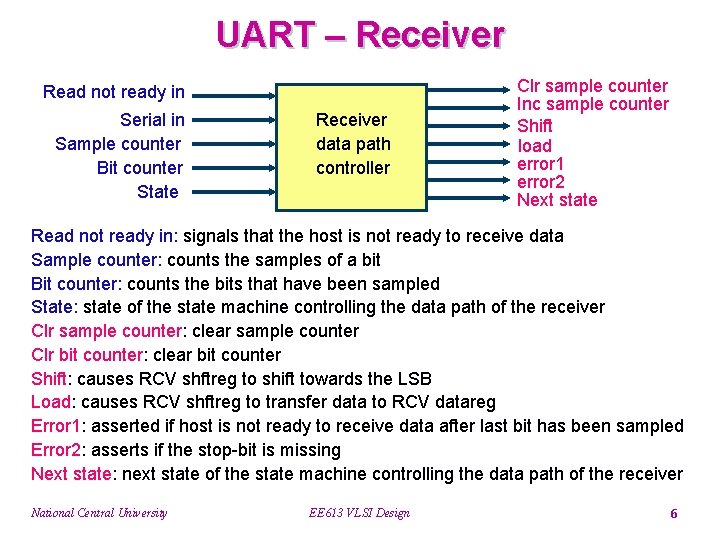

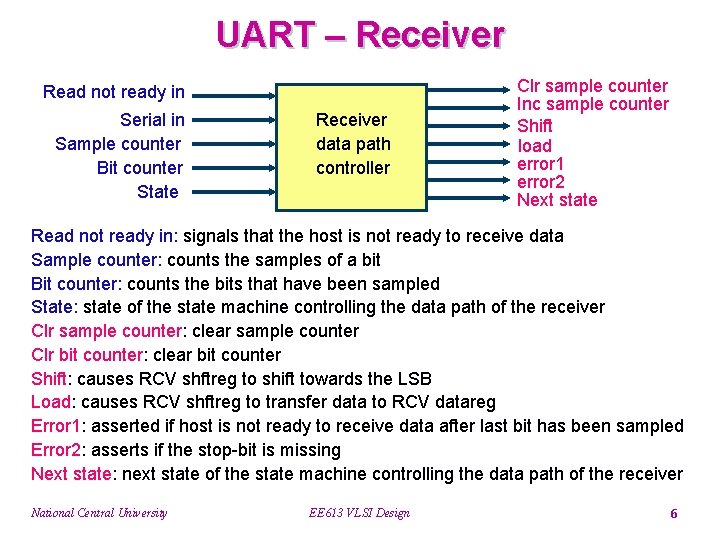

UART – Receiver Read not ready in Serial in Sample counter Bit counter State Receiver data path controller Clr sample counter Inc sample counter Shift load error 1 error 2 Next state Read not ready in: signals that the host is not ready to receive data Sample counter: counts the samples of a bit Bit counter: counts the bits that have been sampled State: state of the state machine controlling the data path of the receiver Clr sample counter: clear sample counter Clr bit counter: clear bit counter Shift: causes RCV shftreg to shift towards the LSB Load: causes RCV shftreg to transfer data to RCV datareg Error 1: asserted if host is not ready to receive data after last bit has been sampled Error 2: asserts if the stop-bit is missing Next state: next state of the state machine controlling the data path of the receiver National Central University EE 613 VLSI Design 6

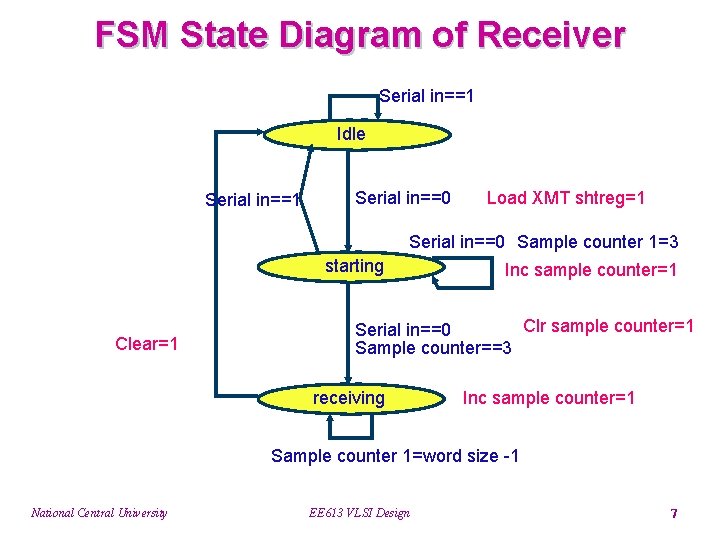

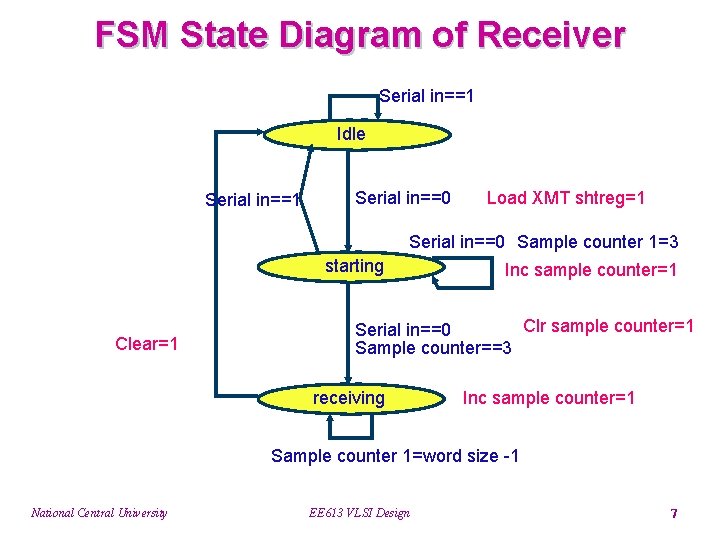

FSM State Diagram of Receiver Serial in==1 Idle Serial in==1 Serial in==0 Load XMT shtreg=1 Serial in==0 Sample counter 1=3 starting Clear=1 Inc sample counter=1 Clr sample counter=1 Serial in==0 Sample counter==3 receiving Inc sample counter=1 Sample counter 1=word size -1 National Central University EE 613 VLSI Design 7