Chapter 4 UART Serial Port Programming 1 Serial

![Sample rate options in CTRLA register SAMPR[2: 0] Descriptions 0 x 0 16 x Sample rate options in CTRLA register SAMPR[2: 0] Descriptions 0 x 0 16 x](https://slidetodoc.com/presentation_image_h/872b42f7d2e1667ae0dd2a0bb4a8d61a/image-25.jpg)

![SAMD 2 x Signals Used for UART (See CTRLA register) TXPO[1: 0] PAD RXPO[1: SAMD 2 x Signals Used for UART (See CTRLA register) TXPO[1: 0] PAD RXPO[1:](https://slidetodoc.com/presentation_image_h/872b42f7d2e1667ae0dd2a0bb4a8d61a/image-36.jpg)

- Slides: 38

Chapter 4 UART Serial Port Programming 1

Serial vs. Parallel Data Transfer 2

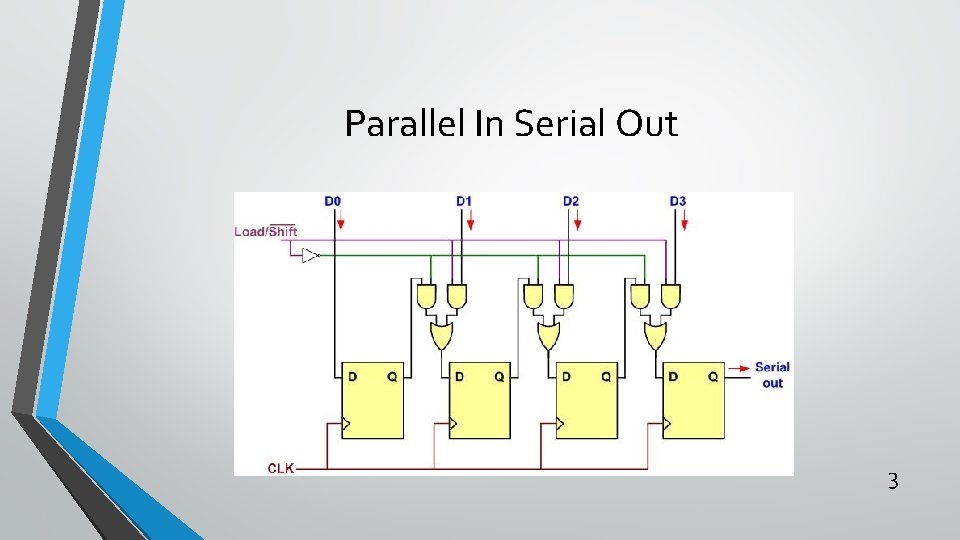

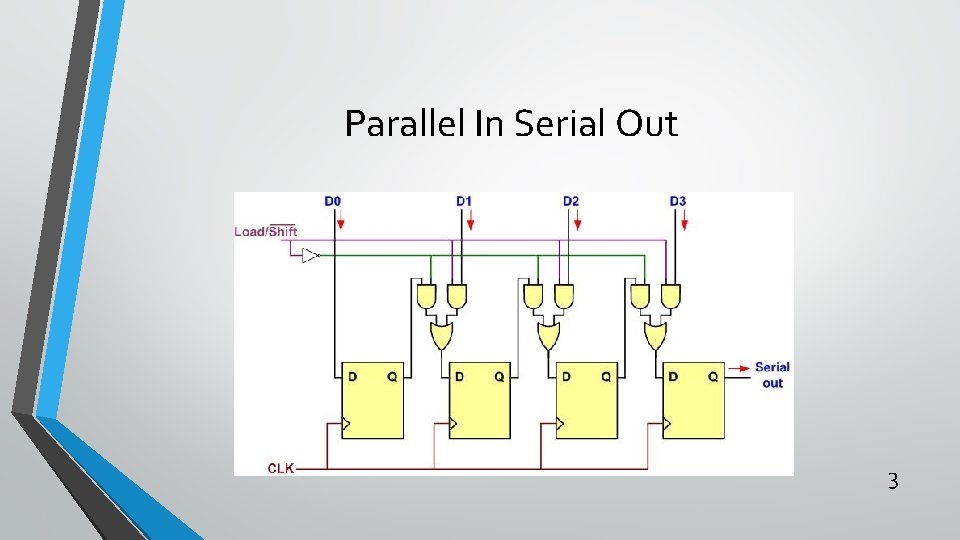

Parallel In Serial Out 3

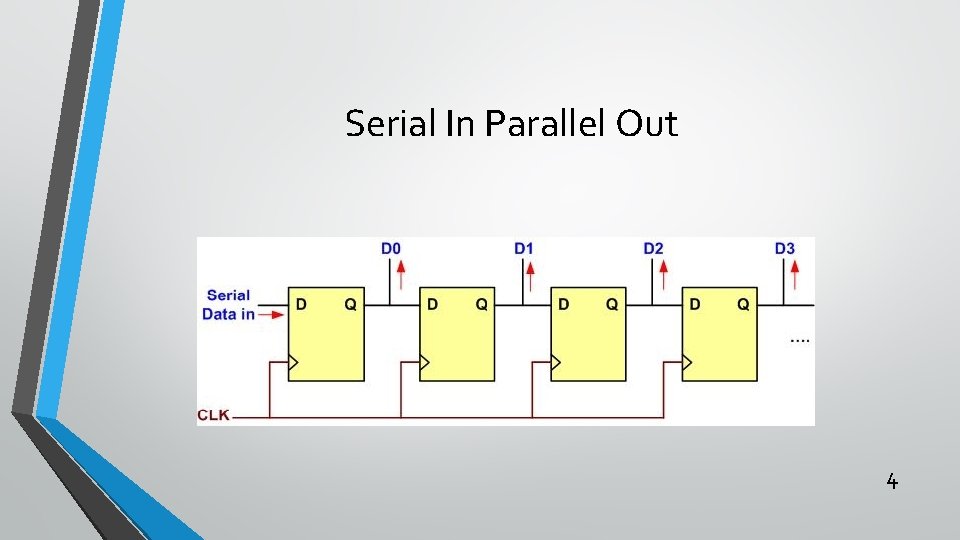

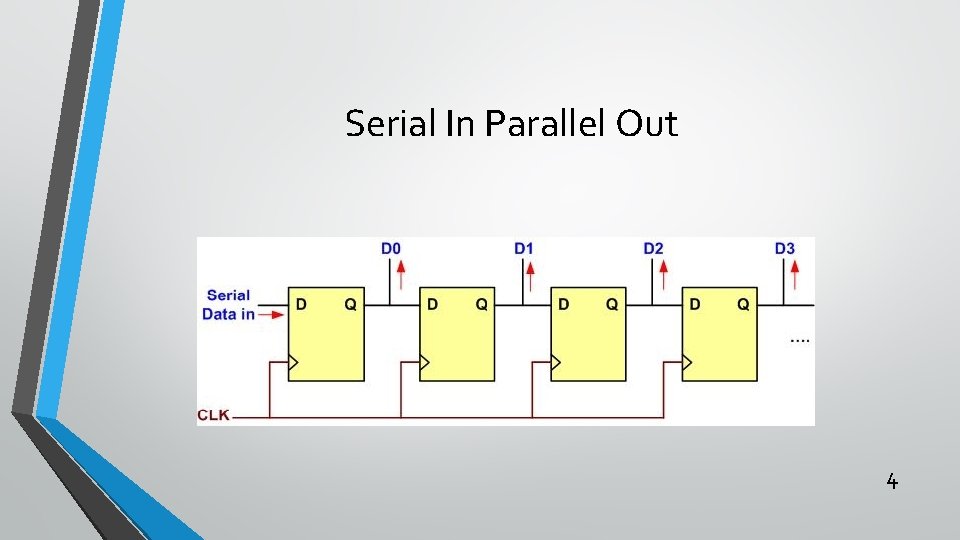

Serial In Parallel Out 4

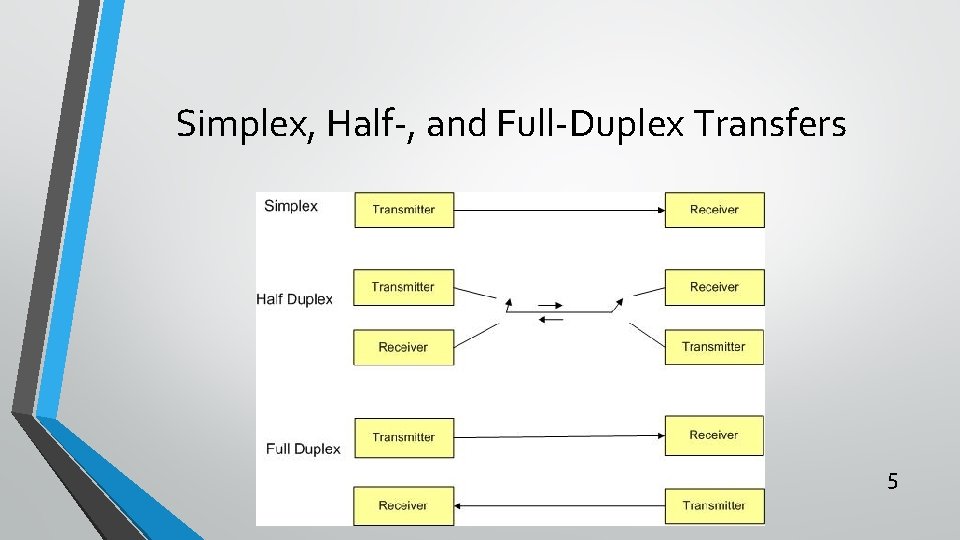

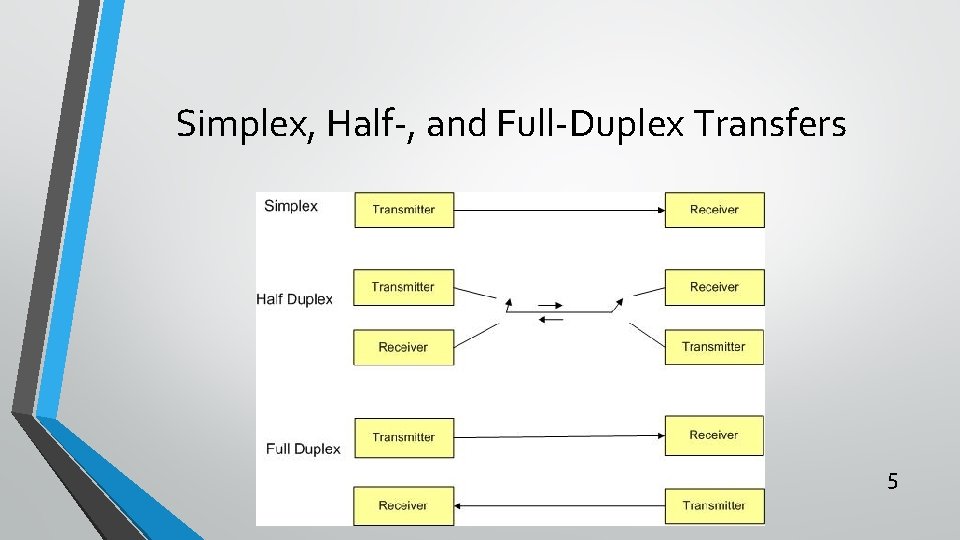

Simplex, Half-, and Full-Duplex Transfers 5

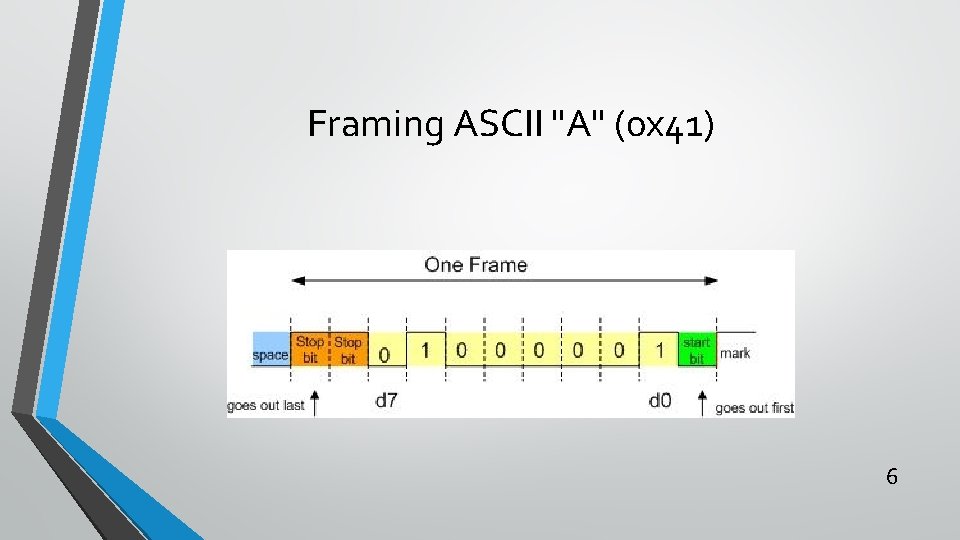

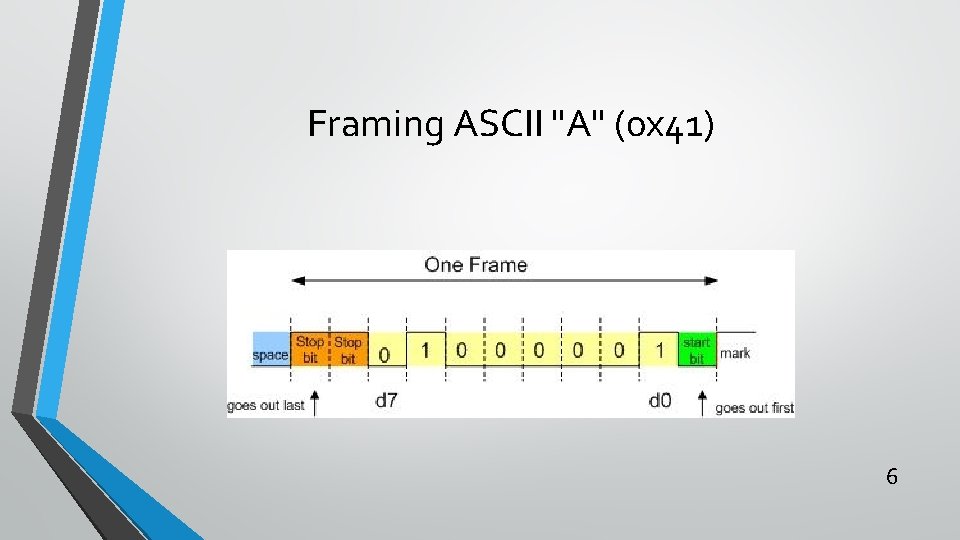

Framing ASCII "A" (0 x 41) 6

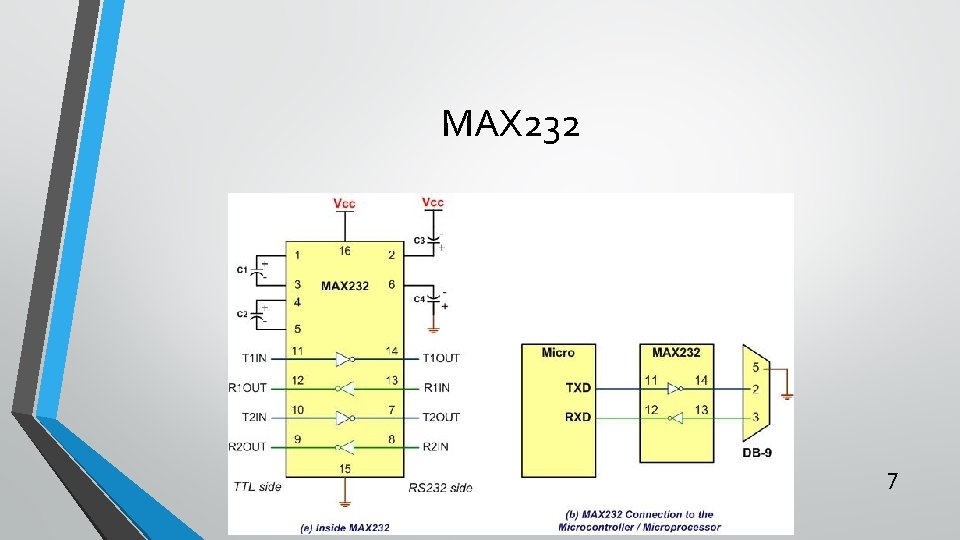

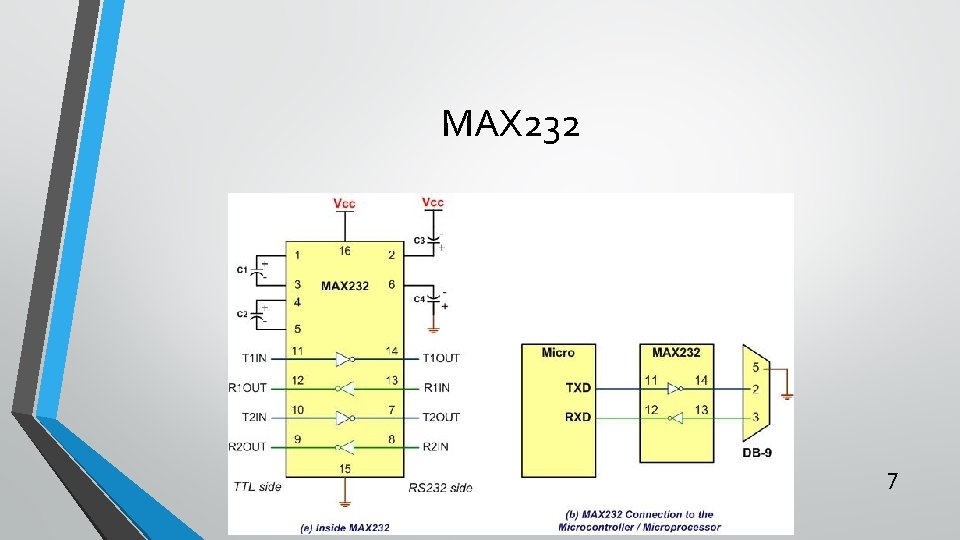

MAX 232 7

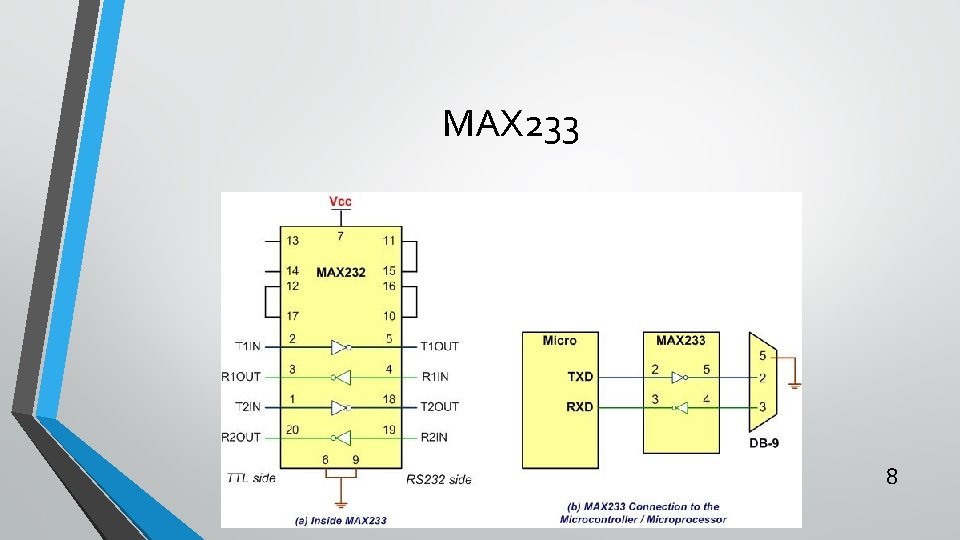

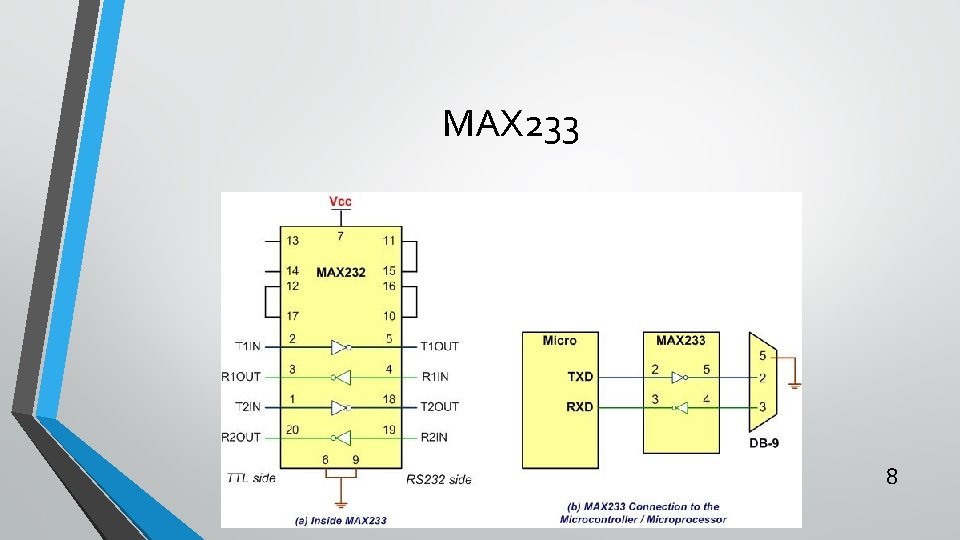

MAX 233 8

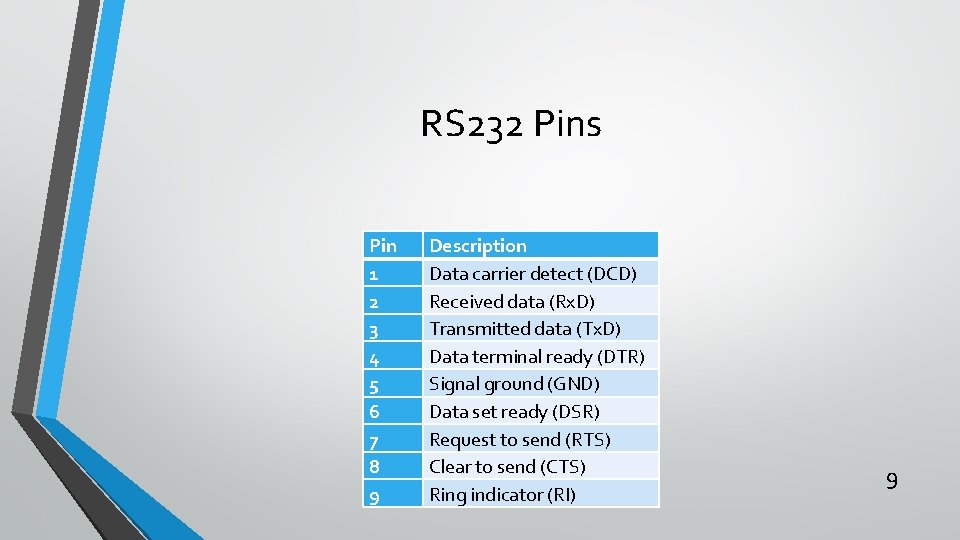

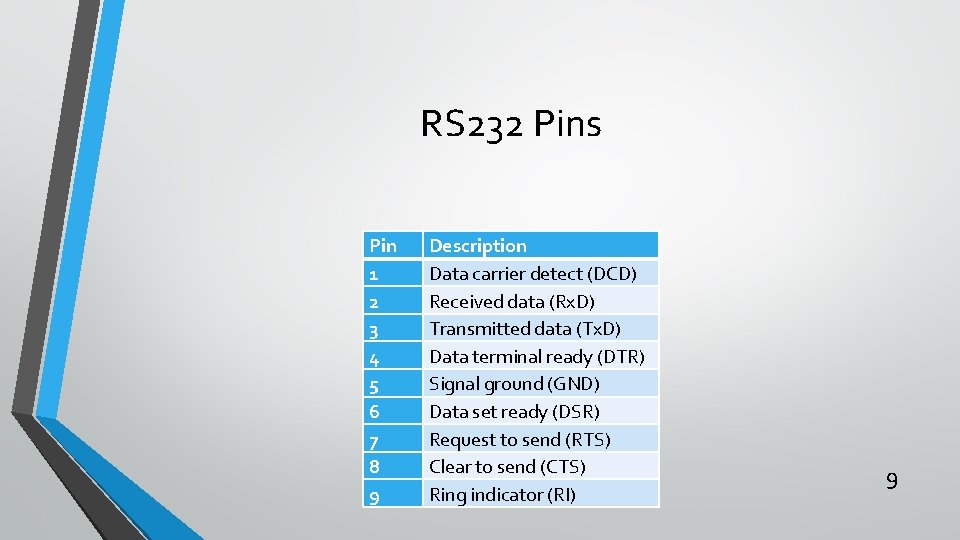

RS 232 Pins Pin 1 2 3 4 5 6 7 8 9 Description Data carrier detect (DCD) Received data (Rx. D) Transmitted data (Tx. D) Data terminal ready (DTR) Signal ground (GND) Data set ready (DSR) Request to send (RTS) Clear to send (CTS) Ring indicator (RI) 9

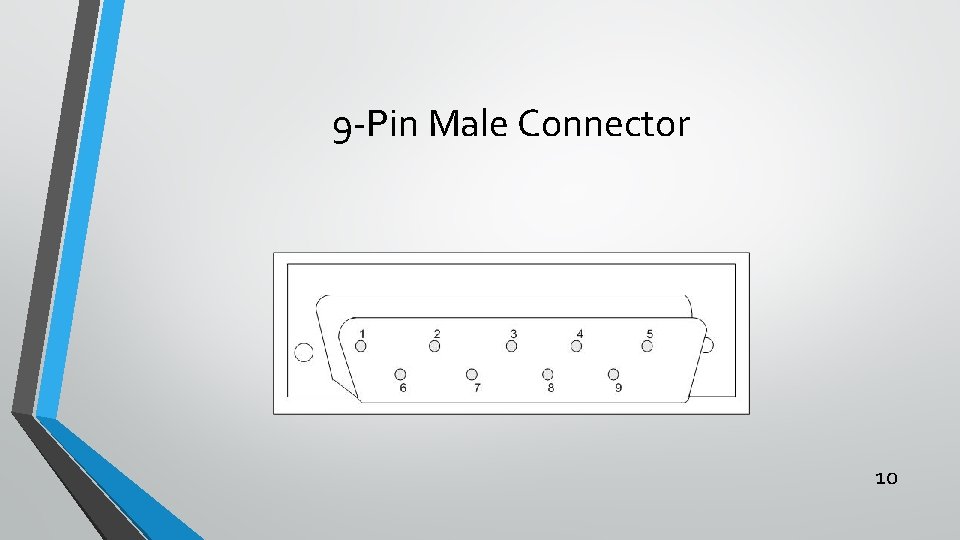

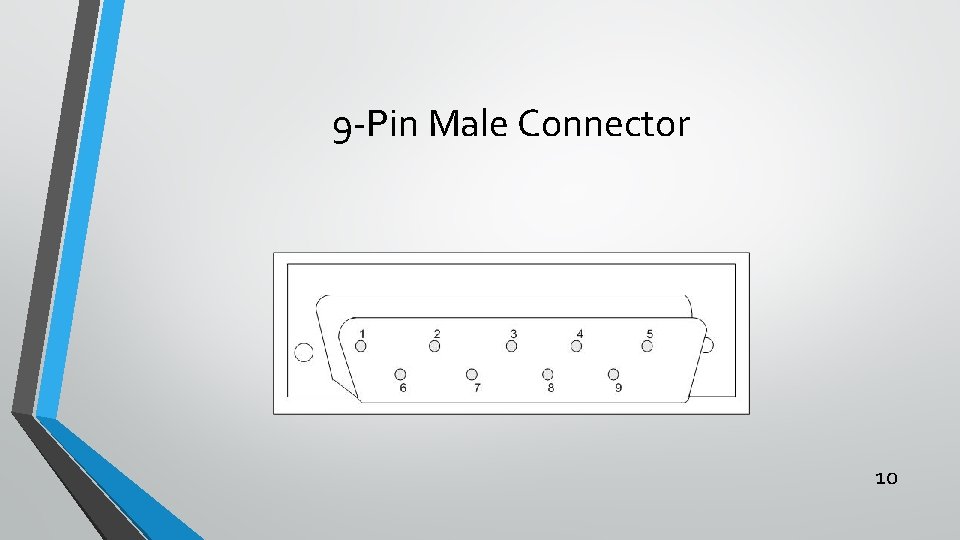

9 -Pin Male Connector 10

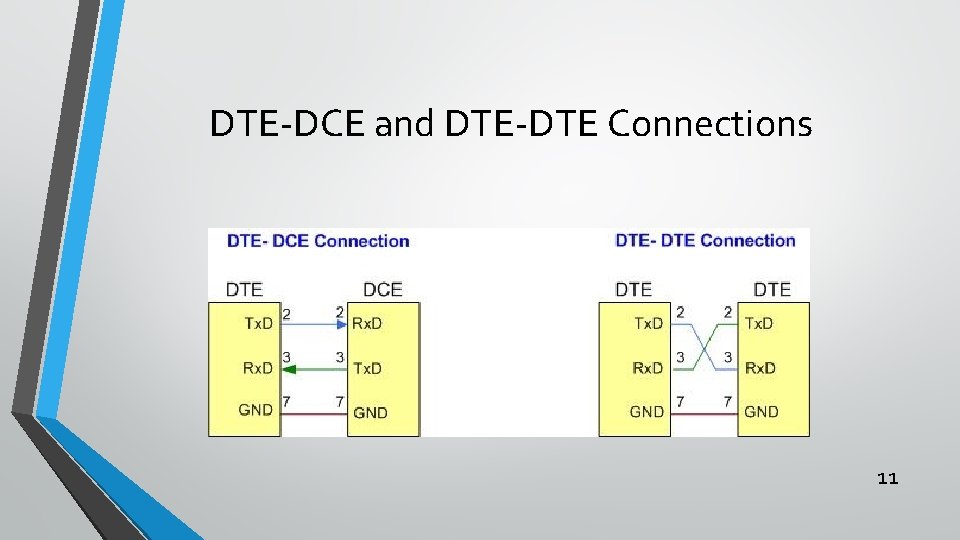

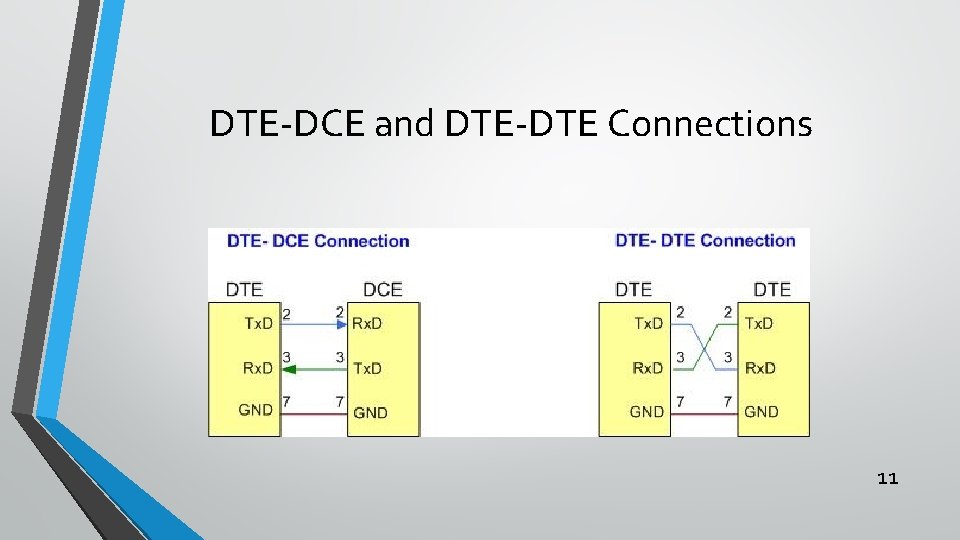

DTE-DCE and DTE-DTE Connections 11

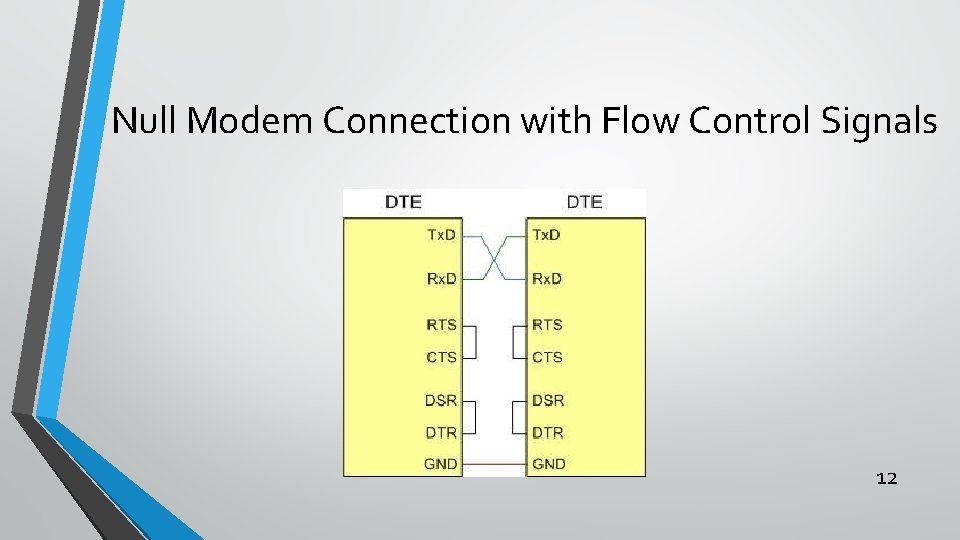

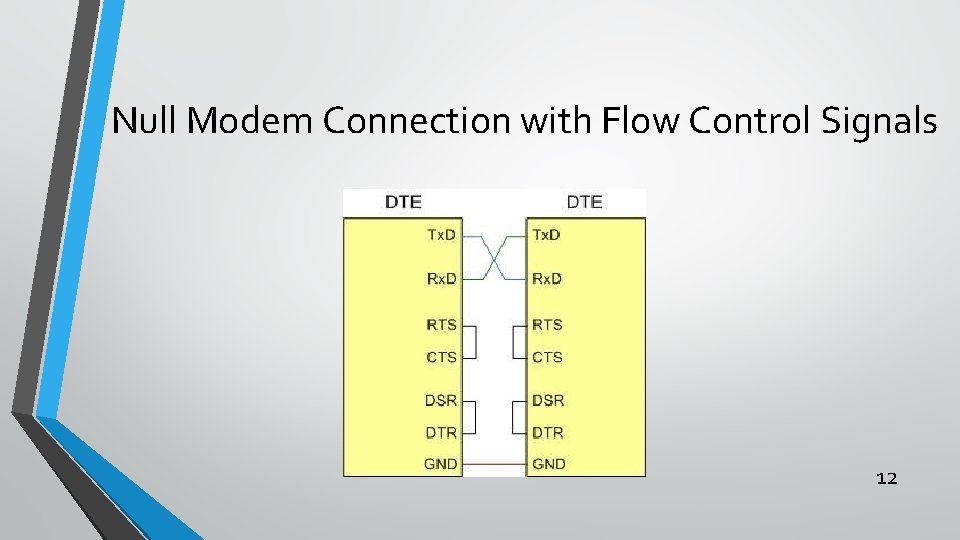

Null Modem Connection with Flow Control Signals 12

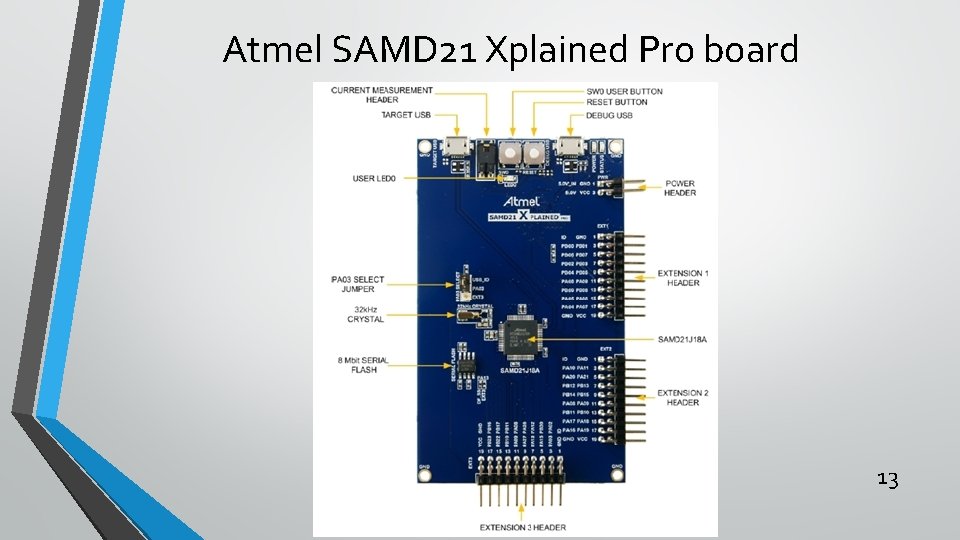

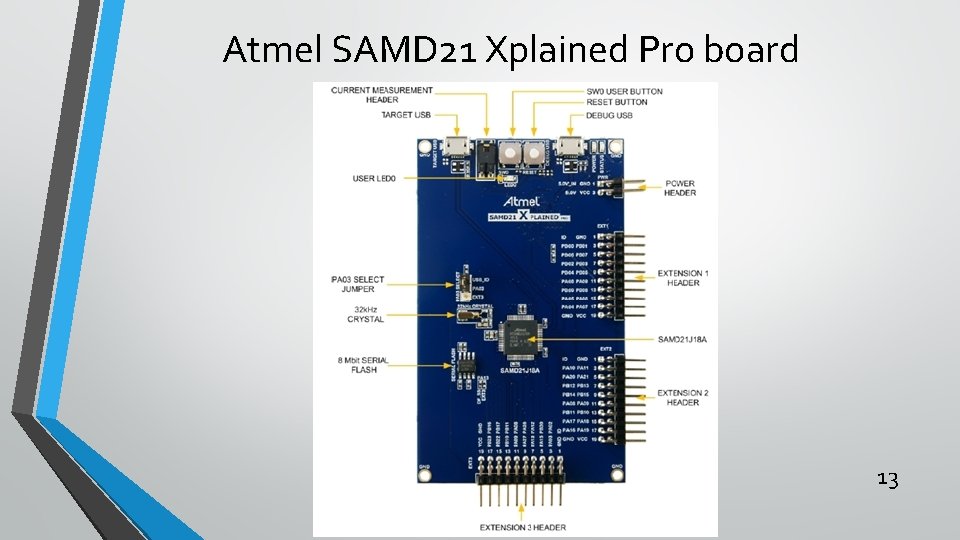

Atmel SAMD 21 Xplained Pro board 13

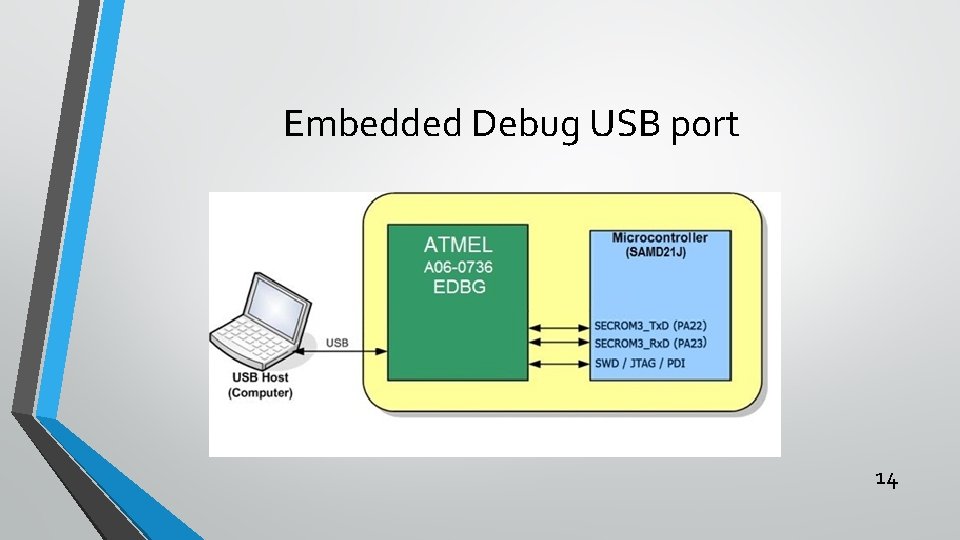

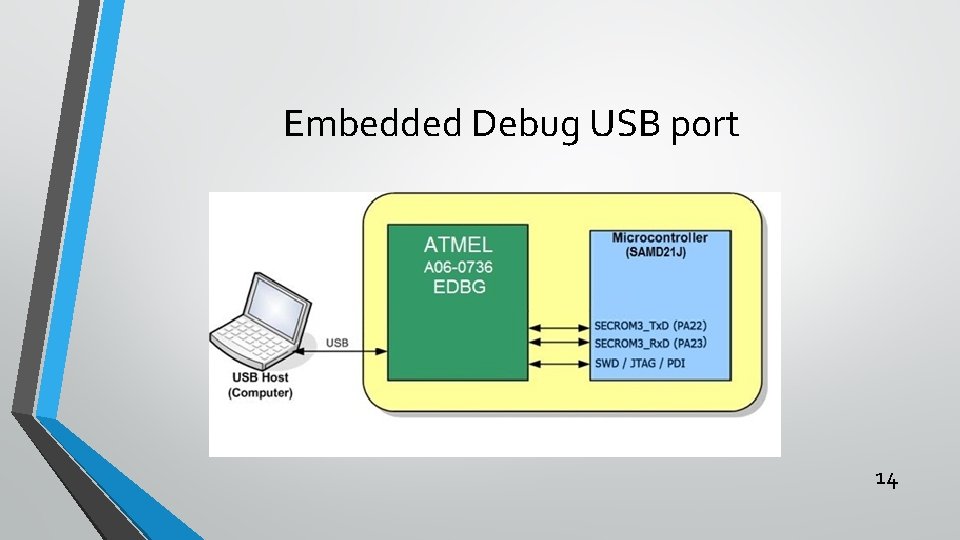

Embedded Debug USB port 14

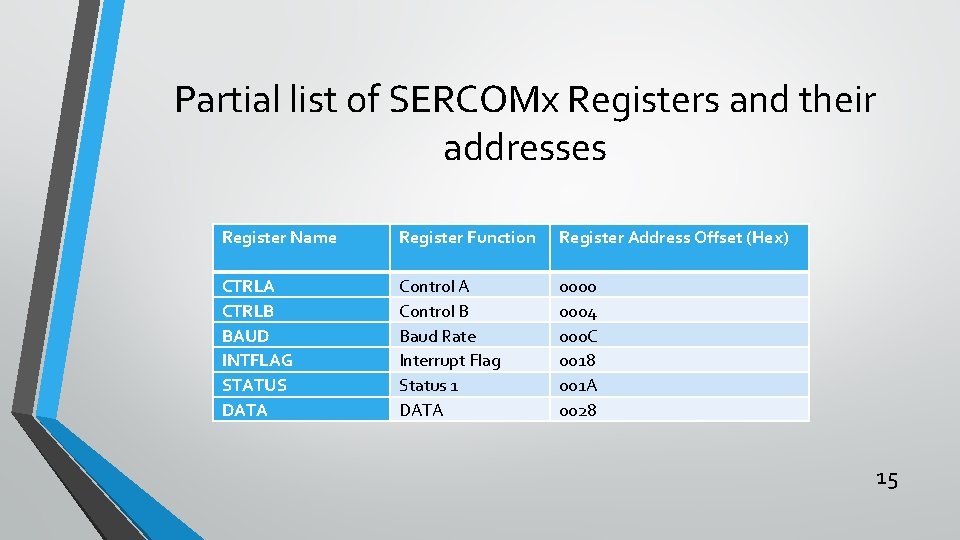

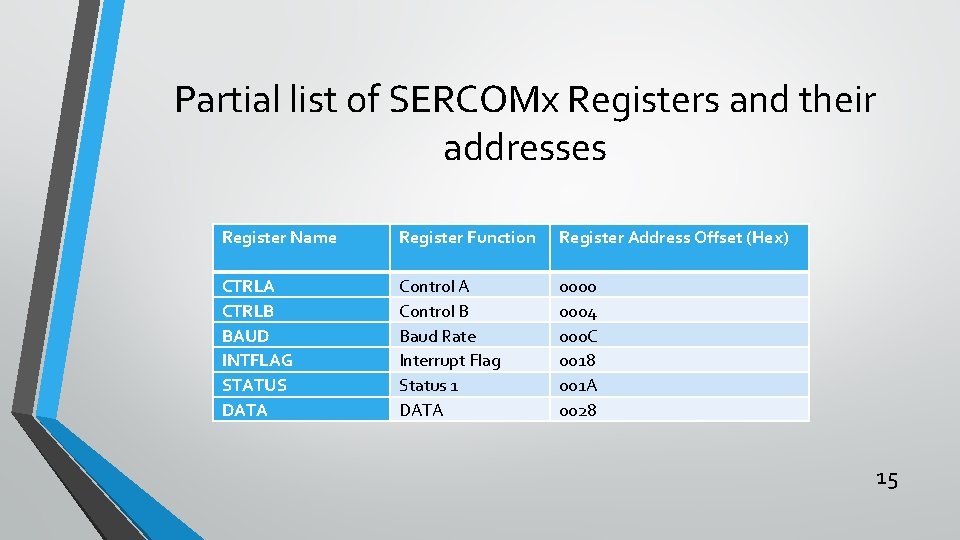

Partial list of SERCOMx Registers and their addresses Register Name Register Function Register Address Offset (Hex) CTRLA CTRLB BAUD INTFLAG STATUS DATA Control B Baud Rate Interrupt Flag Status 1 DATA 0000 0004 000 C 0018 001 A 0028 15

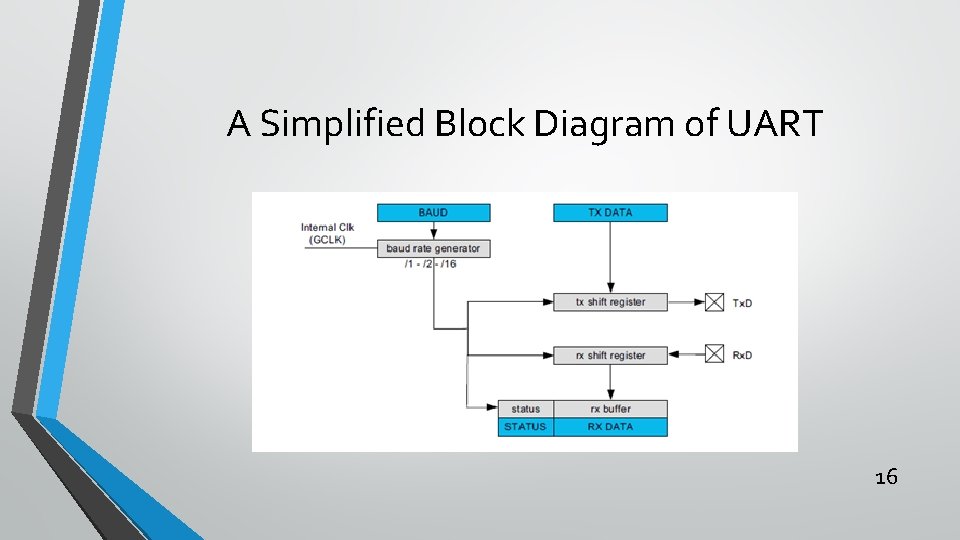

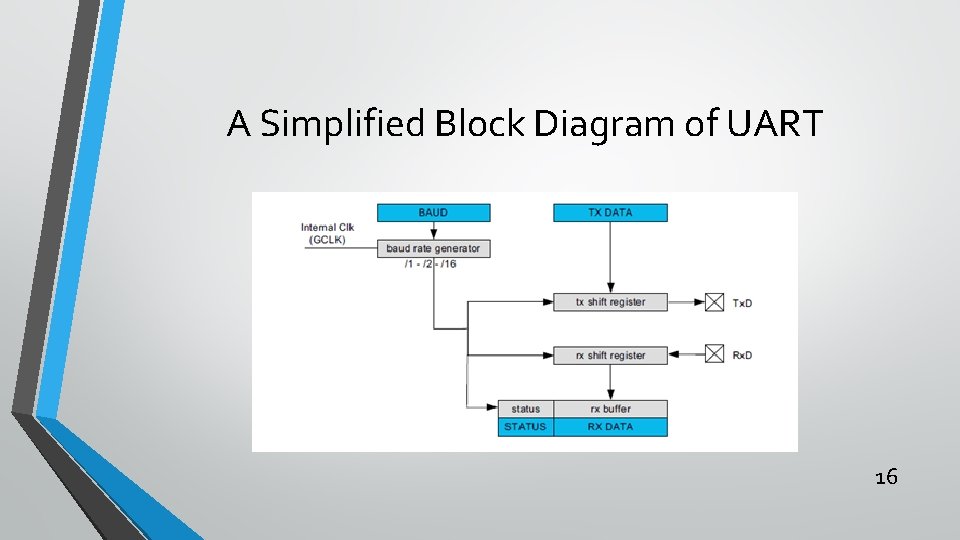

A Simplified Block Diagram of UART 16

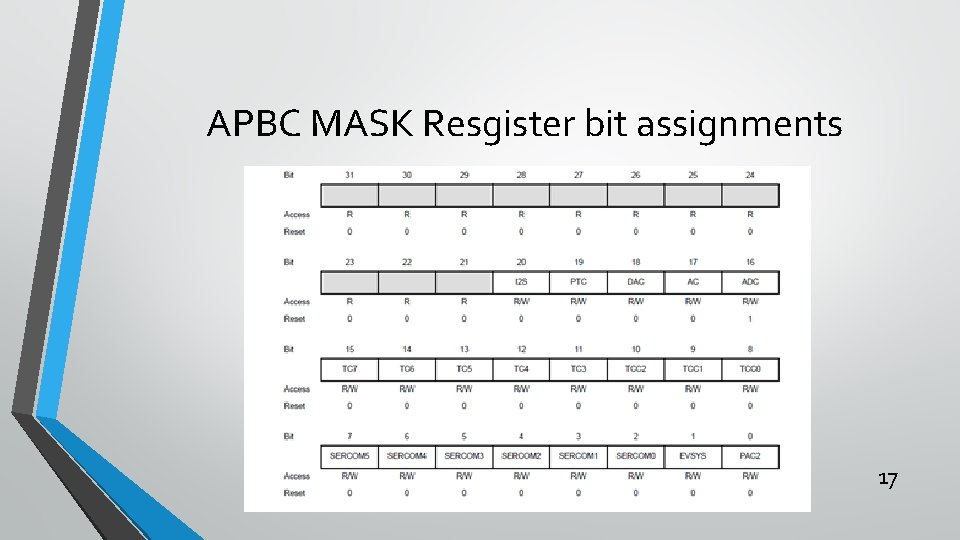

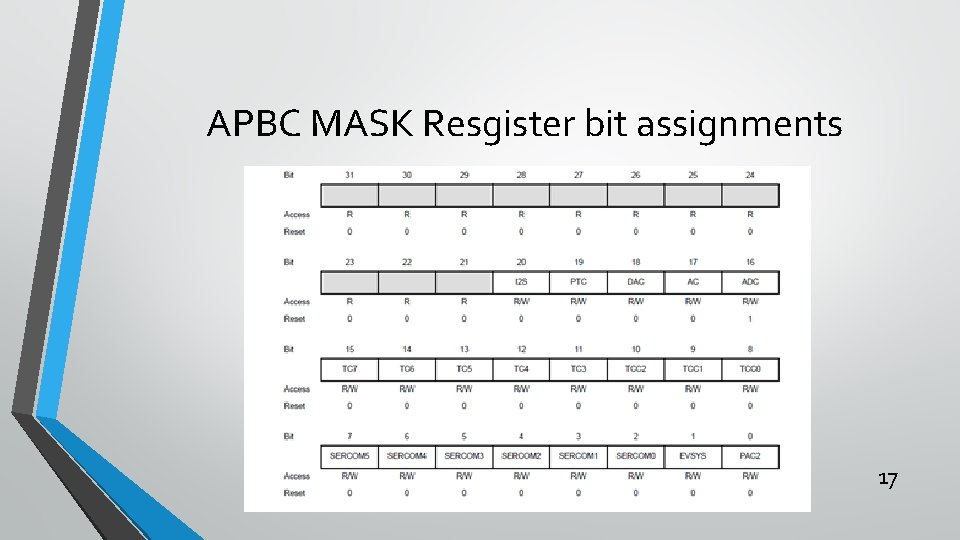

APBC MASK Resgister bit assignments 17

APBC MASK Resgister bit assignments 18

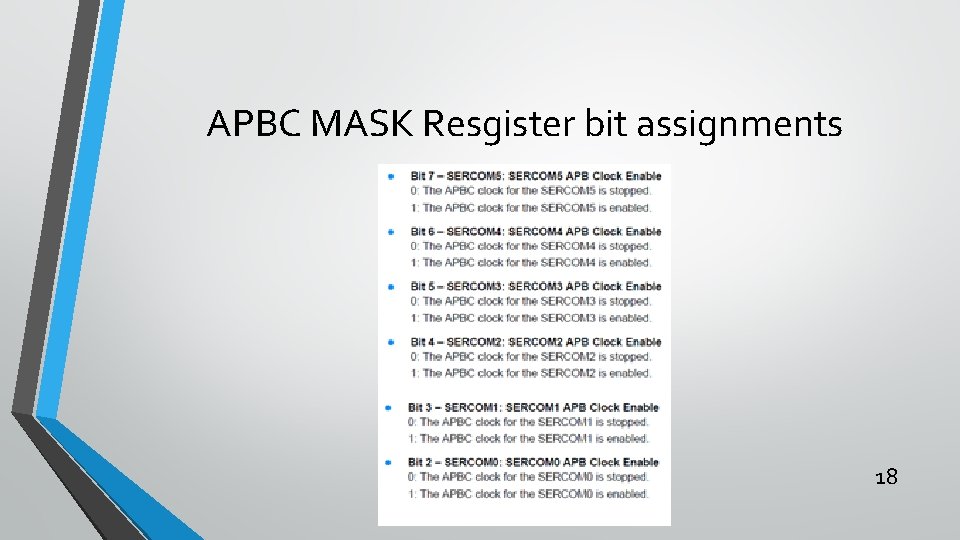

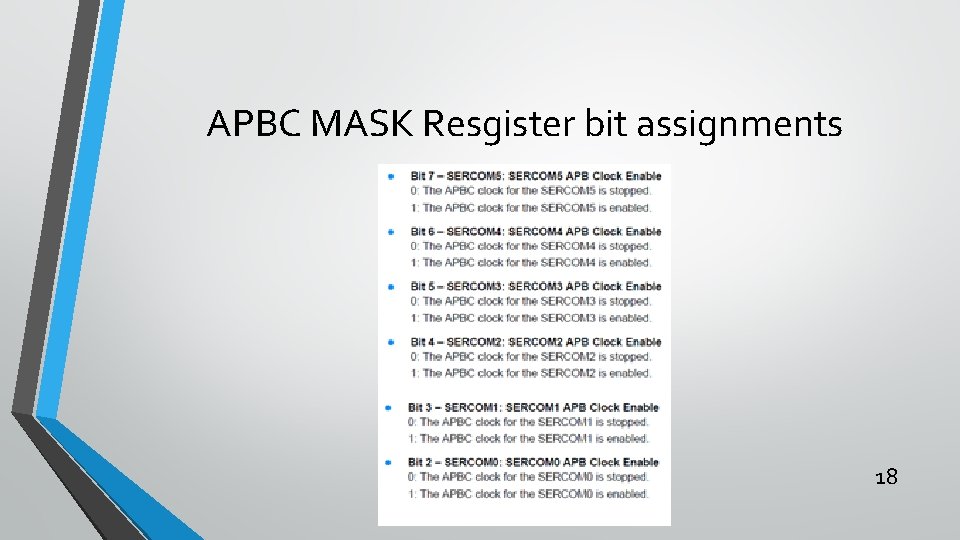

APBC Clock Select Resgister bit assignment 19

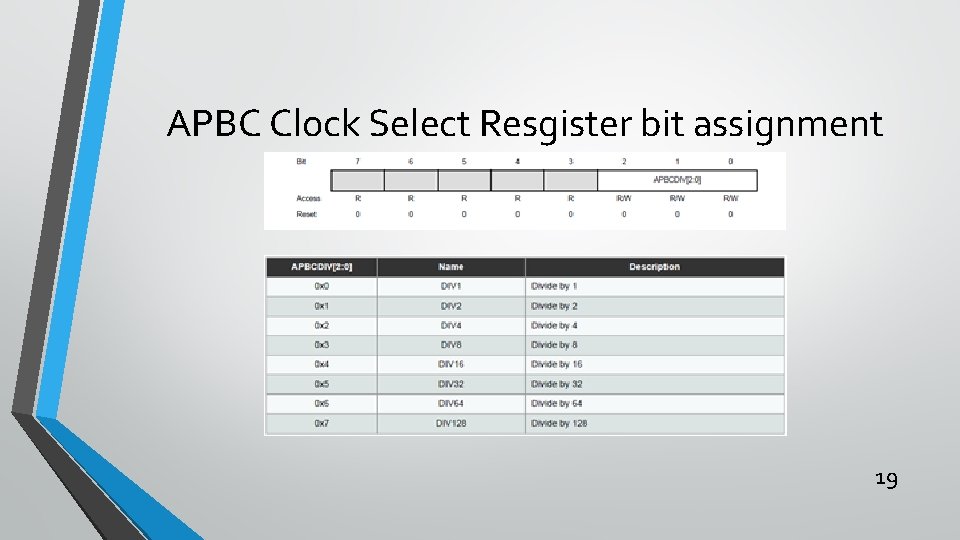

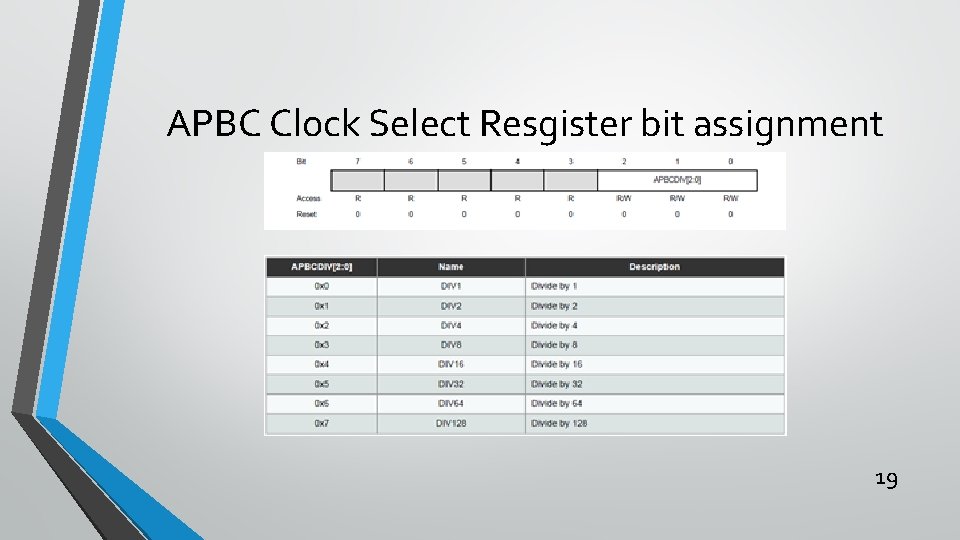

Generic Clock Control Resgister bit assignment 20

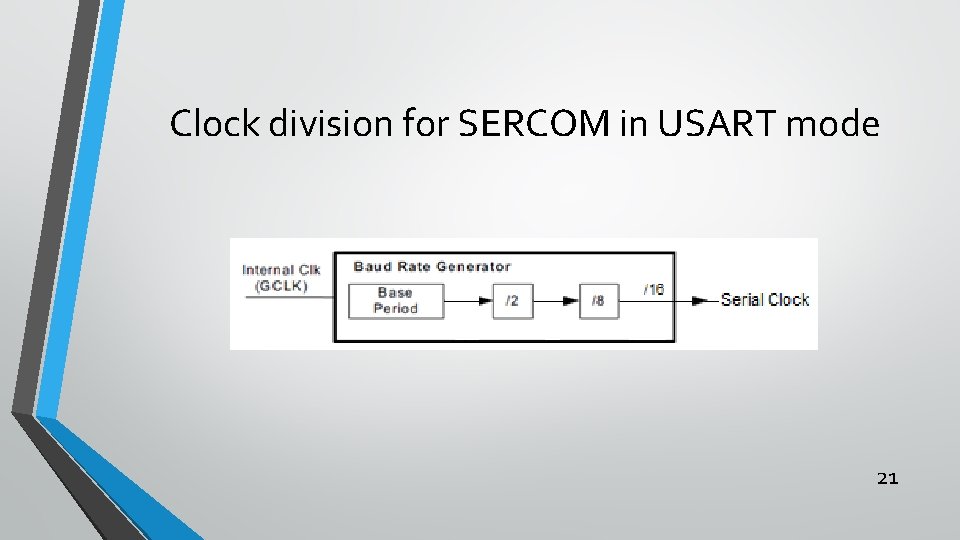

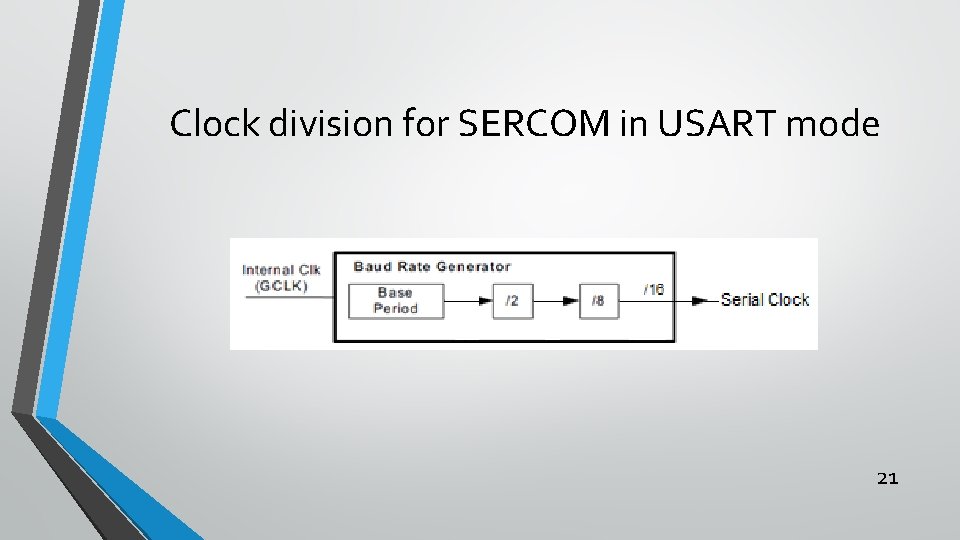

Clock division for SERCOM in USART mode 21

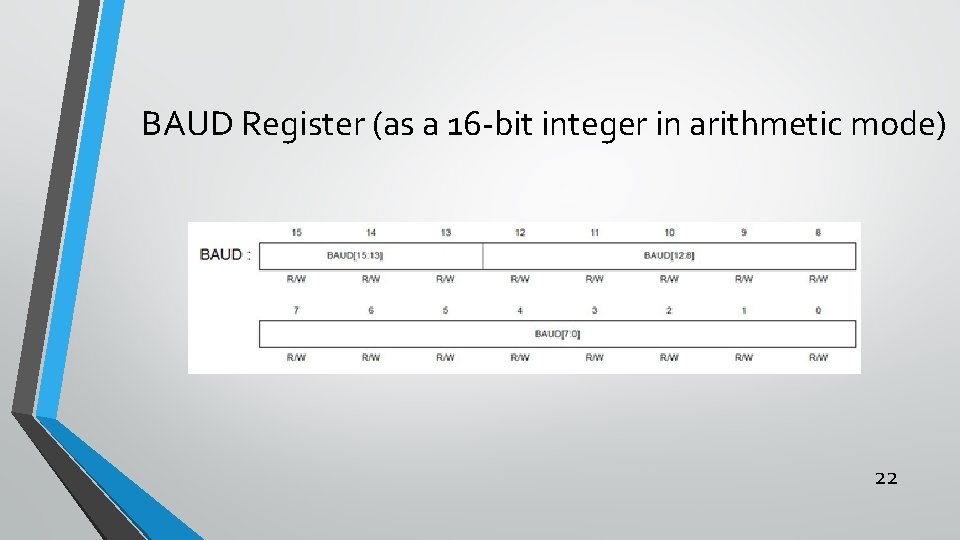

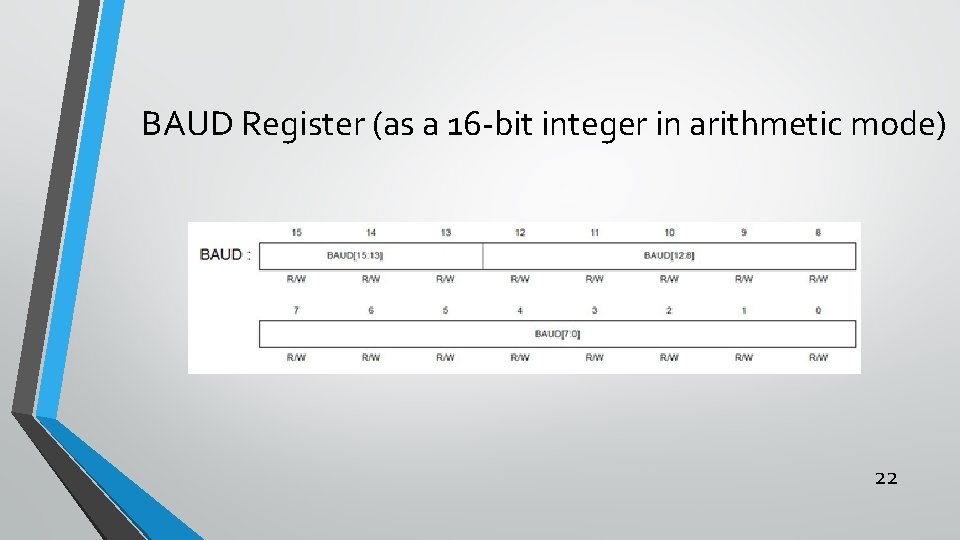

BAUD Register (as a 16 -bit integer in arithmetic mode) 22

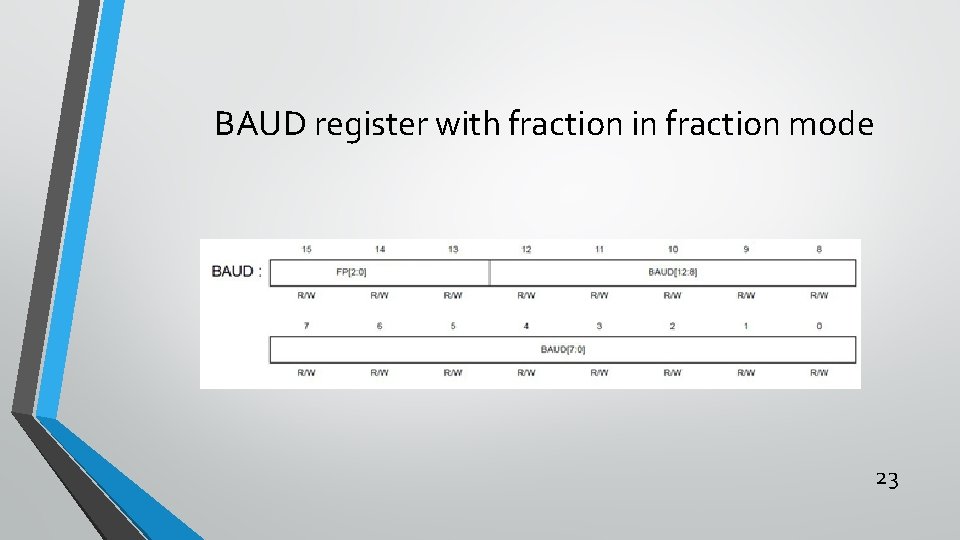

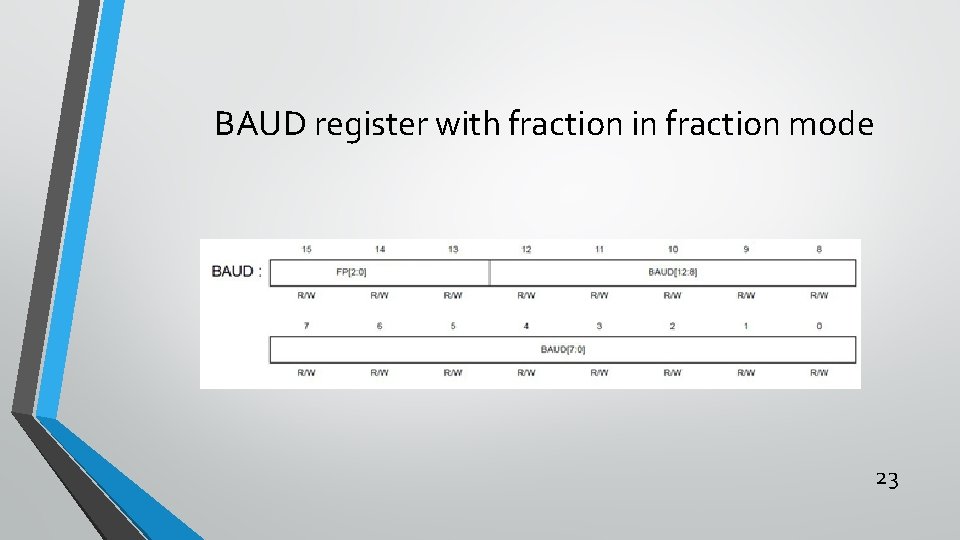

BAUD register with fraction in fraction mode 23

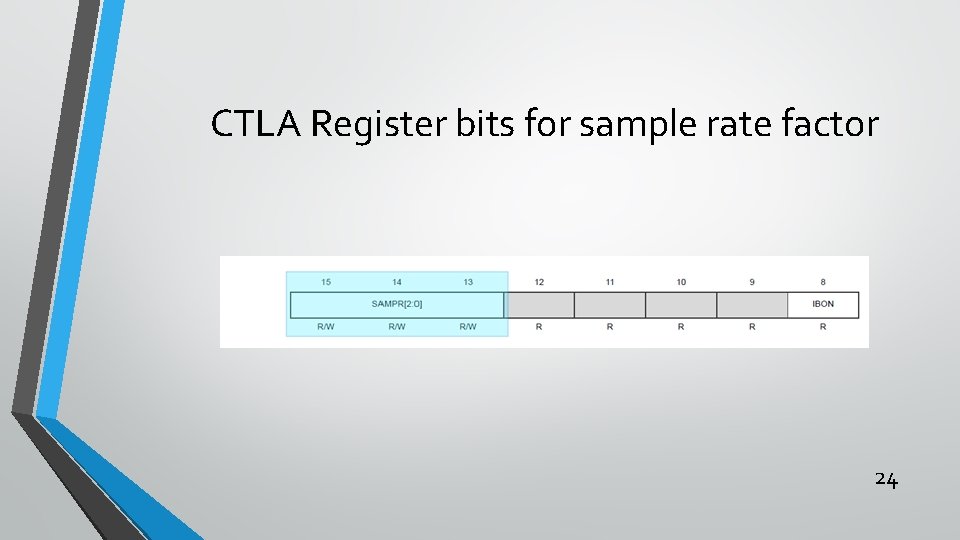

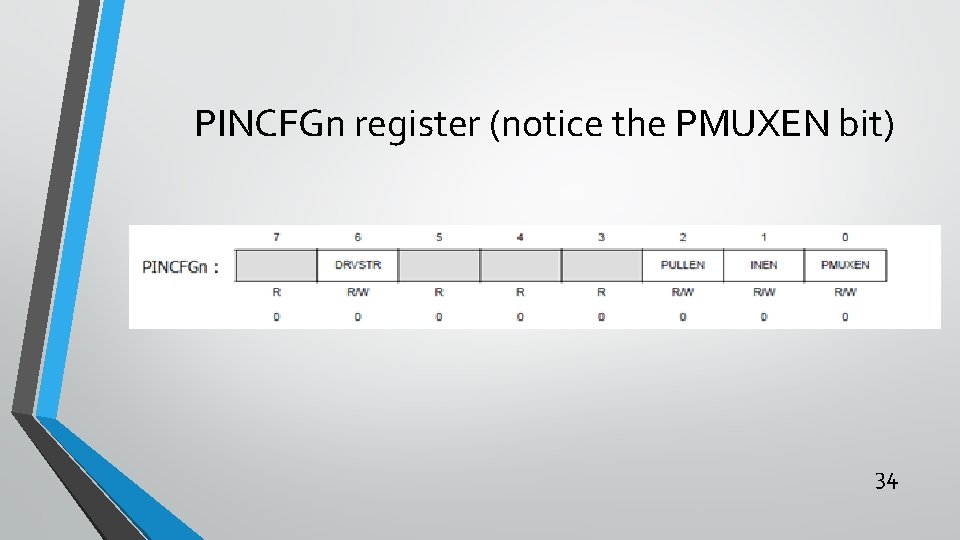

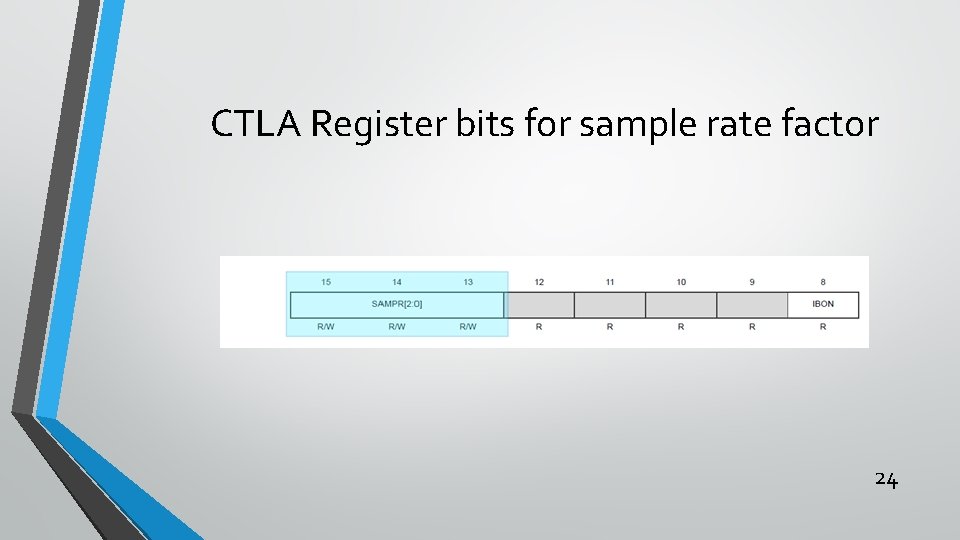

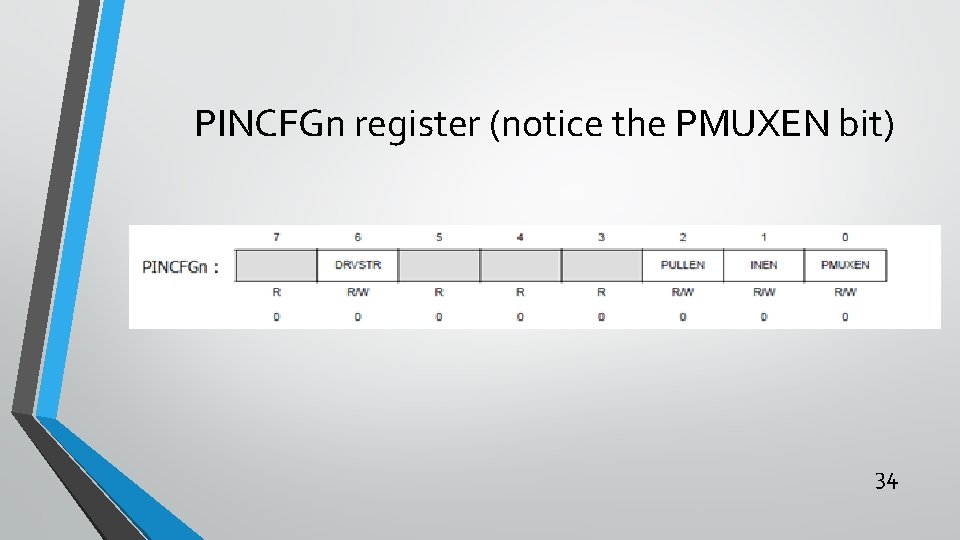

CTLA Register bits for sample rate factor 24

![Sample rate options in CTRLA register SAMPR2 0 Descriptions 0 x 0 16 x Sample rate options in CTRLA register SAMPR[2: 0] Descriptions 0 x 0 16 x](https://slidetodoc.com/presentation_image_h/872b42f7d2e1667ae0dd2a0bb4a8d61a/image-25.jpg)

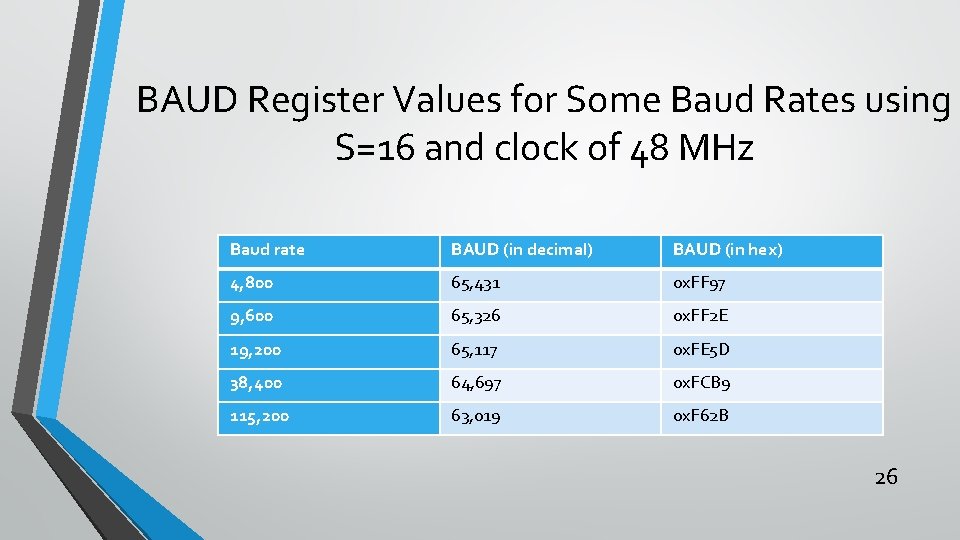

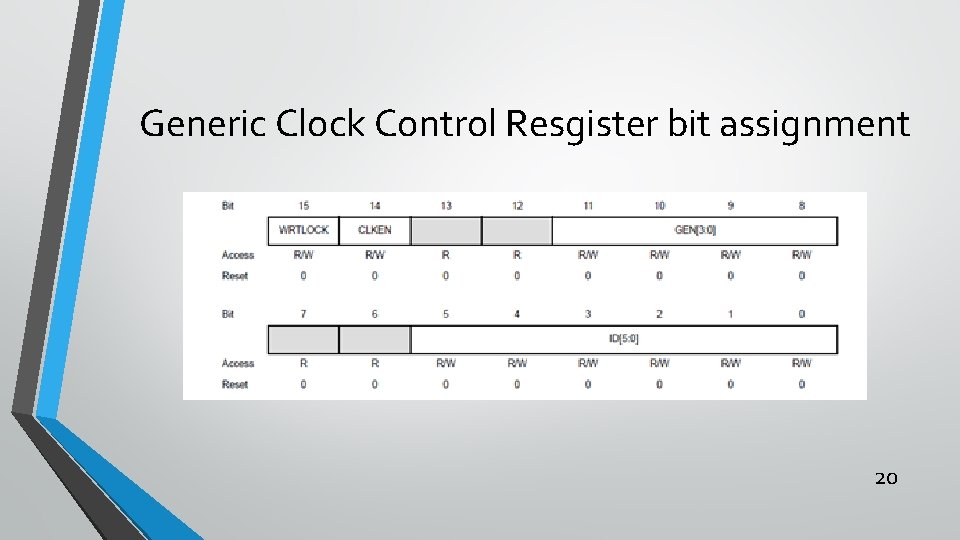

Sample rate options in CTRLA register SAMPR[2: 0] Descriptions 0 x 0 16 x over-sampling using arithmetic baud rate generation. 0 x 1 16 x over-sampling using fractional baud rate generation. 0 x 2 8 x over-sampling using arithmetic baud rate generation. 0 x 3 8 x over-sampling using fractional baud rate generation. 0 x 4 3 x over-sampling using arithmetic baud rate generation. 0 x 5 -0 x 7 Reserved 25

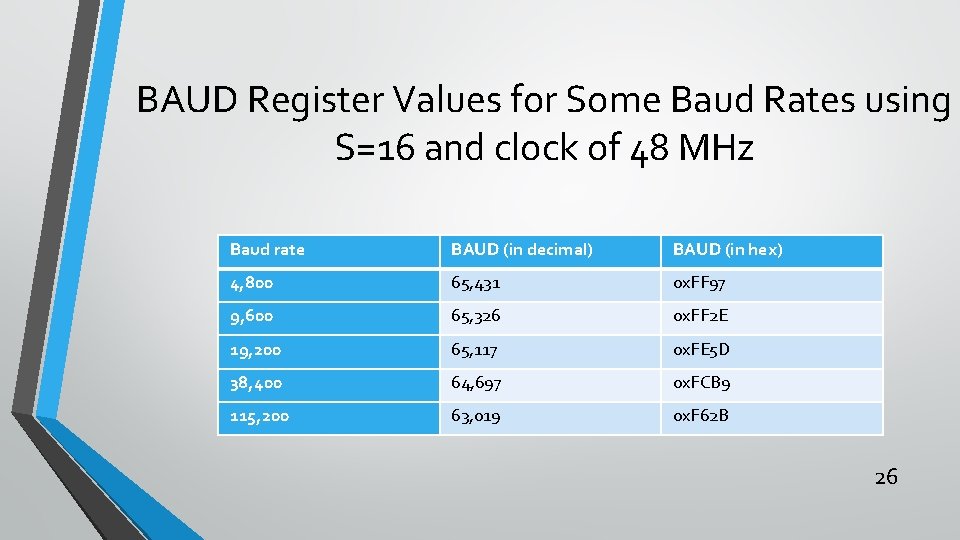

BAUD Register Values for Some Baud Rates using S=16 and clock of 48 MHz Baud rate BAUD (in decimal) BAUD (in hex) 4, 800 65, 431 0 x. FF 97 9, 600 65, 326 0 x. FF 2 E 19, 200 65, 117 0 x. FE 5 D 38, 400 64, 697 0 x. FCB 9 115, 200 63, 019 0 x. F 62 B 26

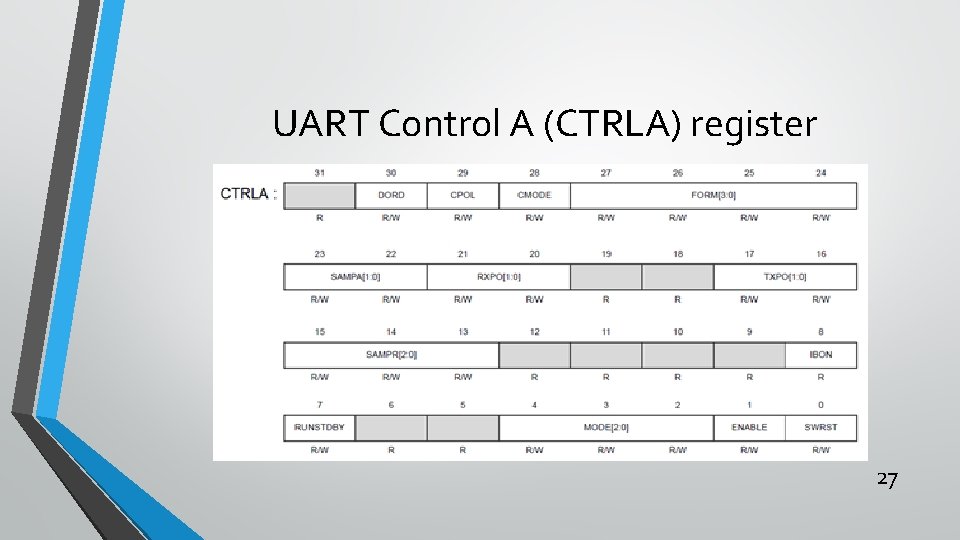

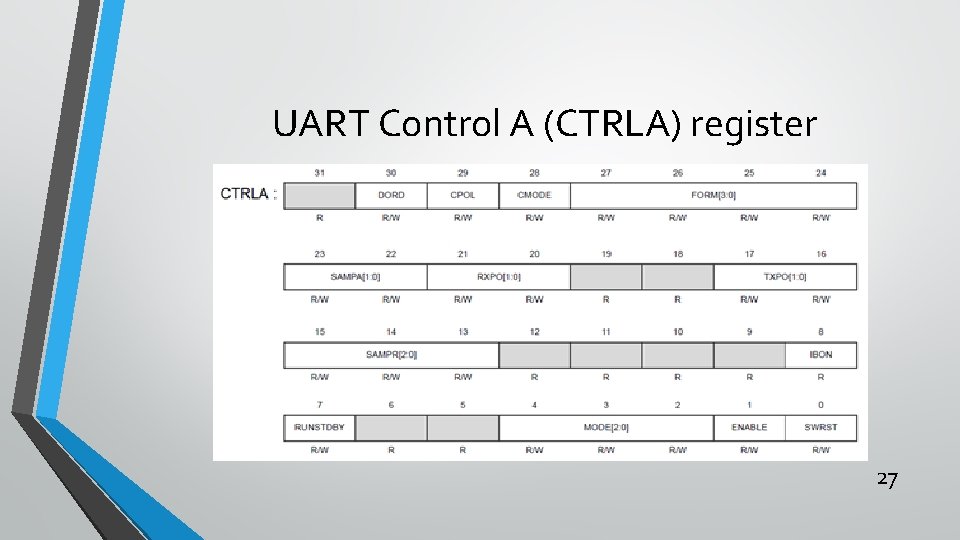

UART Control A (CTRLA) register 27

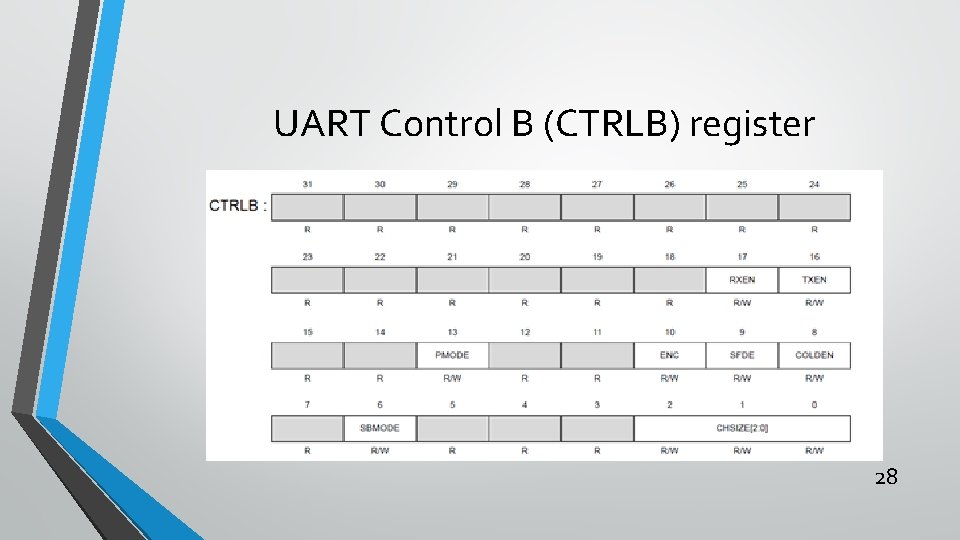

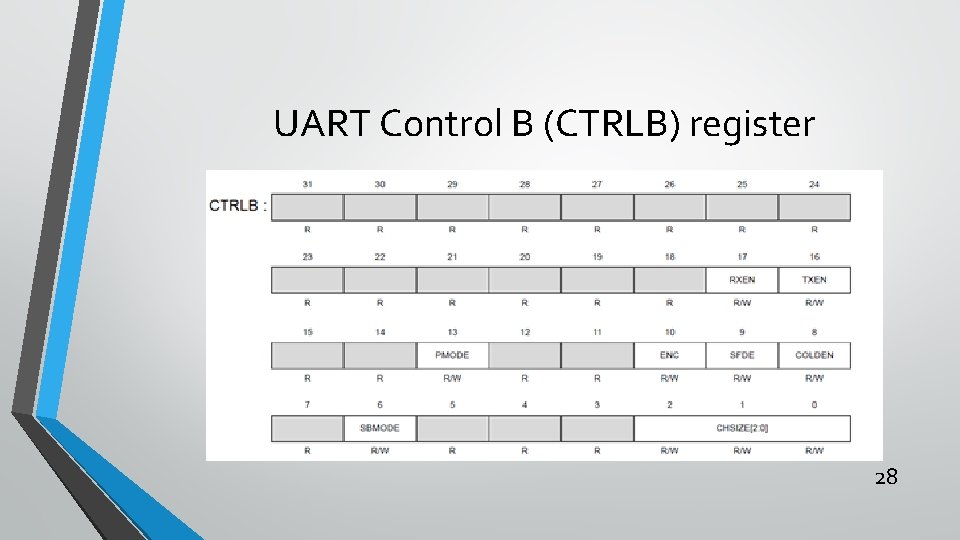

UART Control B (CTRLB) register 28

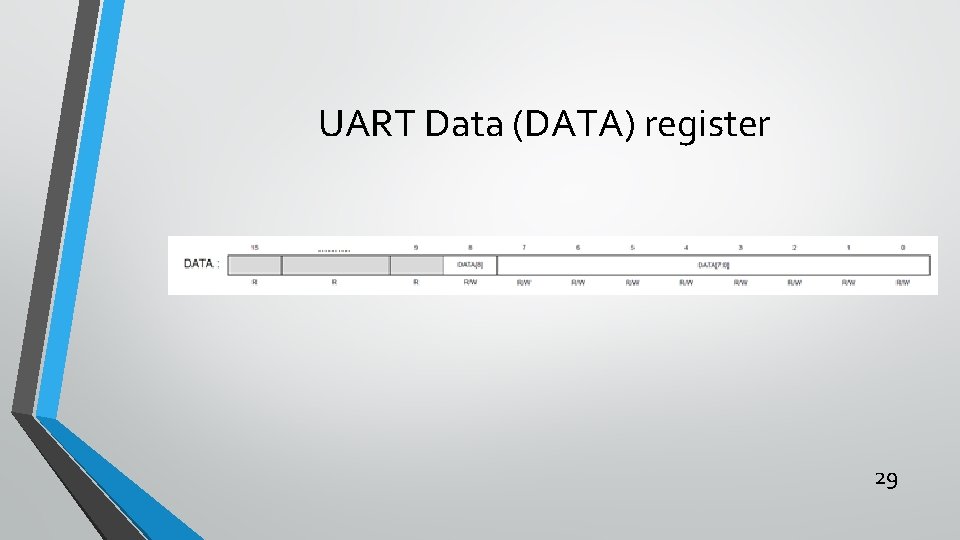

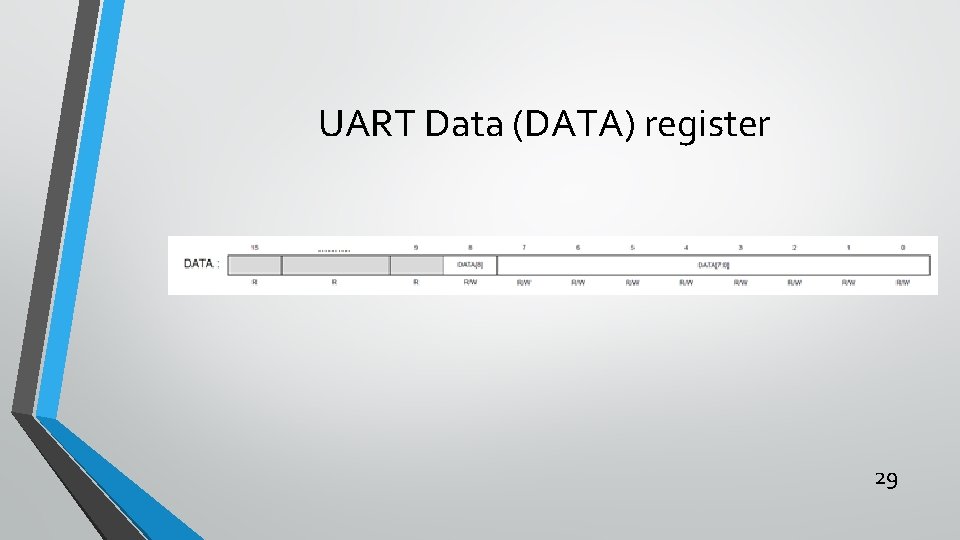

UART Data (DATA) register 29

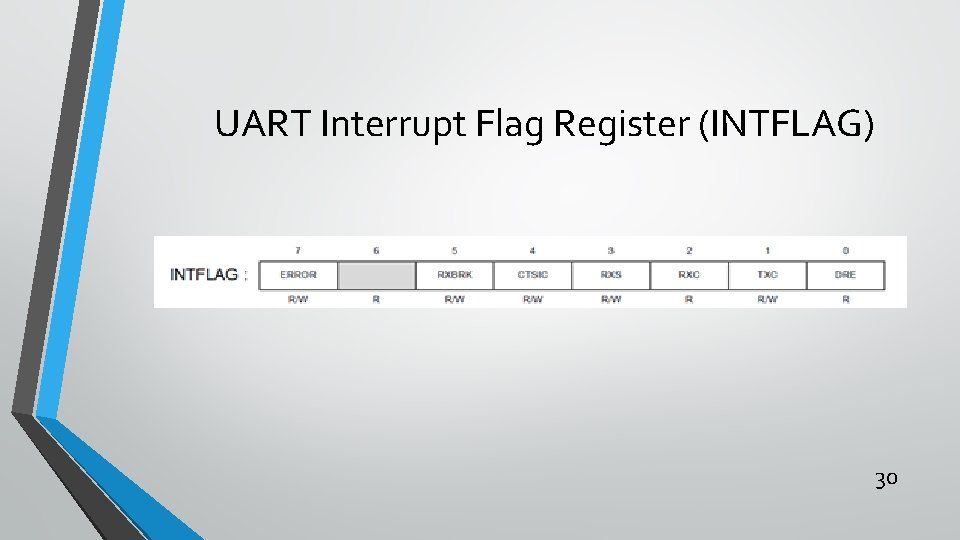

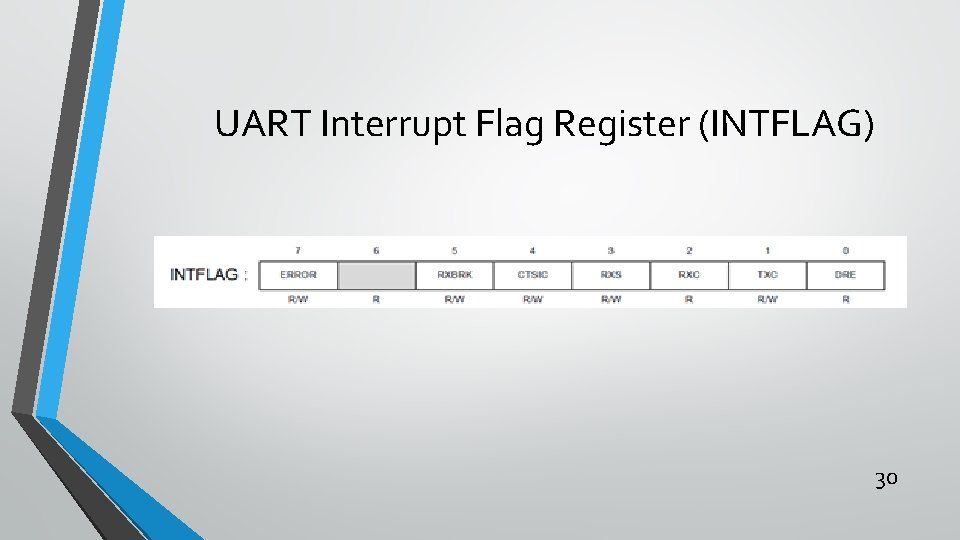

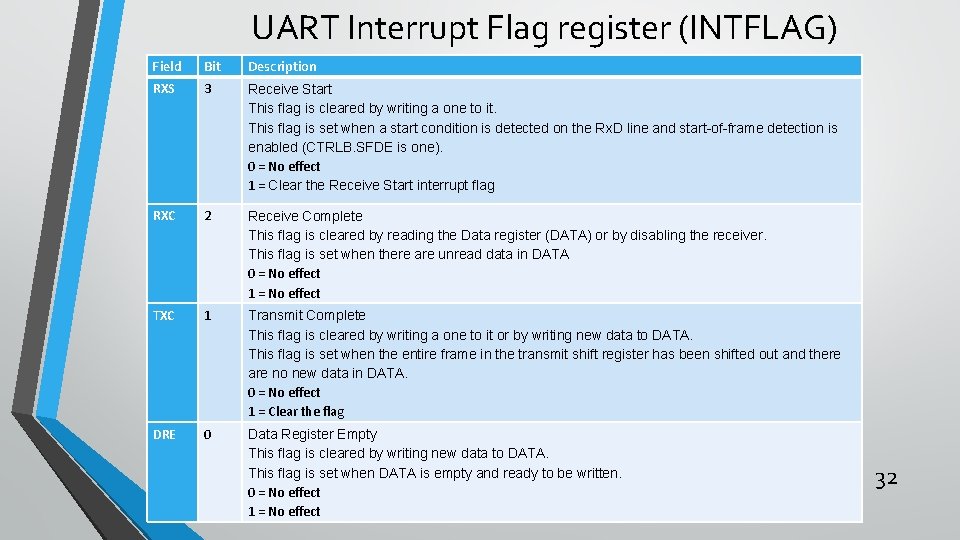

UART Interrupt Flag Register (INTFLAG) 30

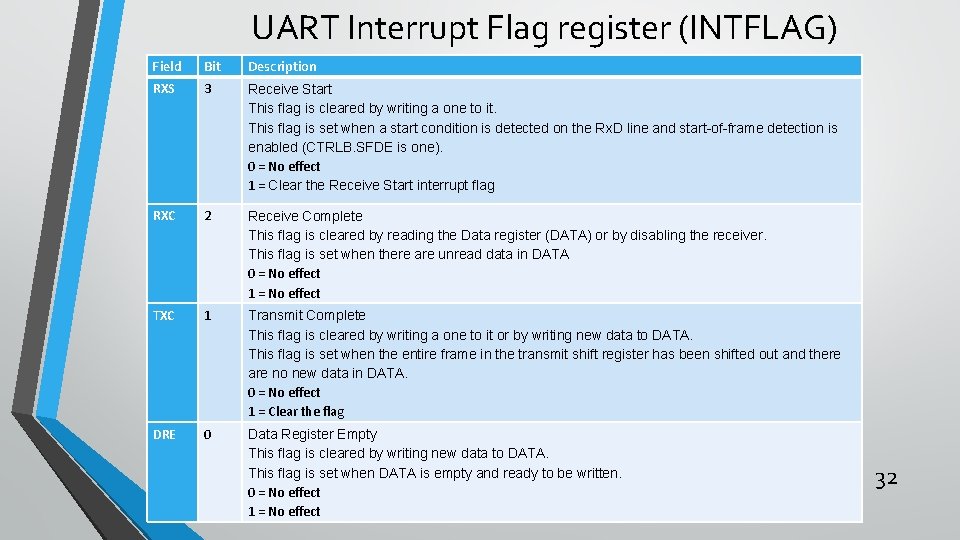

UART Interrupt Flag register (INTFLAG) Field Bit Description ERROR 7 Error This flag is cleared by writing a one to it. This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. Errors that will set this flag are COLL, ISF, BUFOVF, FERR, and PERR. 0 = No effect 1 = Clear the flag 6 Reserved RXBRK 5 Receive Break This flag is cleared by writing a one to it. This flag is set when auto-baud is enabled (CTRLA. FORM) and a break character is received. 0 = No effect 1 = Clear the flag CTSIC 4 Clear to Send Input Change This flag is cleared by writing a one to it. This flag is set when a change is detected on the CTS pin. 0 = No effect 1 = Clear the flag 31

UART Interrupt Flag register (INTFLAG) Field Bit Description RXS 3 Receive Start This flag is cleared by writing a one to it. This flag is set when a start condition is detected on the Rx. D line and start-of-frame detection is enabled (CTRLB. SFDE is one). 0 = No effect 1 = Clear the Receive Start interrupt flag RXC 2 Receive Complete This flag is cleared by reading the Data register (DATA) or by disabling the receiver. This flag is set when there are unread data in DATA 0 = No effect 1 = No effect TXC 1 Transmit Complete This flag is cleared by writing a one to it or by writing new data to DATA. This flag is set when the entire frame in the transmit shift register has been shifted out and there are no new data in DATA. 0 = No effect 1 = Clear the flag DRE 0 Data Register Empty This flag is cleared by writing new data to DATA. This flag is set when DATA is empty and ready to be written. 0 = No effect 1 = No effect 32

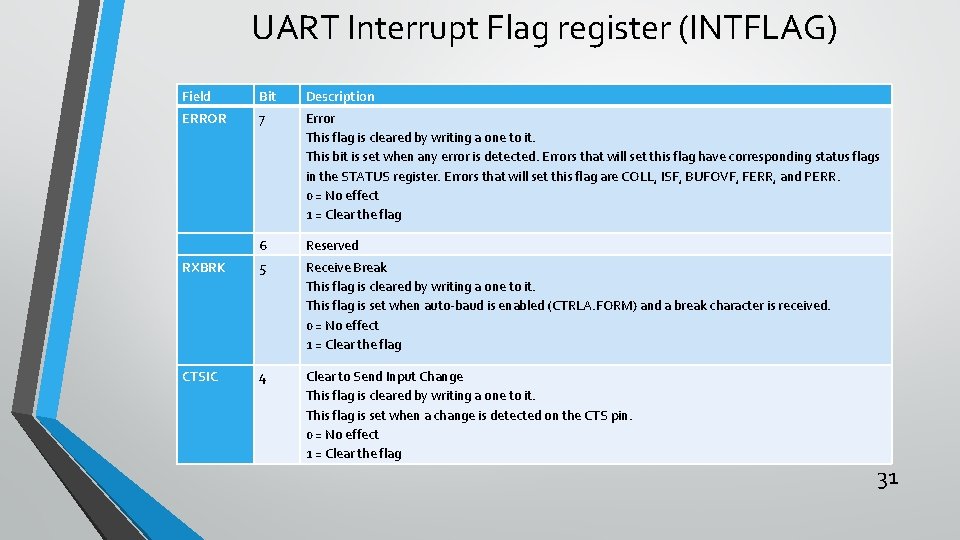

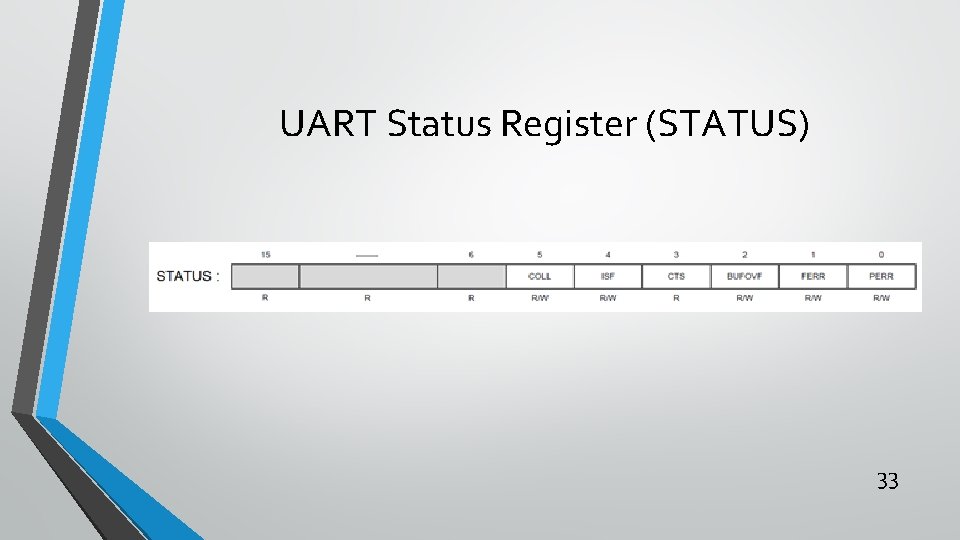

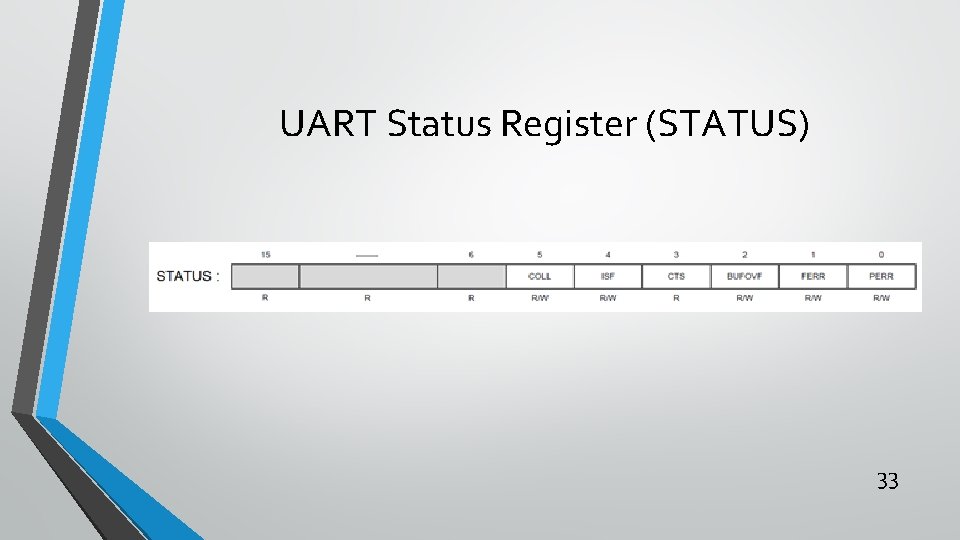

UART Status Register (STATUS) 33

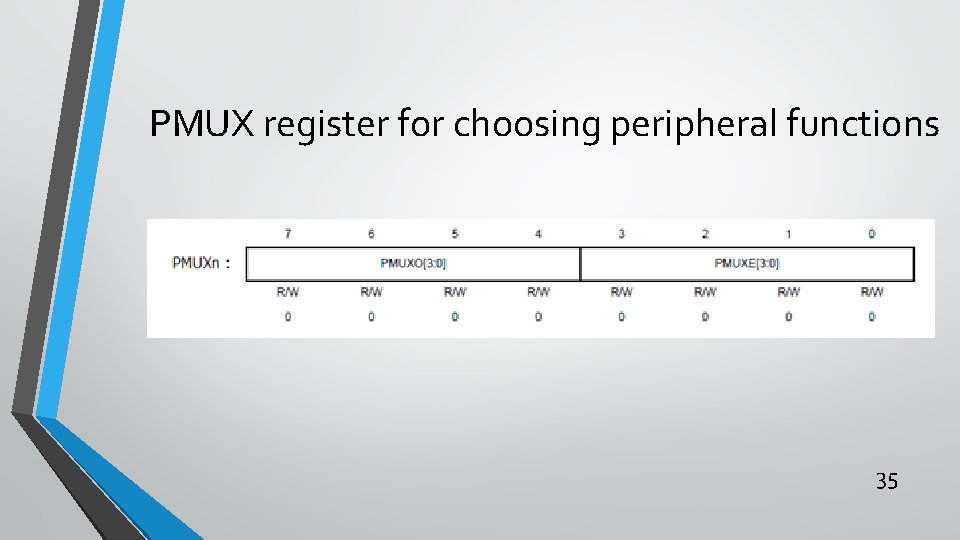

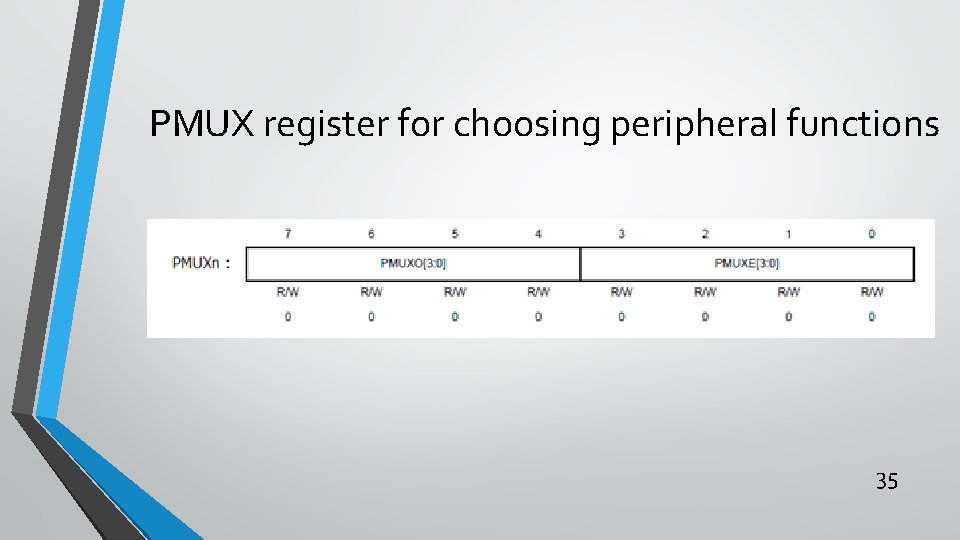

PINCFGn register (notice the PMUXEN bit) 34

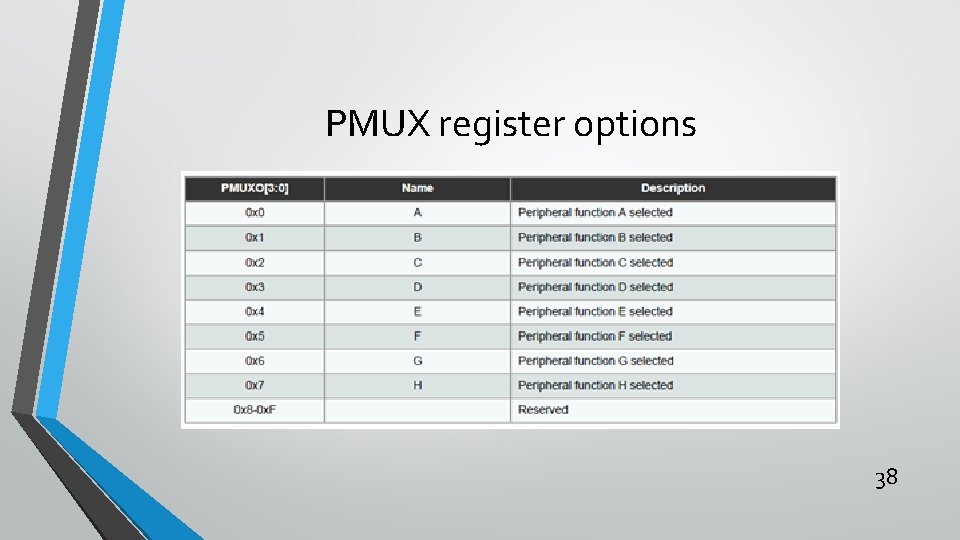

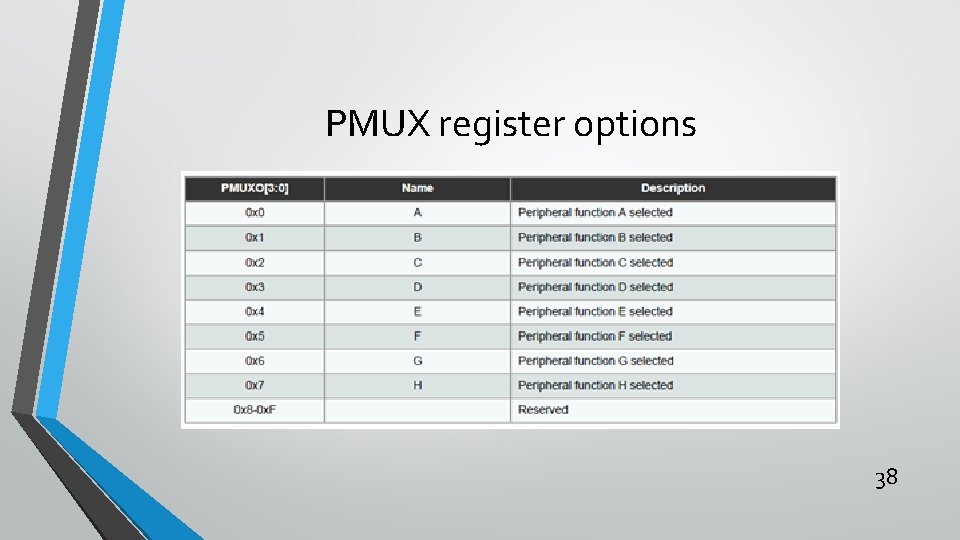

PMUX register for choosing peripheral functions 35

![SAMD 2 x Signals Used for UART See CTRLA register TXPO1 0 PAD RXPO1 SAMD 2 x Signals Used for UART (See CTRLA register) TXPO[1: 0] PAD RXPO[1:](https://slidetodoc.com/presentation_image_h/872b42f7d2e1667ae0dd2a0bb4a8d61a/image-36.jpg)

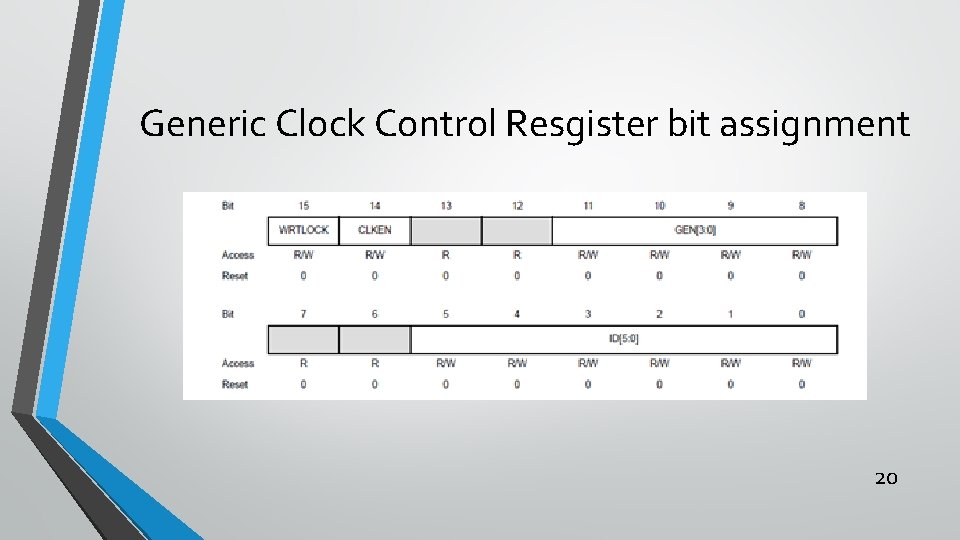

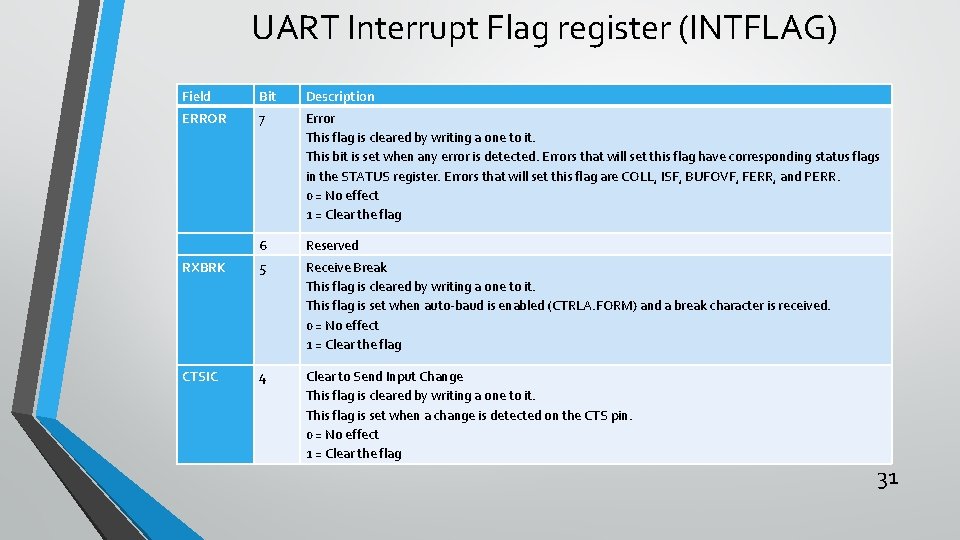

SAMD 2 x Signals Used for UART (See CTRLA register) TXPO[1: 0] PAD RXPO[1: 0] PAD 0 x 0 PAD[0] 0 x 1 PAD[2] 0 x 1 PAD[1] 0 x 2 PAD[0] 0 x 2 PAD[2] 0 x 3 Reserved 0 x 3 PAD[3] 36

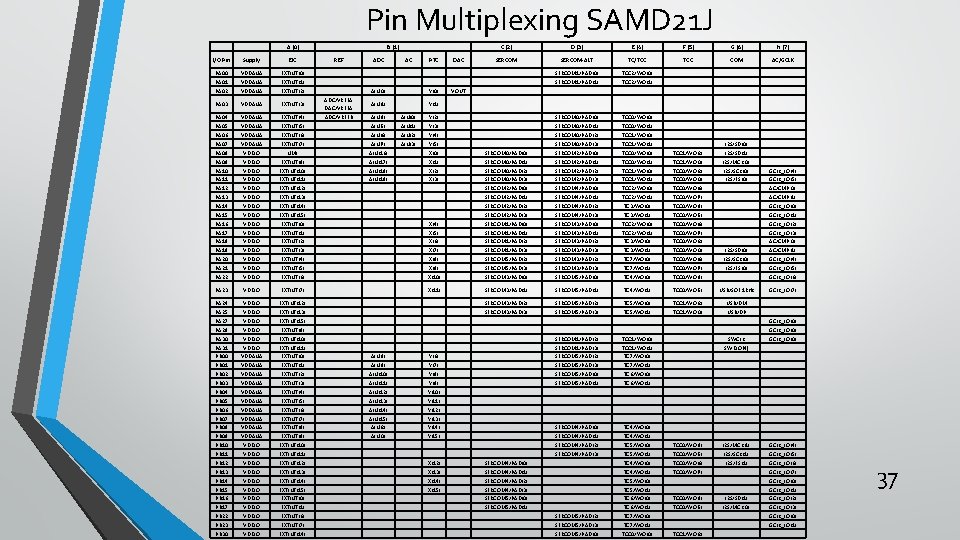

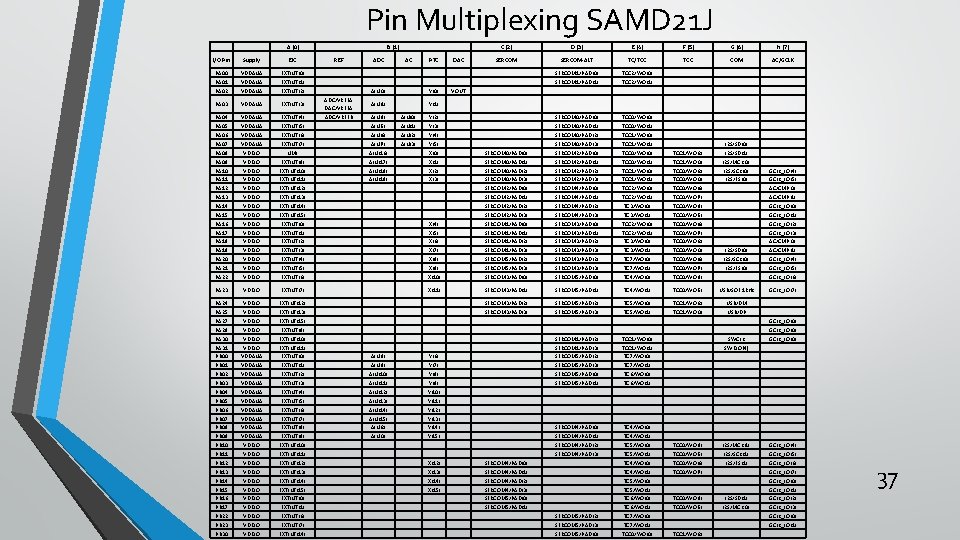

Pin Multiplexing SAMD 21 J A (0) C (2) D (3) E (4) F (5) G (6) H (7) I/O Pin Supply EIC REF ADC B (1) AC PTC DAC SERCOM-ALT TC/TCC COM AC/GCLK PA 00 PA 01 PA 02 VDDANA EXTINT[0] EXTINT[1] EXTINT[2] AIN[0] Y[0] VOUT SERCOM 1/PAD[0] SERCOM 1/PAD[1] TCC 2/WO[0] TCC 2/WO[1] PA 03 VDDANA EXTINT[3] ADC/VREFA DAC/VREFA AIN[1] Y[1] PA 04 PA 05 PA 06 PA 07 PA 08 PA 09 PA 10 PA 11 PA 12 PA 13 PA 14 PA 15 PA 16 PA 17 PA 18 PA 19 PA 20 PA 21 PA 22 VDDANA VDDIO VDDIO VDDIO VDDIO EXTINT[4] EXTINT[5] EXTINT[6] EXTINT[7] NMI EXTINT[9] EXTINT[10] EXTINT[11] EXTINT[12] EXTINT[13] EXTINT[14] EXTINT[15] EXTINT[0] EXTINT[1] EXTINT[2] EXTINT[3] EXTINT[4] EXTINT[5] EXTINT[6] ADC/VREFB AIN[4] AIN[5] AIN[6] AIN[7] AIN[16] AIN[17] AIN[18] AIN[19] AIN[0] AIN[1] AIN[2] AIN[3] Y[2] Y[3] Y[4] Y[5] X[0] X[1] X[2] X[3] X[4] X[5] X[6] X[7] X[8] X[9] X[10] SERCOM 0/PAD[0] SERCOM 0/PAD[1] SERCOM 0/PAD[2] SERCOM 0/PAD[3] SERCOM 2/PAD[0] SERCOM 2/PAD[1] SERCOM 2/PAD[2] SERCOM 2/PAD[3] SERCOM 1/PAD[0] SERCOM 1/PAD[1] SERCOM 1/PAD[2] SERCOM 1/PAD[3] SERCOM 5/PAD[2] SERCOM 5/PAD[3] SERCOM 3/PAD[0] SERCOM 0/PAD[1] SERCOM 0/PAD[2] SERCOM 0/PAD[3] SERCOM 2/PAD[0] SERCOM 2/PAD[1] SERCOM 2/PAD[2] SERCOM 2/PAD[3] SERCOM 4/PAD[0] SERCOM 4/PAD[1] SERCOM 4/PAD[2] SERCOM 4/PAD[3] SERCOM 3/PAD[0] SERCOM 3/PAD[1] SERCOM 3/PAD[2] SERCOM 3/PAD[3] SERCOM 5/PAD[0] TCC 0/WO[1] TCC 1/WO[0] TCC 1/WO[1] TCC 0/WO[0] TCC 0/WO[1] TCC 1/WO[0] TCC 1/WO[1] TCC 2/WO[0] TCC 2/WO[1] TC 3/WO[0] TC 3/WO[1] TC 7/WO[0] TC 7/WO[1] TC 4/WO[0] TCC 1/WO[2] TCC 1/WO[3] TCC 0/WO[2] TCC 0/WO[3] TCC 0/WO[6] TCC 0/WO[7] TCC 0/WO[4] TCC 0/WO[5] TCC 0/WO[6] TCC 0/WO[7] TCC 0/WO[2] TCC 0/WO[3] TCC 0/WO[6] TCC 0/WO[7] TCC 0/WO[4] I 2 S/SD[0] I 2 S/SD[1] I 2 S/MCK[0] I 2 S/SCK[0] I 2 S/FS[0] I 2 S/SD[0] I 2 S/SCK[0] I 2 S/FS[0] GCLK_IO[4] GCLK_IO[5] AC/CMP[0] AC/CMP[1] GCLK_IO[0] GCLK_IO[1] GCLK_IO[2] GCLK_IO[3] AC/CMP[0] AC/CMP[1] GCLK_IO[4] GCLK_IO[5] GCLK_IO[6] PA 23 VDDIO EXTINT[7] X[11] SERCOM 3/PAD[1] SERCOM 5/PAD[1] TC 4/WO[1] TCC 0/WO[5] USB/SOF 1 k. Hz GCLK_IO[7] PA 24 PA 25 PA 27 PA 28 PA 30 PA 31 PB 00 PB 01 PB 02 PB 03 PB 04 PB 05 PB 06 PB 07 PB 08 PB 09 PB 10 PB 11 PB 12 PB 13 PB 14 PB 15 PB 16 PB 17 PB 22 PB 23 PB 30 VDDIO VDDIO VDDANA VDDANA VDDANA VDDIO VDDIO VDDIO EXTINT[12] EXTINT[13] EXTINT[15] EXTINT[8] EXTINT[10] EXTINT[11] EXTINT[0] EXTINT[1] EXTINT[2] EXTINT[3] EXTINT[4] EXTINT[5] EXTINT[6] EXTINT[7] EXTINT[8] EXTINT[9] EXTINT[10] EXTINT[11] EXTINT[12] EXTINT[13] EXTINT[14] EXTINT[15] EXTINT[0] EXTINT[1] EXTINT[6] EXTINT[7] EXTINT[14] AIN[8] AIN[9] AIN[10] AIN[11] AIN[12] AIN[13] AIN[14] AIN[15] AIN[2] AIN[3] Y[6] Y[7] Y[8] Y[9] Y[10] Y[11] Y[12] Y[13] Y[14] Y[15] X[12] X[13] X[14] X[15] SERCOM 3/PAD[2] SERCOM 3/PAD[3] SERCOM 4/PAD[0] SERCOM 4/PAD[1] SERCOM 4/PAD[2] SERCOM 4/PAD[3] SERCOM 5/PAD[0] SERCOM 5/PAD[1] SERCOM 5/PAD[2] SERCOM 5/PAD[3] SERCOM 1/PAD[2] SERCOM 1/PAD[3] SERCOM 5/PAD[2] SERCOM 5/PAD[3] SERCOM 5/PAD[0] SERCOM 5/PAD[1] SERCOM 4/PAD[0] SERCOM 4/PAD[1] SERCOM 4/PAD[2] SERCOM 4/PAD[3] SERCOM 5/PAD[2] SERCOM 5/PAD[3] SERCOM 5/PAD[0] TC 5/WO[1] TCC 1/WO[0] TCC 1/WO[1] TC 7/WO[0] TC 7/WO[1] TC 6/WO[0] TC 6/WO[1] TC 4/WO[0] TC 4/WO[1] TC 5/WO[0] TC 5/WO[1] TC 6/WO[0] TC 6/WO[1] TC 7/WO[0] TC 7/WO[1] TCC 0/WO[0] TCC 1/WO[2] TCC 1/WO[3] TCC 0/WO[4] TCC 0/WO[5] TCC 0/WO[6] TCC 0/WO[7] TCC 0/WO[4] TCC 0/WO[5] TCC 1/WO[2] USB/DM USB/DP SWCLK SWDIO(4) I 2 S/MCK[1] I 2 S/SCK[1] I 2 S/FS[1] I 2 S/SD[1] I 2 S/MCK[0] GCLK_IO[0] GCLK_IO[4] GCLK_IO[5] GCLK_IO[6] GCLK_IO[7] GCLK_IO[0] GCLK_IO[1] GCLK_IO[2] GCLK_IO[3] GCLK_IO[0] GCLK_IO[1] 37

PMUX register options 38