Serial Driver APIs Standard Serial API SPI HDLC

- Slides: 22

Serial Driver APIs Standard Serial API SPI HDLC API 1 -1

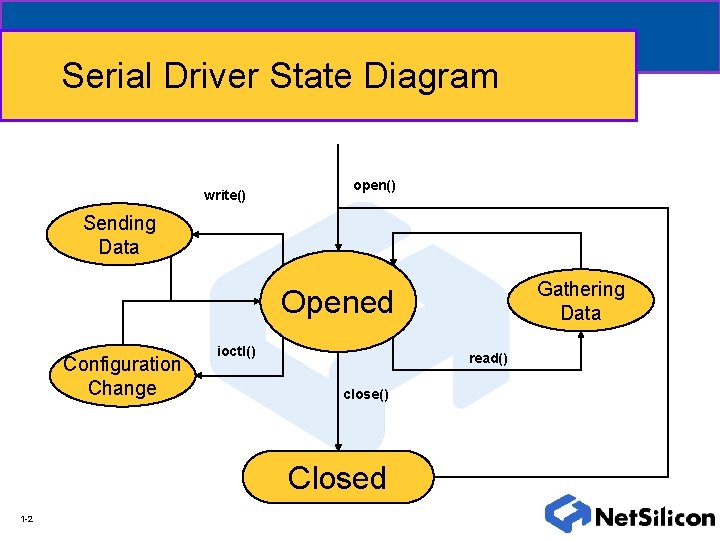

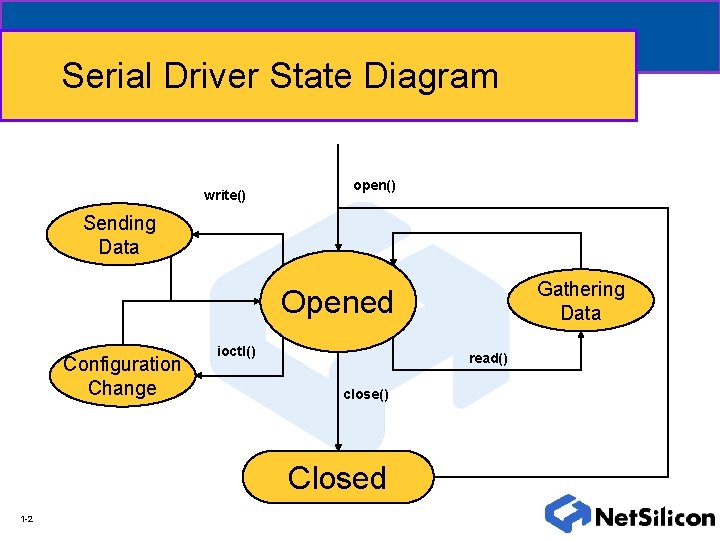

Serial Driver State Diagram write() open() Sending Data Gathering Data Opened Configuration Change ioctl() read() close() Closed 1 -2

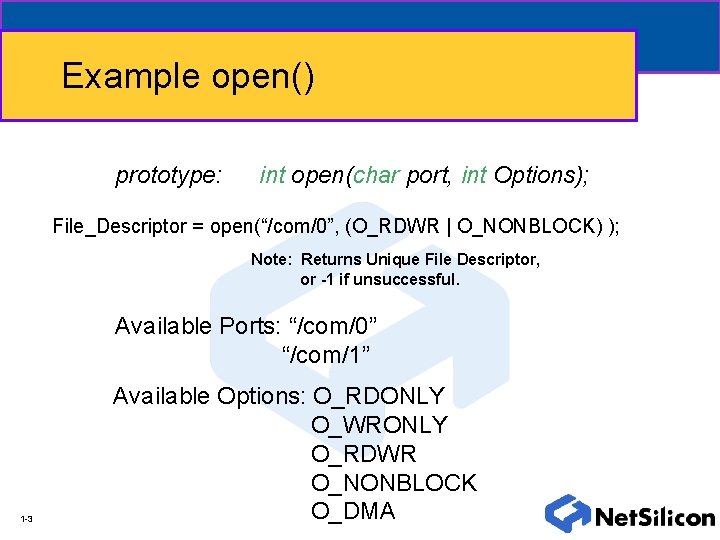

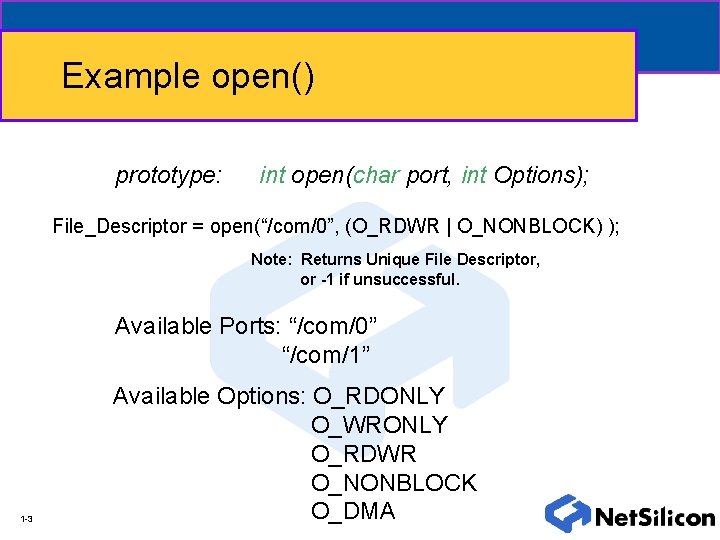

Example open() prototype: int open(char port, int Options); File_Descriptor = open(“/com/0”, (O_RDWR | O_NONBLOCK) ); Note: Returns Unique File Descriptor, or -1 if unsuccessful. Available Ports: “/com/0” “/com/1” 1 -3 Available Options: O_RDONLY O_WRONLY O_RDWR O_NONBLOCK O_DMA

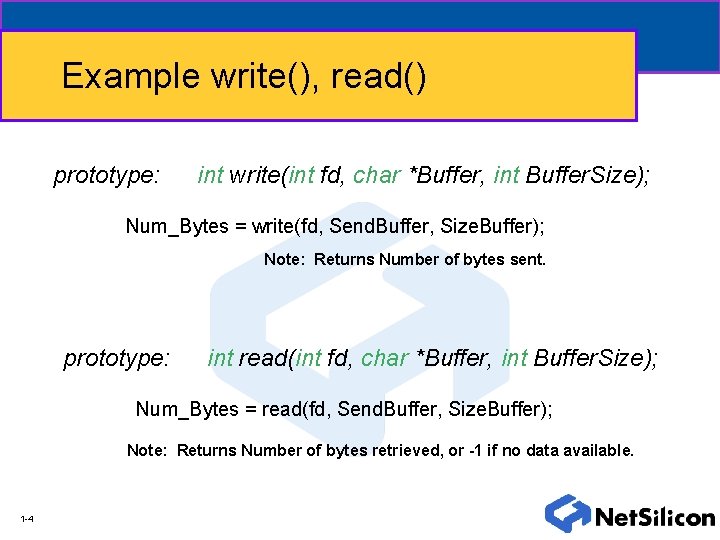

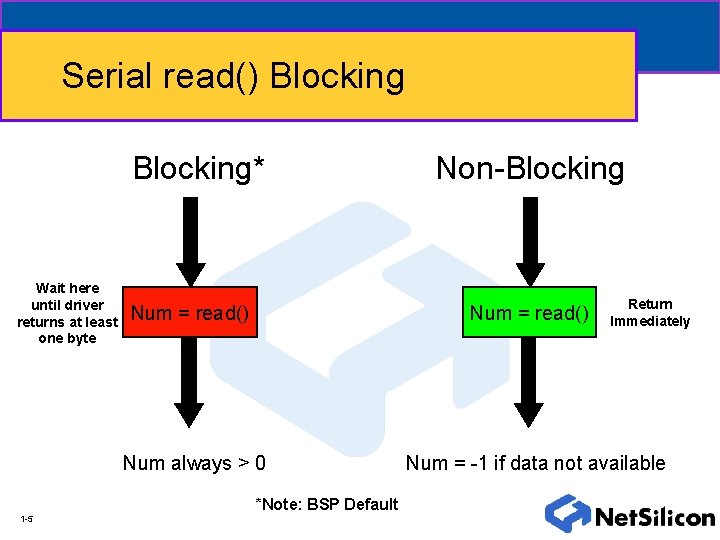

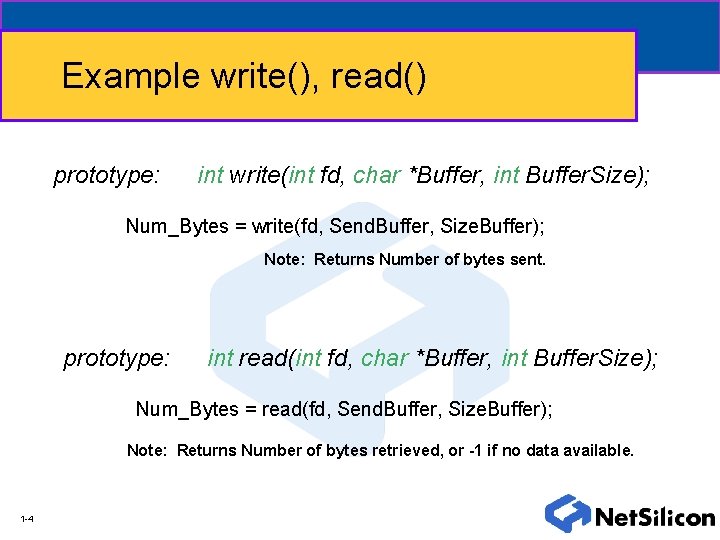

Example write(), read() prototype: int write(int fd, char *Buffer, int Buffer. Size); Num_Bytes = write(fd, Send. Buffer, Size. Buffer); Note: Returns Number of bytes sent. prototype: int read(int fd, char *Buffer, int Buffer. Size); Num_Bytes = read(fd, Send. Buffer, Size. Buffer); Note: Returns Number of bytes retrieved, or -1 if no data available. 1 -4

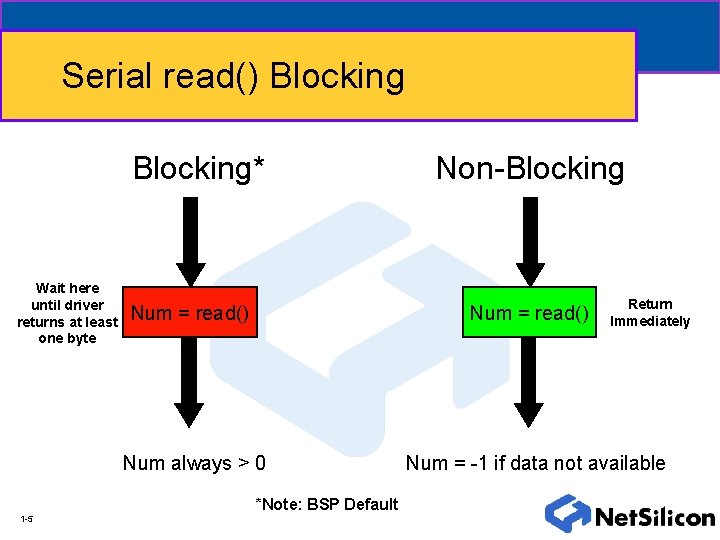

Serial read() Blocking* Wait here until driver returns at least one byte Num = read() Num always > 0 *Note: BSP Default 1 -5 Non-Blocking Return Immediately Num = -1 if data not available

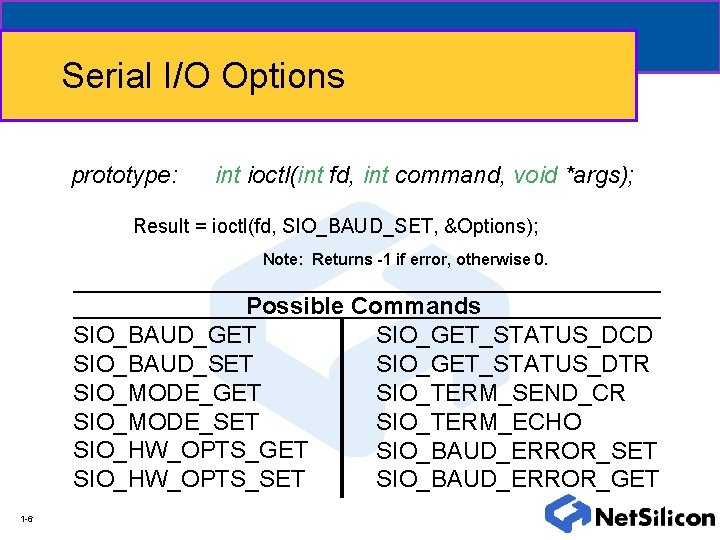

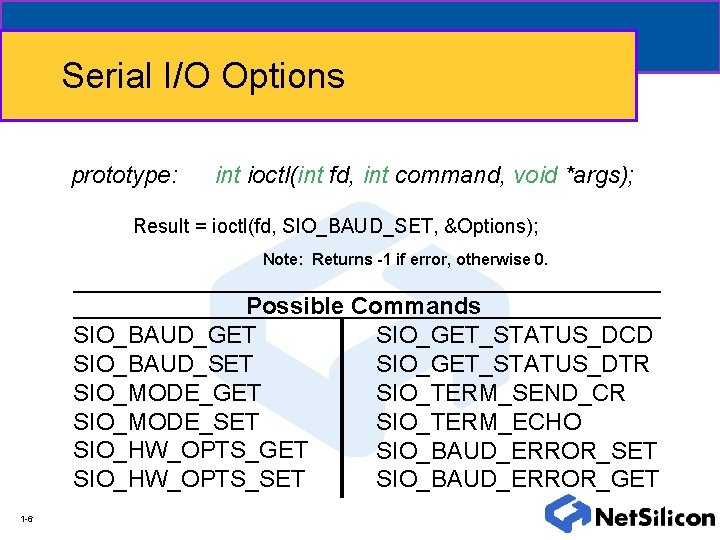

Serial I/O Options prototype: int ioctl(int fd, int command, void *args); Result = ioctl(fd, SIO_BAUD_SET, &Options); Note: Returns -1 if error, otherwise 0. Possible Commands SIO_BAUD_GET SIO_GET_STATUS_DCD SIO_BAUD_SET SIO_GET_STATUS_DTR SIO_MODE_GET SIO_TERM_SEND_CR SIO_MODE_SET SIO_TERM_ECHO SIO_HW_OPTS_GET SIO_BAUD_ERROR_SET SIO_HW_OPTS_SET SIO_BAUD_ERROR_GET 1 -6

Serial Driver for UART Serial Driver for standard UART MODE ONLY The following include files are required for the Serial Port APIs: • netosio. h • netos_serl. h The standard device driver APIs are supported. Use the open(), write(), read(), close(), and ioctl() functions to access the serial ports. Example: fd = open ("/com/1", (O_RDWR | O_ NONBLOCK)); 1 -7

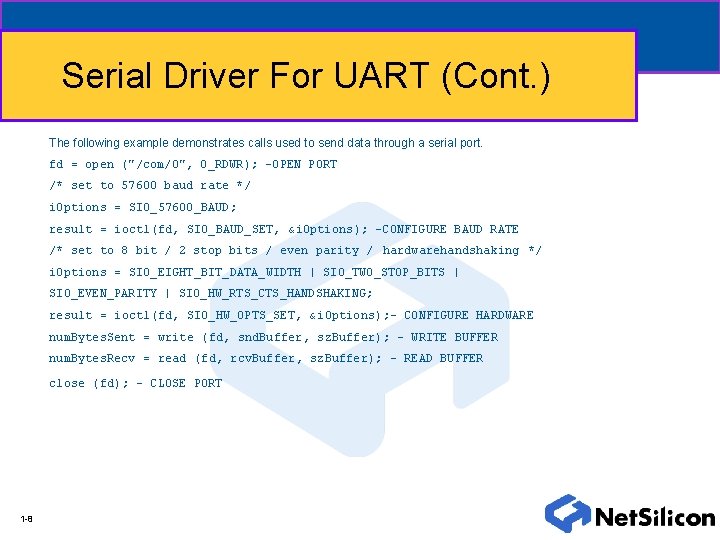

Serial Driver For UART (Cont. ) The following example demonstrates calls used to send data through a serial port. fd = open ("/com/0", O_RDWR); -OPEN PORT /* set to 57600 baud rate */ i. Options = SIO_57600_BAUD; result = ioctl(fd, SIO_BAUD_SET, &i. Options); -CONFIGURE BAUD RATE /* set to 8 bit / 2 stop bits / even parity / hardwarehandshaking */ i. Options = SIO_EIGHT_BIT_DATA_WIDTH | SIO_TWO_STOP_BITS | SIO_EVEN_PARITY | SIO_HW_RTS_CTS_HANDSHAKING; result = ioctl(fd, SIO_HW_OPTS_SET, &i. Options); - CONFIGURE HARDWARE num. Bytes. Sent = write (fd, snd. Buffer, sz. Buffer); - WRITE BUFFER num. Bytes. Recv = read (fd, rcv. Buffer, sz. Buffer); - READ BUFFER close (fd); - CLOSE PORT 1 -8

SPI - Serial Peripheral Interface • Communication between 2 Integrated Circuit • Full duplex, Synchronous interface • Physical Layer (TXD, RXD, CLK, EN*) • Character-oriented data channel • Shorter distances (6 inches) • Maximum port rate (SYSCLK/8) • SPI Driver 1 -9

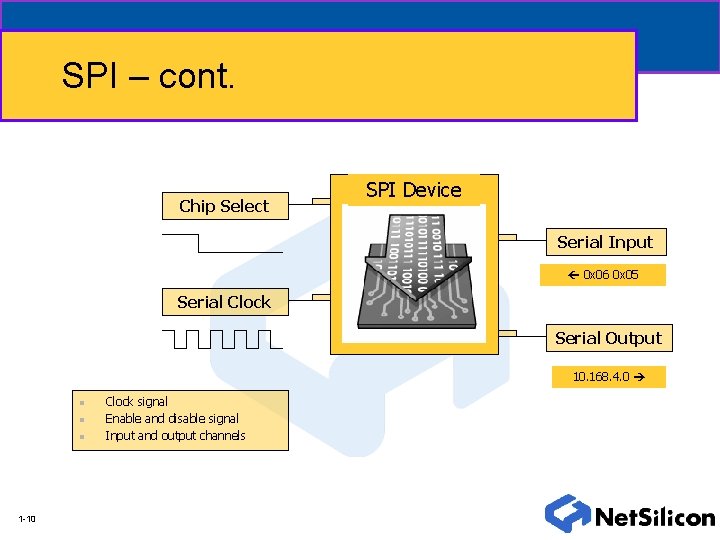

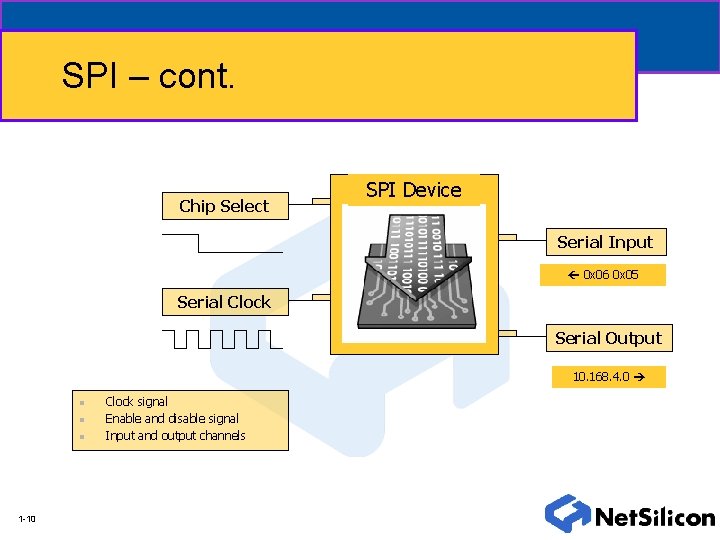

SPI – cont. Chip Select SPI Device Serial Input 0 x 06 0 x 05 Serial Clock Serial Output 10. 168. 4. 0 n n n 1 -10 Clock signal Enable and disable signal Input and output channels

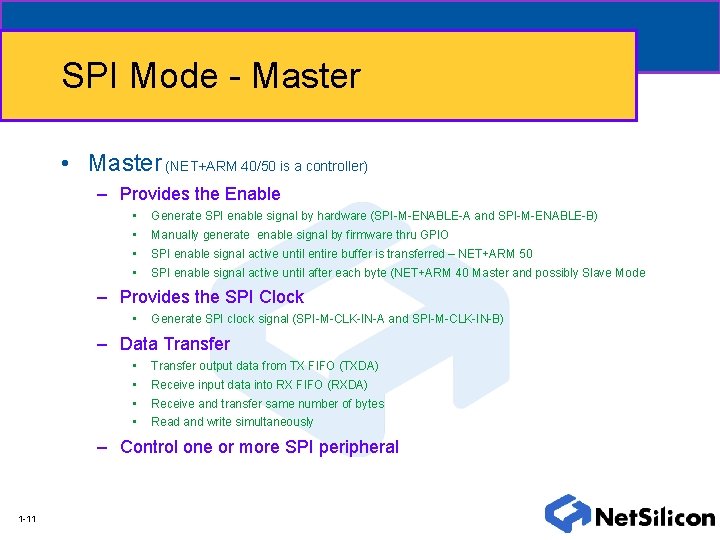

SPI Mode - Master • Master (NET+ARM 40/50 is a controller) – Provides the Enable • • Generate SPI enable signal by hardware (SPI-M-ENABLE-A and SPI-M-ENABLE-B) Manually generate enable signal by firmware thru GPIO SPI enable signal active until entire buffer is transferred – NET+ARM 50 SPI enable signal active until after each byte (NET+ARM 40 Master and possibly Slave Mode – Provides the SPI Clock • Generate SPI clock signal (SPI-M-CLK-IN-A and SPI-M-CLK-IN-B) – Data Transfer • • Transfer output data from TX FIFO (TXDA) Receive input data into RX FIFO (RXDA) Receive and transfer same number of bytes Read and write simultaneously – Control one or more SPI peripheral 1 -11

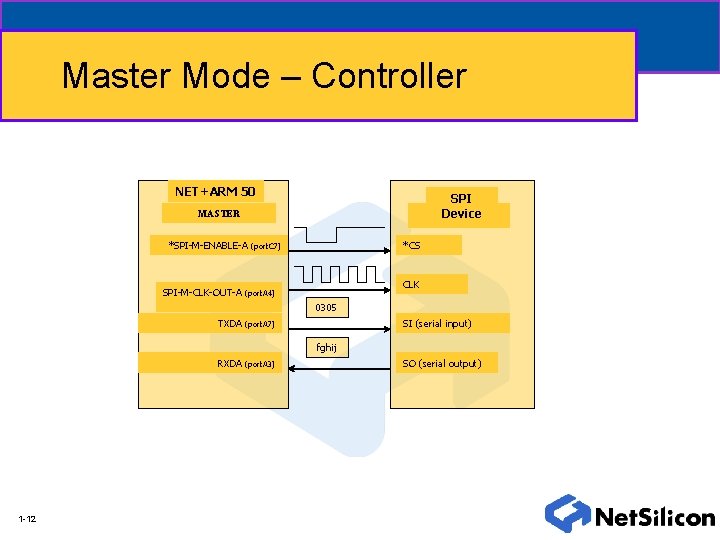

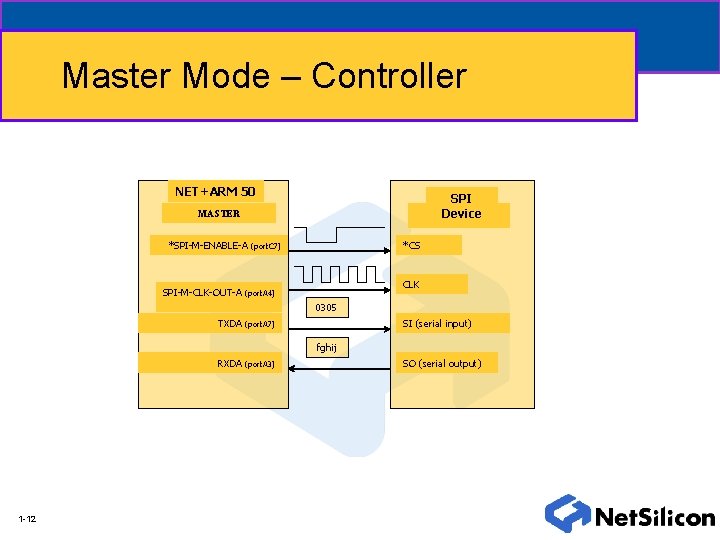

Master Mode – Controller NET+ARM 50 SPI Device MASTER *SPI-M-ENABLE-A SPI-M-CLK-OUT-A *CS (port. C 7) CLK (port. A 4) 0305 TXDA SI (serial input) (port. A 7) fghij RXDA 1 -12 (port. A 3) SO (serial output)

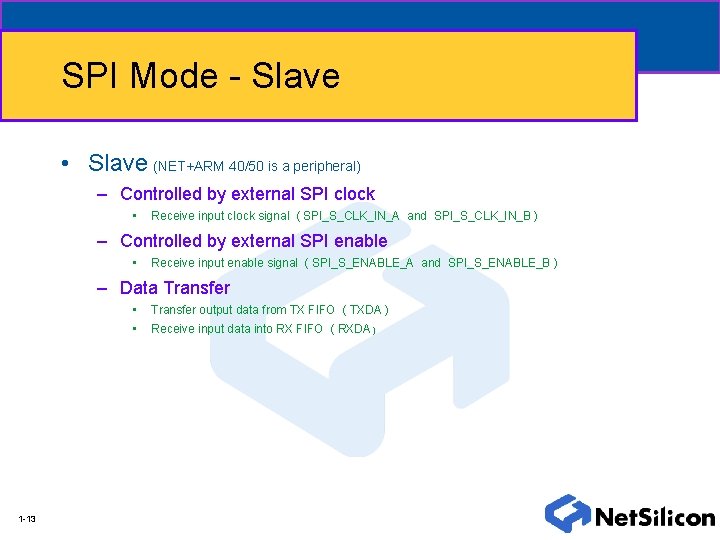

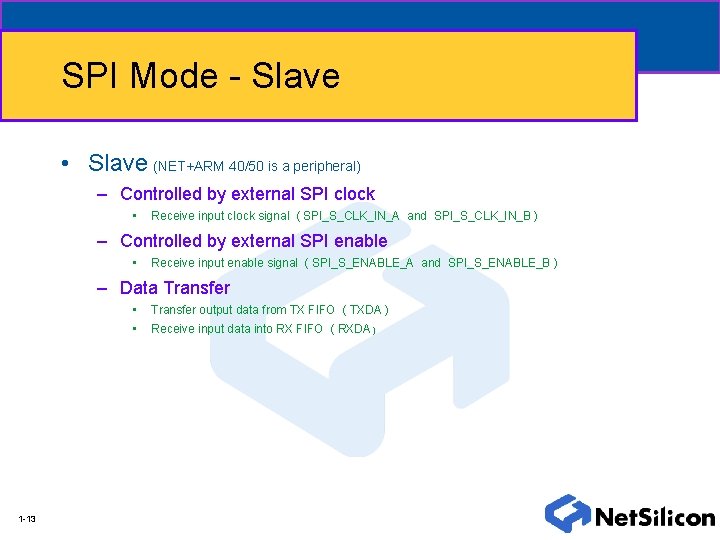

SPI Mode - Slave • Slave (NET+ARM 40/50 is a peripheral) – Controlled by external SPI clock • Receive input clock signal ( SPI_S_CLK_IN_A and SPI_S_CLK_IN_B ) – Controlled by external SPI enable • Receive input enable signal ( SPI_S_ENABLE_A and SPI_S_ENABLE_B ) – Data Transfer • • 1 -13 Transfer output data from TX FIFO ( TXDA ) Receive input data into RX FIFO ( RXDA )

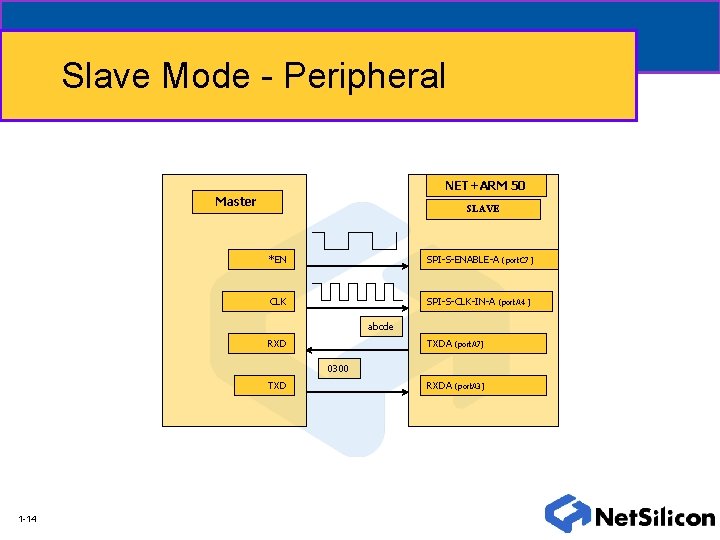

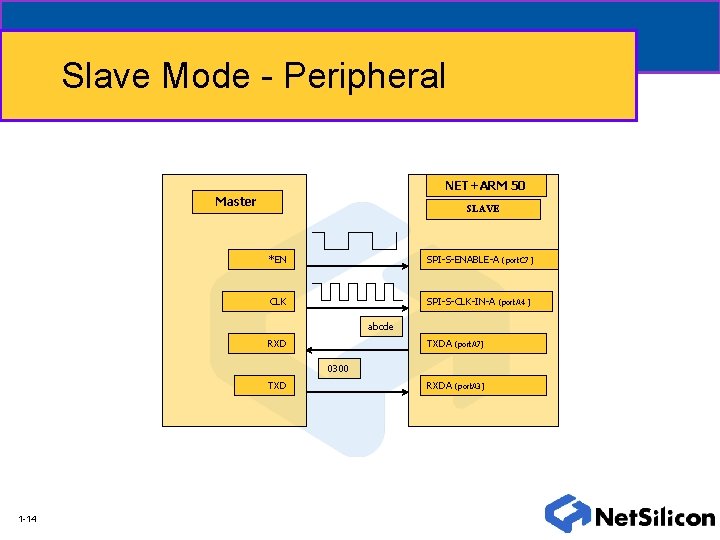

Slave Mode - Peripheral NET+ARM 50 Master SLAVE *EN SPI-S-ENABLE-A CLK SPI-S-CLK-IN-A abcde RXD TXDA (port. A 7) RXDA (port. A 3) 0300 TXD 1 -14 (port. C 7 ) (port. A 4 )

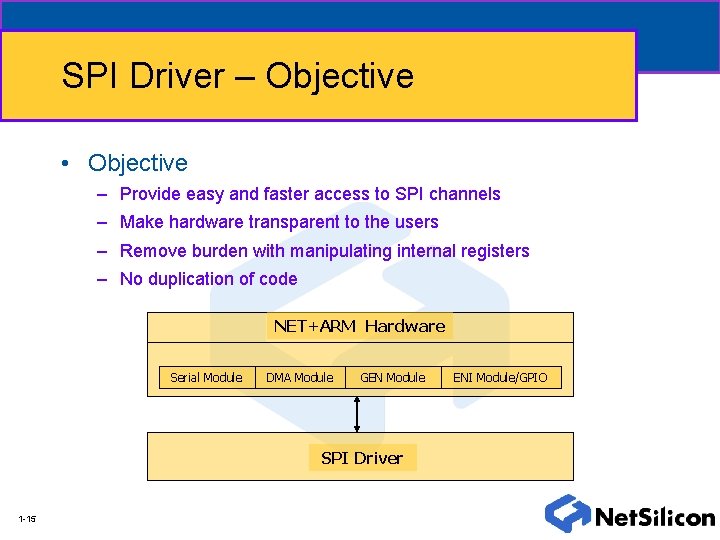

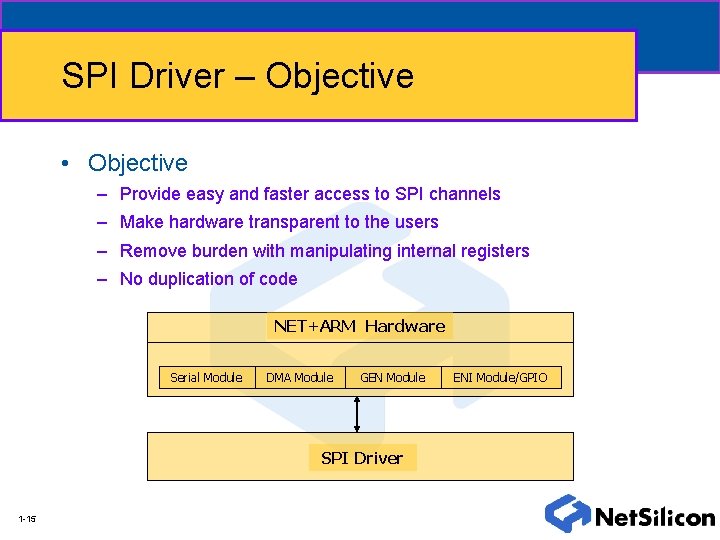

SPI Driver – Objective • Objective – Provide easy and faster access to SPI channels – Make hardware transparent to the users – Remove burden with manipulating internal registers – No duplication of code NET+ARM Hardware Serial Module DMA Module GEN Module SPI Driver 1 -15 ENI Module/GPIO

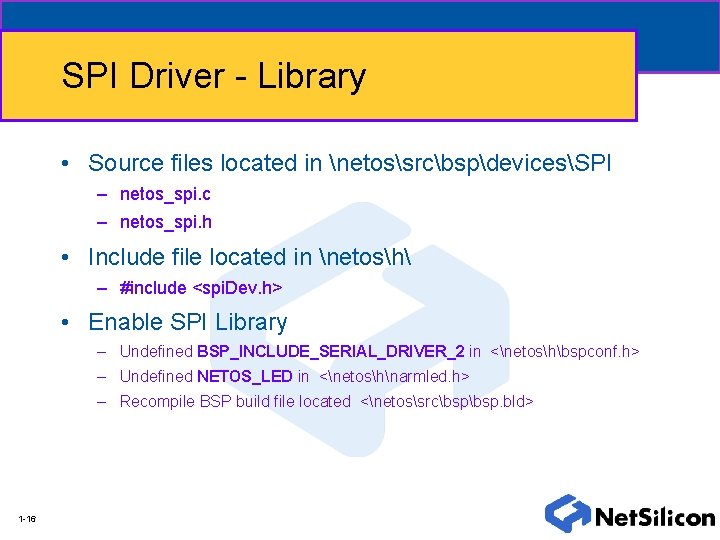

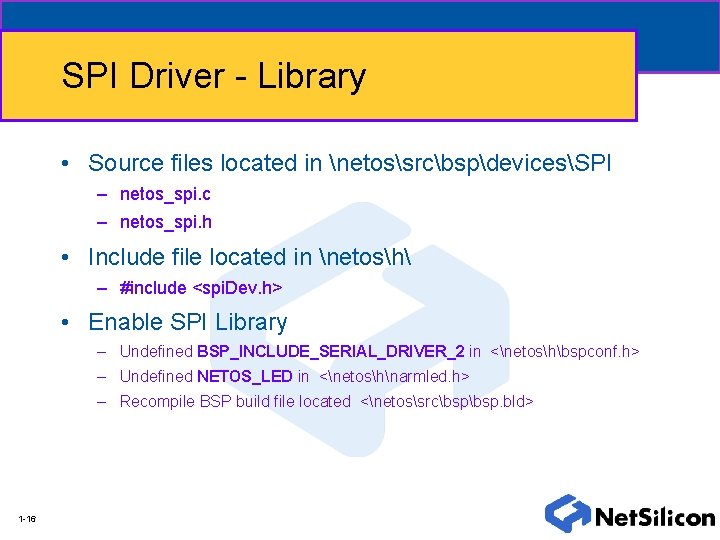

SPI Driver - Library • Source files located in netossrcbspdevicesSPI – netos_spi. c – netos_spi. h • Include file located in netosh – #include <spi. Dev. h> • Enable SPI Library – Undefined BSP_INCLUDE_SERIAL_DRIVER_2 in <netoshbspconf. h> – Undefined NETOS_LED in <netoshnarmled. h> – Recompile BSP build file located <netossrcbsp. bld> 1 -16

High Speed Serial Driver • Uses DMA channels 7, 8, 9 and 10 • Reaches up to a speed of 518400 baud along with 33. 1776 Mhz crystal – However the max baud rate for the 50 chip is 691200 based on 44 MHz Clock. Reminder that the speed varies with the system clock • Sends and receives more than 500, 000 bytes per single send&receive function call • Supports Hardware hand shaking only 1 -17

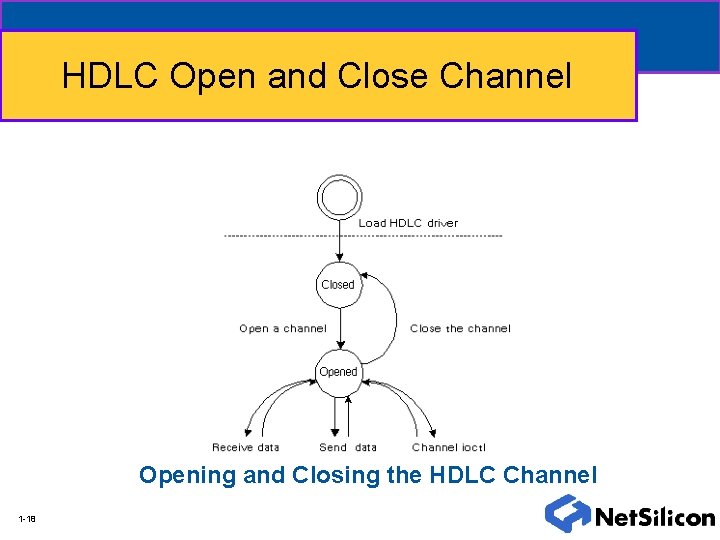

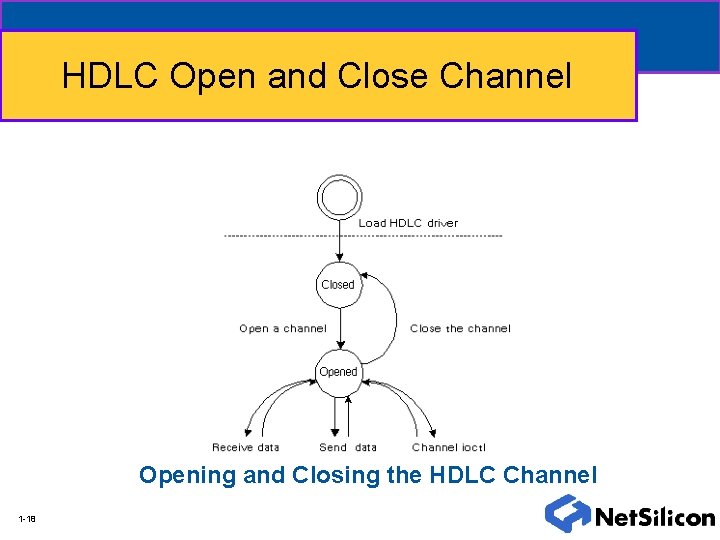

HDLC Open and Close Channel Opening and Closing the HDLC Channel 1 -18

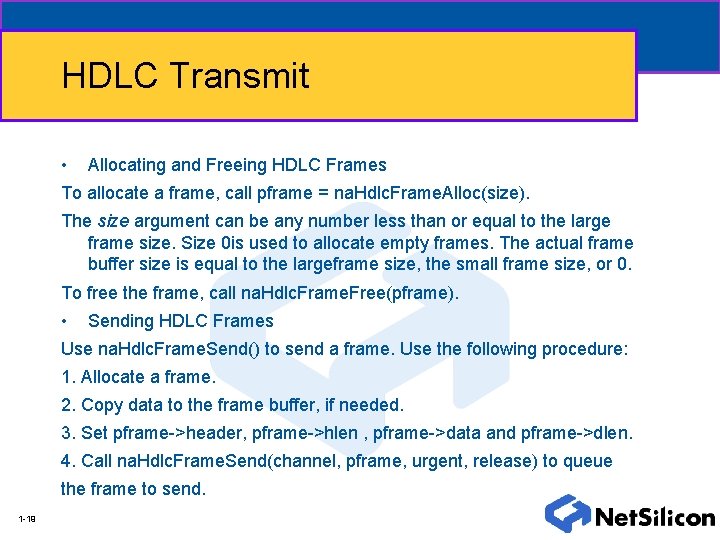

HDLC Transmit • Allocating and Freeing HDLC Frames To allocate a frame, call pframe = na. Hdlc. Frame. Alloc(size). The size argument can be any number less than or equal to the large frame size. Size 0 is used to allocate empty frames. The actual frame buffer size is equal to the largeframe size, the small frame size, or 0. To free the frame, call na. Hdlc. Frame. Free(pframe). • Sending HDLC Frames Use na. Hdlc. Frame. Send() to send a frame. Use the following procedure: 1. Allocate a frame. 2. Copy data to the frame buffer, if needed. 3. Set pframe->header, pframe->hlen , pframe->data and pframe->dlen. 4. Call na. Hdlc. Frame. Send(channel, pframe, urgent, release) to queue the frame to send. 1 -19

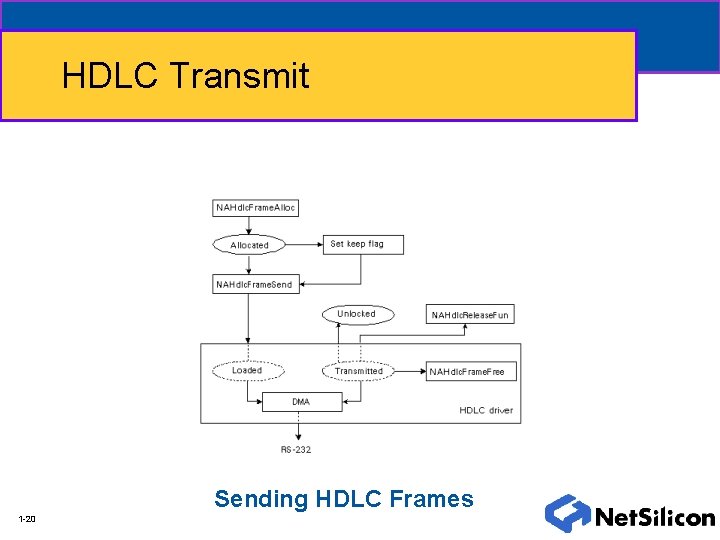

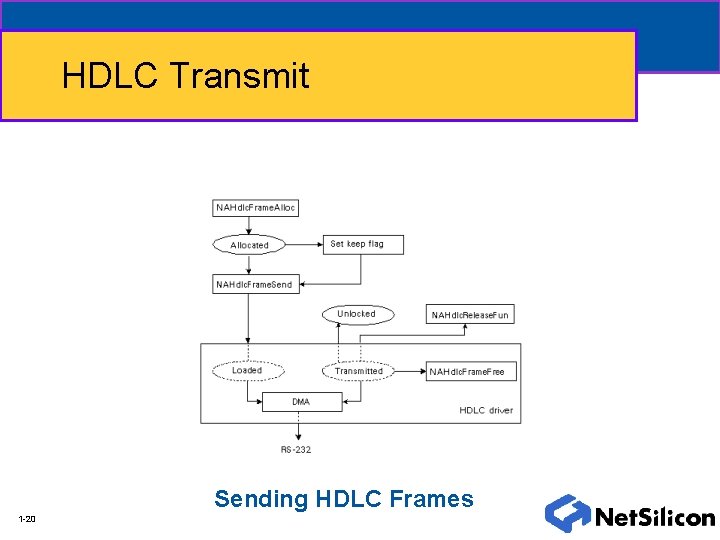

HDLC Transmit Sending HDLC Frames 1 -20

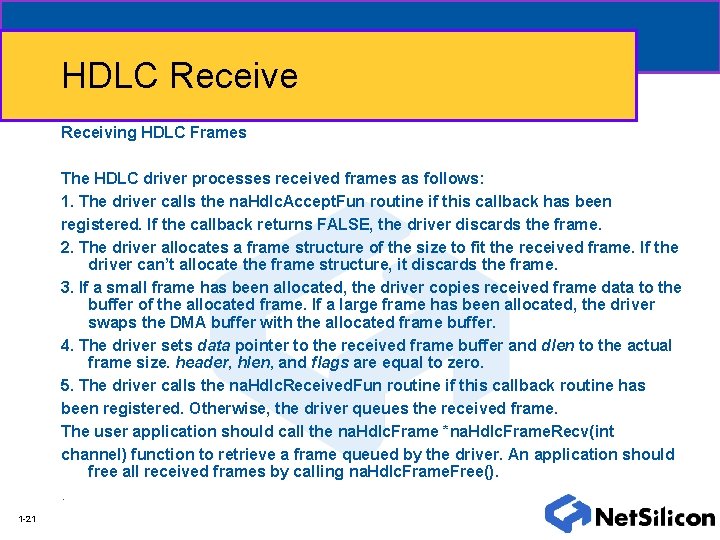

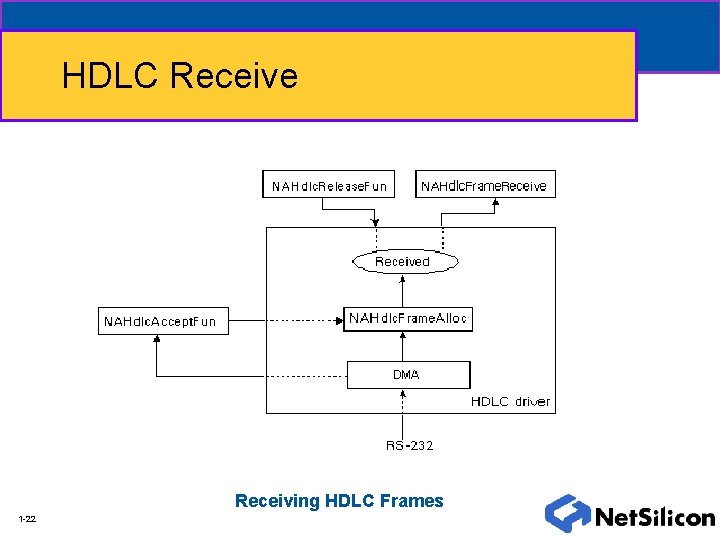

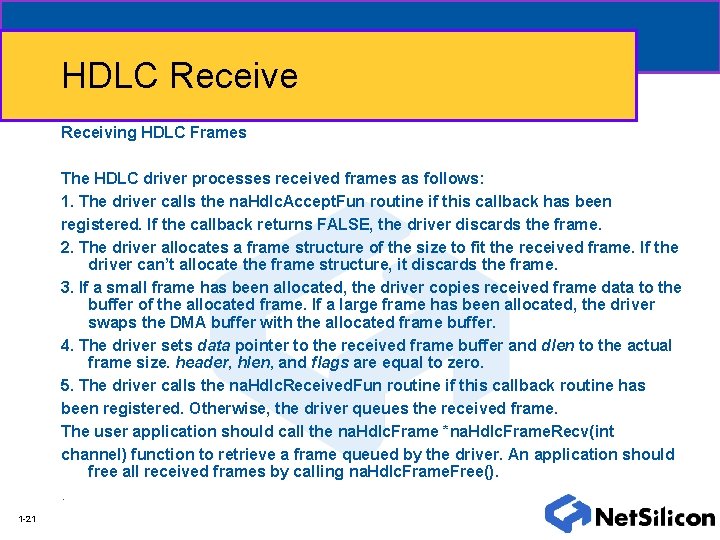

HDLC Receive Receiving HDLC Frames The HDLC driver processes received frames as follows: 1. The driver calls the na. Hdlc. Accept. Fun routine if this callback has been registered. If the callback returns FALSE, the driver discards the frame. 2. The driver allocates a frame structure of the size to fit the received frame. If the driver can’t allocate the frame structure, it discards the frame. 3. If a small frame has been allocated, the driver copies received frame data to the buffer of the allocated frame. If a large frame has been allocated, the driver swaps the DMA buffer with the allocated frame buffer. 4. The driver sets data pointer to the received frame buffer and dlen to the actual frame size. header, hlen, and flags are equal to zero. 5. The driver calls the na. Hdlc. Received. Fun routine if this callback routine has been registered. Otherwise, the driver queues the received frame. The user application should call the na. Hdlc. Frame *na. Hdlc. Frame. Recv(int channel) function to retrieve a frame queued by the driver. An application should free all received frames by calling na. Hdlc. Frame. Free(). . 1 -21

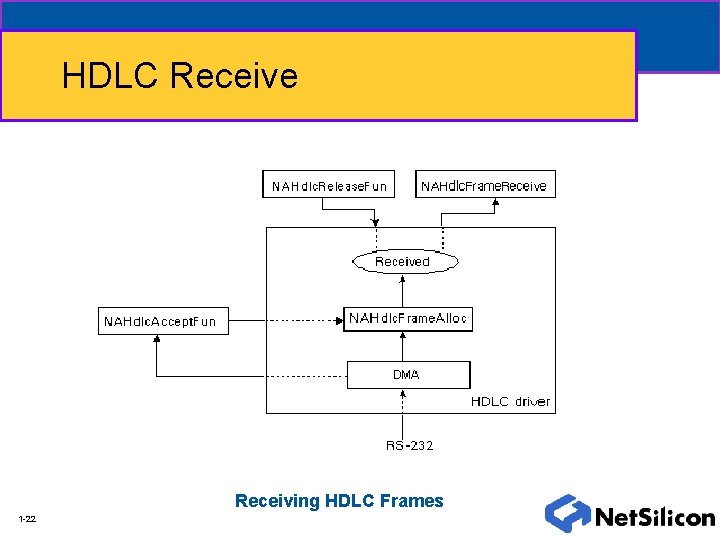

HDLC Receive Receiving HDLC Frames 1 -22