THIS AND THAT Universal Modeling Language UML For

![[Single / Multiple] + [Instruction / Memory] Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline [Single / Multiple] + [Instruction / Memory] Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline](https://slidetodoc.com/presentation_image/c1fcd42138031e934d50a476305adefc/image-11.jpg)

- Slides: 16

THIS AND THAT

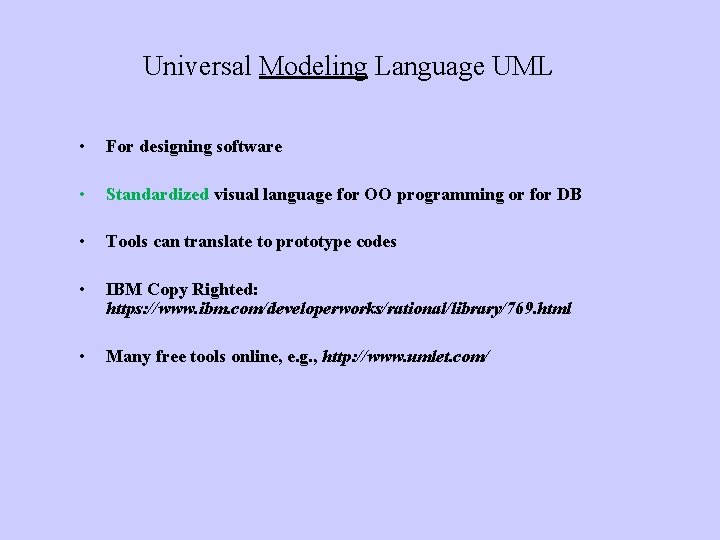

Universal Modeling Language UML • For designing software • Standardized visual language for OO programming or for DB • Tools can translate to prototype codes • IBM Copy Righted: https: //www. ibm. com/developerworks/rational/library/769. html • Many free tools online, e. g. , http: //www. umlet. com/

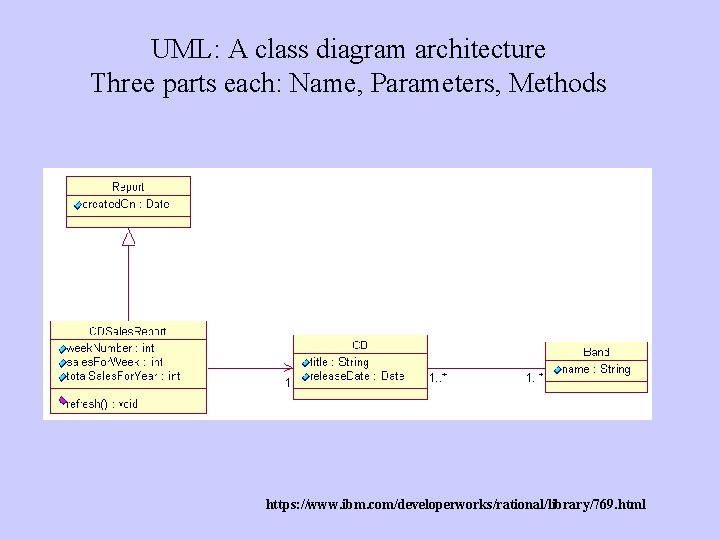

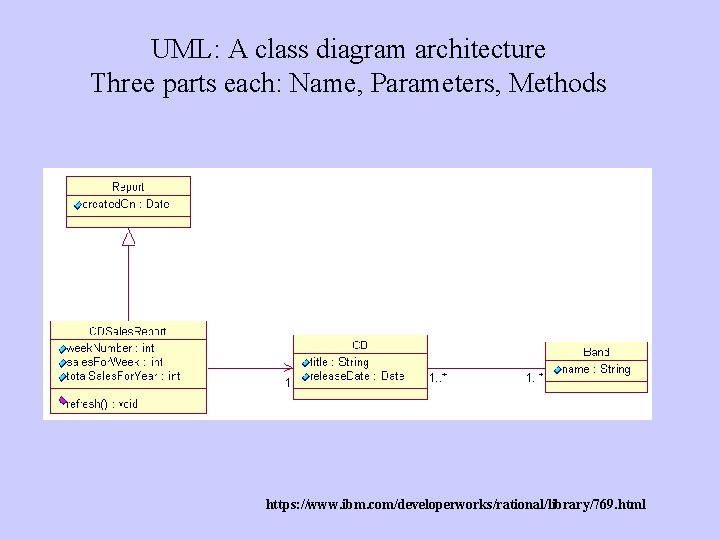

UML: A class diagram architecture Three parts each: Name, Parameters, Methods https: //www. ibm. com/developerworks/rational/library/769. html

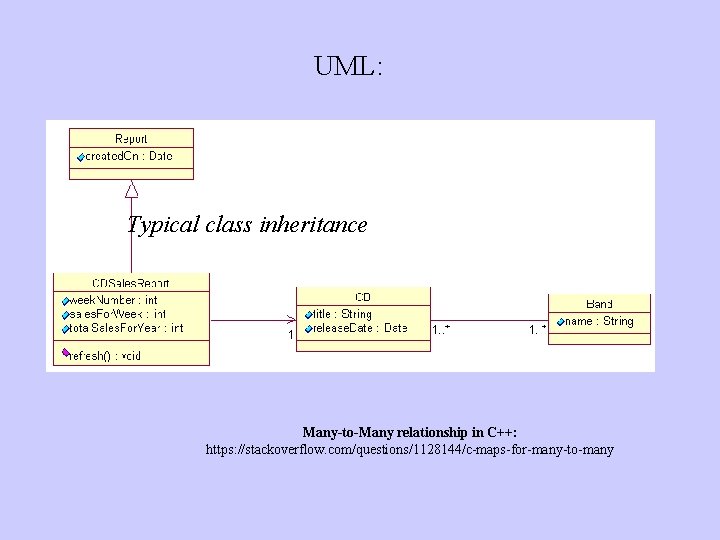

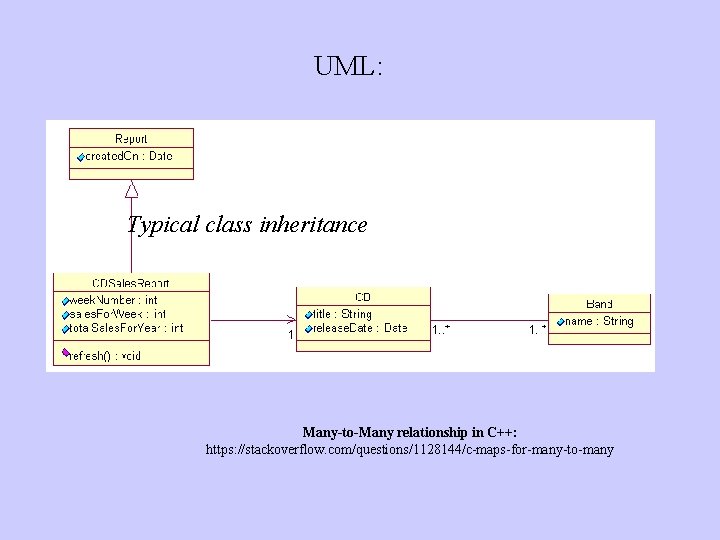

UML: Typical class inheritance Many-to-Many relationship in C++: https: //stackoverflow. com/questions/1128144/c-maps-for-many-to-many

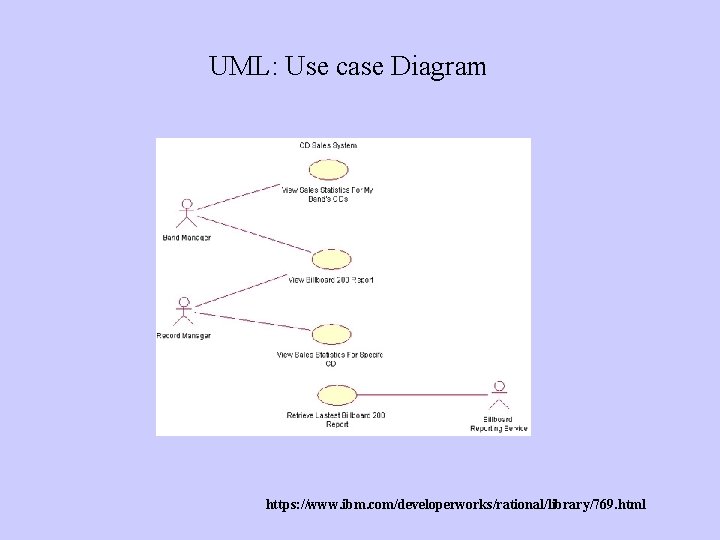

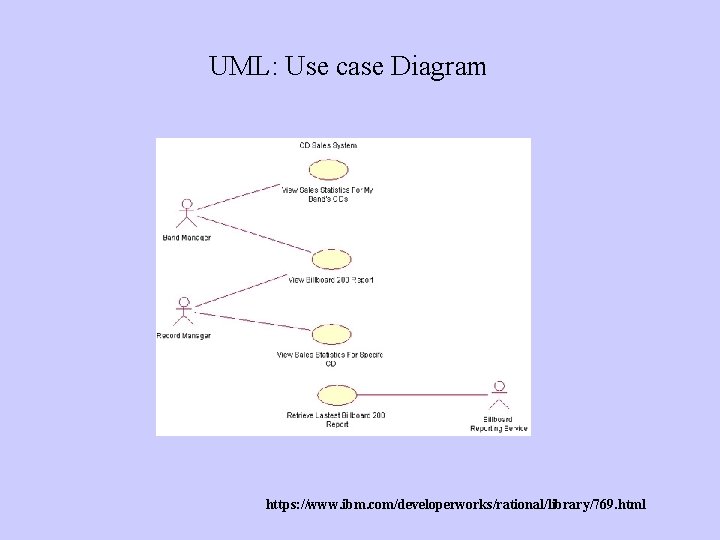

UML: Use case Diagram https: //www. ibm. com/developerworks/rational/library/769. html

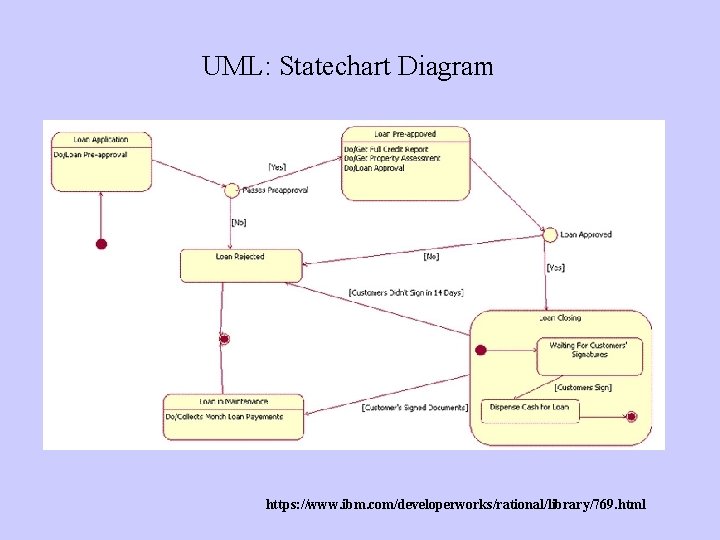

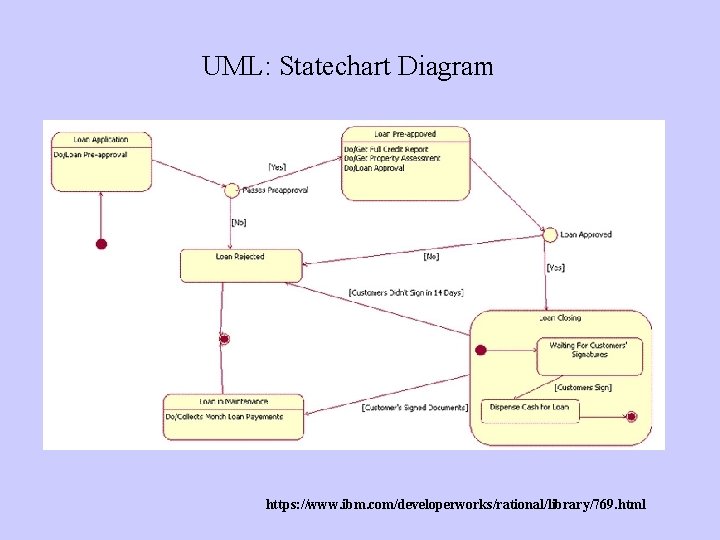

UML: Statechart Diagram https: //www. ibm. com/developerworks/rational/library/769. html

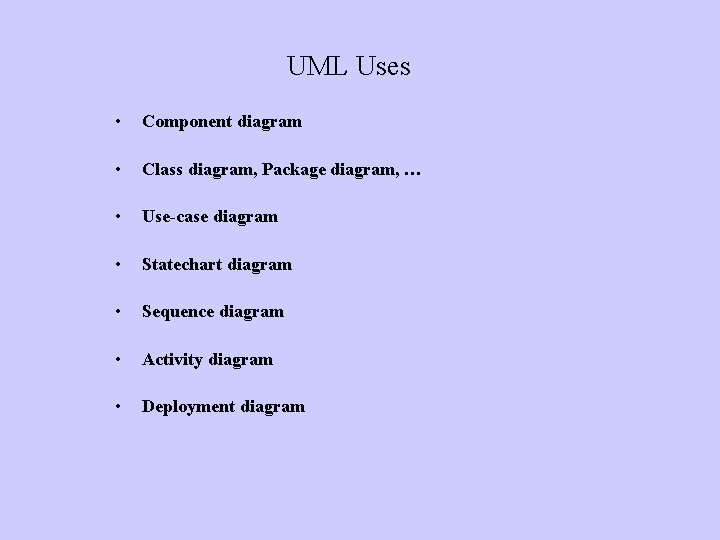

UML Uses • Component diagram • Class diagram, Package diagram, … • Use-case diagram • Statechart diagram • Sequence diagram • Activity diagram • Deployment diagram

GPU computing

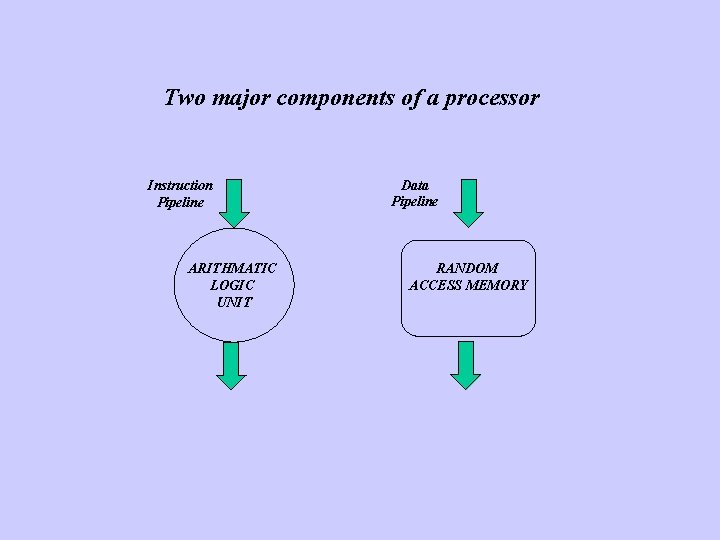

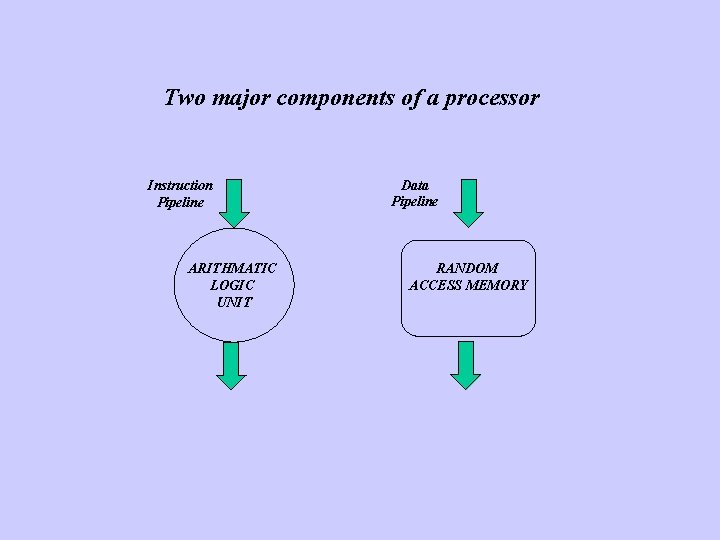

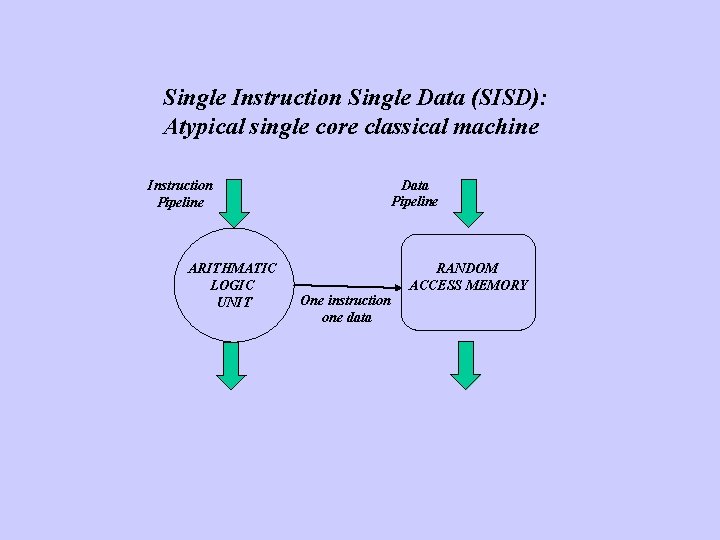

Two major components of a processor Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline RANDOM ACCESS MEMORY

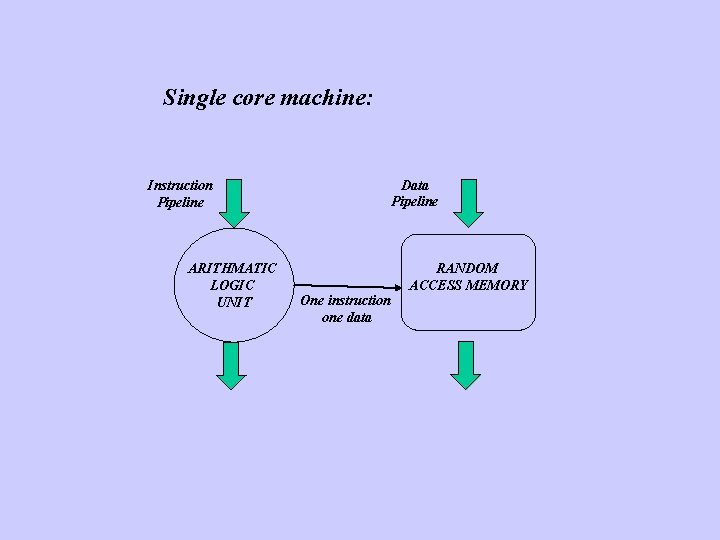

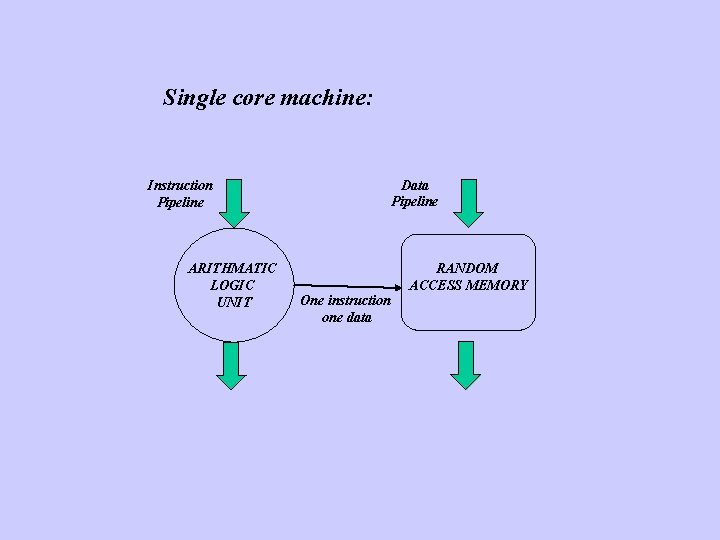

Single core machine: Data Pipeline Instruction Pipeline ARITHMATIC LOGIC UNIT RANDOM ACCESS MEMORY One instruction one data

![Single Multiple Instruction Memory Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline [Single / Multiple] + [Instruction / Memory] Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline](https://slidetodoc.com/presentation_image/c1fcd42138031e934d50a476305adefc/image-11.jpg)

[Single / Multiple] + [Instruction / Memory] Instruction Pipeline ARITHMATIC LOGIC UNIT Data Pipeline RANDOM ACCESS MEMORY

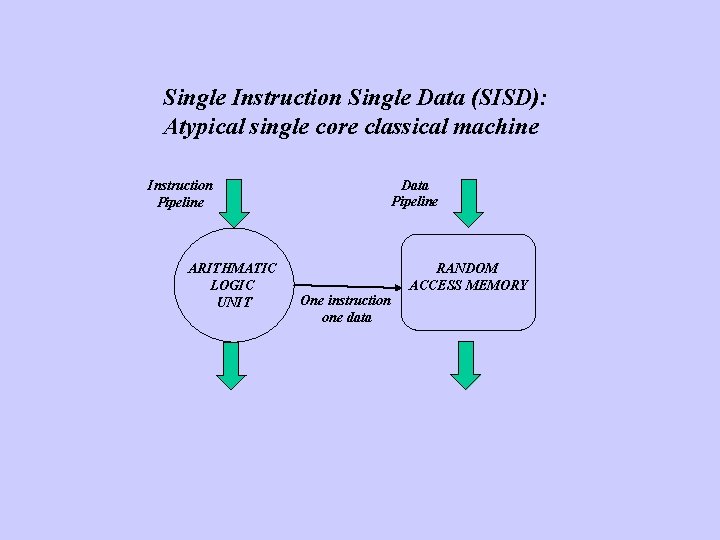

Single Instruction Single Data (SISD): Atypical single core classical machine Data Pipeline Instruction Pipeline ARITHMATIC LOGIC UNIT RANDOM ACCESS MEMORY One instruction one data

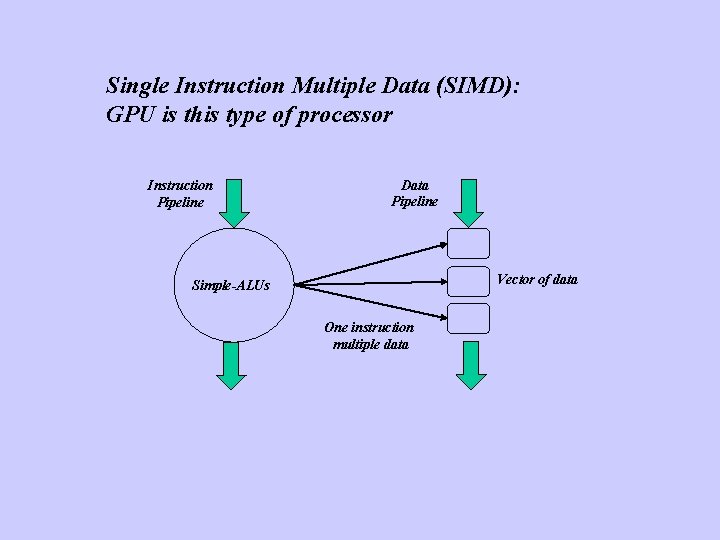

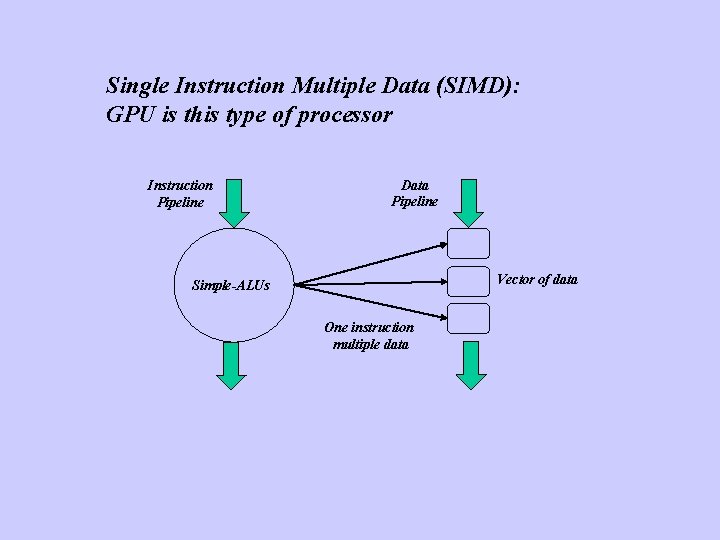

Single Instruction Multiple Data (SIMD): GPU is this type of processor Instruction Pipeline Data Pipeline Vector of data Simple-ALUs One instruction multiple data

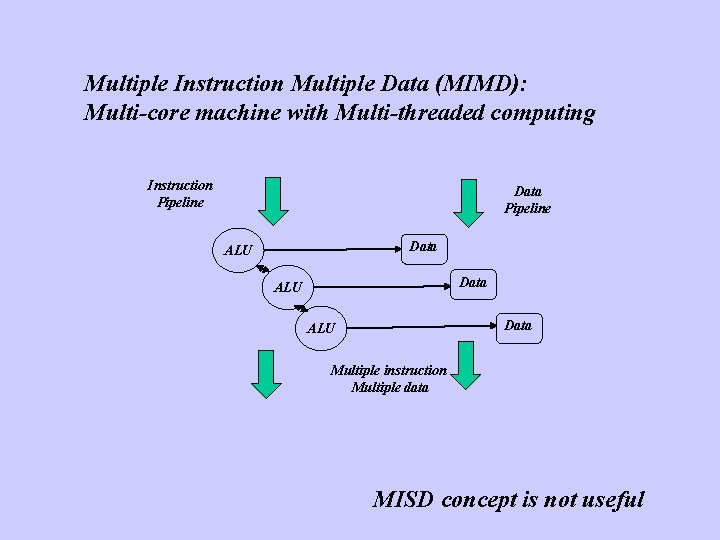

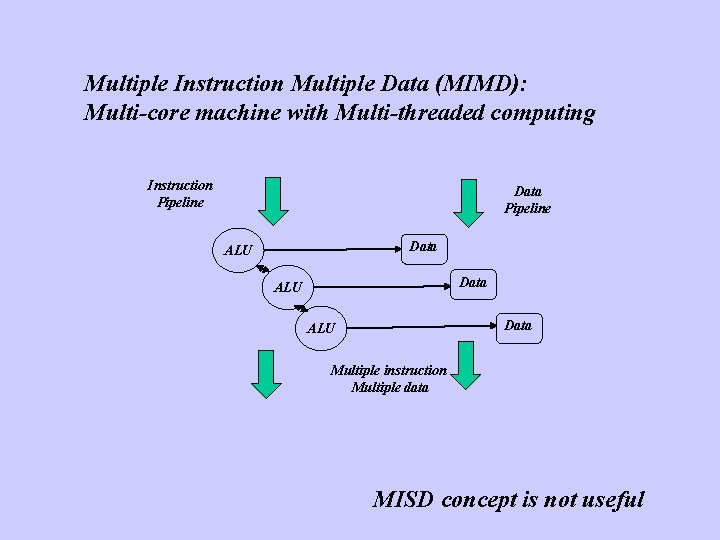

Multiple Instruction Multiple Data (MIMD): Multi-core machine with Multi-threaded computing Instruction Pipeline Data ALU Multiple instruction Multiple data MISD concept is not useful

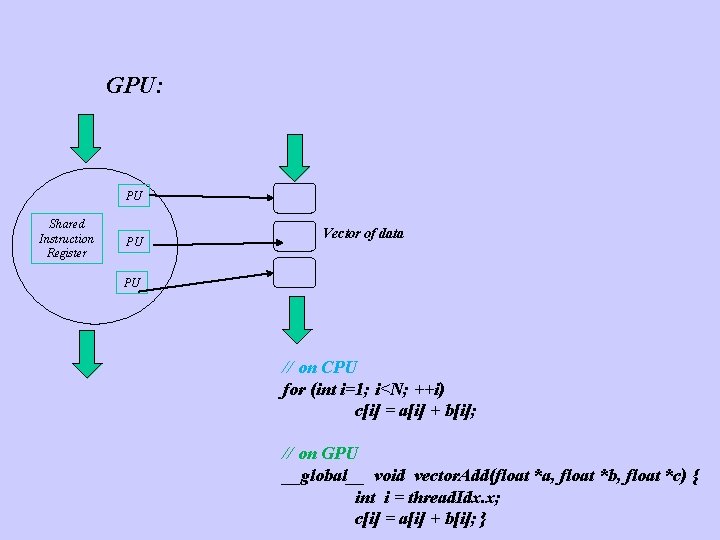

GPU: Data Pipeline Instruction Pipeline One instruction multiple data Processing Unit Shared Instruction Register Processing Unit Vector of data

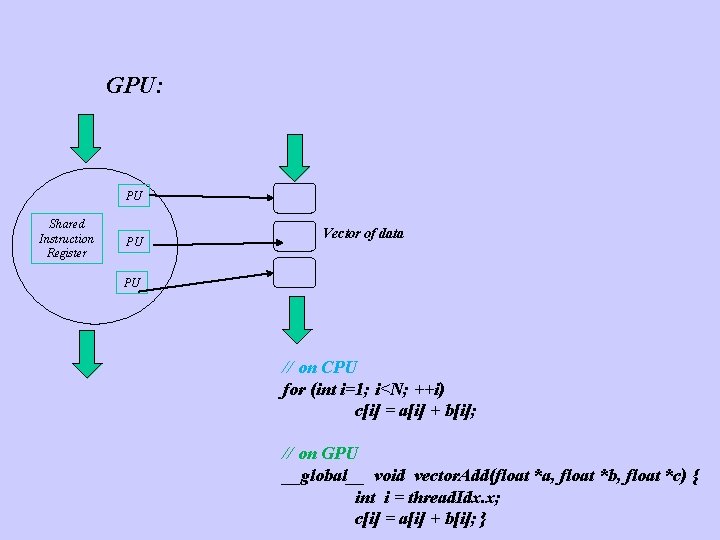

GPU: PU Shared Instruction Register PU Vector of data PU // on CPU for (int i=1; i<N; ++i) c[i] = a[i] + b[i]; // on GPU __global__ void vector. Add(float *a, float *b, float *c) { int i = thread. Idx. x; c[i] = a[i] + b[i]; }