Overview IO memory mapped programmed interrupt driven Traps

![Traps 1) Execute 2) Trap Vectors are at memory locations [0000: 00 FF] 3) Traps 1) Execute 2) Trap Vectors are at memory locations [0000: 00 FF] 3)](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-3.jpg)

![Subroutines JSR Instruction: JSR offset (11 bit) 0100 1 xxxxxx [PC ] R 7, Subroutines JSR Instruction: JSR offset (11 bit) 0100 1 xxxxxx [PC ] R 7,](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-4.jpg)

![State of Program - Program Status Register PSR: PSR[15] – Privilege Bit PSR[10: 8] State of Program - Program Status Register PSR: PSR[15] – Privilege Bit PSR[10: 8]](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-10.jpg)

- Slides: 16

Overview • I/O – memory mapped programmed / interrupt driven • Traps mechanism & RET • Subroutines & JSRR & RET • Interrupt mechanism & RTI

LC-3 has Memory Mapped I/O LC-3 Memory Layout: x 0000 – x 00 FF Trap vectors (Supports Software Interrupts) x 0020 [x 0400] GETC (Read Char from Keyboard) x 0021 [x 0430] OUT x 0022 [x 0450] PUTS (Write string to Console) x 0023 [x 04 A 0] IN x 0024 [x 04 E 0] PUTSP (Write “packed” string to Console) x 0025 [x. FD 70] HALT (Turn off run latch in MCR) (Write Character to Console) (Prompt, input character from Keyboard, echo character to Console) x 0100 – x 01 FF Interrupt Vectors (Supports Hardware Interrupts) x 0200 – x 2 FFF System Programs & Data (“Operating System”) x 3000 – x. FDFF User Programs Area x. FE 00 – x. FFFF I/O Programming “Registers” (Mapped I/O Registers) x. FE 00 KBSR [15 {Ready}, 14 {Intr enable}] (Keyboard Status Register) x. FE 02 KBDR [7: 0{ascii data}] (Keyboard Data Register) x. FE 04 DSR [15{Done}, 14{Intr enable}] (Display Status Register) x. FE 06 DDR [7: 0{ascii data}] (Display Data Register x. FFFE MCR [15{Run latch}] (Machine Control Register)

![Traps 1 Execute 2 Trap Vectors are at memory locations 0000 00 FF 3 Traps 1) Execute 2) Trap Vectors are at memory locations [0000: 00 FF] 3)](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-3.jpg)

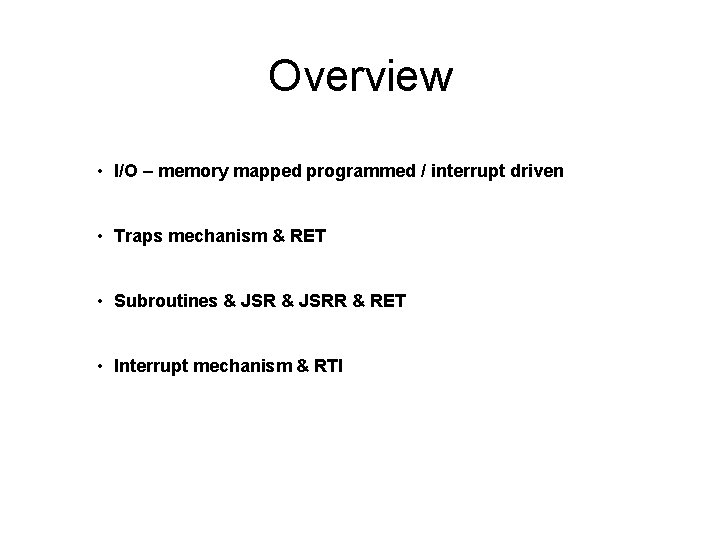

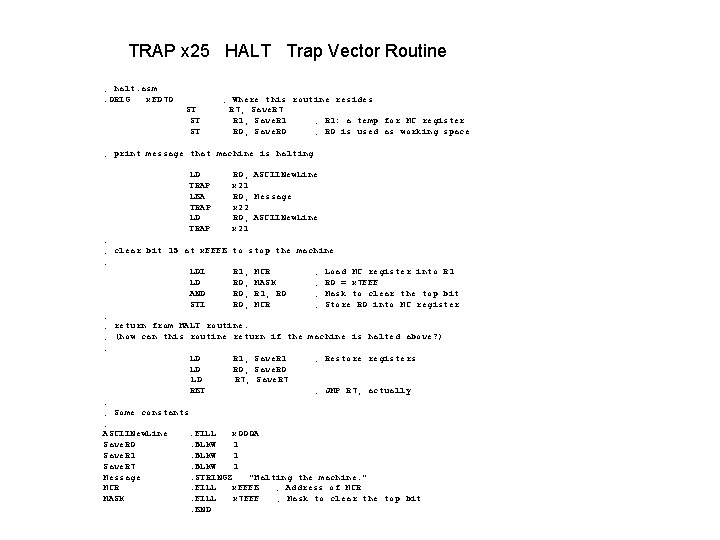

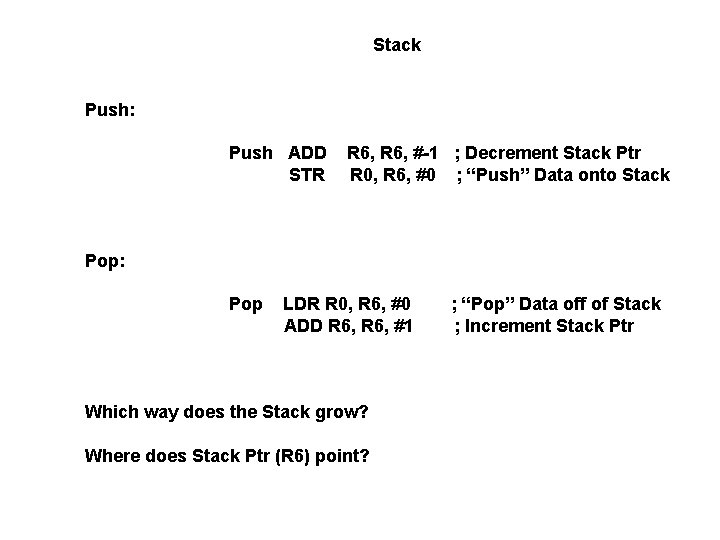

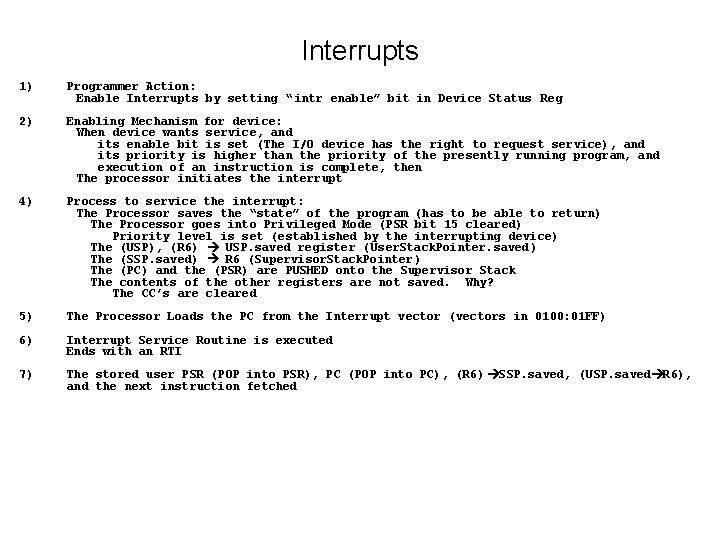

Traps 1) Execute 2) Trap Vectors are at memory locations [0000: 00 FF] 3) Trap Vectors contain addresses of Trap Service Routines 4) (PC) is loaded into R 7 5) Address of Trap Service Routine loaded into PC 6) Service Routine Program executed 7) Trap service routine program ends with an RET ( (R 7) loaded into PC) TRAP “vector” - Operating System Service Routines

![Subroutines JSR Instruction JSR offset 11 bit 0100 1 xxxxxx PC R 7 Subroutines JSR Instruction: JSR offset (11 bit) 0100 1 xxxxxx [PC ] R 7,](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-4.jpg)

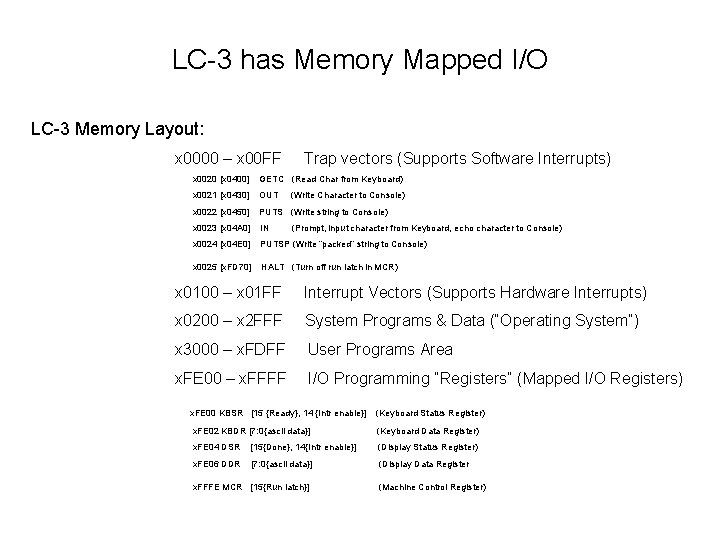

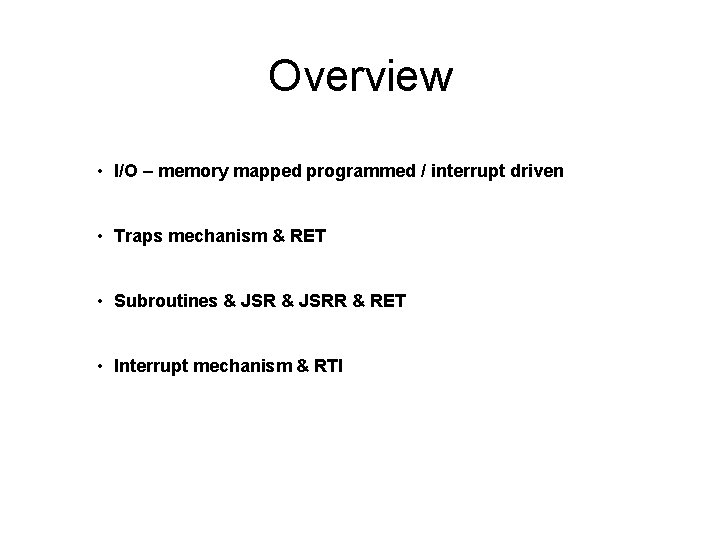

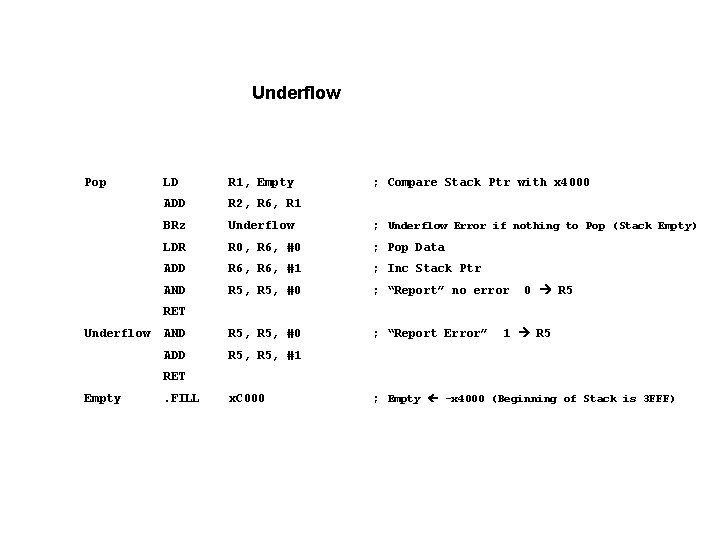

Subroutines JSR Instruction: JSR offset (11 bit) 0100 1 xxxxxx [PC ] R 7, JMP Offset Jump to Subroutine at offset from PC JSRR Instruction JSRR Rb 0100 0 00 xxx 000000 [PC ] R 7, JMP [Reg] Jump to Subroutine at address in Rb Return RET 1100 000 111 000000 C 1 C 0 [R 7] PC (JMP R 7) Return to Instruction after Jump to Subroutine

Subroutines 1) Execute 2) Location of Subroutine is specified in the Instruction 3) JSR or JSRR - Call Subroutine or Method [PC] stored in R 7 4) Address from JSR or JSRR is loaded into PC • Subroutine is executed R 0 likely contains passed parameter (or address) R 5 may be used to return error message R 0 likely contains return parameter (or address) 6) Subroutine program ends with an RET ( [R 7] loaded into PC) How does this mechanism support recursion? It doesn’t! Implement a stack to accommodate recursion.

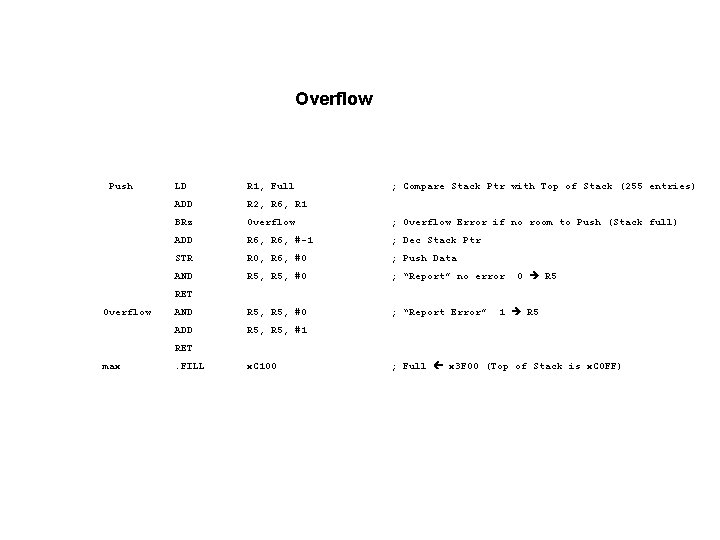

Stack Push: Push ADD STR R 6, #-1 ; Decrement Stack Ptr R 0, R 6, #0 ; “Push” Data onto Stack Pop: Pop LDR R 0, R 6, #0 ADD R 6, #1 Which way does the Stack grow? Where does Stack Ptr (R 6) point? ; “Pop” Data off of Stack ; Increment Stack Ptr

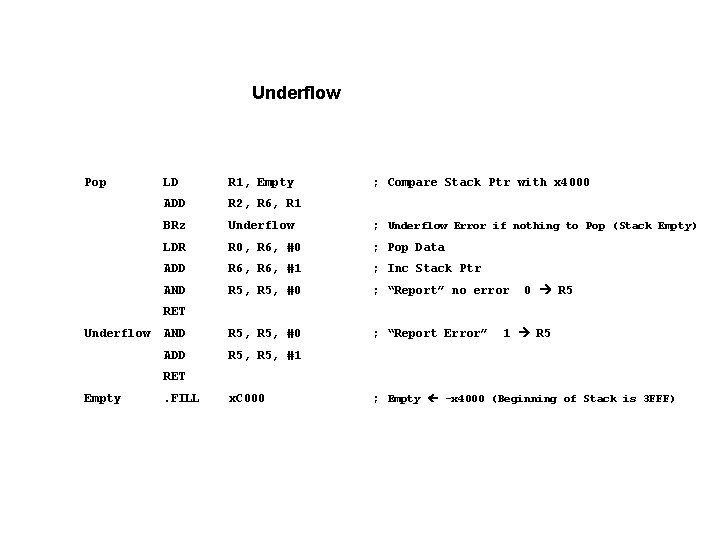

Underflow Pop LD R 1, Empty ; Compare Stack Ptr with x 4000 ADD R 2, R 6, R 1 BRz Underflow ; Underflow Error if nothing to Pop (Stack Empty) LDR R 0, R 6, #0 ; Pop Data ADD R 6, #1 ; Inc Stack Ptr AND R 5, #0 ; “Report” no error AND R 5, #0 ; “Report Error” ADD R 5, #1 0 R 5 RET Underflow 1 R 5 RET Empty . FILL x. C 000 ; Empty -x 4000 (Beginning of Stack is 3 FFF)

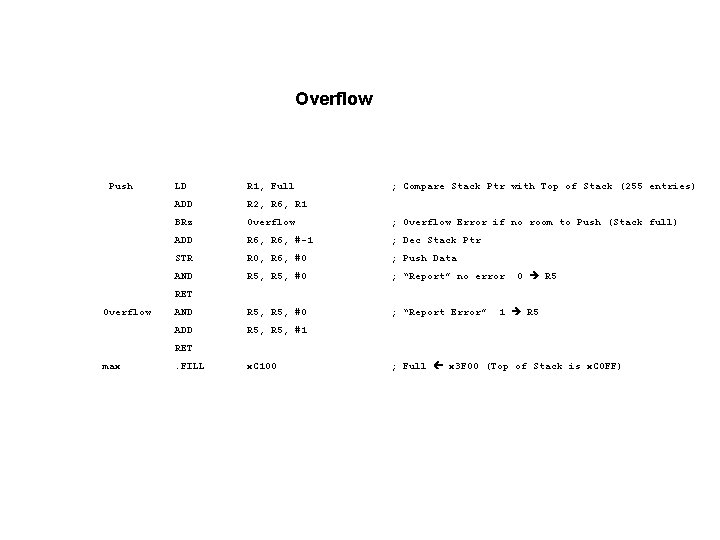

Overflow Push LD R 1, Full ; Compare Stack Ptr with Top of Stack (255 entries) ADD R 2, R 6, R 1 BRz Overflow ; Overflow Error if no room to Push (Stack full) ADD R 6, #-1 ; Dec Stack Ptr STR R 0, R 6, #0 ; Push Data AND R 5, #0 ; “Report” no error AND R 5, #0 ; “Report Error” ADD R 5, #1 0 R 5 RET Overflow 1 R 5 RET max . FILL x. C 100 ; Full x 3 F 00 (Top of Stack is x. C 0 FF)

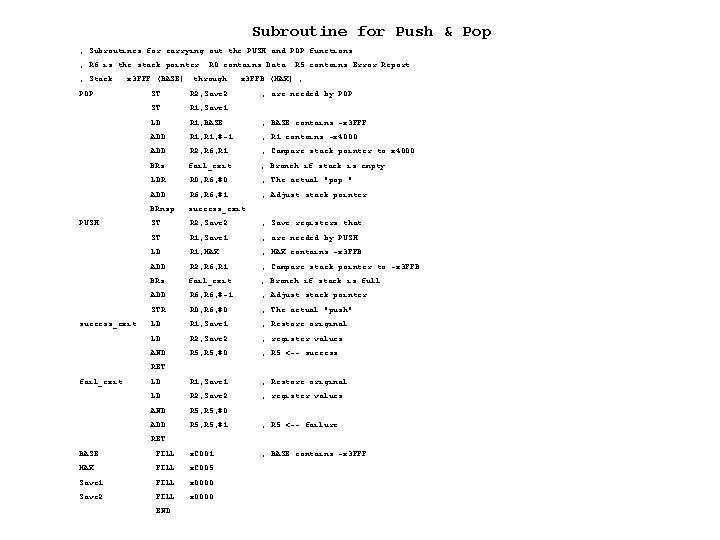

Subroutine for Push & Pop ; Subroutines for carrying out the PUSH and POP functions. ; R 6 is the stack pointer. R 0 contains Data. R 5 contains Error Report ; Stack: x 3 FFF (BASE) through ST R 2, Save 2 ST R 1, Save 1 LD R 1, BASE ; BASE contains -x 3 FFF. ADD R 1, #-1 ; R 1 contains -x 4000. POP PUSH success_exit x 3 FFB (MAX). ; ; are needed by POP. ADD R 2, R 6, R 1 ; Compare stack pointer to x 4000 BRz fail_exit ; Branch if stack is empty. LDR R 0, R 6, #0 ; The actual "pop. " ; Adjust stack pointer ADD R 6, #1 BRnzp success_exit ST R 2, Save 2 ; Save registers that ST R 1, Save 1 ; are needed by PUSH. LD R 1, MAX ; MAX contains -x 3 FFB ADD R 2, R 6, R 1 ; Compare stack pointer to -x 3 FFB BRz fail_exit ; Branch if stack is full. ADD R 6, #-1 ; Adjust stack pointer STR R 0, R 6, #0 ; The actual "push" LD R 1, Save 1 ; Restore original LD R 2, Save 2 ; register values. AND R 5, #0 ; R 5 <-- success. LD R 1, Save 1 ; Restore original LD R 2, Save 2 ; register values. AND R 5, #0 ADD R 5, #1 ; R 5 <-- failure. ; BASE contains -x 3 FFF. RET fail_exit RET BASE . FILL x. C 001 MAX . FILL x. C 005 Save 1 . FILL x 0000 Save 2 . FILL x 0000 . END

![State of Program Program Status Register PSR PSR15 Privilege Bit PSR10 8 State of Program - Program Status Register PSR: PSR[15] – Privilege Bit PSR[10: 8]](https://slidetodoc.com/presentation_image_h2/6ed0a6ca81b5711933d5e61cdf554231/image-10.jpg)

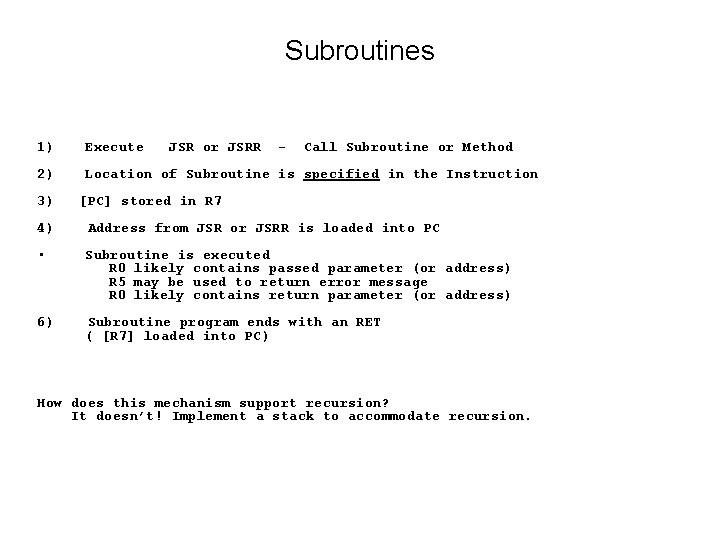

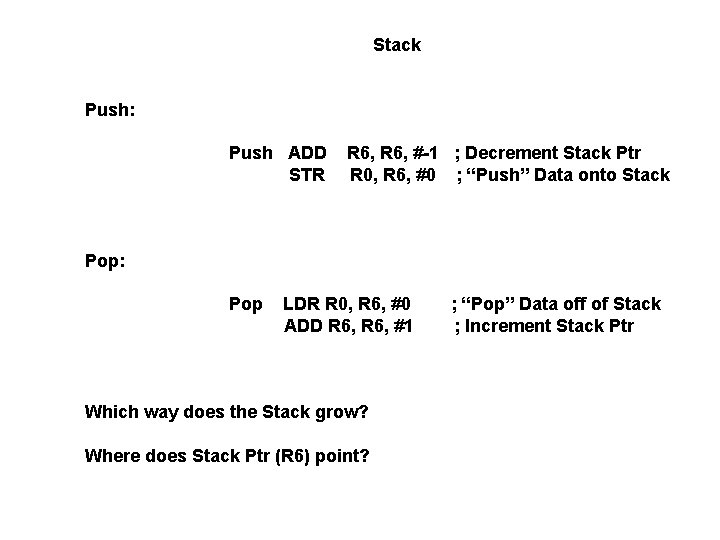

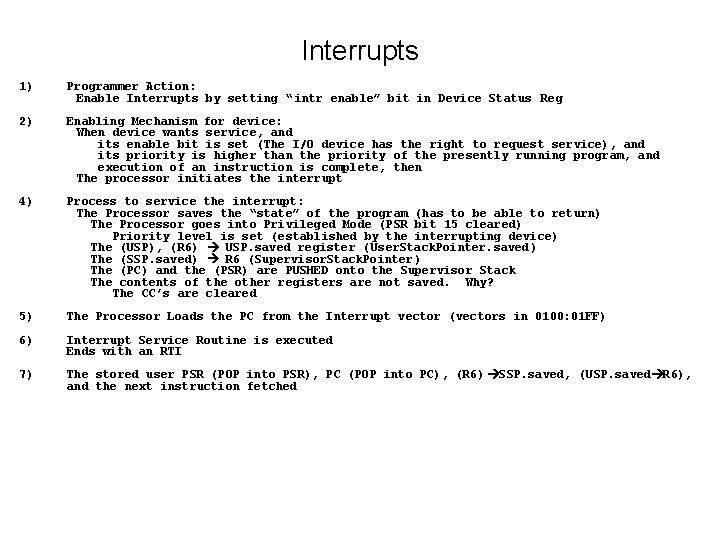

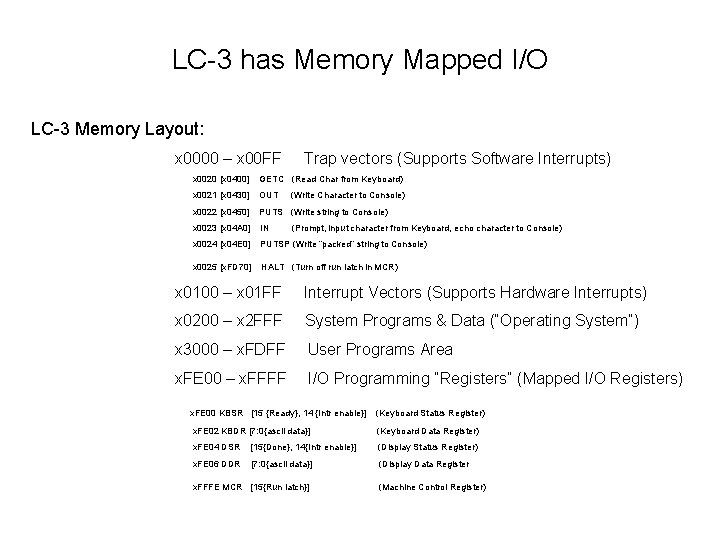

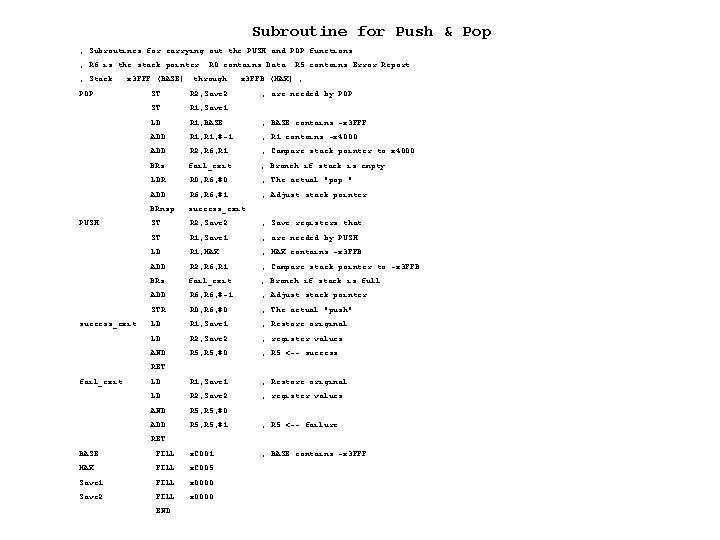

State of Program - Program Status Register PSR: PSR[15] – Privilege Bit PSR[10: 8] – Priority Bits PSR[2: 0] – Condition codes - N, Z, P

Interrupts 1) Programmer Action: Enable Interrupts by setting “ intr enable” bit in Device Status Reg 2) Enabling Mechanism for device: When device wants service, and its enable bit is set (The I/O device has the right to request service), and its priority is higher than the priority of the presently running program, and execution of an instruction is complete, then The processor initiates the interrupt 4) Process to service the interrupt: The Processor saves the “state” of the program (has to be able to return) The Processor goes into Privileged Mode (PSR bit 15 cleared) Priority level is set (established by the interrupting device) The (USP), (R 6) USP. saved register (User. Stack. Pointer. saved) The (SSP. saved) R 6 (Supervisor. Stack. Pointer) The (PC) and the (PSR) are PUSHED onto the Supervisor Stack The contents of the other registers are not saved. Why? The CC’s are cleared 5) The Processor Loads the PC from the Interrupt vector (vectors in 0100: 01 FF) 6) Interrupt Service Routine is executed Ends with an RTI 7) The stored user PSR (POP into PSR), PC (POP into PC), (R 6) SSP. saved, (USP. saved R 6), and the next instruction fetched

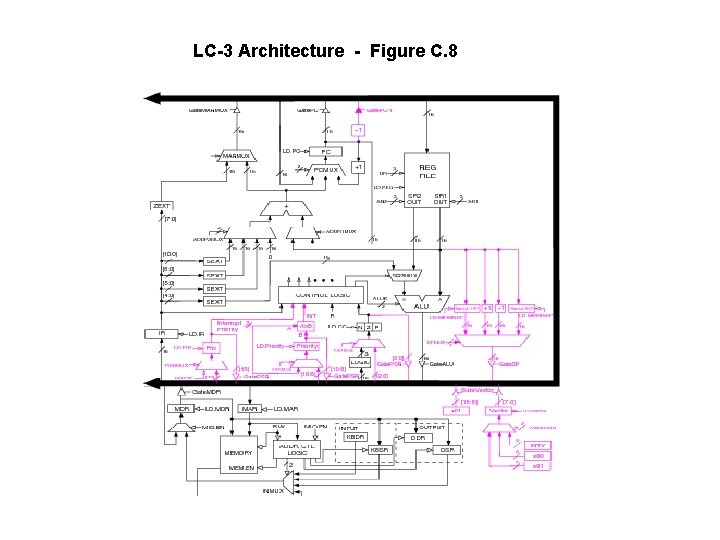

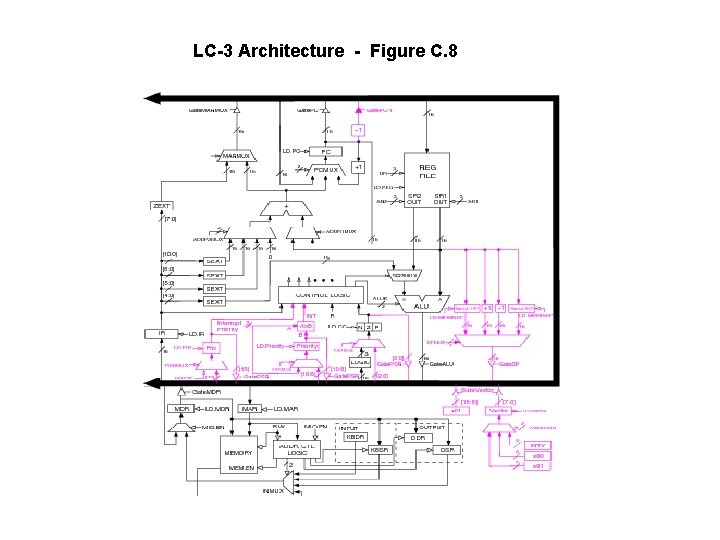

LC-3 Architecture - Figure C. 8

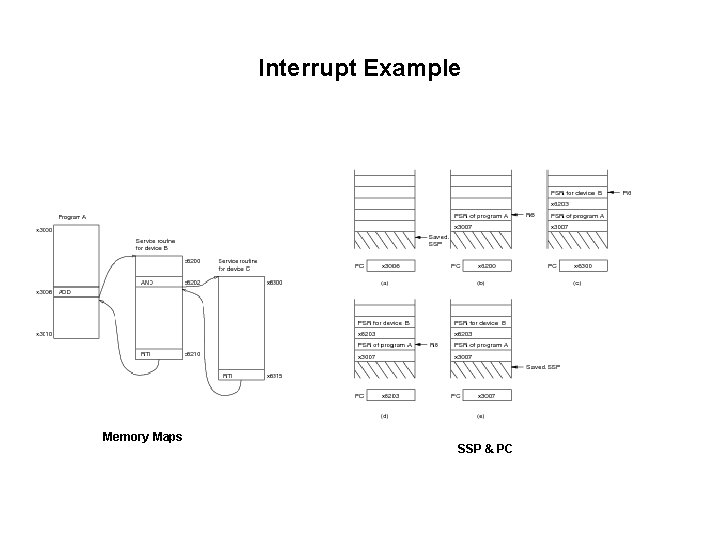

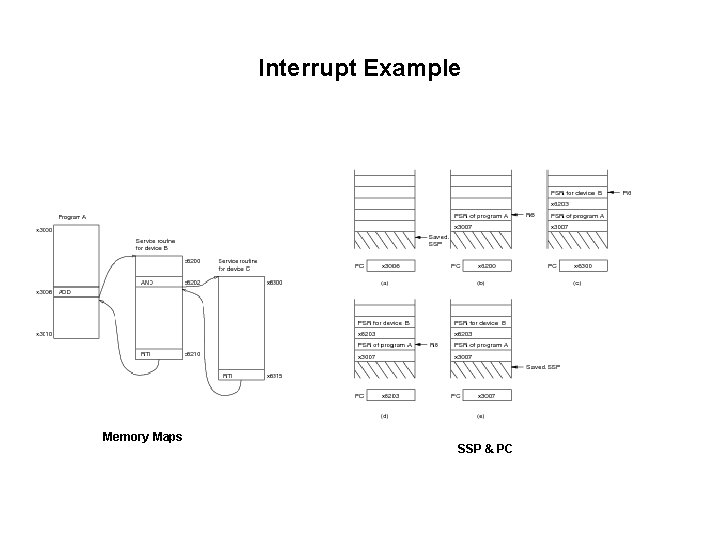

Interrupt Example Memory Maps SSP & PC

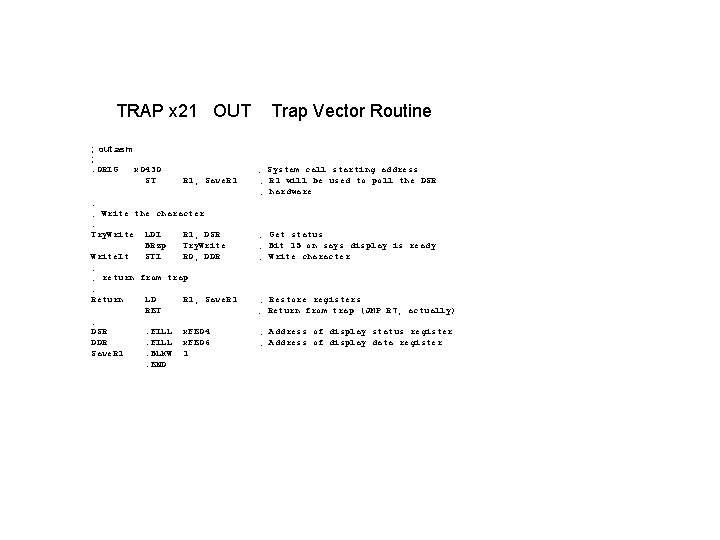

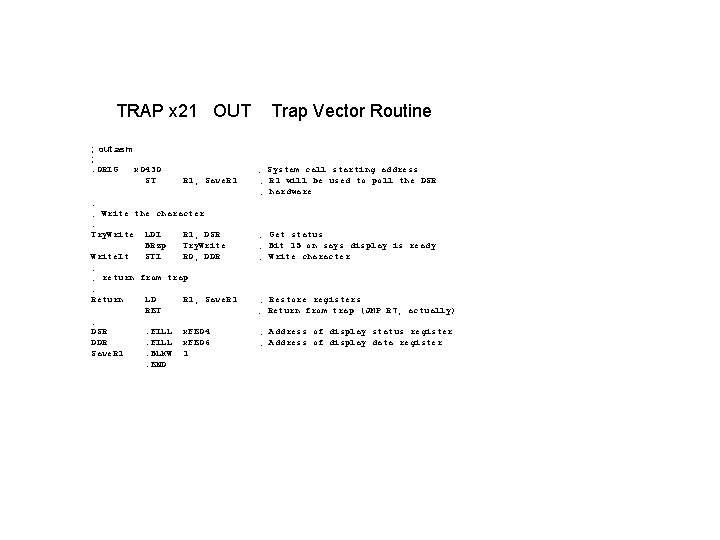

TRAP x 21 OUT ; out. asm ; . ORIG x 0430 ST R 1, Save. R 1 ; ; Write the character ; Try. Write LDI R 1, DSR BRzp Try. Write. It STI R 0, DDR ; ; return from trap ; Return LD R 1, Save. R 1 RET ; DSR. FILL x. FE 04 DDR. FILL x. FE 06 Save. R 1. BLKW 1. END Trap Vector Routine ; System call starting address ; R 1 will be used to poll the DSR ; hardware ; Get status ; Bit 15 on says display is ready ; Write character ; Restore registers ; Return from trap (JMP R 7, actually) ; Address of display status register ; Address of display data register

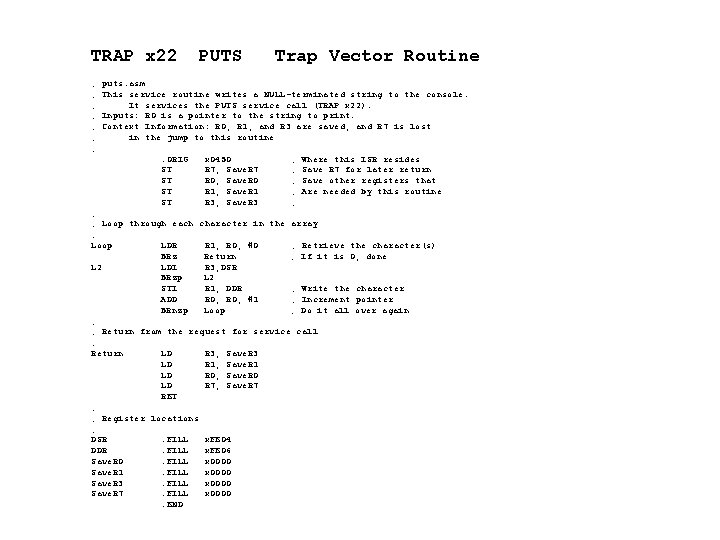

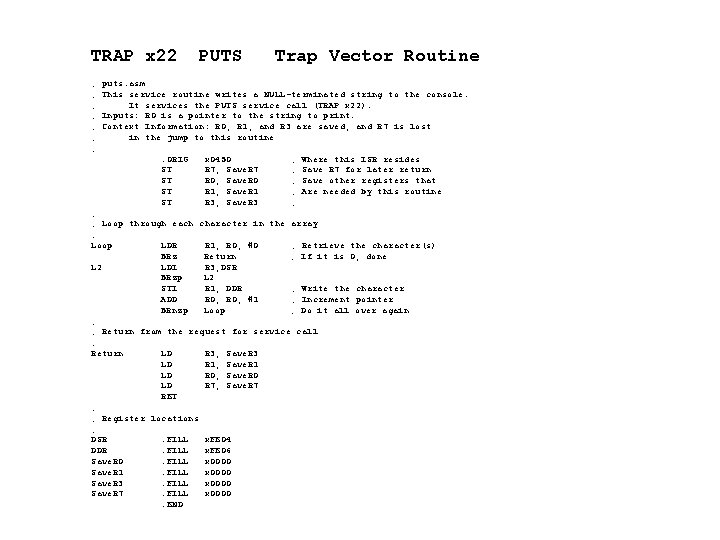

TRAP x 22 ; ; ; ; PUTS Trap Vector Routine puts. asm This service routine writes a NULL-terminated string to the console. It services the PUTS service call (TRAP x 22). Inputs: R 0 is a pointer to the string to print. Context Information: R 0, R 1, and R 3 are saved, and R 7 is lost in the jump to this routine. ORIG ST ST x 0450 R 7, Save. R 7 R 0, Save. R 0 R 1, Save. R 1 R 3, Save. R 3 ; ; ; Where this ISR resides Save R 7 for later return Save other registers that Are needed by this routine ; ; Loop through each character in the array ; Loop LDR R 1, R 0, #0 ; Retrieve the character(s) BRz Return ; If it is 0, done L 2 LDI R 3, DSR BRzp L 2 STI R 1, DDR ; Write the character ADD R 0, #1 ; Increment pointer BRnzp Loop ; Do it all over again ; ; Return from the request for service call ; Return LD R 3, Save. R 3 LD R 1, Save. R 1 LD R 0, Save. R 0 LD R 7, Save. R 7 RET ; ; Register locations ; DSR. FILL x. FE 04 DDR. FILL x. FE 06 Save. R 0. FILL x 0000 Save. R 1. FILL x 0000 Save. R 3. FILL x 0000 Save. R 7. FILL x 0000. END

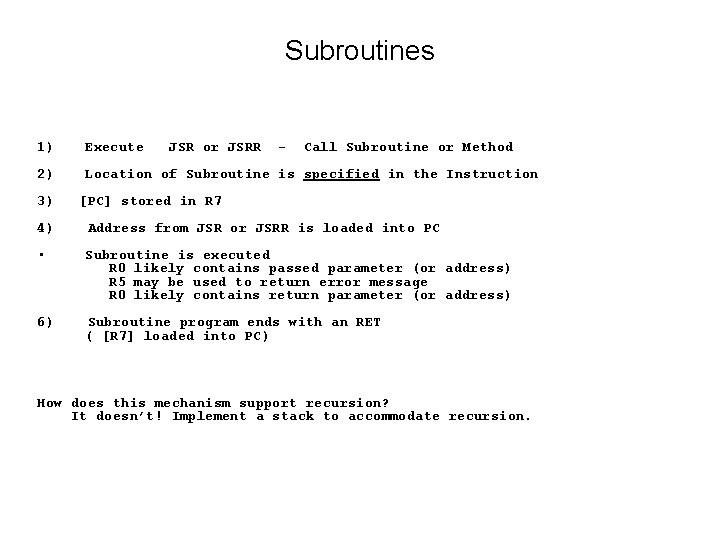

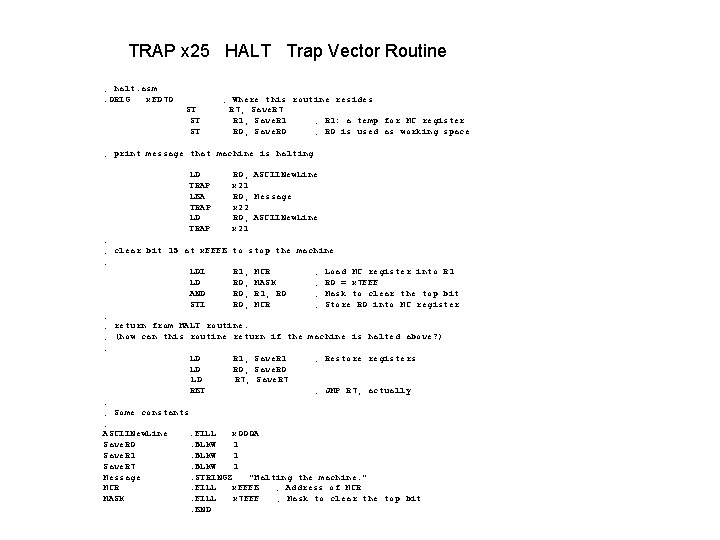

TRAP x 25 HALT Trap Vector Routine ; halt. asm. ORIG x. FD 70 ST ST ST ; Where this routine resides R 7, Save. R 7 R 1, Save. R 1 ; R 1: a temp for MC register R 0, Save. R 0 ; R 0 is used as working space ; print message that machine is halting LD TRAP LEA TRAP LD TRAP R 0, ASCIINew. Line x 21 R 0, Message x 22 R 0, ASCIINew. Line x 21 ; ; clear bit 15 at x. FFFE to stop the machine ; LDI R 1, MCR ; Load MC register into R 1 LD R 0, MASK ; R 0 = x 7 FFF AND R 0, R 1, R 0 ; Mask to clear the top bit STI R 0, MCR ; Store R 0 into MC register ; ; return from HALT routine. ; (how can this routine return if the machine is halted above? ) ; LD R 1, Save. R 1 ; Restore registers LD R 0, Save. R 0 LD R 7, Save. R 7 RET ; JMP R 7, actually ; ; Some constants ; ASCIINew. Line. FILL x 000 A Save. R 0. BLKW 1 Save. R 1. BLKW 1 Save. R 7. BLKW 1 Message. STRINGZ "Halting the machine. " MCR. FILL x. FFFE ; Address of MCR MASK. FILL x 7 FFF ; Mask to clear the top bit. END