Polled IO versus Interrupt Driven IO Polled InputOutput

- Slides: 26

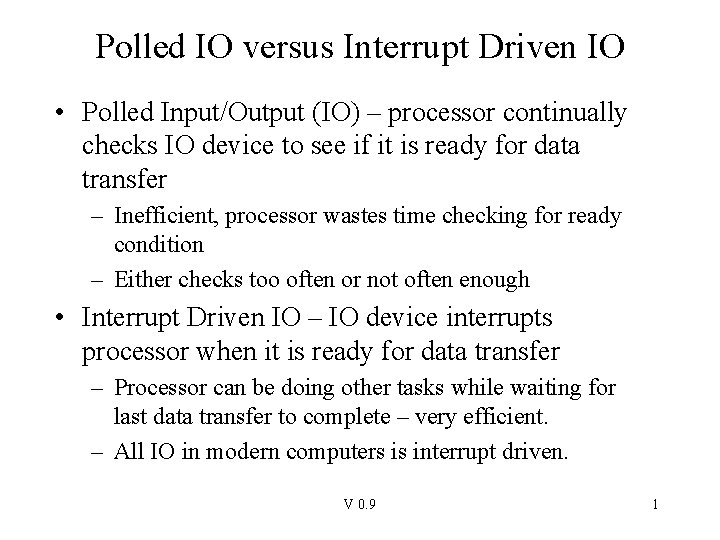

Polled IO versus Interrupt Driven IO • Polled Input/Output (IO) – processor continually checks IO device to see if it is ready for data transfer – Inefficient, processor wastes time checking for ready condition – Either checks too often or not often enough • Interrupt Driven IO – IO device interrupts processor when it is ready for data transfer – Processor can be doing other tasks while waiting for last data transfer to complete – very efficient. – All IO in modern computers is interrupt driven. V 0. 9 1

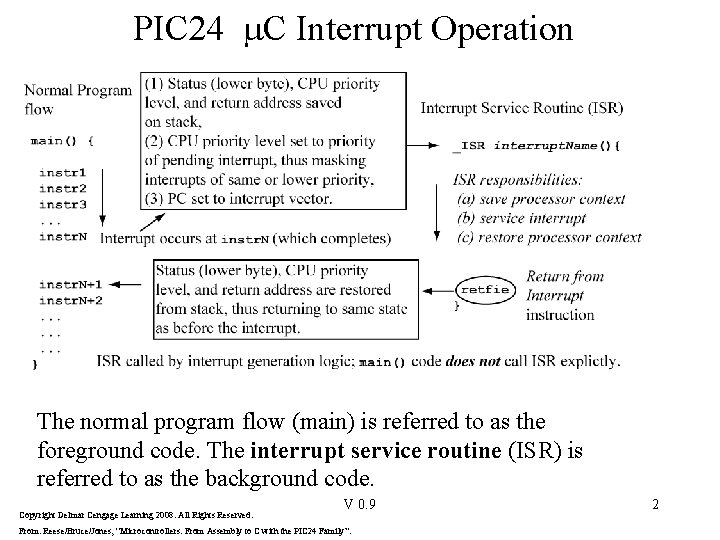

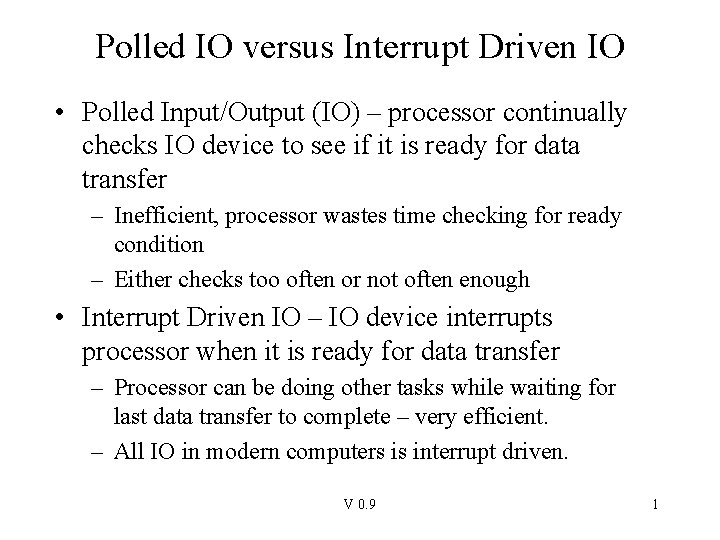

PIC 24 C Interrupt Operation The normal program flow (main) is referred to as the foreground code. The interrupt service routine (ISR) is referred to as the background code. Copyright Delmar Cengage Learning 2008. All Rights Reserved. V 0. 9 From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. 2

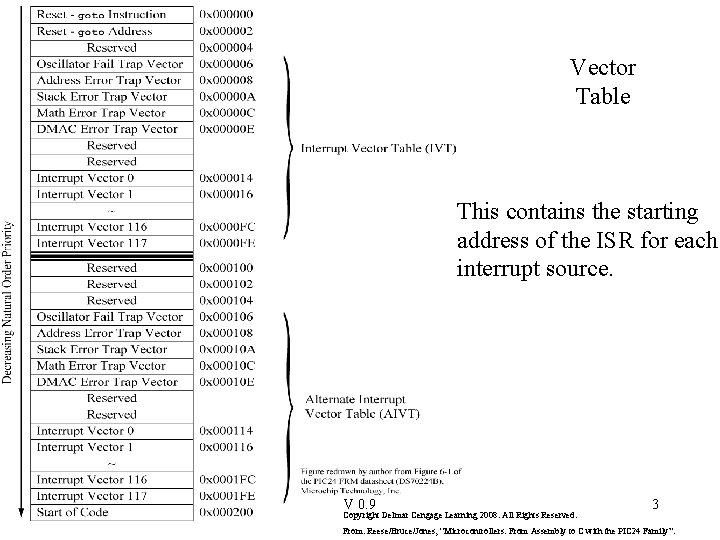

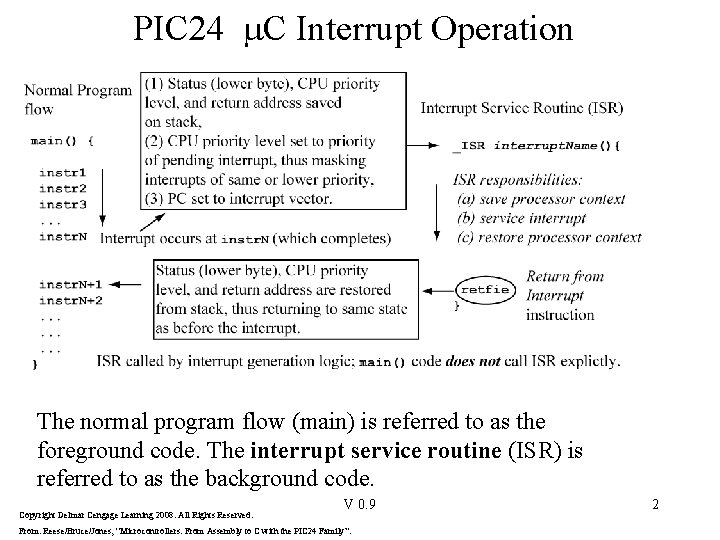

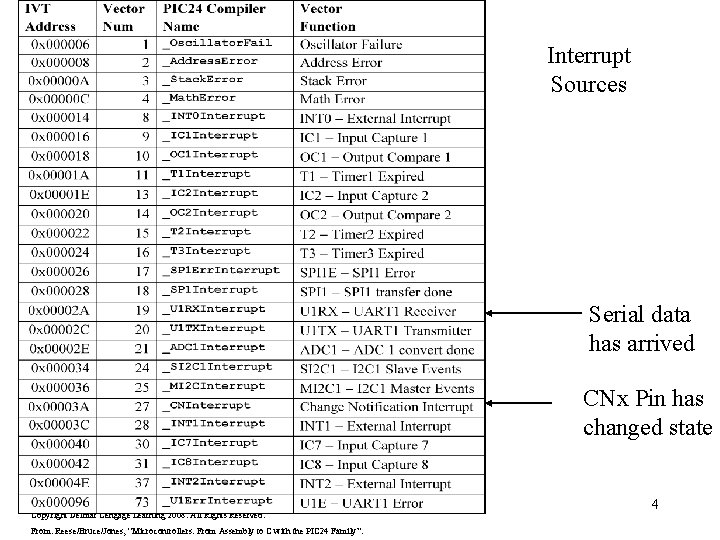

Vector Table This contains the starting address of the ISR for each interrupt source. V 0. 9 Copyright Delmar Cengage Learning 2008. All Rights Reserved. 3 From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”.

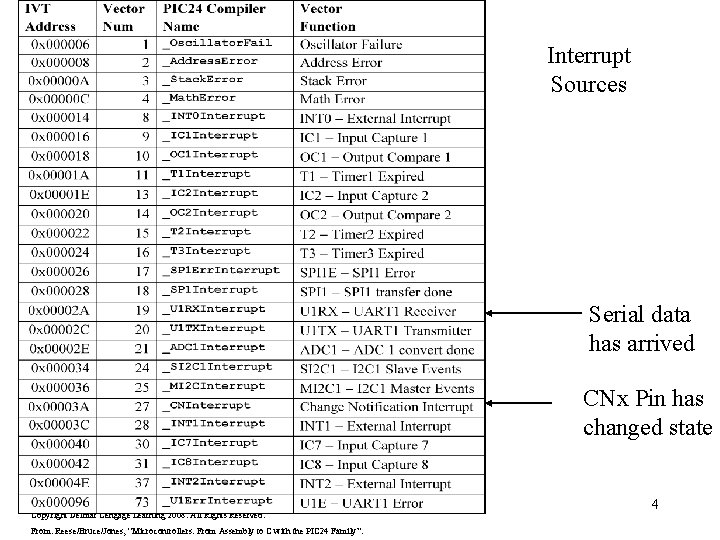

Interrupt Sources Serial data has arrived CNx Pin has changed state Copyright Delmar Cengage Learning 2008. All Rights Reserved. V 0. 9 From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. 4

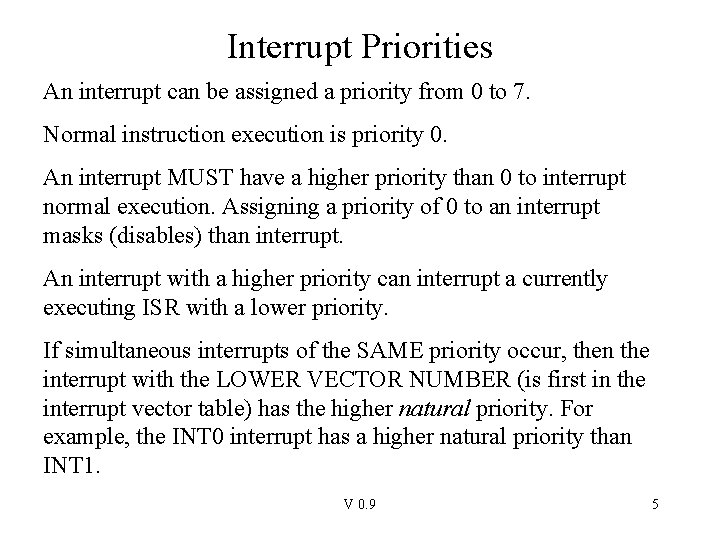

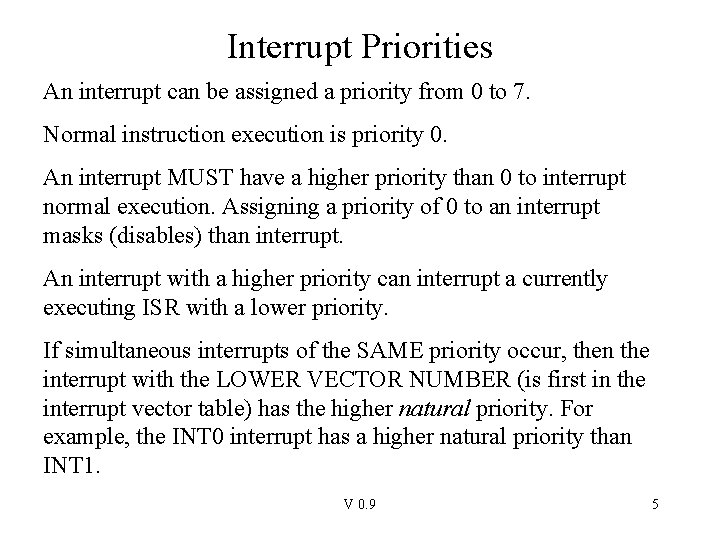

Interrupt Priorities An interrupt can be assigned a priority from 0 to 7. Normal instruction execution is priority 0. An interrupt MUST have a higher priority than 0 to interrupt normal execution. Assigning a priority of 0 to an interrupt masks (disables) than interrupt. An interrupt with a higher priority can interrupt a currently executing ISR with a lower priority. If simultaneous interrupts of the SAME priority occur, then the interrupt with the LOWER VECTOR NUMBER (is first in the interrupt vector table) has the higher natural priority. For example, the INT 0 interrupt has a higher natural priority than INT 1. V 0. 9 5

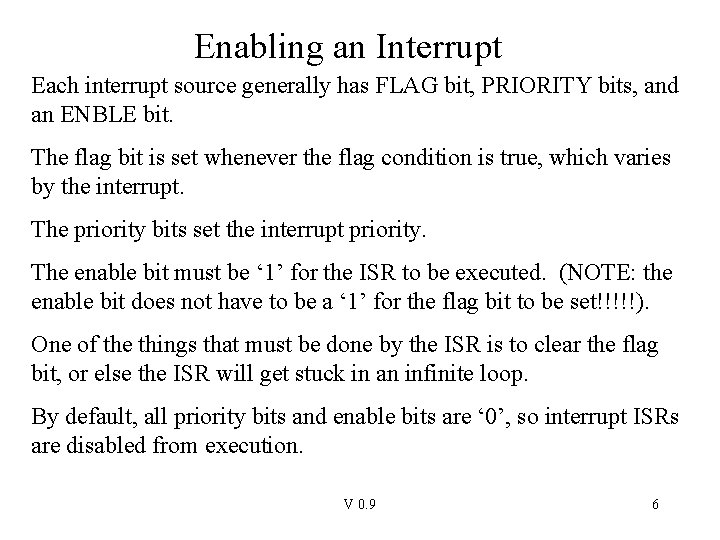

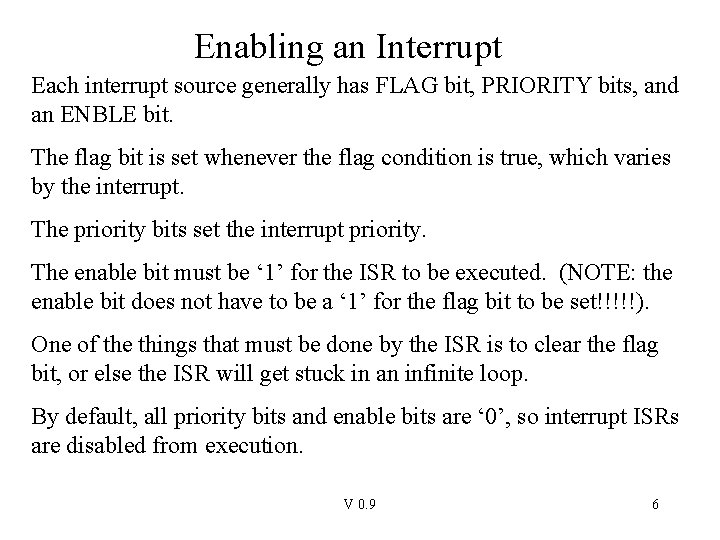

Enabling an Interrupt Each interrupt source generally has FLAG bit, PRIORITY bits, and an ENBLE bit. The flag bit is set whenever the flag condition is true, which varies by the interrupt. The priority bits set the interrupt priority. The enable bit must be ‘ 1’ for the ISR to be executed. (NOTE: the enable bit does not have to be a ‘ 1’ for the flag bit to be set!!!!!). One of the things that must be done by the ISR is to clear the flag bit, or else the ISR will get stuck in an infinite loop. By default, all priority bits and enable bits are ‘ 0’, so interrupt ISRs are disabled from execution. V 0. 9 6

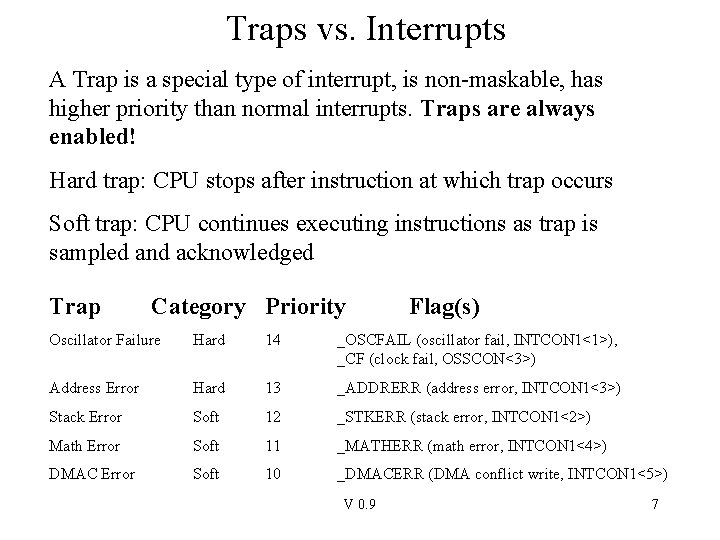

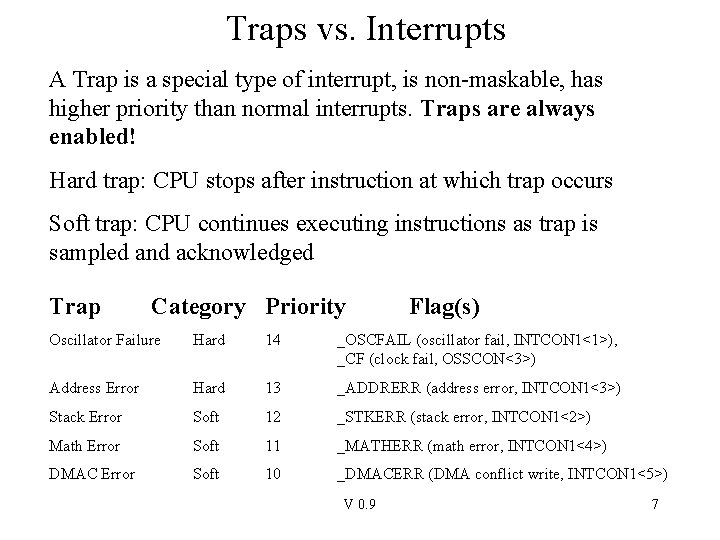

Traps vs. Interrupts A Trap is a special type of interrupt, is non-maskable, has higher priority than normal interrupts. Traps are always enabled! Hard trap: CPU stops after instruction at which trap occurs Soft trap: CPU continues executing instructions as trap is sampled and acknowledged Trap Category Priority Flag(s) Oscillator Failure Hard 14 _OSCFAIL (oscillator fail, INTCON 1<1>), _CF (clock fail, OSSCON<3>) Address Error Hard 13 _ADDRERR (address error, INTCON 1<3>) Stack Error Soft 12 _STKERR (stack error, INTCON 1<2>) Math Error Soft 11 _MATHERR (math error, INTCON 1<4>) DMAC Error Soft 10 _DMACERR (DMA conflict write, INTCON 1<5>) V 0. 9 7

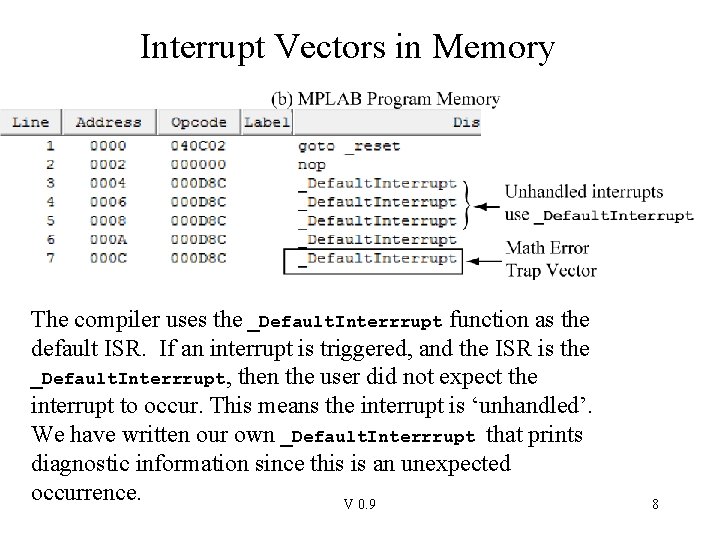

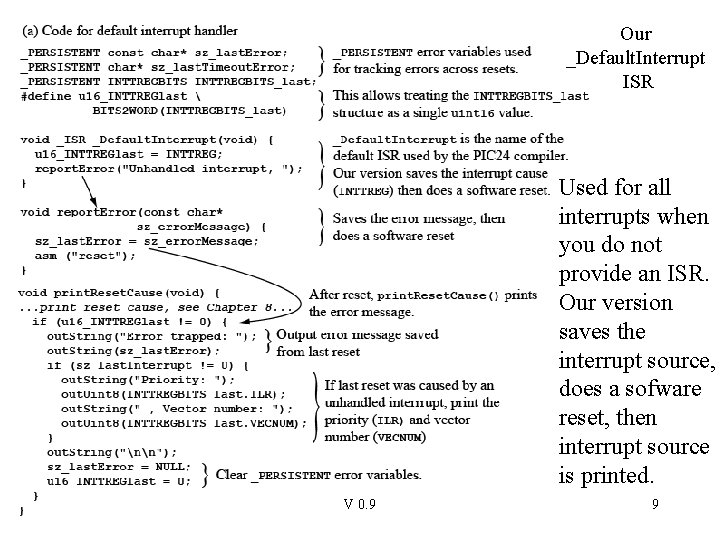

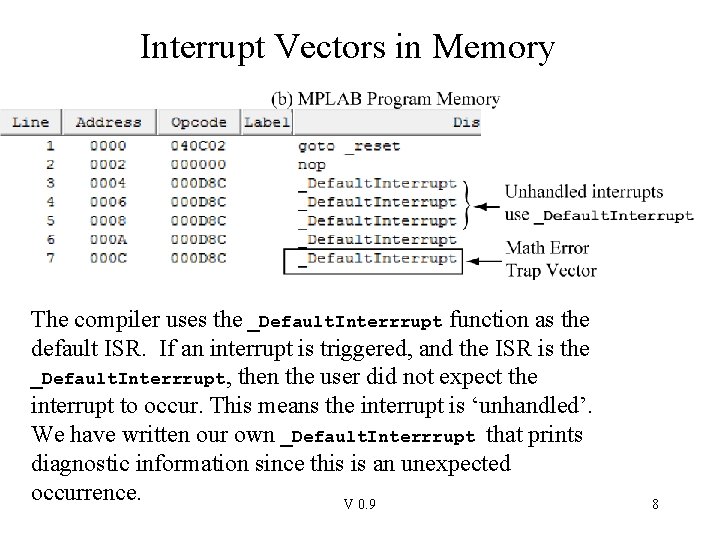

Interrupt Vectors in Memory The compiler uses the _Default. Interrrupt function as the default ISR. If an interrupt is triggered, and the ISR is the _Default. Interrrupt, then the user did not expect the interrupt to occur. This means the interrupt is ‘unhandled’. We have written our own _Default. Interrrupt that prints diagnostic information since this is an unexpected occurrence. V 0. 9 8

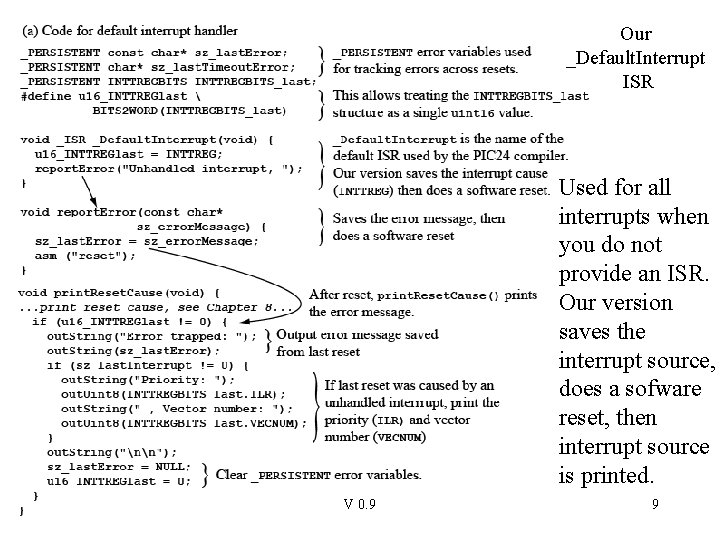

Our _Default. Interrupt ISR Used for all interrupts when you do not provide an ISR. Our version saves the interrupt source, does a sofware reset, then interrupt source is printed. V 0. 9 9

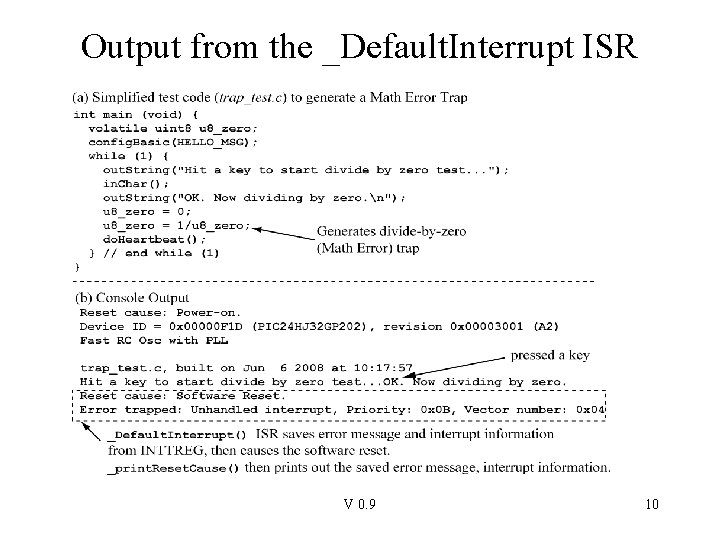

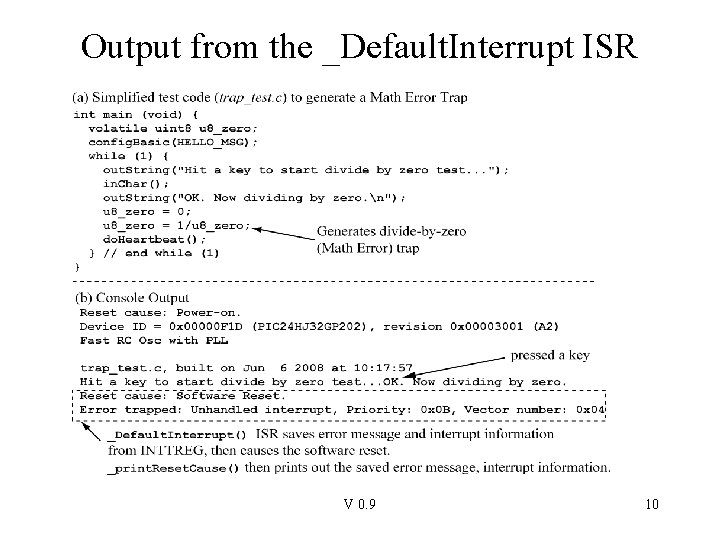

Output from the _Default. Interrupt ISR V 0. 9 10

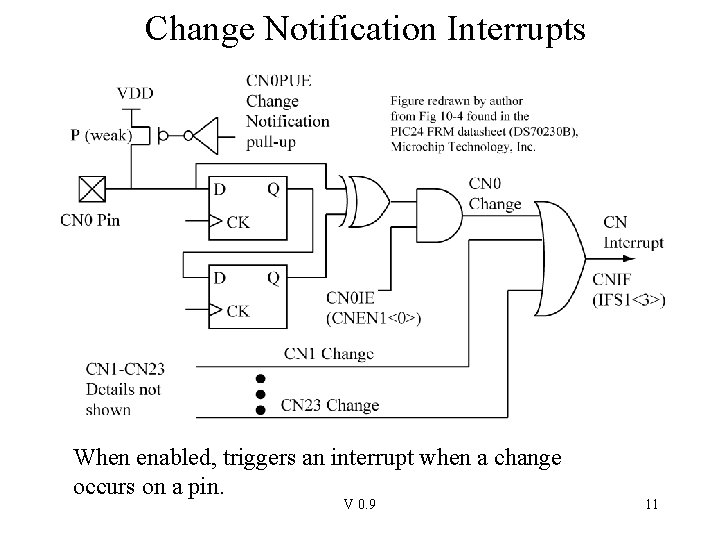

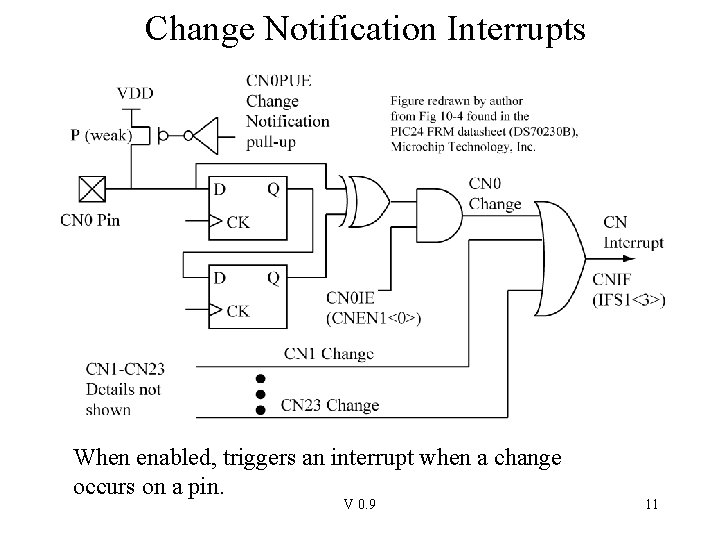

Change Notification Interrupts When enabled, triggers an interrupt when a change occurs on a pin. V 0. 9 11

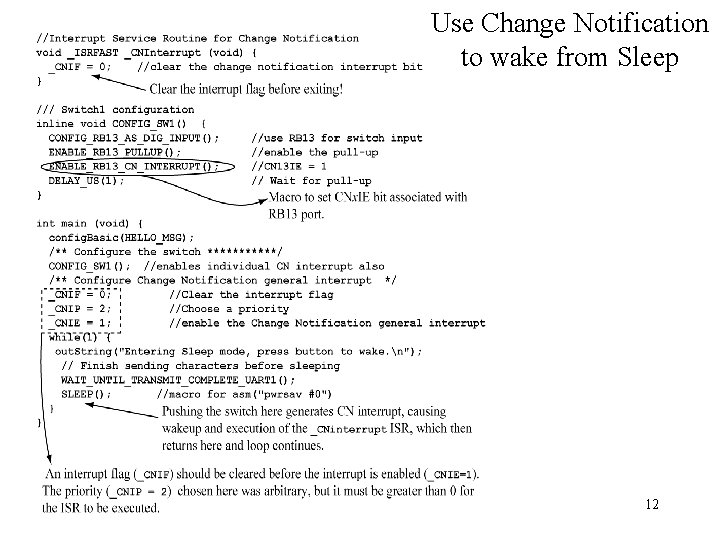

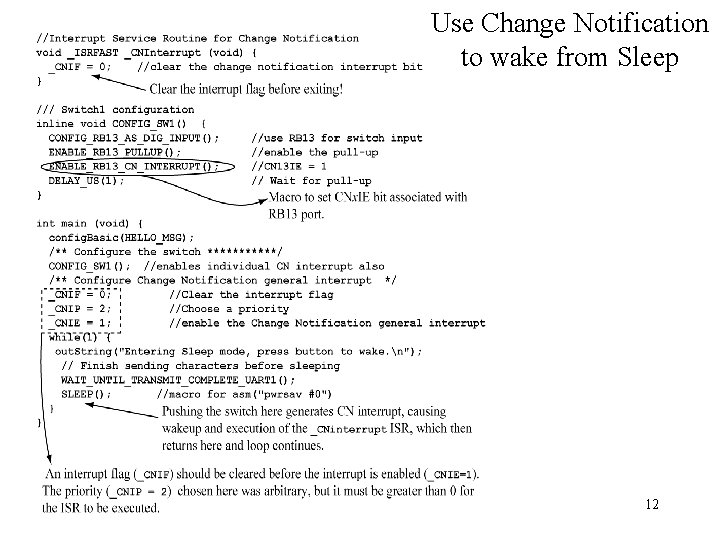

Use Change Notification to wake from Sleep V 0. 9 12

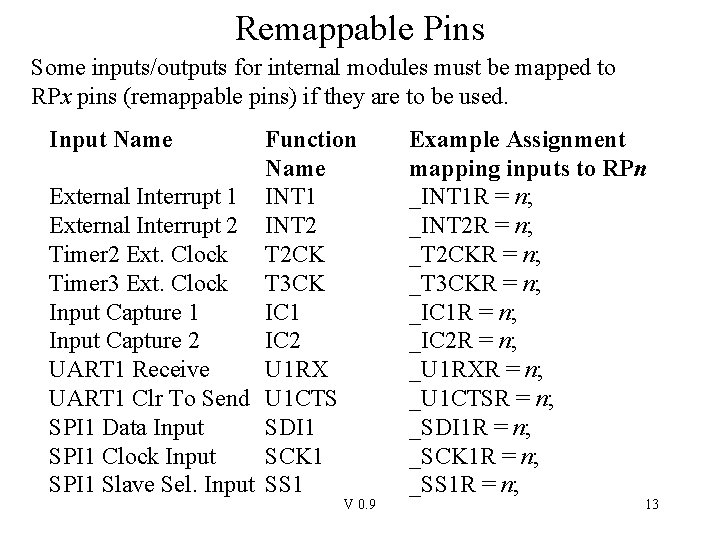

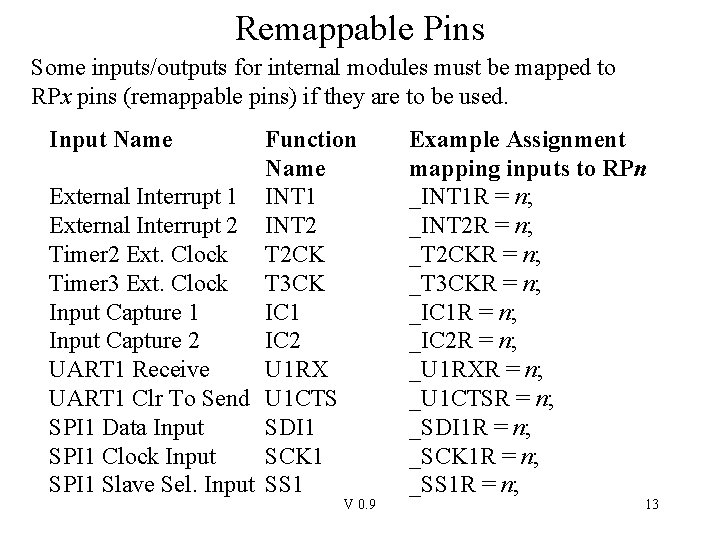

Remappable Pins Some inputs/outputs for internal modules must be mapped to RPx pins (remappable pins) if they are to be used. Input Name Function Name External Interrupt 1 INT 1 External Interrupt 2 INT 2 Timer 2 Ext. Clock T 2 CK Timer 3 Ext. Clock T 3 CK Input Capture 1 IC 1 Input Capture 2 IC 2 UART 1 Receive U 1 RX UART 1 Clr To Send U 1 CTS SPI 1 Data Input SDI 1 SPI 1 Clock Input SCK 1 SPI 1 Slave Sel. Input SS 1 V 0. 9 Example Assignment mapping inputs to RPn _INT 1 R = n; _INT 2 R = n; _T 2 CKR = n; _T 3 CKR = n; _IC 1 R = n; _IC 2 R = n; _U 1 RXR = n; _U 1 CTSR = n; _SDI 1 R = n; _SCK 1 R = n; _SS 1 R = n; 13

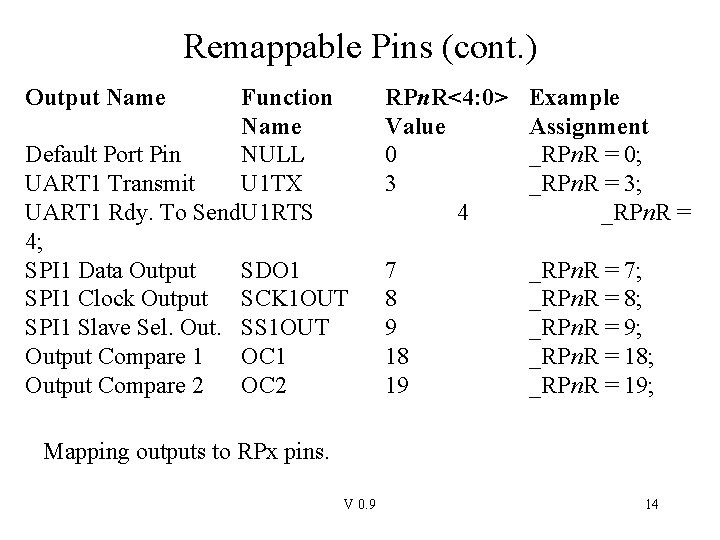

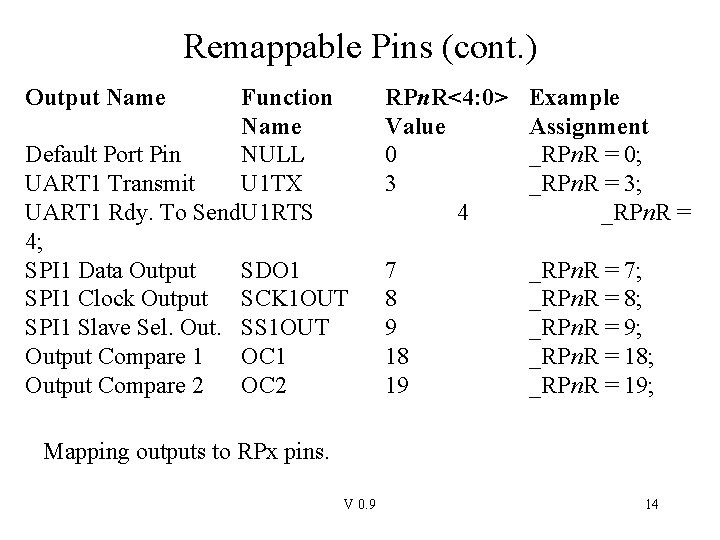

Remappable Pins (cont. ) Output Name Function Name Default Port Pin NULL UART 1 Transmit U 1 TX UART 1 Rdy. To Send. U 1 RTS 4; SPI 1 Data Output SDO 1 SPI 1 Clock Output SCK 1 OUT SPI 1 Slave Sel. Out. SS 1 OUT Output Compare 1 OC 1 Output Compare 2 OC 2 RPn. R<4: 0> Value 0 3 4 Example Assignment _RPn. R = 0; _RPn. R = 3; _RPn. R = 7 8 9 18 19 _RPn. R = 7; _RPn. R = 8; _RPn. R = 9; _RPn. R = 18; _RPn. R = 19; Mapping outputs to RPx pins. V 0. 9 14

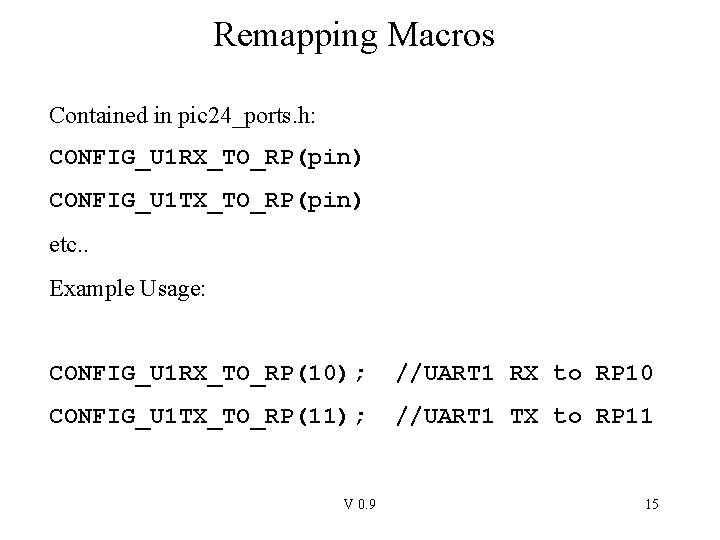

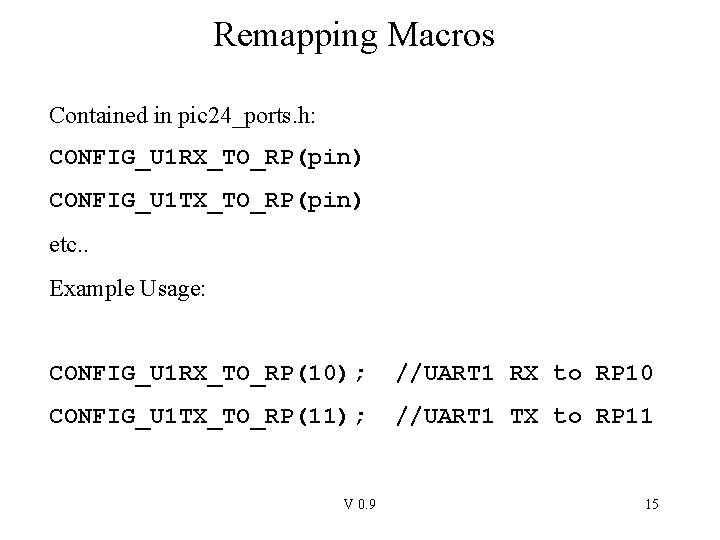

Remapping Macros Contained in pic 24_ports. h: CONFIG_U 1 RX_TO_RP(pin) CONFIG_U 1 TX_TO_RP(pin) etc. . Example Usage: CONFIG_U 1 RX_TO_RP(10); //UART 1 RX to RP 10 CONFIG_U 1 TX_TO_RP(11); //UART 1 TX to RP 11 V 0. 9 15

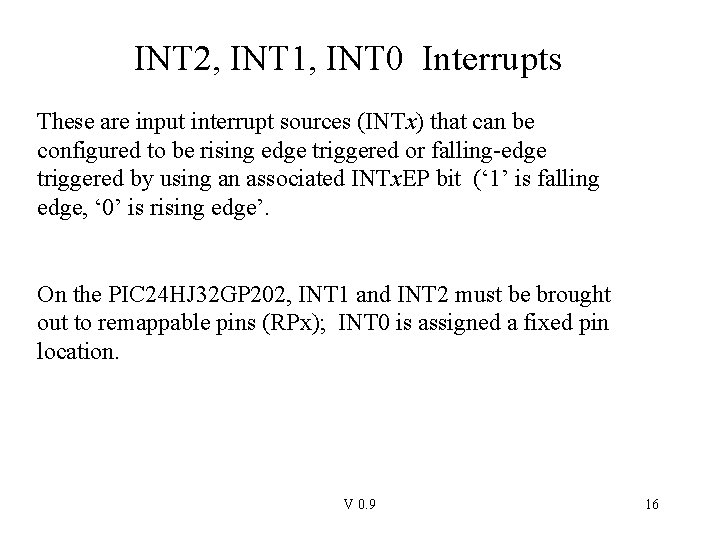

INT 2, INT 1, INT 0 Interrupts These are input interrupt sources (INTx) that can be configured to be rising edge triggered or falling-edge triggered by using an associated INTx. EP bit (‘ 1’ is falling edge, ‘ 0’ is rising edge’. On the PIC 24 HJ 32 GP 202, INT 1 and INT 2 must be brought out to remappable pins (RPx); INT 0 is assigned a fixed pin location. V 0. 9 16

//Interrupt Service Routine for INT 1 void _ISRFAST _INT 1 Interrupt (void) { _INT 1 IF = 0; //clear the interrupt bit } /// Switch 1 configuration, use RB 13 inline void CONFIG_SW 1() { CONFIG_RB 13_AS_DIG_INPUT(); //use RB 13 for switch input ENABLE_RB 13_PULLUP(); //enable the pullup DELAY_US(1); // Wait for pull-up } int main (void) { Use INT 1 to wake config. Basic(HELLO_MSG); /** Configure the switch ******/ from Sleep mode CONFIG_SW 1(); CONFIG_INT 1_TO_RP(13); //map INT 1 to RP 13 /** Configure INT 1 interrupt */ _INT 1 IF = 0; //Clear the interrupt flag _INT 1 IP = 2; //Choose a priority _INT 1 EP = 1; //negative edge triggerred _INT 1 IE = 1; //enable INT 1 interrupt while(1) { out. String("Entering Sleep mode, press button to wake. n"); //finish sending characters before sleeping WAIT_UNTIL_TRANSMIT_COMPLETE_UART 1(); SLEEP(); //macro for asm("pwrsav #0") } V 0. 9 17 }

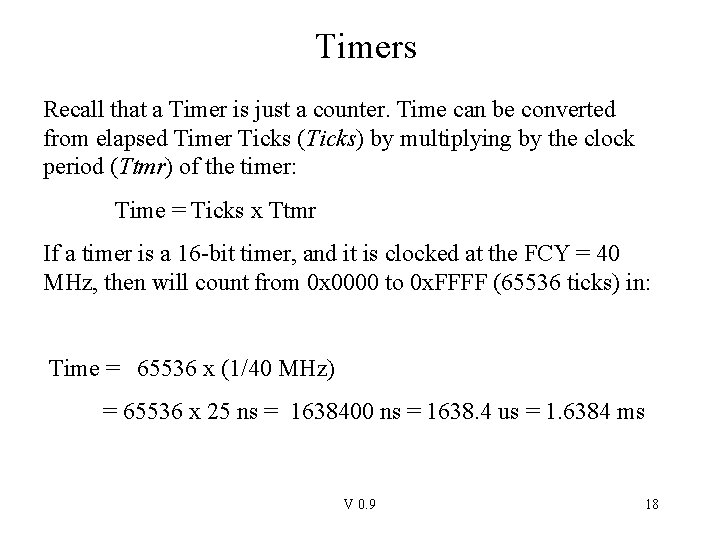

Timers Recall that a Timer is just a counter. Time can be converted from elapsed Timer Ticks (Ticks) by multiplying by the clock period (Ttmr) of the timer: Time = Ticks x Ttmr If a timer is a 16 -bit timer, and it is clocked at the FCY = 40 MHz, then will count from 0 x 0000 to 0 x. FFFF (65536 ticks) in: Time = 65536 x (1/40 MHz) = 65536 x 25 ns = 1638400 ns = 1638. 4 us = 1. 6384 ms V 0. 9 18

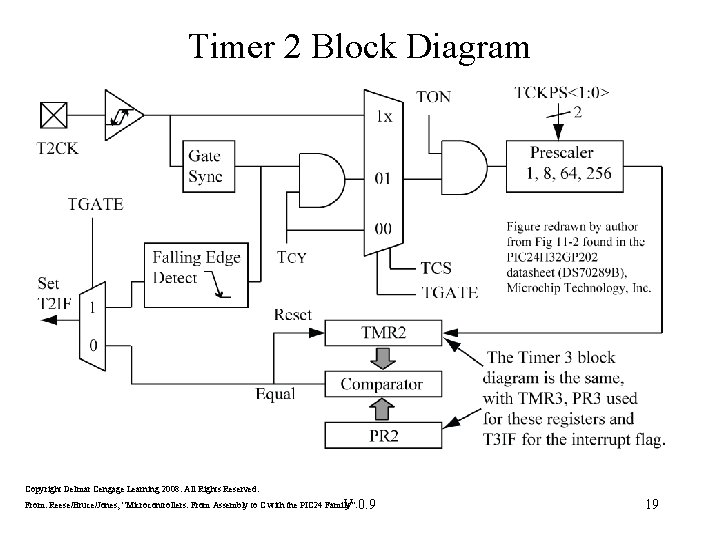

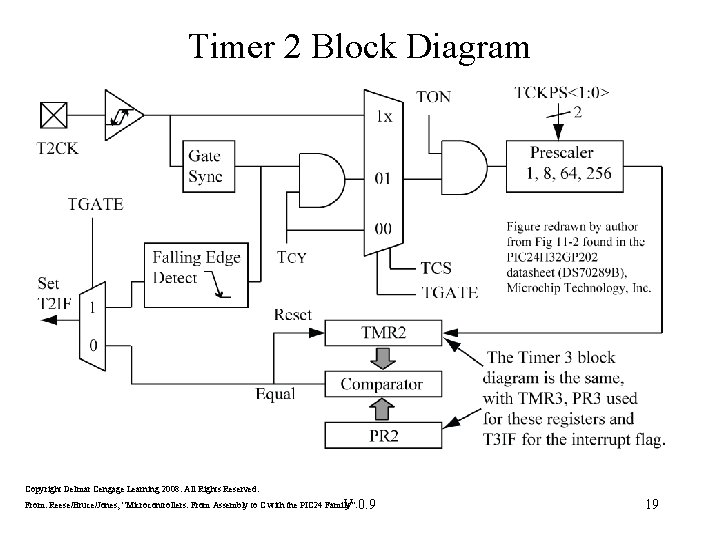

Timer 2 Block Diagram Copyright Delmar Cengage Learning 2008. All Rights Reserved. From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. V 0. 9 19

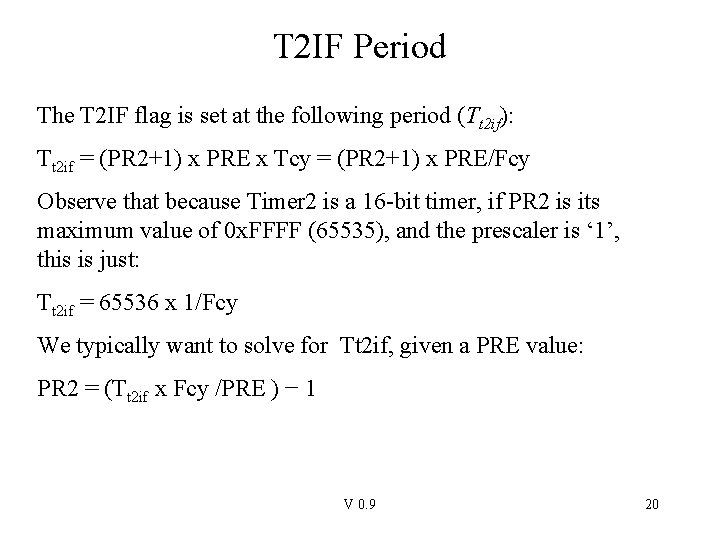

T 2 IF Period The T 2 IF flag is set at the following period (Tt 2 if): Tt 2 if = (PR 2+1) x PRE x Tcy = (PR 2+1) x PRE/Fcy Observe that because Timer 2 is a 16 -bit timer, if PR 2 is its maximum value of 0 x. FFFF (65535), and the prescaler is ‘ 1’, this is just: Tt 2 if = 65536 x 1/Fcy We typically want to solve for Tt 2 if, given a PRE value: PR 2 = (Tt 2 if x Fcy /PRE ) − 1 V 0. 9 20

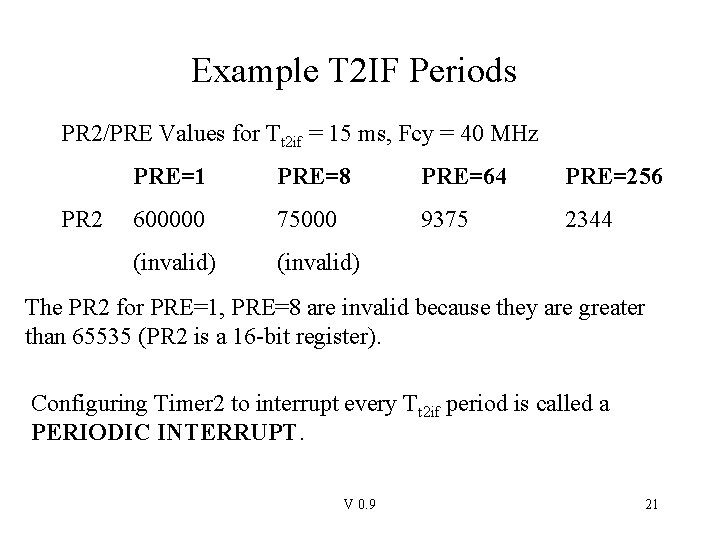

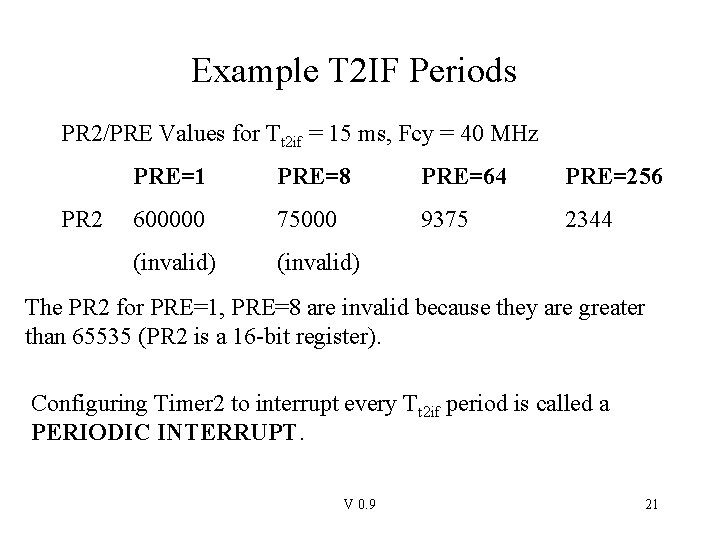

Example T 2 IF Periods PR 2/PRE Values for Tt 2 if = 15 ms, Fcy = 40 MHz PR 2 PRE=1 PRE=8 PRE=64 PRE=256 600000 75000 9375 2344 (invalid) The PR 2 for PRE=1, PRE=8 are invalid because they are greater than 65535 (PR 2 is a 16 -bit register). Configuring Timer 2 to interrupt every Tt 2 if period is called a PERIODIC INTERRUPT. V 0. 9 21

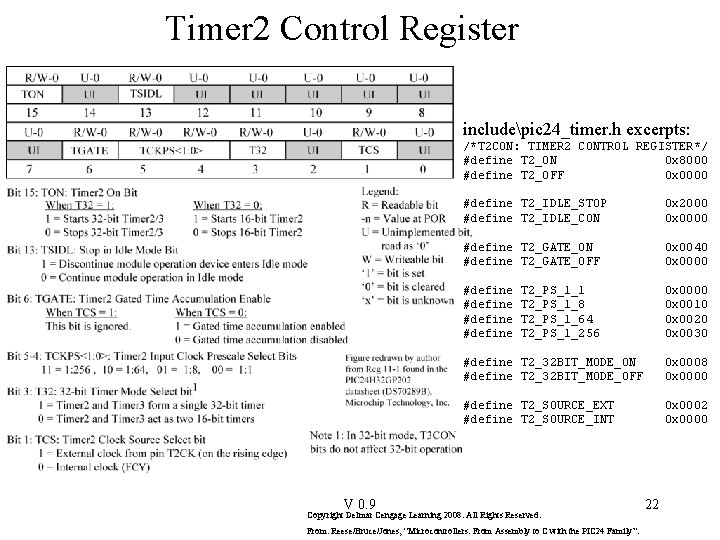

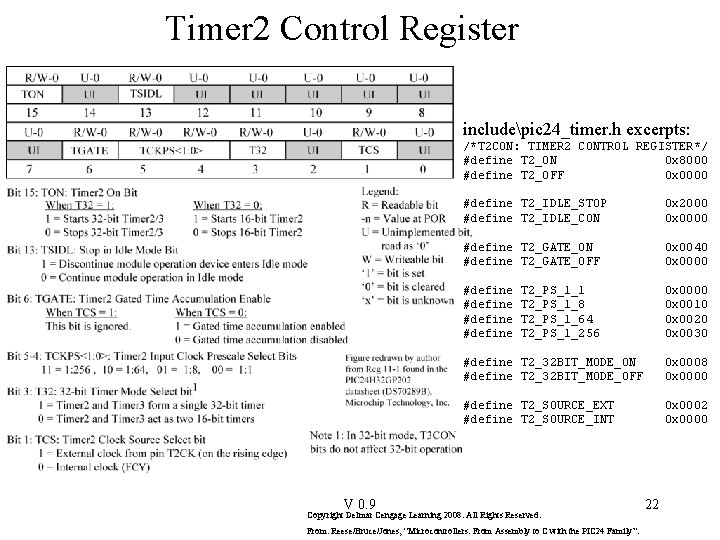

Timer 2 Control Register includepic 24_timer. h excerpts: /*T 2 CON: TIMER 2 CONTROL REGISTER*/ #define T 2_ON 0 x 8000 #define T 2_OFF 0 x 0000 #define T 2_IDLE_STOP #define T 2_IDLE_CON 0 x 2000 0 x 0000 #define T 2_GATE_ON #define T 2_GATE_OFF 0 x 0040 0 x 0000 #define 0 x 0000 0 x 0010 0 x 0020 0 x 0030 T 2_PS_1_1 T 2_PS_1_8 T 2_PS_1_64 T 2_PS_1_256 #define T 2_32 BIT_MODE_ON #define T 2_32 BIT_MODE_OFF 0 x 0008 0 x 0000 #define T 2_SOURCE_EXT #define T 2_SOURCE_INT 0 x 0002 0 x 0000 V 0. 9 Copyright Delmar Cengage Learning 2008. All Rights Reserved. From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. 22

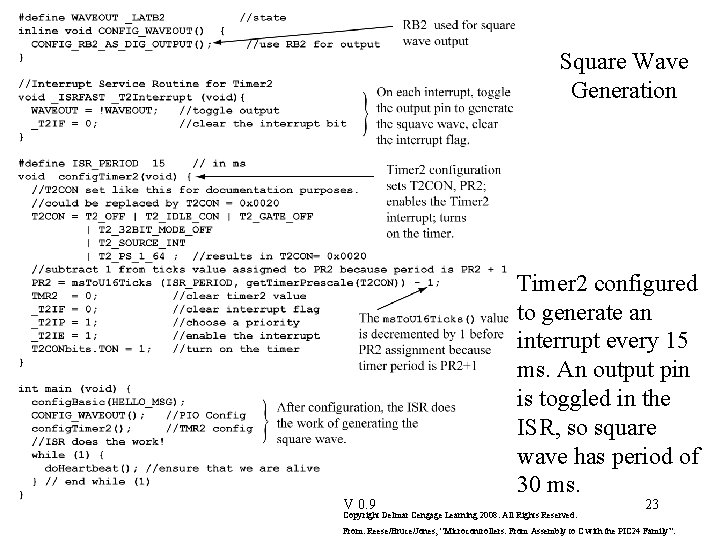

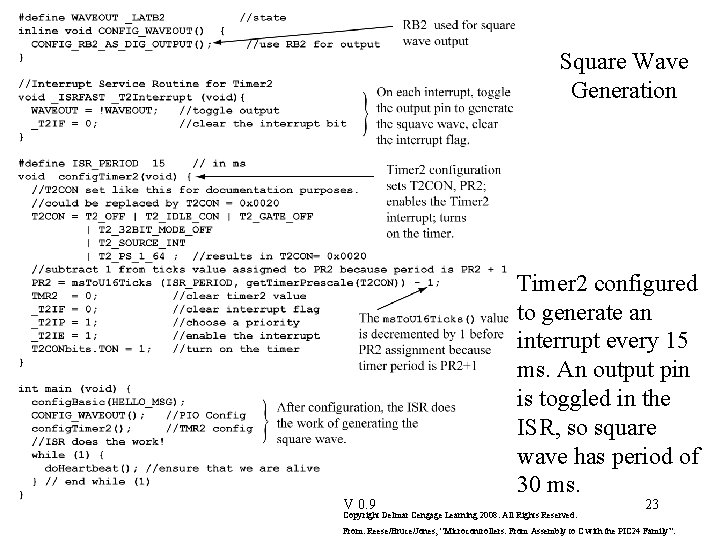

Square Wave Generation V 0. 9 Timer 2 configured to generate an interrupt every 15 ms. An output pin is toggled in the ISR, so square wave has period of 30 ms. Copyright Delmar Cengage Learning 2008. All Rights Reserved. 23 From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”.

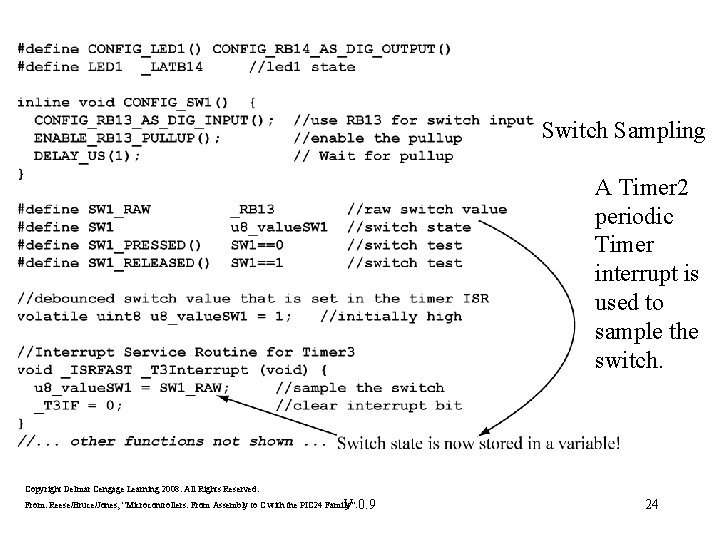

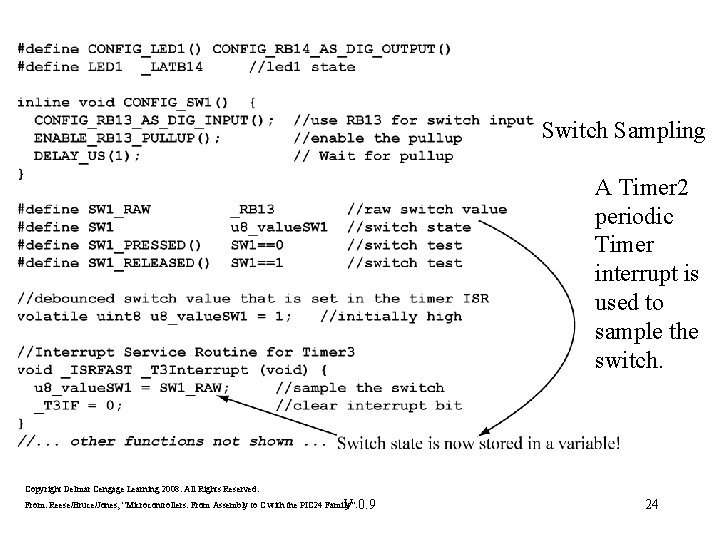

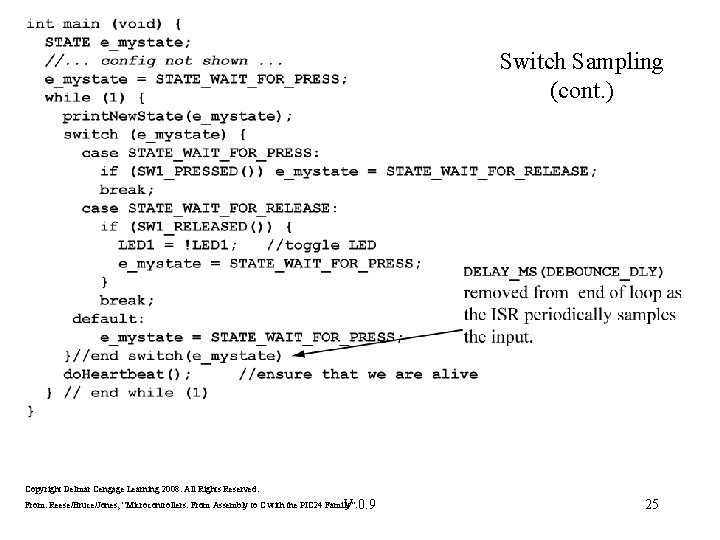

Switch Sampling A Timer 2 periodic Timer interrupt is used to sample the switch. Copyright Delmar Cengage Learning 2008. All Rights Reserved. From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. V 0. 9 24

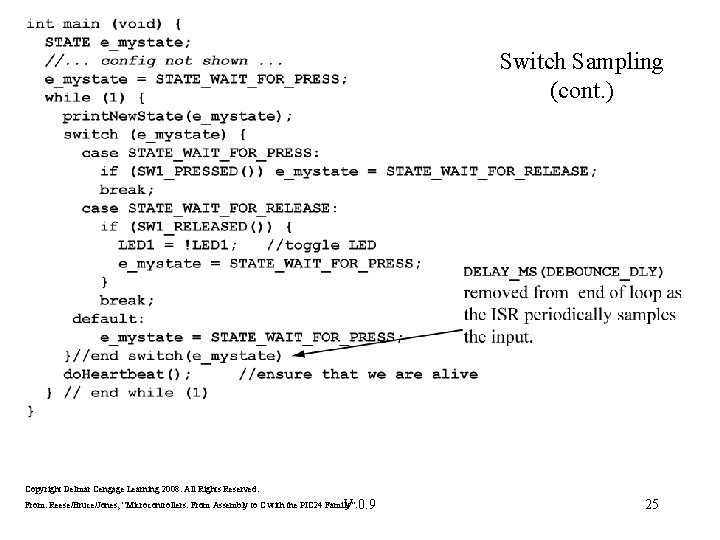

Switch Sampling (cont. ) Copyright Delmar Cengage Learning 2008. All Rights Reserved. From: Reese/Bruce/Jones, “Microcontrollers: From Assembly to C with the PIC 24 Family”. V 0. 9 25

Dividing Work between the ISR and main() There are usually multiple ways to divide work between the ISR and main(). The ‘right’ choice is the one that services the I/O event in a timely manner, and there can be more than right choice. Golden Rules: The ISR should do its work as fast as possible. Do not put long software delays into an ISR. An ISR should never wait for I/O, the I/O event should trigger the ISR! An ISR is never called as a subroutine. V 0. 9 26