More on the Atmega 32 instruction set Basic

More on the Atmega 32 instruction set Basic Instructions CS-280 Dr. Mark L. Hornick 1

Don’t confuse instructions with directives l l l Directives are used by the Assembler as it generates machine code from assembly instructions Directives are not converted to machine instructions Instructions appear in blue in AVRStudio CS-280 Dr. Mark L. Hornick 2

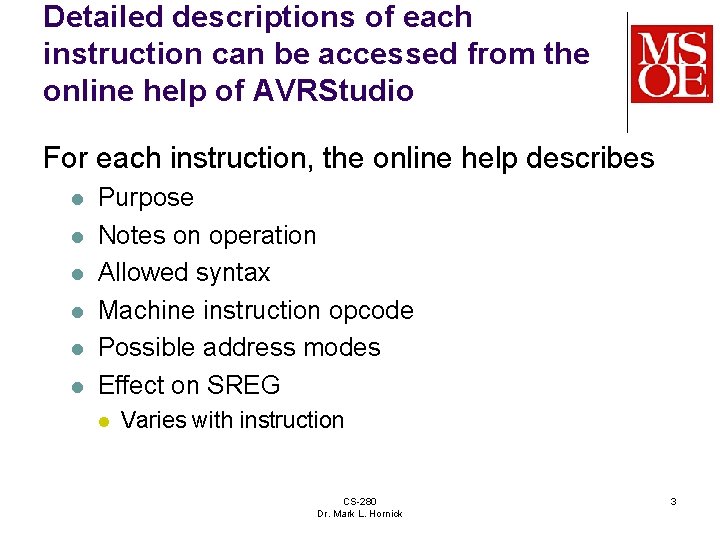

Detailed descriptions of each instruction can be accessed from the online help of AVRStudio For each instruction, the online help describes l l l Purpose Notes on operation Allowed syntax Machine instruction opcode Possible address modes Effect on SREG l Varies with instruction CS-280 Dr. Mark L. Hornick 3

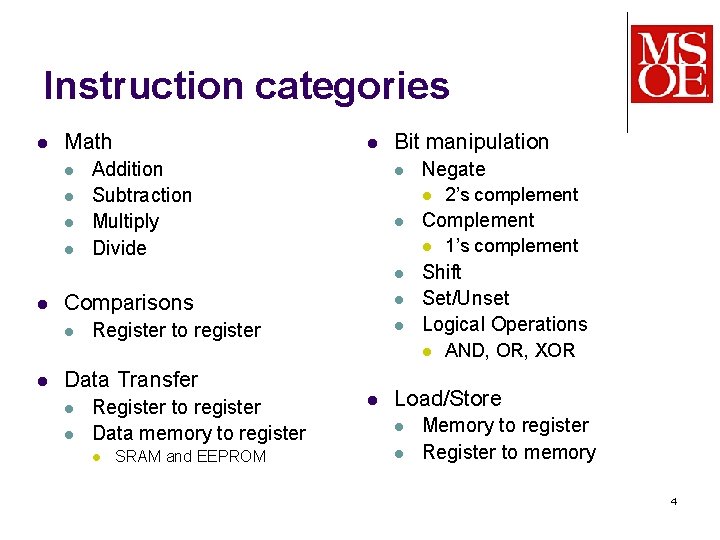

Instruction categories l Math l l l Addition Subtraction Multiply Divide Bit manipulation l l l Comparisons l l l Register to register Data Transfer l l Register to register Data memory to register l SRAM and EEPROM l 1’s complement Shift Set/Unset Logical Operations l l 2’s complement Complement l l l Negate AND, OR, XOR Load/Store l l Memory to register Register to memory 4

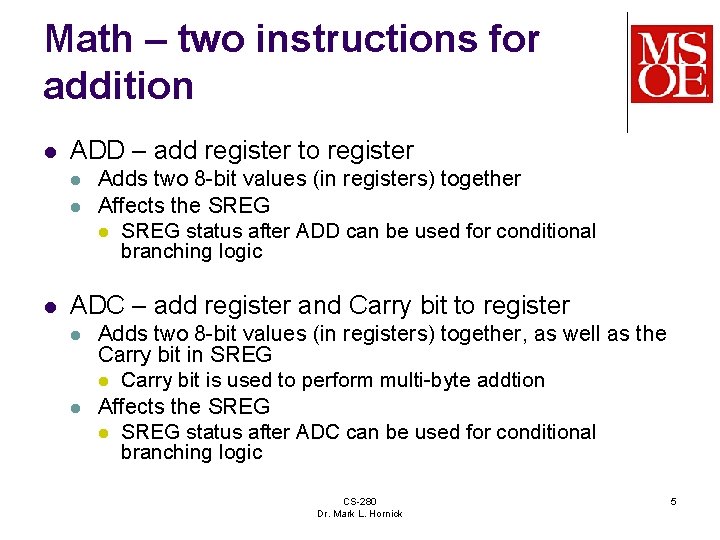

Math – two instructions for addition l ADD – add register to register l l l Adds two 8 -bit values (in registers) together Affects the SREG l SREG status after ADD can be used for conditional branching logic ADC – add register and Carry bit to register l l Adds two 8 -bit values (in registers) together, as well as the Carry bit in SREG l Carry bit is used to perform multi-byte addtion Affects the SREG l SREG status after ADC can be used for conditional branching logic CS-280 Dr. Mark L. Hornick 5

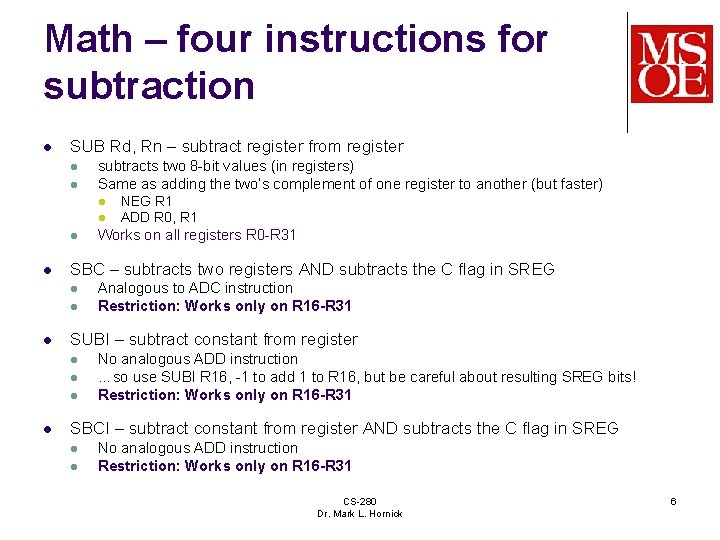

Math – four instructions for subtraction l SUB Rd, Rn – subtract register from register l l subtracts two 8 -bit values (in registers) Same as adding the two’s complement of one register to another (but faster) l l l Analogous to ADC instruction Restriction: Works only on R 16 -R 31 SUBI – subtract constant from register l l Works on all registers R 0 -R 31 SBC – subtracts two registers AND subtracts the C flag in SREG l l NEG R 1 ADD R 0, R 1 No analogous ADD instruction …so use SUBI R 16, -1 to add 1 to R 16, but be careful about resulting SREG bits! Restriction: Works only on R 16 -R 31 SBCI – subtract constant from register AND subtracts the C flag in SREG l l No analogous ADD instruction Restriction: Works only on R 16 -R 31 CS-280 Dr. Mark L. Hornick 6

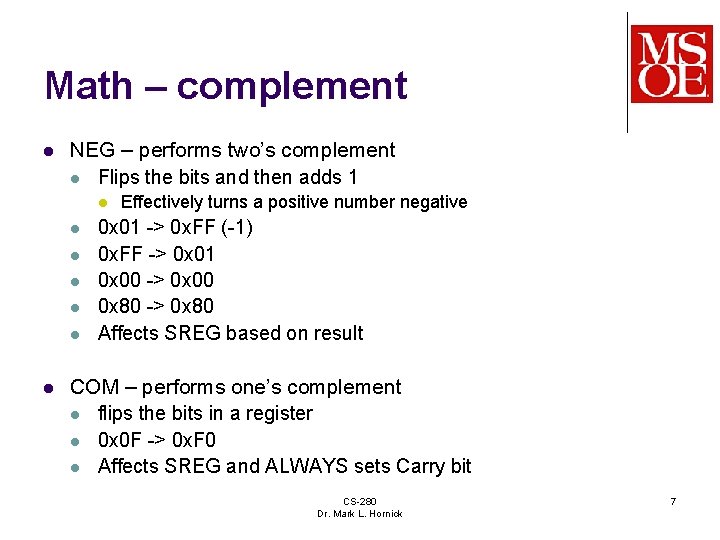

Math – complement l NEG – performs two’s complement l Flips the bits and then adds 1 l l l l Effectively turns a positive number negative 0 x 01 -> 0 x. FF (-1) 0 x. FF -> 0 x 01 0 x 00 -> 0 x 00 0 x 80 -> 0 x 80 Affects SREG based on result COM – performs one’s complement l flips the bits in a register l 0 x 0 F -> 0 x. F 0 l Affects SREG and ALWAYS sets Carry bit CS-280 Dr. Mark L. Hornick 7

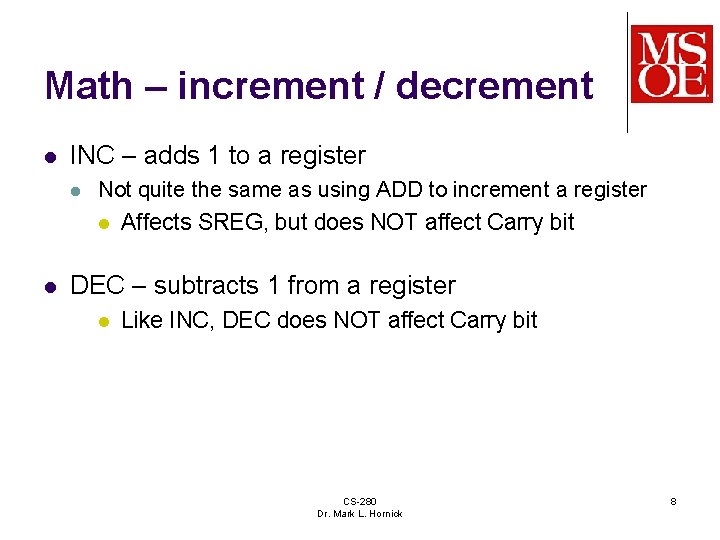

Math – increment / decrement l INC – adds 1 to a register l l Not quite the same as using ADD to increment a register l Affects SREG, but does NOT affect Carry bit DEC – subtracts 1 from a register l Like INC, DEC does NOT affect Carry bit CS-280 Dr. Mark L. Hornick 8

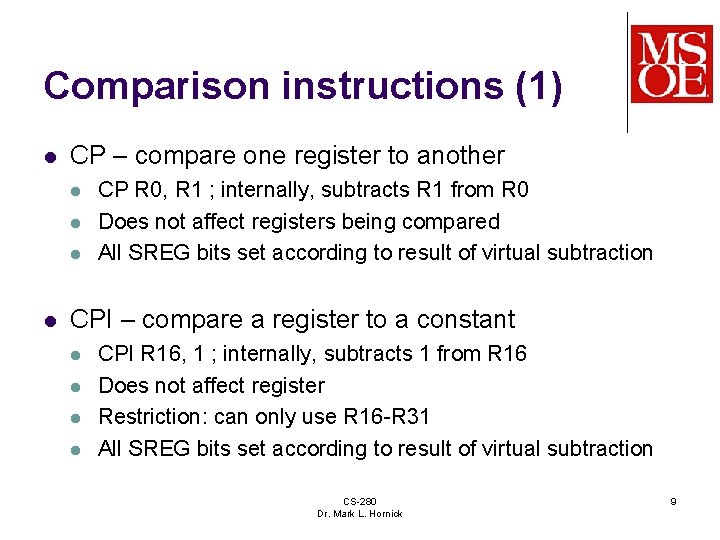

Comparison instructions (1) l CP – compare one register to another l l CP R 0, R 1 ; internally, subtracts R 1 from R 0 Does not affect registers being compared All SREG bits set according to result of virtual subtraction CPI – compare a register to a constant l l CPI R 16, 1 ; internally, subtracts 1 from R 16 Does not affect register Restriction: can only use R 16 -R 31 All SREG bits set according to result of virtual subtraction CS-280 Dr. Mark L. Hornick 9

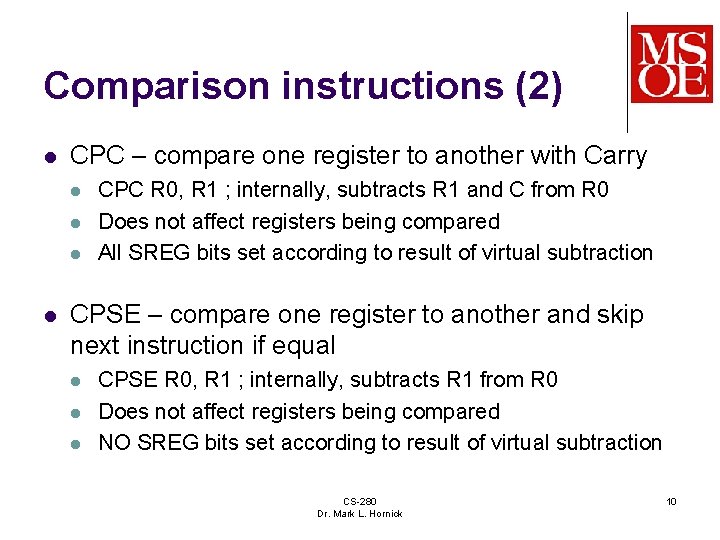

Comparison instructions (2) l CPC – compare one register to another with Carry l l CPC R 0, R 1 ; internally, subtracts R 1 and C from R 0 Does not affect registers being compared All SREG bits set according to result of virtual subtraction CPSE – compare one register to another and skip next instruction if equal l CPSE R 0, R 1 ; internally, subtracts R 1 from R 0 Does not affect registers being compared NO SREG bits set according to result of virtual subtraction CS-280 Dr. Mark L. Hornick 10

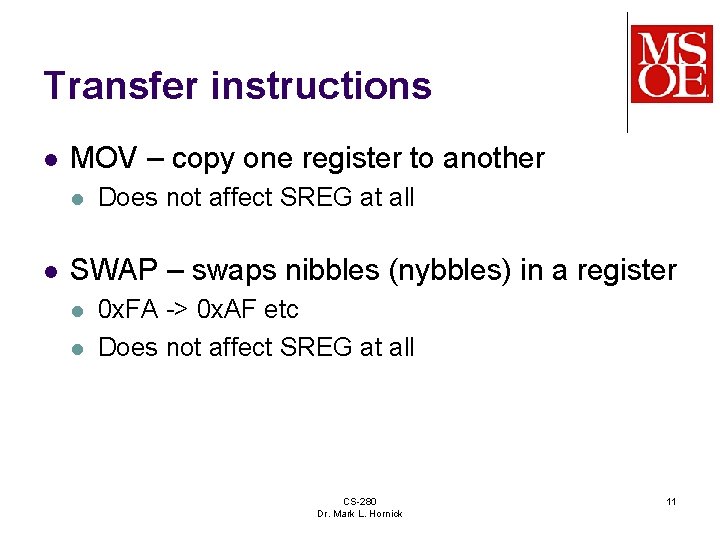

Transfer instructions l MOV – copy one register to another l l Does not affect SREG at all SWAP – swaps nibbles (nybbles) in a register l l 0 x. FA -> 0 x. AF etc Does not affect SREG at all CS-280 Dr. Mark L. Hornick 11

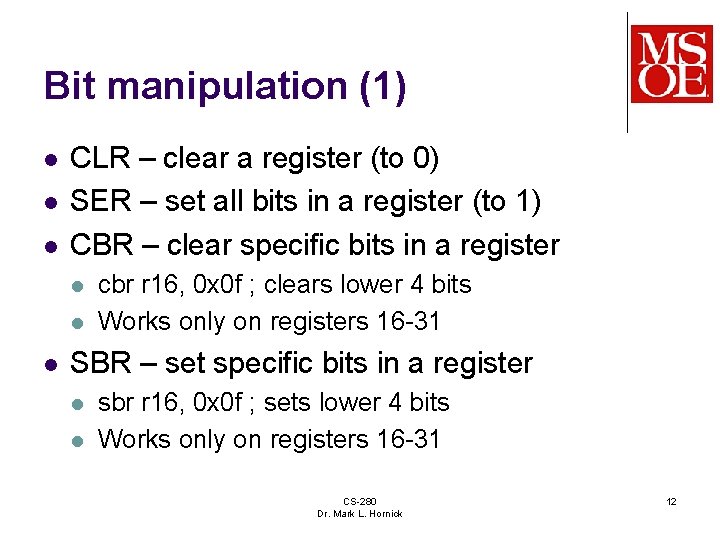

Bit manipulation (1) l l l CLR – clear a register (to 0) SER – set all bits in a register (to 1) CBR – clear specific bits in a register l l l cbr r 16, 0 x 0 f ; clears lower 4 bits Works only on registers 16 -31 SBR – set specific bits in a register l l sbr r 16, 0 x 0 f ; sets lower 4 bits Works only on registers 16 -31 CS-280 Dr. Mark L. Hornick 12

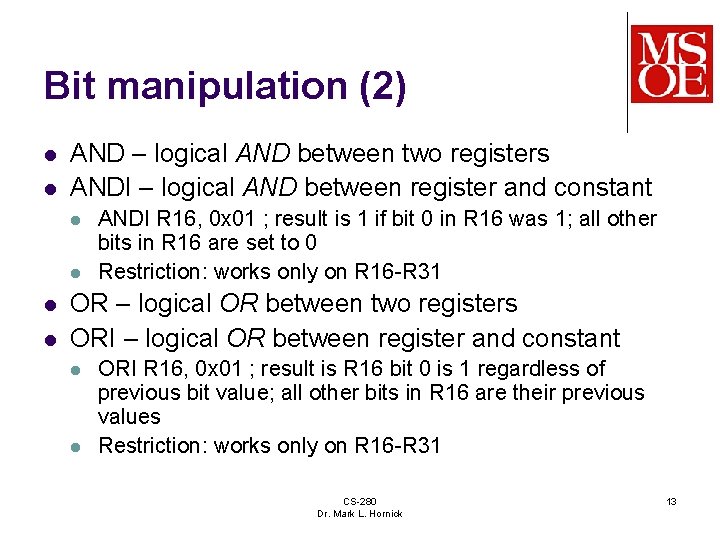

Bit manipulation (2) l l AND – logical AND between two registers ANDI – logical AND between register and constant l l ANDI R 16, 0 x 01 ; result is 1 if bit 0 in R 16 was 1; all other bits in R 16 are set to 0 Restriction: works only on R 16 -R 31 OR – logical OR between two registers ORI – logical OR between register and constant l l ORI R 16, 0 x 01 ; result is R 16 bit 0 is 1 regardless of previous bit value; all other bits in R 16 are their previous values Restriction: works only on R 16 -R 31 CS-280 Dr. Mark L. Hornick 13

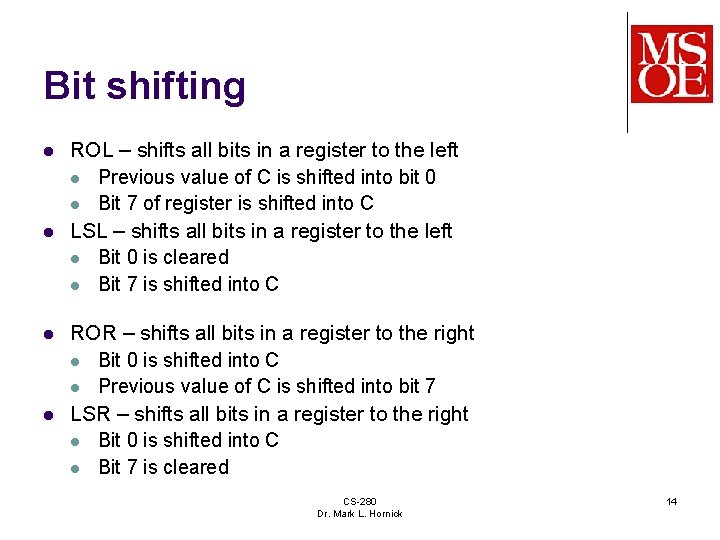

Bit shifting l l ROL – shifts all bits in a register to the left l Previous value of C is shifted into bit 0 l Bit 7 of register is shifted into C LSL – shifts all bits in a register to the left l Bit 0 is cleared l Bit 7 is shifted into C ROR – shifts all bits in a register to the right l Bit 0 is shifted into C l Previous value of C is shifted into bit 7 LSR – shifts all bits in a register to the right l Bit 0 is shifted into C l Bit 7 is cleared CS-280 Dr. Mark L. Hornick 14

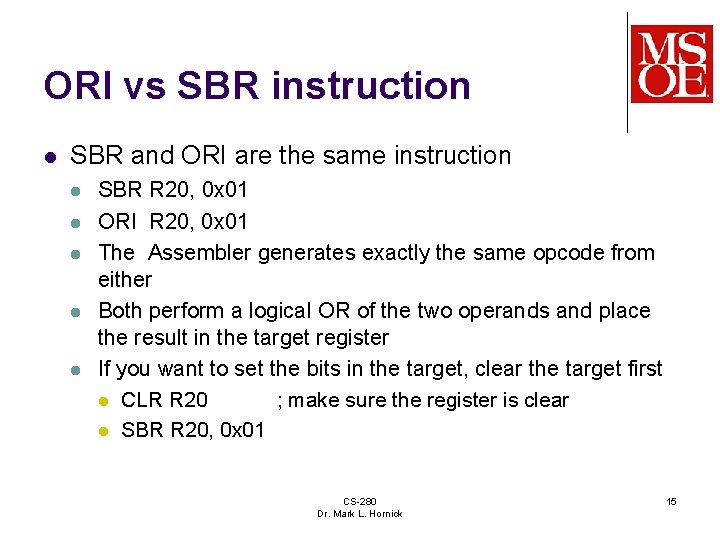

ORI vs SBR instruction l SBR and ORI are the same instruction l l l SBR R 20, 0 x 01 ORI R 20, 0 x 01 The Assembler generates exactly the same opcode from either Both perform a logical OR of the two operands and place the result in the target register If you want to set the bits in the target, clear the target first l CLR R 20 ; make sure the register is clear l SBR R 20, 0 x 01 CS-280 Dr. Mark L. Hornick 15

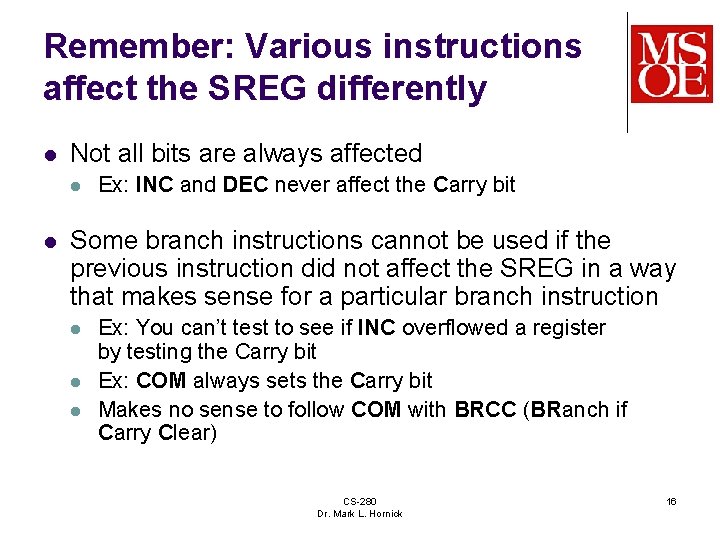

Remember: Various instructions affect the SREG differently l Not all bits are always affected l l Ex: INC and DEC never affect the Carry bit Some branch instructions cannot be used if the previous instruction did not affect the SREG in a way that makes sense for a particular branch instruction l l l Ex: You can’t test to see if INC overflowed a register by testing the Carry bit Ex: COM always sets the Carry bit Makes no sense to follow COM with BRCC (BRanch if Carry Clear) CS-280 Dr. Mark L. Hornick 16

- Slides: 16