MO 401 Arquitetura de Computadores I 2006 Prof

![Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t](https://slidetodoc.com/presentation_image_h2/4125b4c346bba305088876cff4ca1be9/image-44.jpg)

- Slides: 51

MO 401 Arquitetura de Computadores I 2006 Prof. Paulo Cesar Centoducatte@ic. unicamp. br www. ic. unicamp. br/~ducatte MO 401 -2007 Revisado MO 401 3. 1

MO 401 Arquitetura de Computadores I Conjunto de Instruções “Computer Architecture: A Quantitative Approach” - (Capítulo 2) MO 401 -2007 Revisado MO 401 3. 2

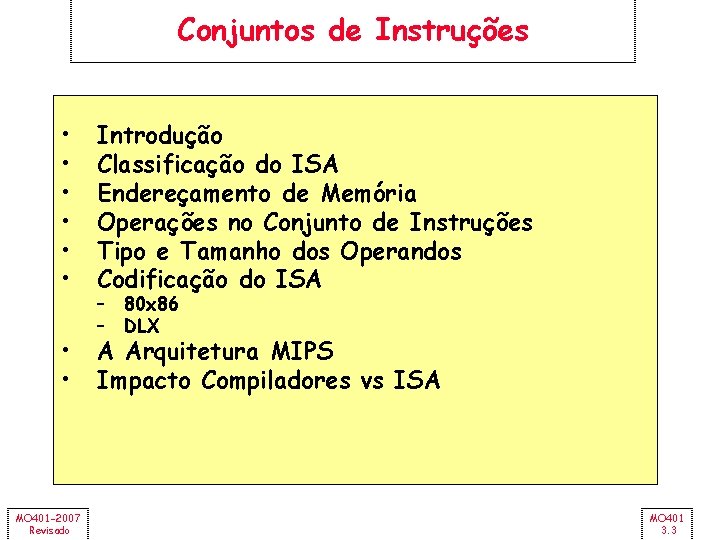

Conjuntos de Instruções • • • Introdução Classificação do ISA Endereçamento de Memória Operações no Conjunto de Instruções Tipo e Tamanho dos Operandos Codificação do ISA • • A Arquitetura MIPS Impacto Compiladores vs ISA MO 401 -2007 Revisado – – 80 x 86 DLX MO 401 3. 3

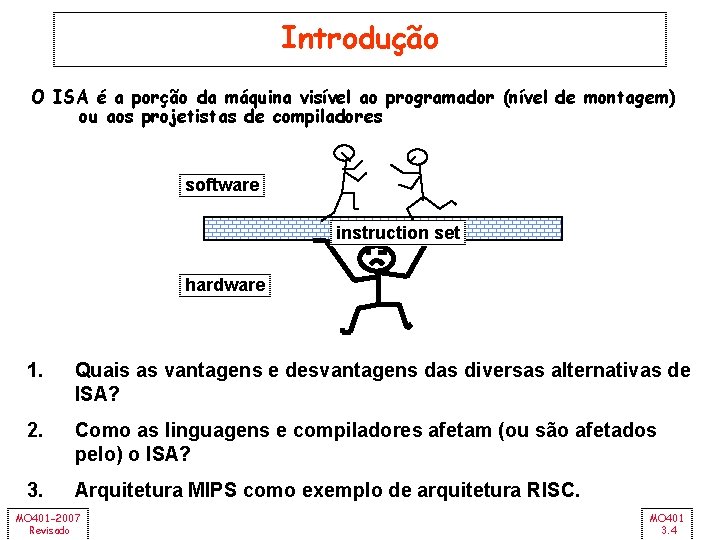

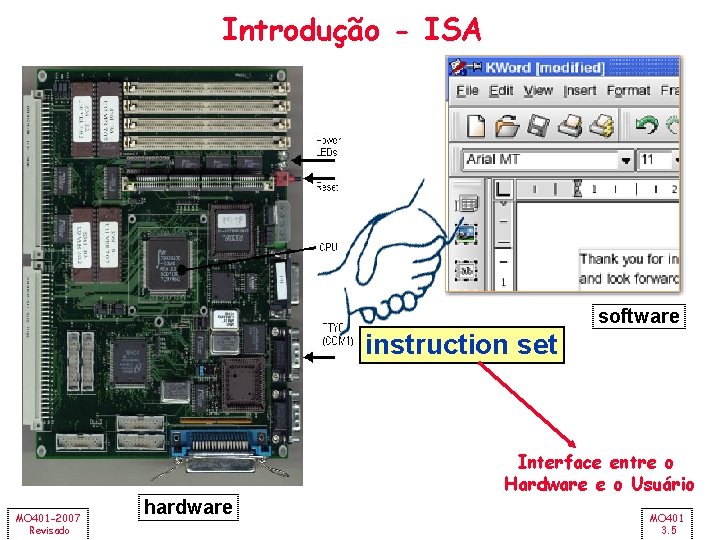

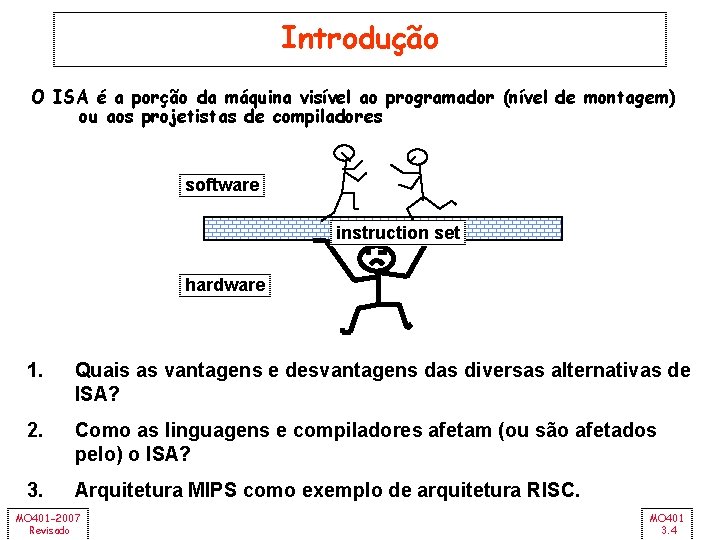

Introdução O ISA é a porção da máquina visível ao programador (nível de montagem) ou aos projetistas de compiladores software instruction set hardware 1. Quais as vantagens e desvantagens das diversas alternativas de ISA? 2. Como as linguagens e compiladores afetam (ou são afetados pelo) o ISA? 3. Arquitetura MIPS como exemplo de arquitetura RISC. MO 401 -2007 Revisado MO 401 3. 4

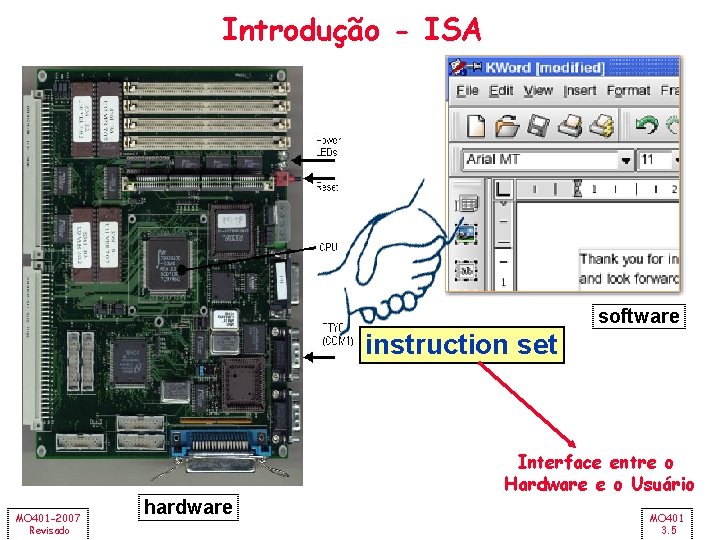

Introdução - ISA software instruction set Interface entre o Hardware e o Usuário MO 401 -2007 Revisado hardware MO 401 3. 5

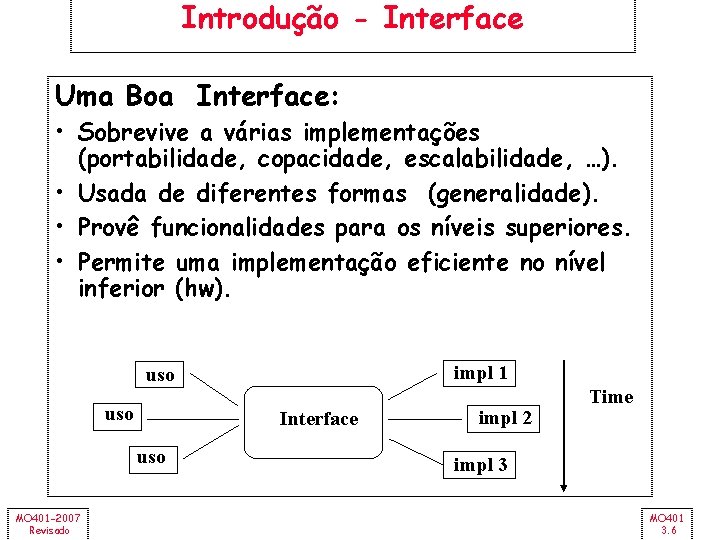

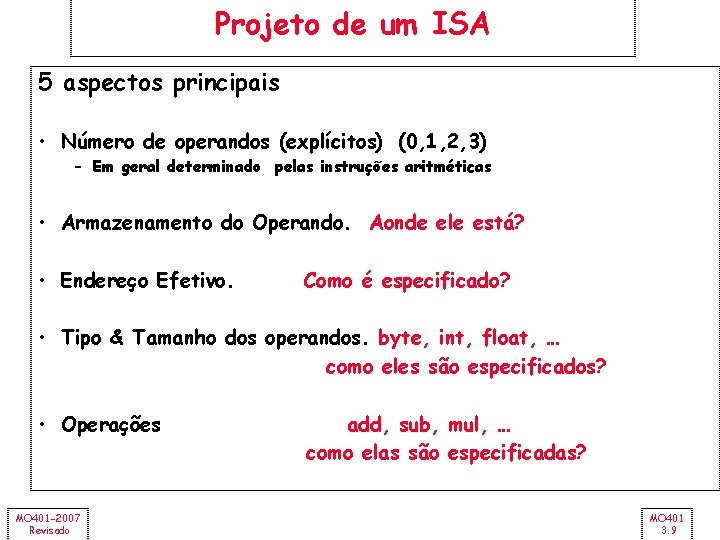

Introdução - Interface Uma Boa Interface: • Sobrevive a várias implementações (portabilidade, copacidade, escalabilidade, …). • Usada de diferentes formas (generalidade). • Provê funcionalidades para os níveis superiores. • Permite uma implementação eficiente no nível inferior (hw). impl 1 uso Interface uso MO 401 -2007 Revisado impl 2 Time impl 3 MO 401 3. 6

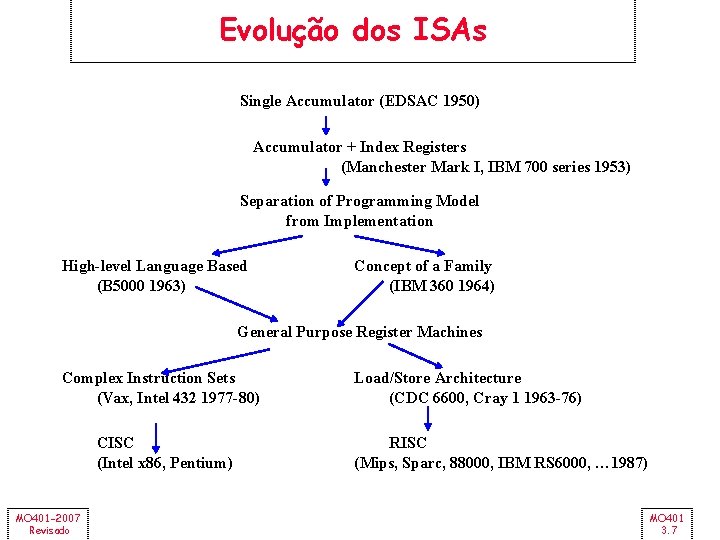

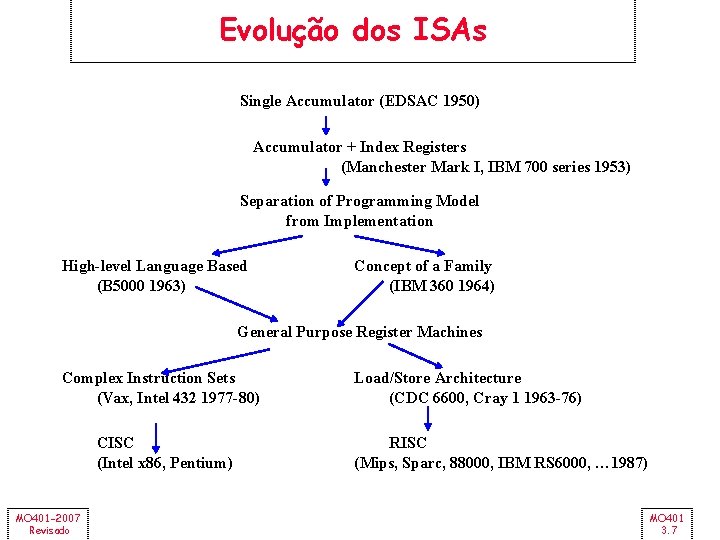

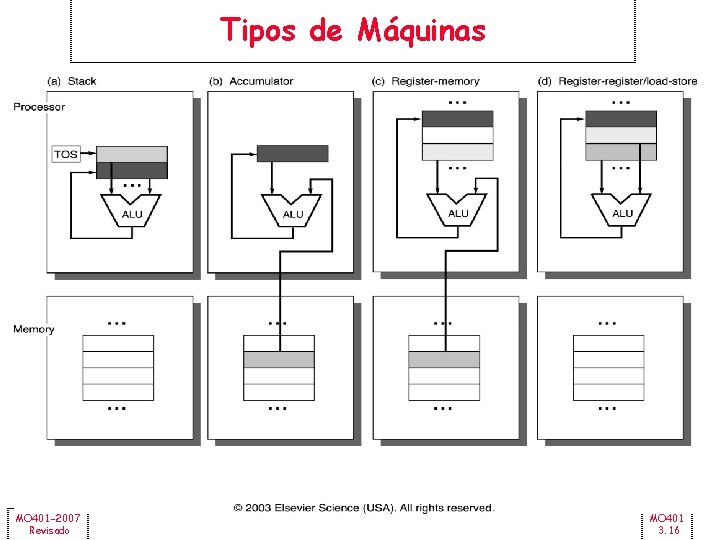

Evolução dos ISAs Single Accumulator (EDSAC 1950) Accumulator + Index Registers (Manchester Mark I, IBM 700 series 1953) Separation of Programming Model from Implementation High-level Language Based (B 5000 1963) Concept of a Family (IBM 360 1964) General Purpose Register Machines Complex Instruction Sets (Vax, Intel 432 1977 -80) CISC (Intel x 86, Pentium) MO 401 -2007 Revisado Load/Store Architecture (CDC 6600, Cray 1 1963 -76) RISC (Mips, Sparc, 88000, IBM RS 6000, … 1987) MO 401 3. 7

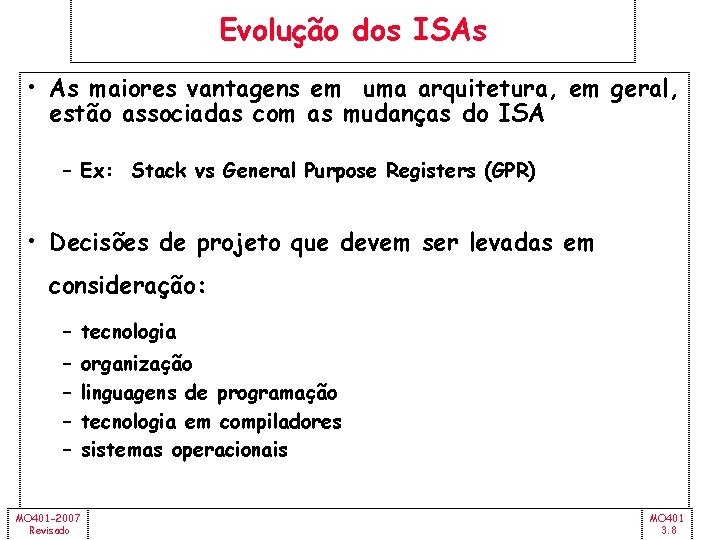

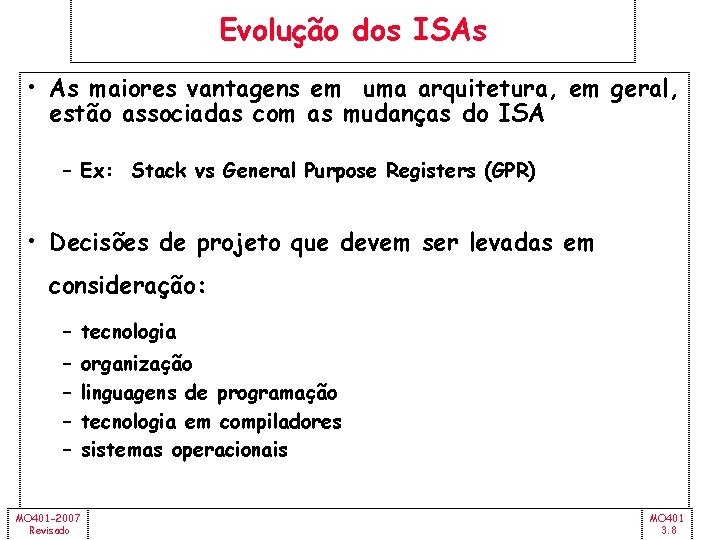

Evolução dos ISAs • As maiores vantagens em uma arquitetura, em geral, estão associadas com as mudanças do ISA – Ex: Stack vs General Purpose Registers (GPR) • Decisões de projeto que devem ser levadas em consideração: – tecnologia – – MO 401 -2007 Revisado organização linguagens de programação tecnologia em compiladores sistemas operacionais MO 401 3. 8

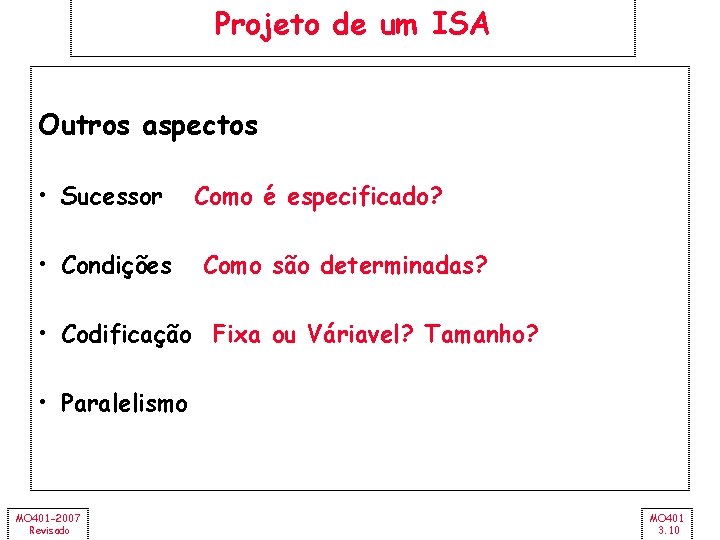

Projeto de um ISA 5 aspectos principais • Número de operandos (explícitos) (0, 1, 2, 3) – Em geral determinado pelas instruções aritméticas • Armazenamento do Operando. Aonde ele está? • Endereço Efetivo. Como é especificado? • Tipo & Tamanho dos operandos. byte, int, float, … como eles são especificados? • Operações MO 401 -2007 Revisado add, sub, mul, … como elas são especificadas? MO 401 3. 9

Projeto de um ISA Outros aspectos • Sucessor • Condições Como é especificado? Como são determinadas? • Codificação Fixa ou Váriavel? Tamanho? • Paralelismo MO 401 -2007 Revisado MO 401 3. 10

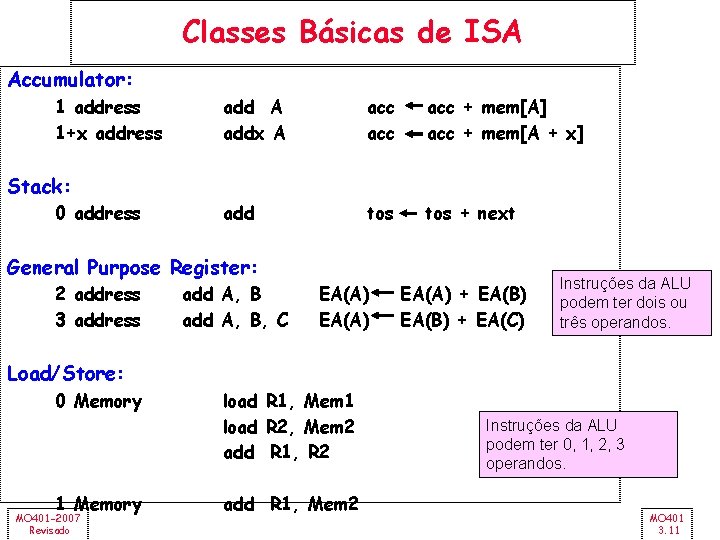

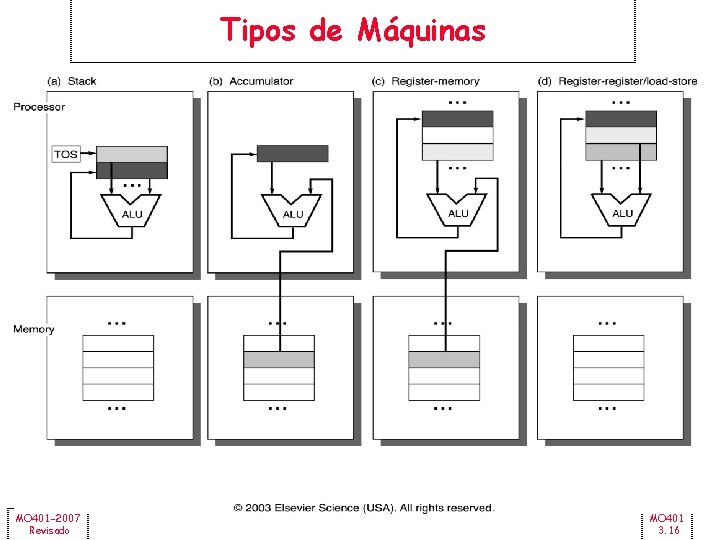

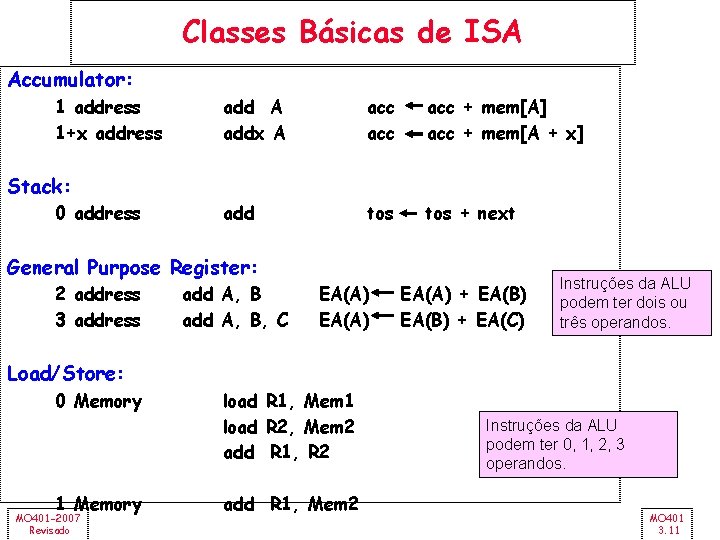

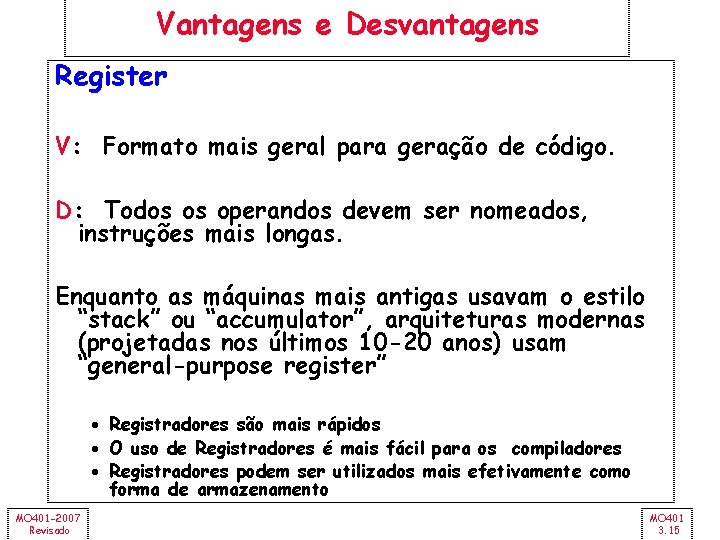

Classes Básicas de ISA Accumulator: 1 address 1+x address add A addx A acc acc + mem[A] acc + mem[A + x] add tos + next Stack: 0 address General Purpose Register: 2 address 3 address add A, B, C EA(A) + EA(B) + EA(C) Instruções da ALU podem ter dois ou três operandos. Load/Store: 0 Memory 1 Memory MO 401 -2007 Revisado load R 1, Mem 1 load R 2, Mem 2 add R 1, R 2 add R 1, Mem 2 Instruções da ALU podem ter 0, 1, 2, 3 operandos. MO 401 3. 11

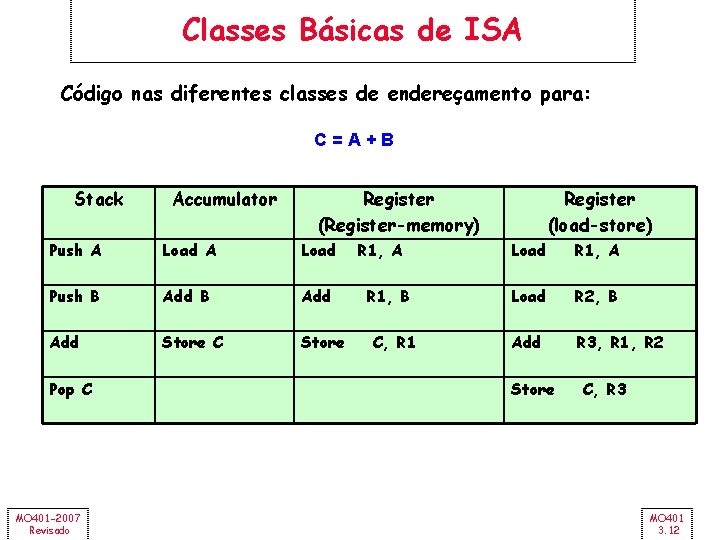

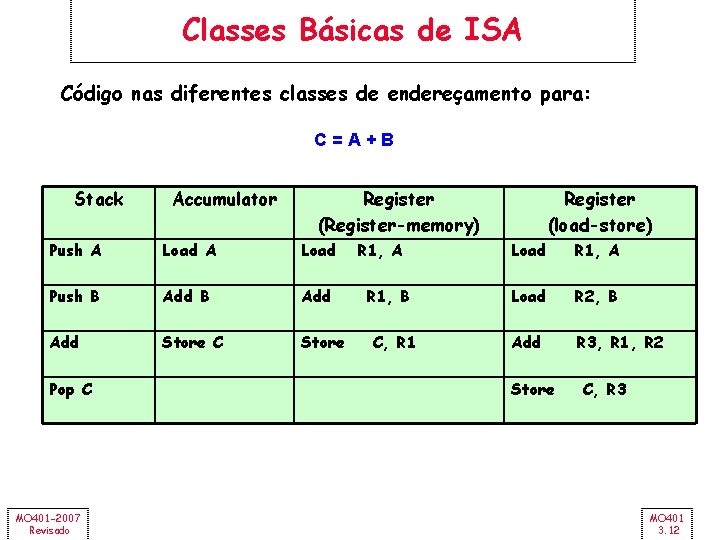

Classes Básicas de ISA Código nas diferentes classes de endereçamento para: C=A+B Stack Accumulator Register (Register-memory) Push A Load Push B Add Add Store C Store Pop C MO 401 -2007 Revisado R 1, A R 1, B C, R 1 Register (load-store) Load R 1, A Load R 2, B Add R 3, R 1, R 2 Store C, R 3 MO 401 3. 12

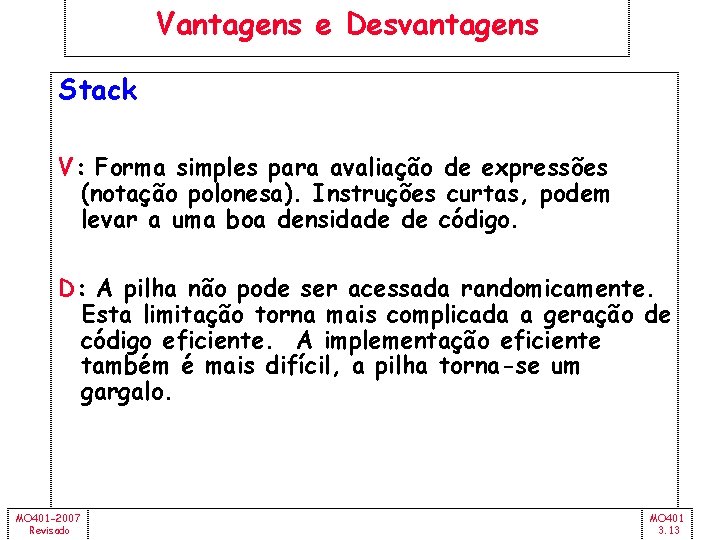

Vantagens e Desvantagens Stack V: Forma simples para avaliação de expressões (notação polonesa). Instruções curtas, podem levar a uma boa densidade de código. D: A pilha não pode ser acessada randomicamente. Esta limitação torna mais complicada a geração de código eficiente. A implementação eficiente também é mais difícil, a pilha torna-se um gargalo. MO 401 -2007 Revisado MO 401 3. 13

Vantagens e Desvantagens Accumulator V: Minimiza o número de estados internos da máquina. Instruções curtas. D: Uma vez que o acumulador é um temporário, o tráfego na memória é alto. MO 401 -2007 Revisado MO 401 3. 14

Vantagens e Desvantagens Register V: Formato mais geral para geração de código. D: Todos os operandos devem ser nomeados, instruções mais longas. Enquanto as máquinas mais antigas usavam o estilo “stack” ou “accumulator”, arquiteturas modernas (projetadas nos últimos 10 -20 anos) usam “general-purpose register” · Registradores são mais rápidos · O uso de Registradores é mais fácil para os compiladores · Registradores podem ser utilizados mais efetivamente como forma de armazenamento MO 401 -2007 Revisado MO 401 3. 15

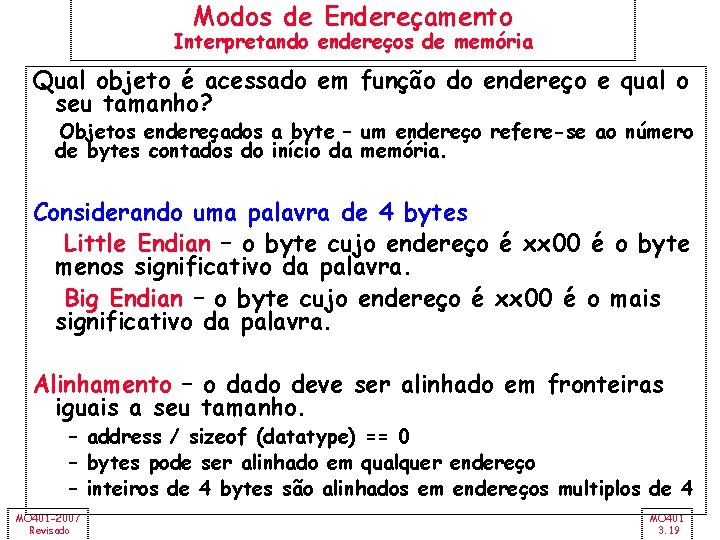

Tipos de Máquinas MO 401 -2007 Revisado MO 401 3. 16

MO 401 -2007 Revisado MO 401 3. 17

Registradores no Intel 80 X 86 GPR 0 EAX Accumulator GPR 1 ECX Count register, string, loop GPR 2 EDX Data Register; multiply, divide GPR 3 EBX Base Address Register GPR 4 ESP Stack Pointer GPR 5 EBP Base Pointer – for base of stack seg. GPR 6 ESI Index Register GPR 7 EDI Index Register CS Code Segment Pointer SS Stack Segment Pointer DS Data Segment Pointer ES Extra Data Segment Pointer FS Data Seg. 2 GS Data Seg. 3 EIP Instruction Counter Eflags Condition Codes PC MO 401 -2007 Revisado MO 401 3. 18

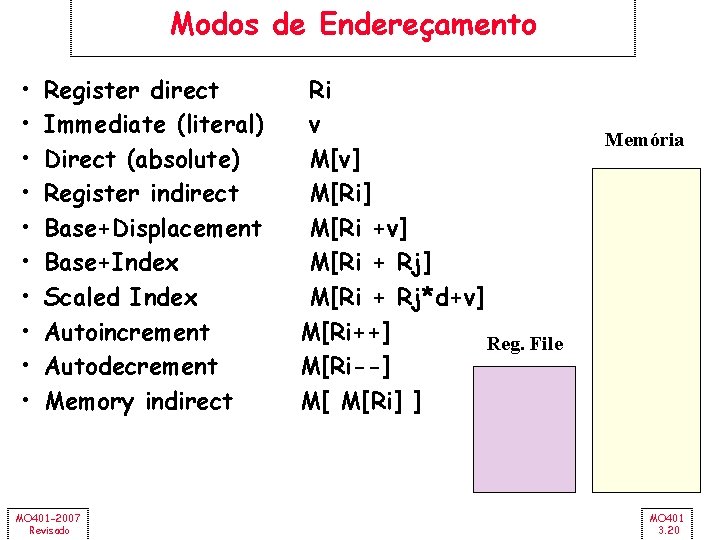

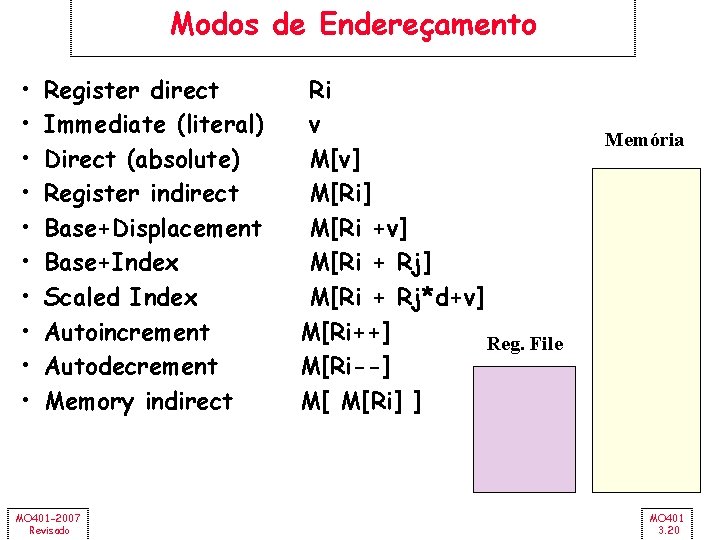

Modos de Endereçamento Interpretando endereços de memória Qual objeto é acessado em função do endereço e qual o seu tamanho? Objetos endereçados a byte – um endereço refere-se ao número de bytes contados do início da memória. Considerando uma palavra de 4 bytes Little Endian – o byte cujo endereço é xx 00 é o byte menos significativo da palavra. Big Endian – o byte cujo endereço é xx 00 é o mais significativo da palavra. Alinhamento – o dado deve ser alinhado em fronteiras iguais a seu tamanho. – address / sizeof (datatype) == 0 – bytes pode ser alinhado em qualquer endereço – inteiros de 4 bytes são alinhados em endereços multiplos de 4 MO 401 -2007 Revisado MO 401 3. 19

Modos de Endereçamento • • • Register direct Immediate (literal) Direct (absolute) Register indirect Base+Displacement Base+Index Scaled Index Autoincrement Autodecrement Memory indirect MO 401 -2007 Revisado Ri v M[v] M[Ri +v] M[Ri + Rj*d+v] M[Ri++] Reg. File M[Ri--] M[ M[Ri] ] Memória MO 401 3. 20

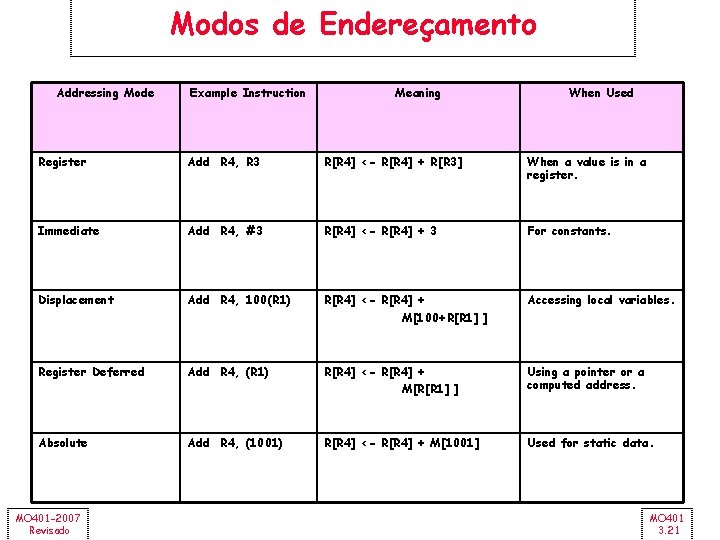

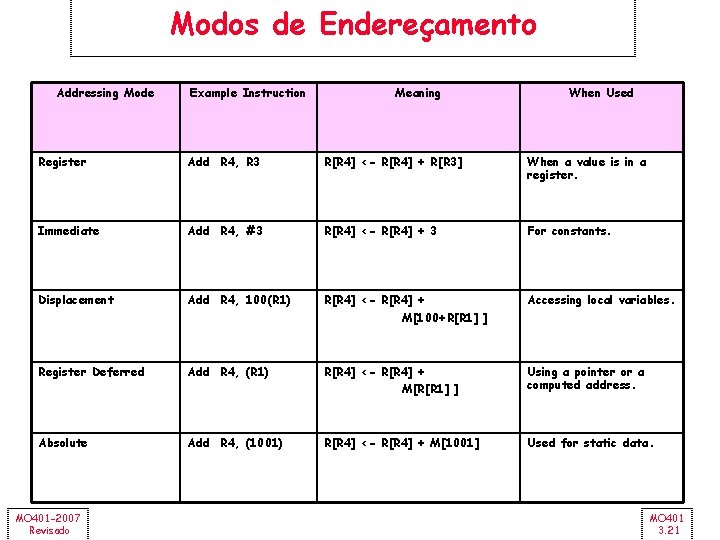

Modos de Endereçamento Addressing Mode Example Instruction Meaning When Used Register Add R 4, R 3 R[R 4] <- R[R 4] + R[R 3] When a value is in a register. Immediate Add R 4, #3 R[R 4] <- R[R 4] + 3 For constants. Displacement Add R 4, 100(R 1) R[R 4] <- R[R 4] + M[100+R[R 1] ] Accessing local variables. Register Deferred Add R 4, (R 1) R[R 4] <- R[R 4] + M[R[R 1] ] Using a pointer or a computed address. Absolute Add R 4, (1001) R[R 4] <- R[R 4] + M[1001] Used for static data. MO 401 -2007 Revisado MO 401 3. 21

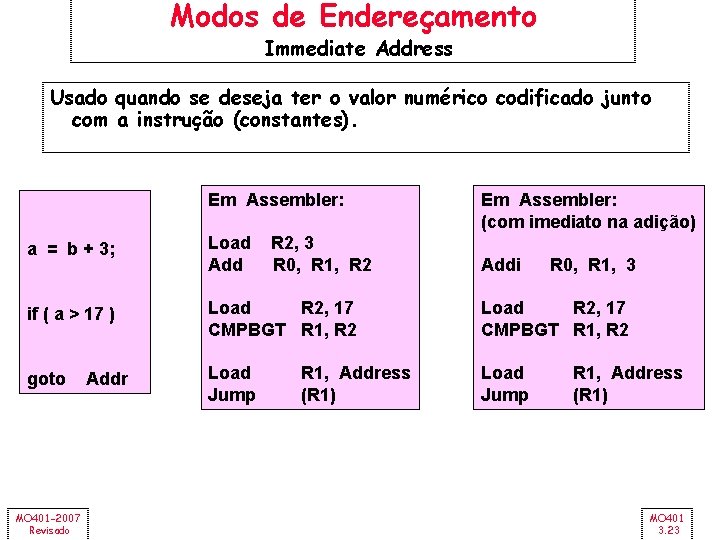

Modos de Endereçamento Displacement Qual o tamanho do deslocamento? r: Depende do espaço reservado na codificação da instrução. Para endereços dentro do alcance do deslocamento: Add R 4, 10000 (R 0) Para endereços fora do alcance do deslocamento, o compilador deve gerar: Load Add R 1, address R 4, 0 (R 1) No IA 32 e no DLX, o espaço alocado é de 16 bits. MO 401 -2007 Revisado MO 401 3. 22

Modos de Endereçamento Immediate Address Usado quando se deseja ter o valor numérico codificado junto com a instrução (constantes). Em Assembler: a = b + 3; Load Add if ( a > 17 ) Load R 2, 17 CMPBGT R 1, R 2 goto Load Jump MO 401 -2007 Revisado Addr R 2, 3 R 0, R 1, R 2 Em Assembler: (com imediato na adição) R 1, Address (R 1) Addi R 0, R 1, 3 R 1, Address (R 1) MO 401 3. 23

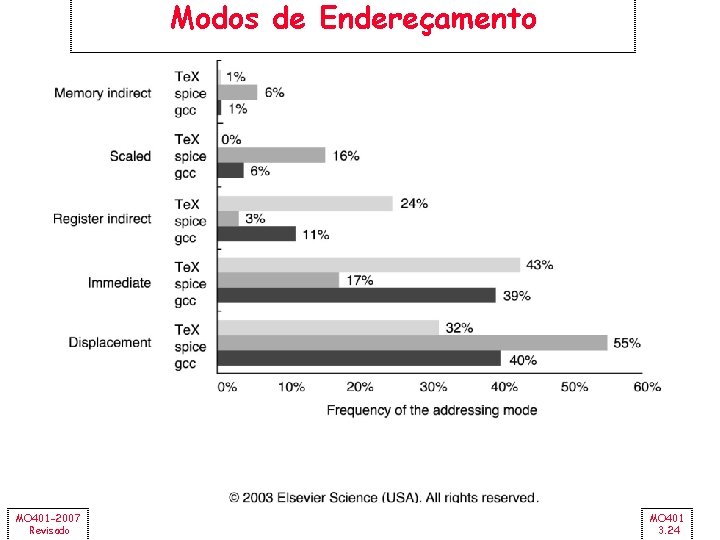

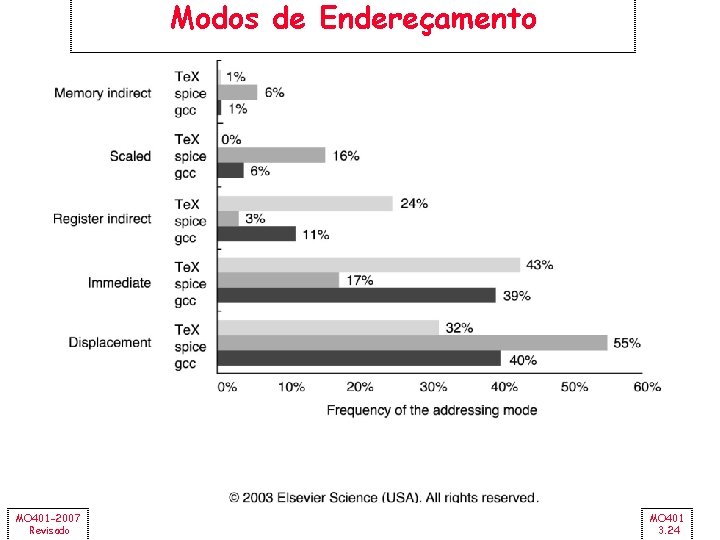

Modos de Endereçamento MO 401 -2007 Revisado MO 401 3. 24

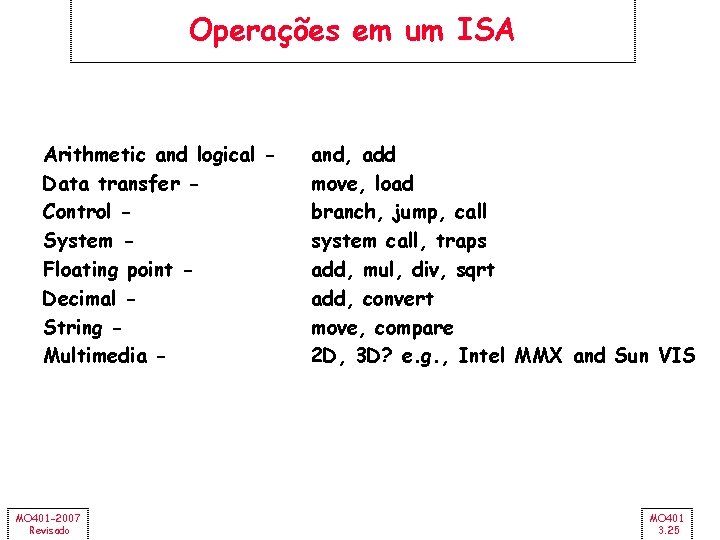

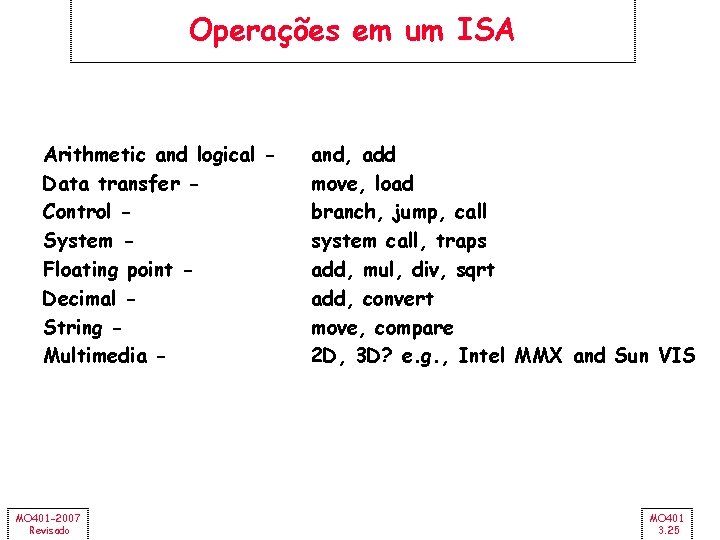

Operações em um ISA Arithmetic and logical Data transfer Control System Floating point Decimal String Multimedia - MO 401 -2007 Revisado and, add move, load branch, jump, call system call, traps add, mul, div, sqrt add, convert move, compare 2 D, 3 D? e. g. , Intel MMX and Sun VIS MO 401 3. 25

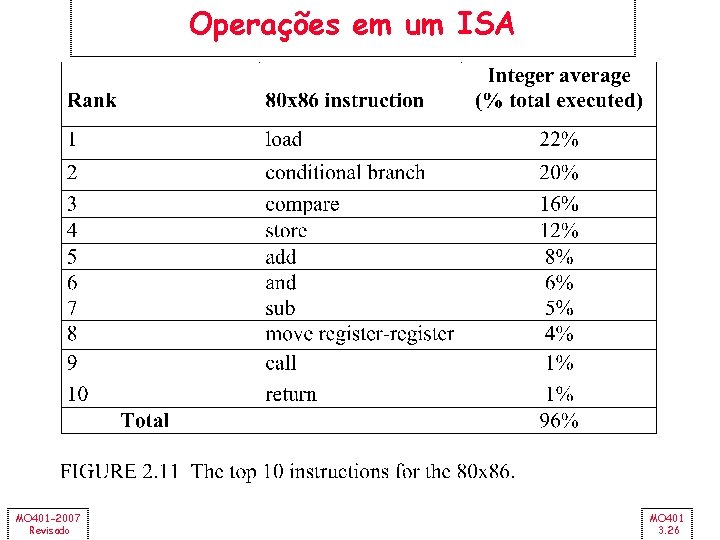

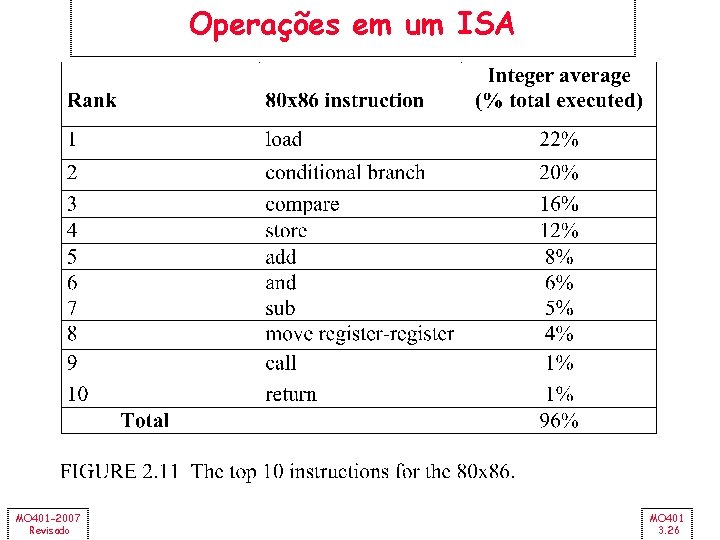

Operações em um ISA MO 401 -2007 Revisado MO 401 3. 26

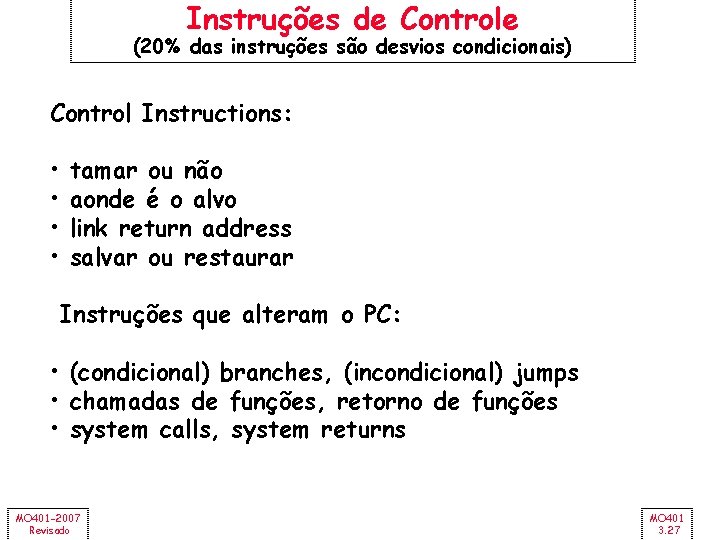

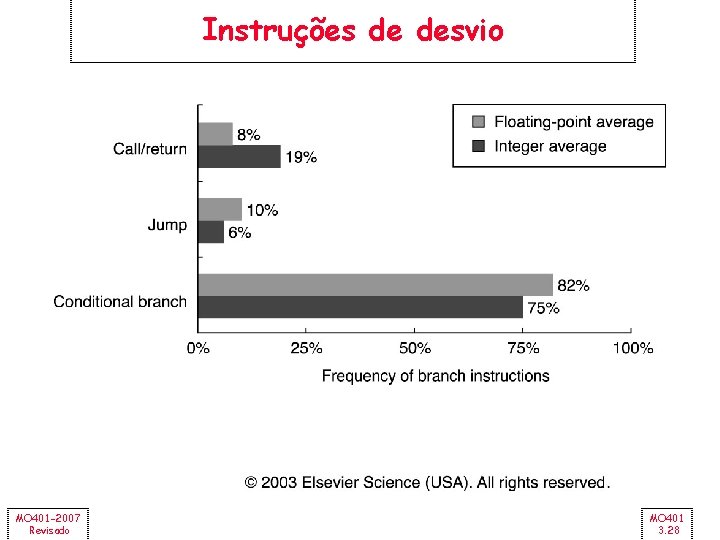

Instruções de Controle (20% das instruções são desvios condicionais) Control Instructions: • • tamar ou não aonde é o alvo link return address salvar ou restaurar Instruções que alteram o PC: • (condicional) branches, (incondicional) jumps • chamadas de funções, retorno de funções • system calls, system returns MO 401 -2007 Revisado MO 401 3. 27

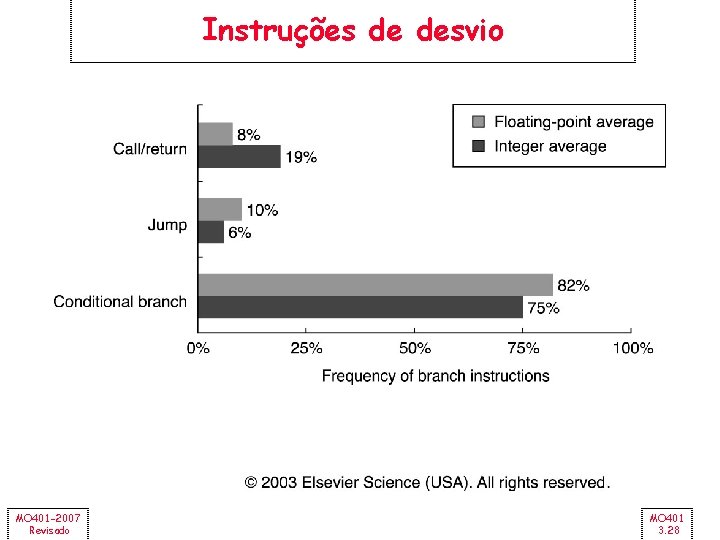

Instruções de desvio MO 401 -2007 Revisado MO 401 3. 28

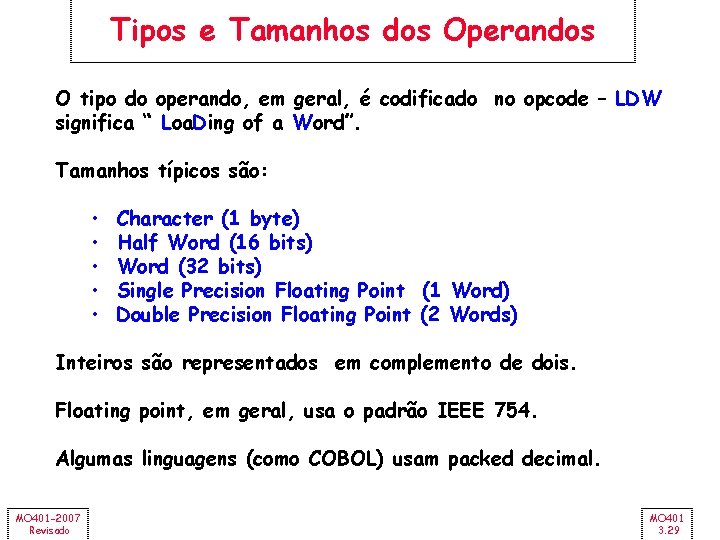

Tipos e Tamanhos dos Operandos O tipo do operando, em geral, é codificado no opcode – LDW significa “ Loa. Ding of a Word”. Tamanhos típicos são: • • • Character (1 byte) Half Word (16 bits) Word (32 bits) Single Precision Floating Point (1 Word) Double Precision Floating Point (2 Words) Inteiros são representados em complemento de dois. Floating point, em geral, usa o padrão IEEE 754. Algumas linguagens (como COBOL) usam packed decimal. MO 401 -2007 Revisado MO 401 3. 29

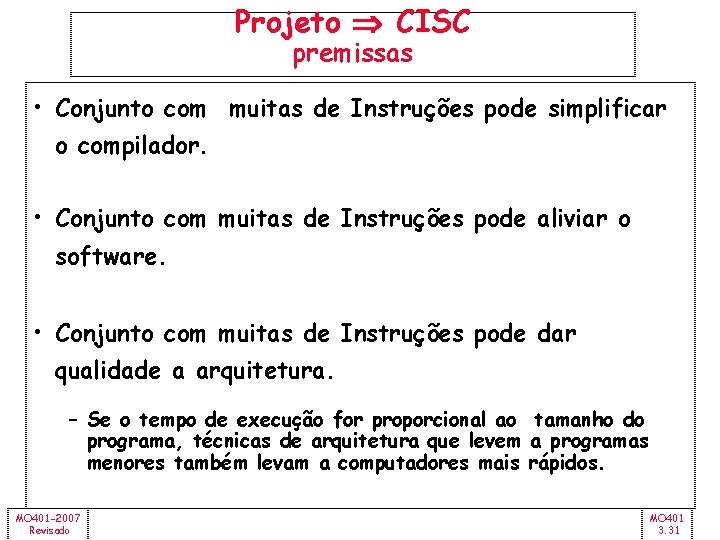

RISC vs CISC RISC = Reduced Instruction Set Computer • • Conjunto de Instruções pequeno Instruções de tamanho fixo Operações executadas somente em registradores Chip simples, em geral, executam com velocidade de clock elevada. CISC = Complex Instruction Set Computer • • • Conjunto de Instruções grande Instruções Complexas e de tamanho variável Operações Memória-Memória MO 401 -2007 Revisado MO 401 3. 30

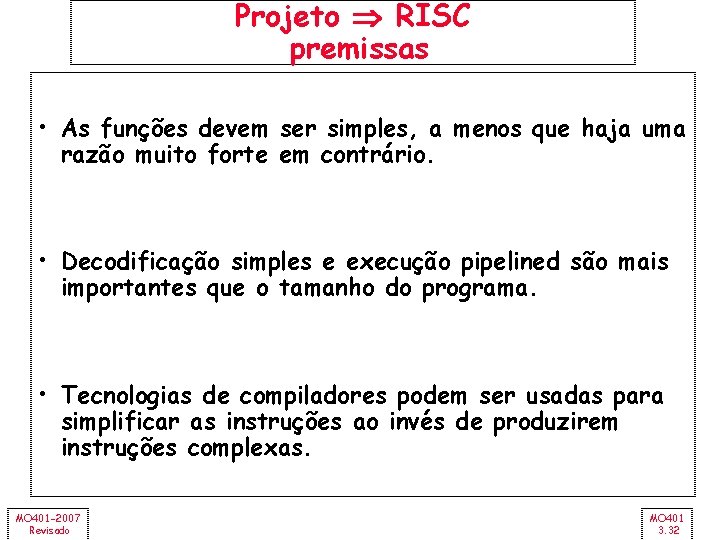

Projeto CISC premissas • Conjunto com muitas de Instruções pode simplificar o compilador. • Conjunto com muitas de Instruções pode aliviar o software. • Conjunto com muitas de Instruções pode dar qualidade a arquitetura. – Se o tempo de execução for proporcional ao tamanho do programa, técnicas de arquitetura que levem a programas menores também levam a computadores mais rápidos. MO 401 -2007 Revisado MO 401 3. 31

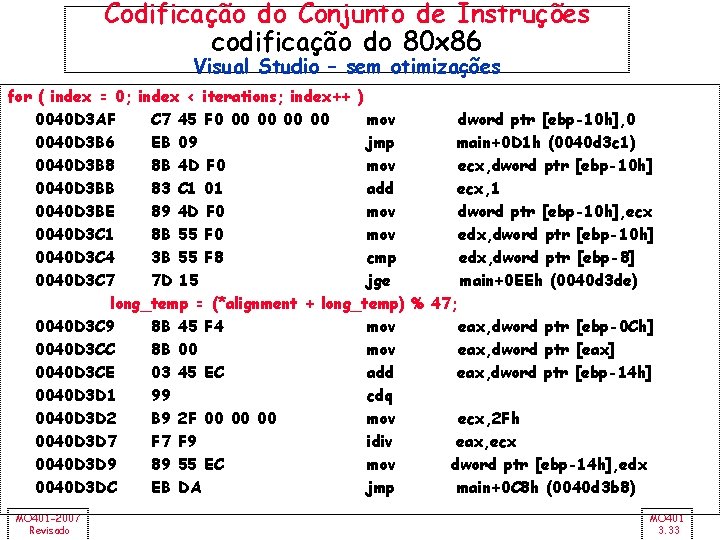

Projeto RISC premissas • As funções devem ser simples, a menos que haja uma razão muito forte em contrário. • Decodificação simples e execução pipelined são mais importantes que o tamanho do programa. • Tecnologias de compiladores podem ser usadas para simplificar as instruções ao invés de produzirem instruções complexas. MO 401 -2007 Revisado MO 401 3. 32

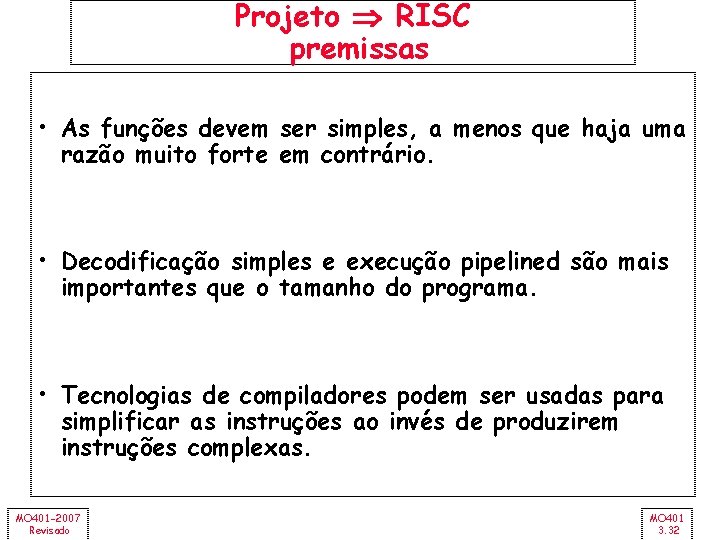

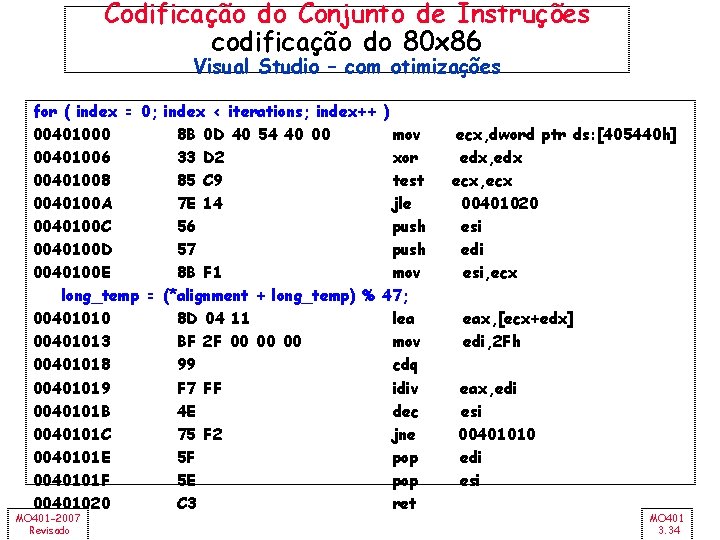

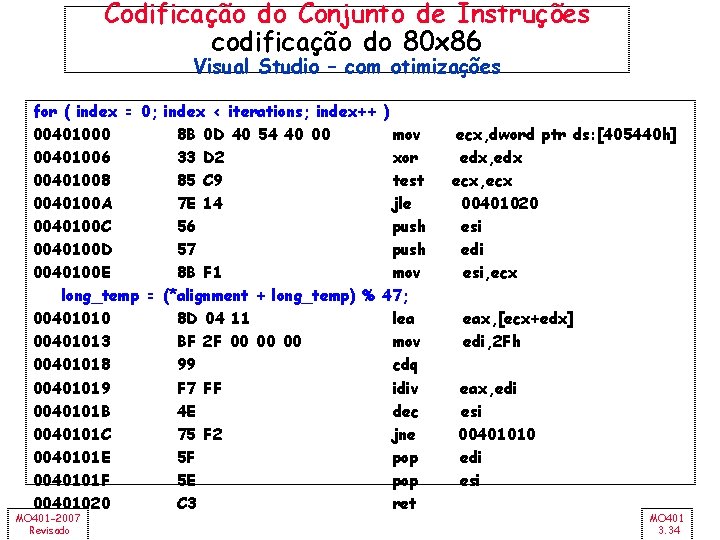

Codificação do Conjunto de Instruções codificação do 80 x 86 Visual Studio – sem otimizações for ( index = 0; index < iterations; index++ ) 0040 D 3 AF C 7 45 F 0 00 00 mov dword ptr [ebp-10 h], 0 0040 D 3 B 6 EB 09 jmp main+0 D 1 h (0040 d 3 c 1) 0040 D 3 B 8 8 B 4 D F 0 mov ecx, dword ptr [ebp-10 h] 0040 D 3 BB 83 C 1 01 add ecx, 1 0040 D 3 BE 89 4 D F 0 mov dword ptr [ebp-10 h], ecx 0040 D 3 C 1 8 B 55 F 0 mov edx, dword ptr [ebp-10 h] 0040 D 3 C 4 3 B 55 F 8 cmp edx, dword ptr [ebp-8] 0040 D 3 C 7 7 D 15 jge main+0 EEh (0040 d 3 de) long_temp = (*alignment + long_temp) % 47; 0040 D 3 C 9 8 B 45 F 4 mov eax, dword ptr [ebp-0 Ch] 0040 D 3 CC 8 B 00 mov eax, dword ptr [eax] 0040 D 3 CE 03 45 EC add eax, dword ptr [ebp-14 h] 0040 D 3 D 1 99 cdq 0040 D 3 D 2 B 9 2 F 00 00 00 mov ecx, 2 Fh 0040 D 3 D 7 F 9 idiv eax, ecx 0040 D 3 D 9 89 55 EC mov dword ptr [ebp-14 h], edx 0040 D 3 DC EB DA jmp main+0 C 8 h (0040 d 3 b 8) MO 401 -2007 Revisado MO 401 3. 33

Codificação do Conjunto de Instruções codificação do 80 x 86 Visual Studio – com otimizações for ( index = 0; index < iterations; index++ 00401000 8 B 0 D 40 54 40 00 00401006 33 D 2 00401008 85 C 9 0040100 A 7 E 14 0040100 C 56 0040100 D 57 0040100 E 8 B F 1 long_temp = (*alignment + long_temp) % 00401010 8 D 04 11 00401013 BF 2 F 00 00401018 99 00401019 F 7 FF 0040101 B 4 E 0040101 C 75 F 2 0040101 E 5 F 0040101 F 5 E 00401020 C 3 MO 401 -2007 Revisado ) mov xor test jle push mov 47; lea mov cdq idiv dec jne pop ret ecx, dword ptr ds: [405440 h] edx, edx ecx, ecx 00401020 esi edi esi, ecx eax, [ecx+edx] edi, 2 Fh eax, edi esi 00401010 edi esi MO 401 3. 34

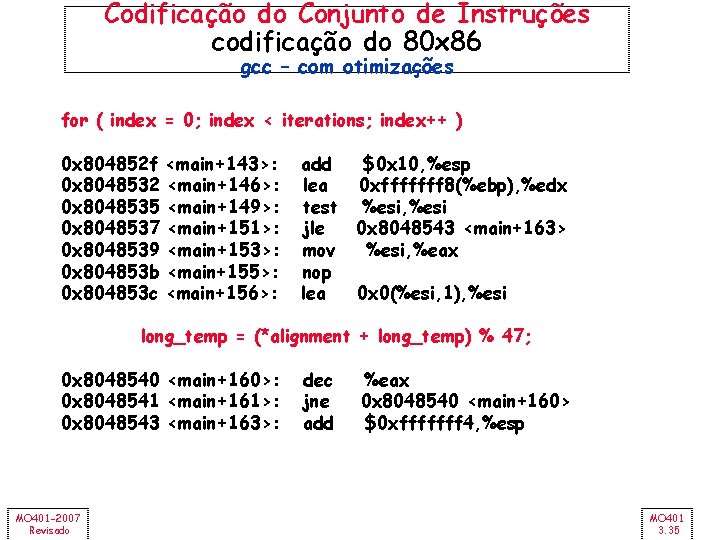

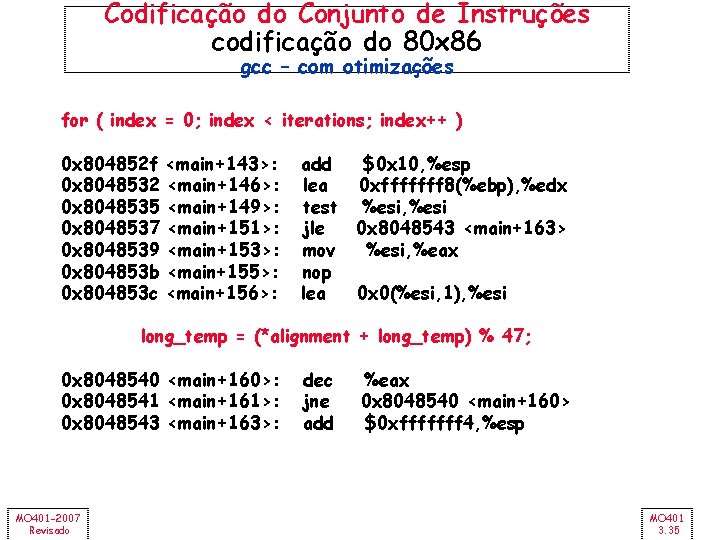

Codificação do Conjunto de Instruções codificação do 80 x 86 gcc – com otimizações for ( index = 0; index < iterations; index++ ) 0 x 804852 f 0 x 8048532 0 x 8048535 0 x 8048537 0 x 8048539 0 x 804853 b 0 x 804853 c <main+143>: <main+146>: <main+149>: <main+151>: <main+153>: <main+155>: <main+156>: add $0 x 10, %esp lea 0 xfffffff 8(%ebp), %edx test %esi, %esi jle 0 x 8048543 <main+163> mov %esi, %eax nop lea 0 x 0(%esi, 1), %esi long_temp = (*alignment + long_temp) % 47; 0 x 8048540 <main+160>: 0 x 8048541 <main+161>: 0 x 8048543 <main+163>: MO 401 -2007 Revisado dec jne add %eax 0 x 8048540 <main+160> $0 xfffffff 4, %esp MO 401 3. 35

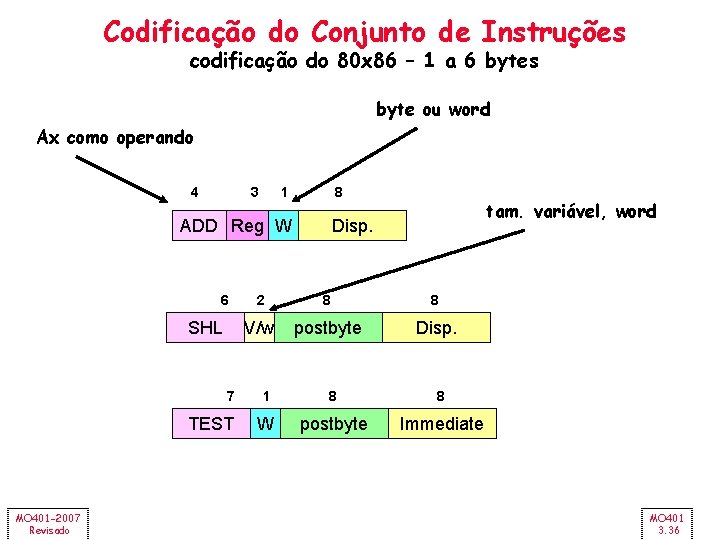

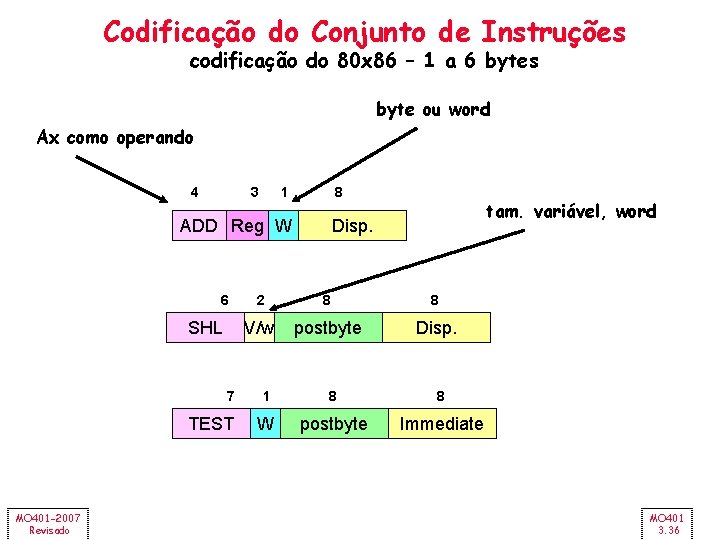

Codificação do Conjunto de Instruções codificação do 80 x 86 – 1 a 6 bytes byte ou word Ax como operando 4 3 1 8 ADD Reg W 6 SHL MO 401 -2007 Revisado tam. variável, word Disp. 2 8 8 V/w postbyte Disp. 7 1 8 8 TEST W postbyte Immediate MO 401 3. 36

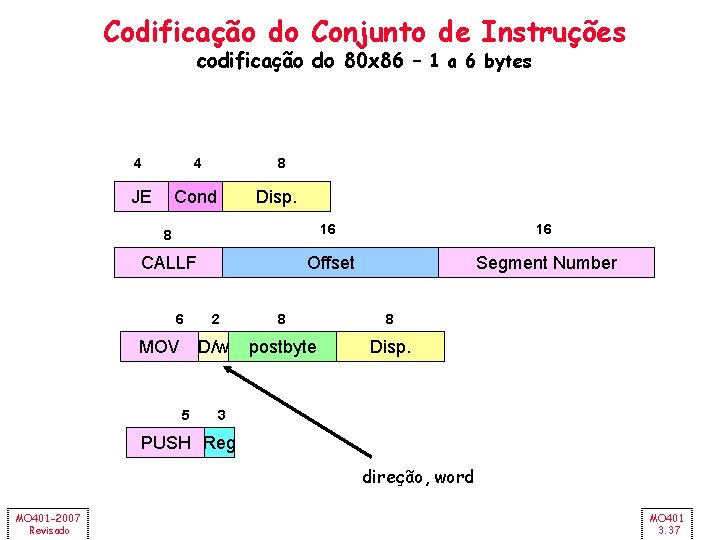

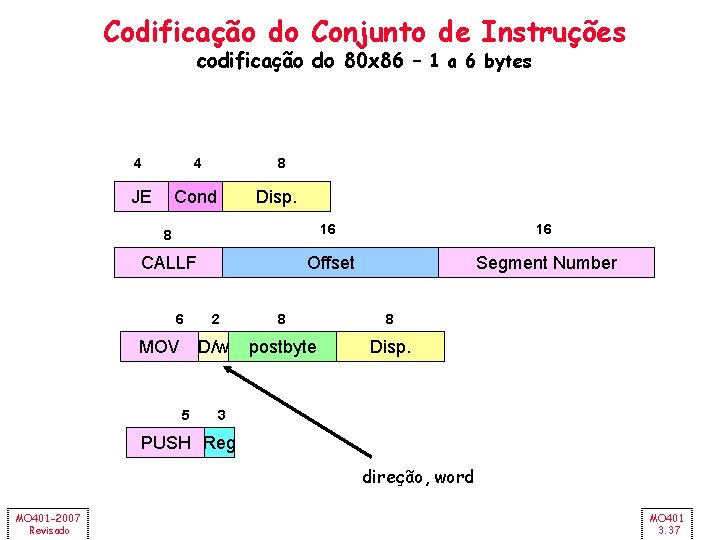

Codificação do Conjunto de Instruções codificação do 80 x 86 – 1 a 6 bytes 4 4 8 JE Cond Disp. 8 16 16 CALLF Offset Segment Number 6 MOV 5 2 8 8 D/w postbyte Disp. 3 PUSH Reg direção, word MO 401 -2007 Revisado MO 401 3. 37

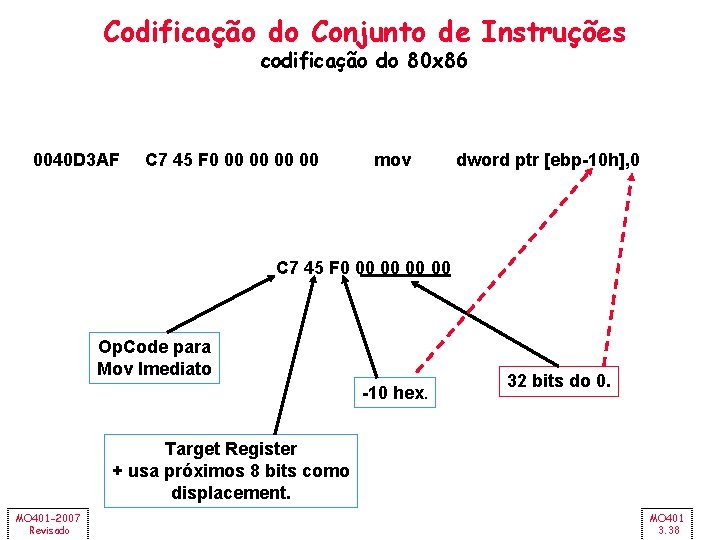

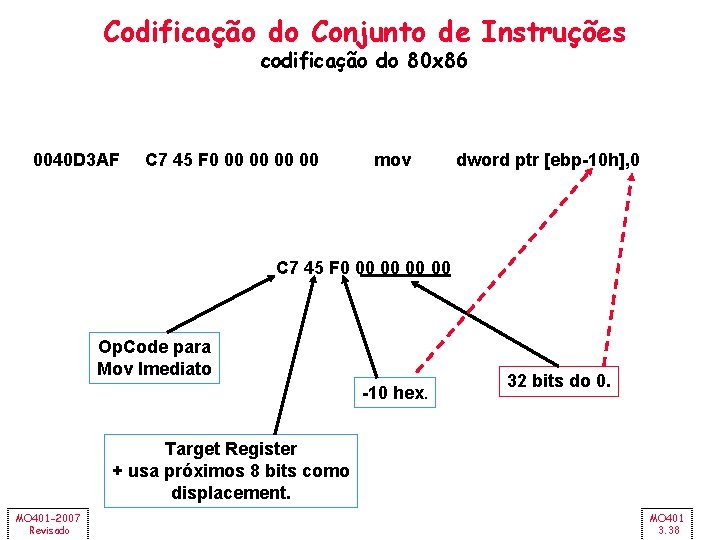

Codificação do Conjunto de Instruções codificação do 80 x 86 0040 D 3 AF C 7 45 F 0 00 00 mov dword ptr [ebp-10 h], 0 C 7 45 F 0 00 00 Op. Code para Mov Imediato -10 hex. 32 bits do 0. Target Register + usa próximos 8 bits como displacement. MO 401 -2007 Revisado MO 401 3. 38

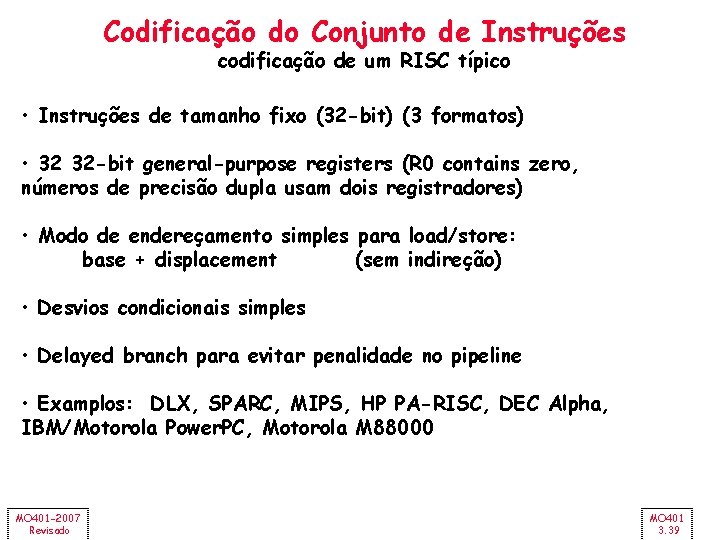

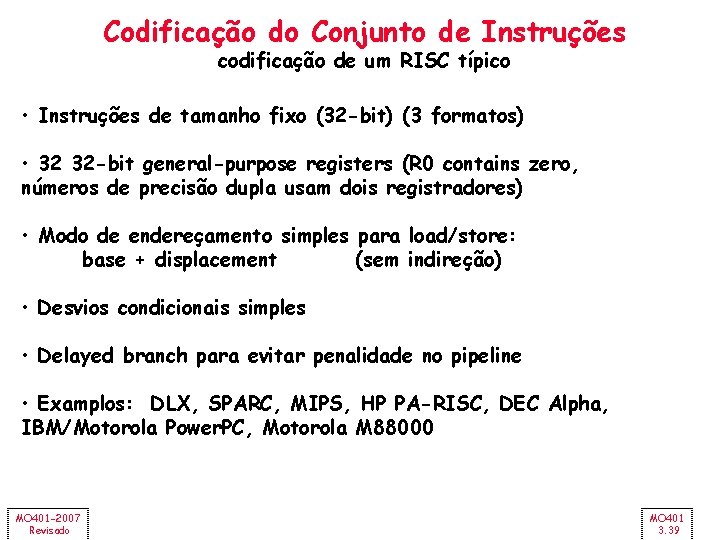

Codificação do Conjunto de Instruções codificação de um RISC típico • Instruções de tamanho fixo (32 -bit) (3 formatos) • 32 32 -bit general-purpose registers (R 0 contains zero, números de precisão dupla usam dois registradores) • Modo de endereçamento simples para load/store: base + displacement (sem indireção) • Desvios condicionais simples • Delayed branch para evitar penalidade no pipeline • Examplos: DLX, SPARC, MIPS, HP PA-RISC, DEC Alpha, IBM/Motorola Power. PC, Motorola M 88000 MO 401 -2007 Revisado MO 401 3. 39

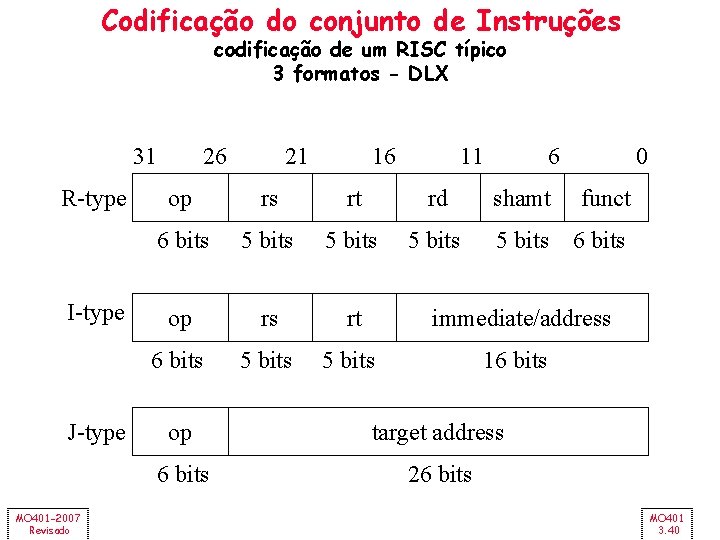

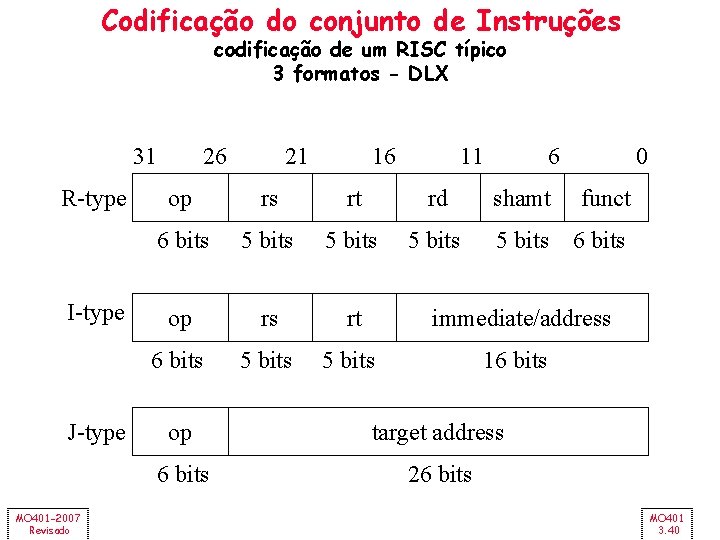

Codificação do conjunto de Instruções codificação de um RISC típico 3 formatos - DLX 31 R-type I-type J-type MO 401 -2007 Revisado 26 21 16 11 6 0 op rs rt rd shamt funct 6 bits 5 bits 6 bits op rs rt immediate/address 6 bits 5 bits 16 bits op target address 6 bits 26 bits MO 401 3. 40

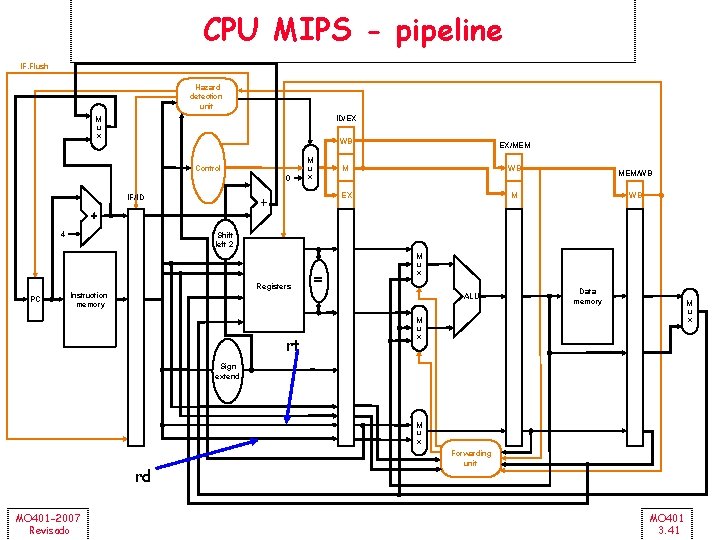

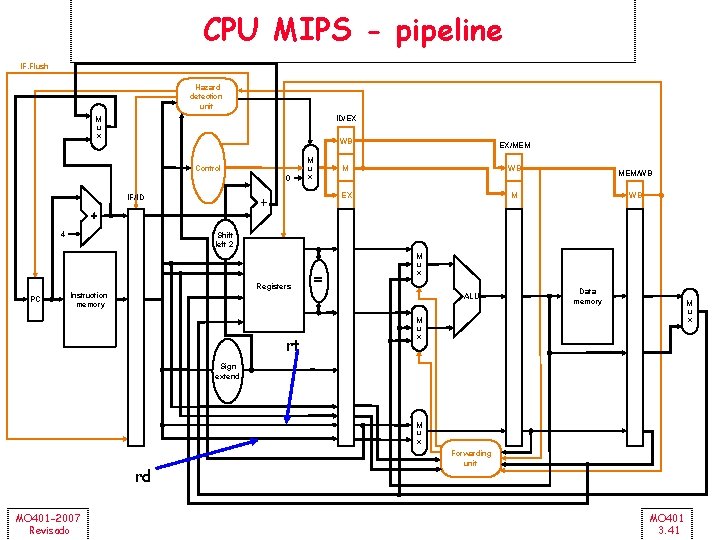

CPU MIPS - pipeline IF. Flush Hazard detection unit ID/EX M u x WB Control 0 M u x IF/ID 4 PC EX/MEM M WB EX M MEM/WB WB Shift left 2 Registers Instruction memory = M u x ALU rt Data memory M u x Sign extend M u x rd MO 401 -2007 Revisado Forwarding unit MO 401 3. 41

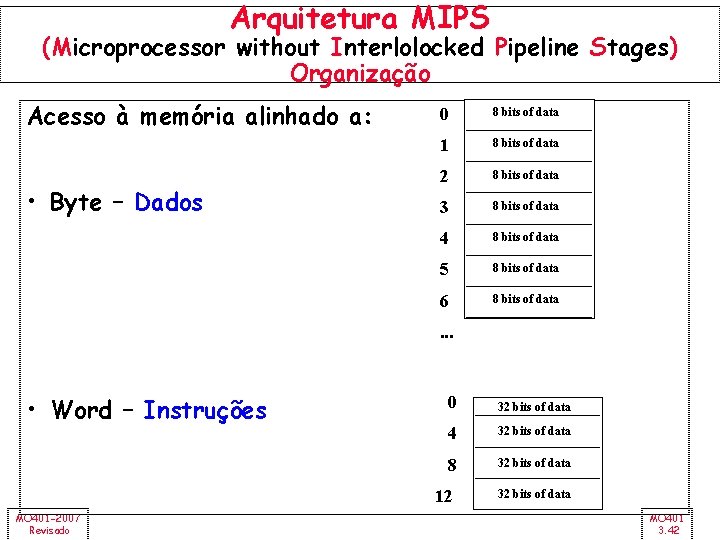

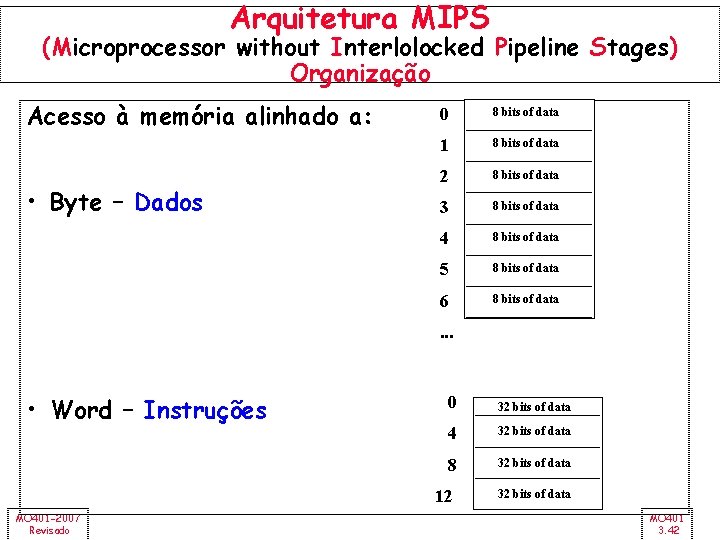

Arquitetura MIPS (Microprocessor without Interlolocked Pipeline Stages) Organização Acesso à memória alinhado a: • Byte – Dados 0 8 bits of data 1 8 bits of data 2 8 bits of data 3 8 bits of data 4 8 bits of data 5 8 bits of data 6 8 bits of data . . . • Word – Instruções 0 32 bits of data 4 32 bits of data 8 32 bits of data 12 MO 401 -2007 Revisado 32 bits of data MO 401 3. 42

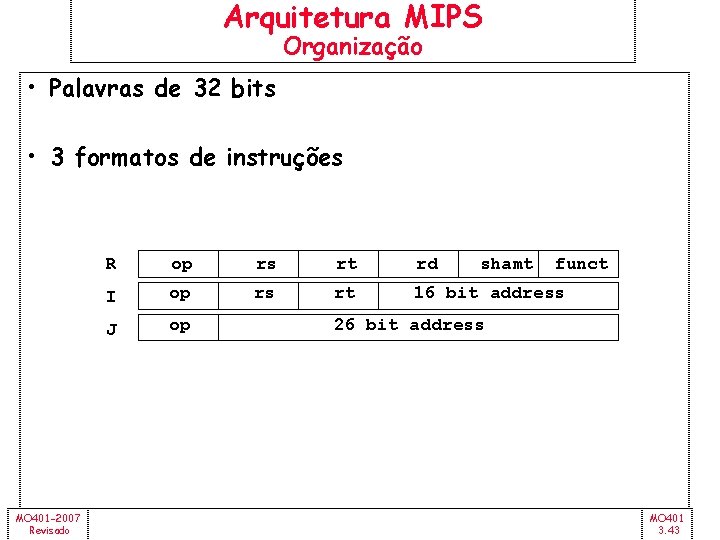

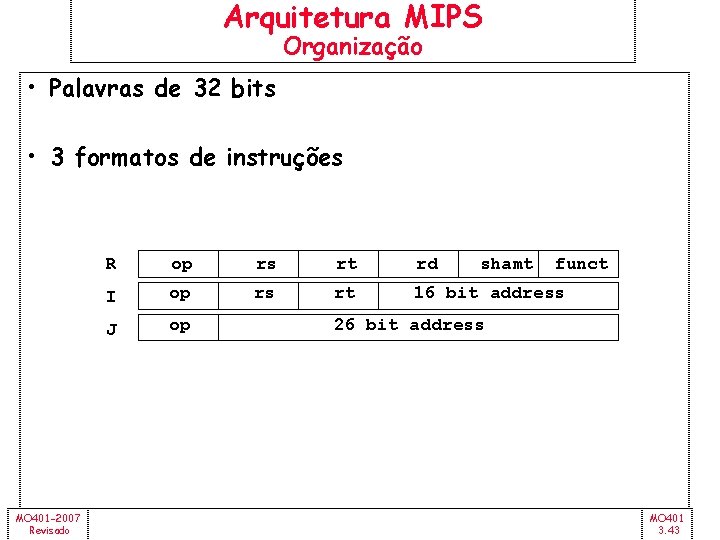

Arquitetura MIPS Organização • Palavras de 32 bits • 3 formatos de instruções MO 401 -2007 Revisado R op rs rt rd I op rs rt 16 bit address J op shamt funct 26 bit address MO 401 3. 43

![Arquitetura MIPS Organização Código C A300 h A300 Código MIPS lw t Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t](https://slidetodoc.com/presentation_image_h2/4125b4c346bba305088876cff4ca1be9/image-44.jpg)

Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t 0, 1200($t 1) add $t 0, $s 2, $t 0 sw $t 0, 1200($t 1) MO 401 -2007 Revisado MO 401 3. 44

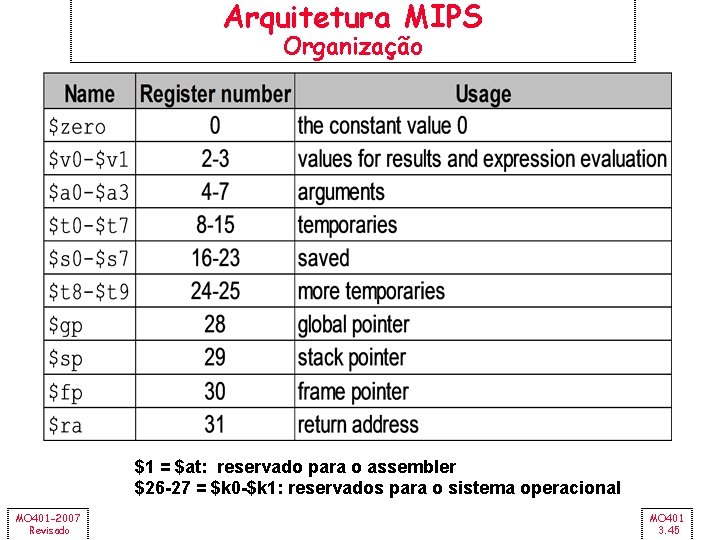

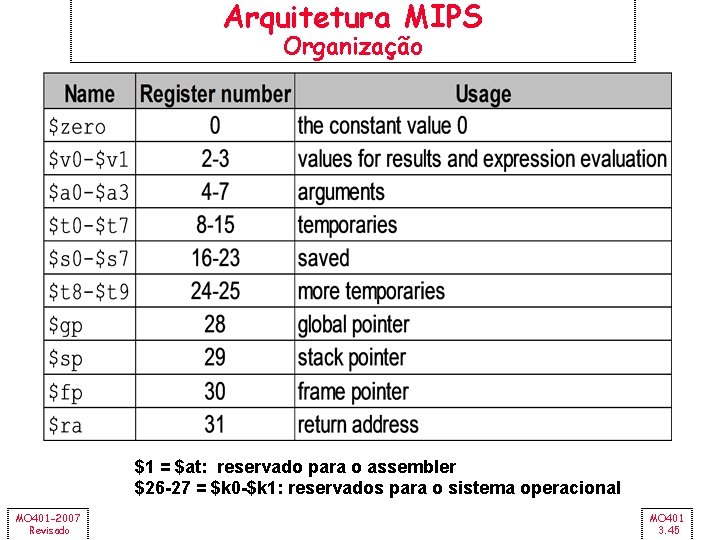

Arquitetura MIPS Organização $1 = $at: reservado para o assembler $26 -27 = $k 0 -$k 1: reservados para o sistema operacional MO 401 -2007 Revisado MO 401 3. 45

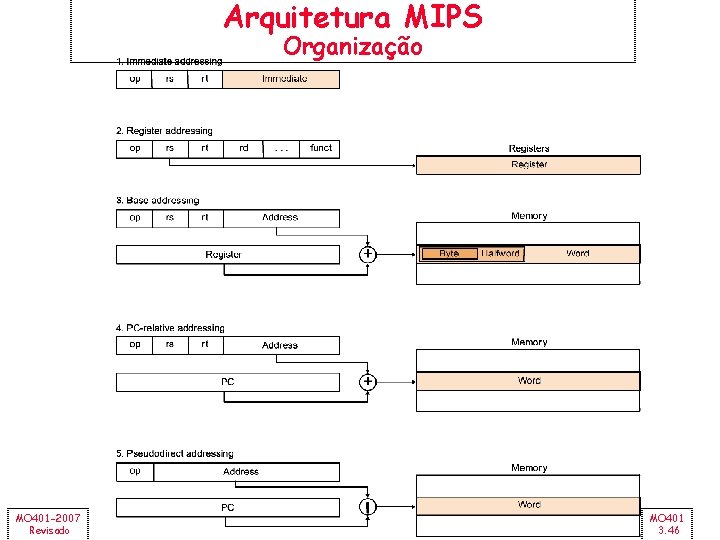

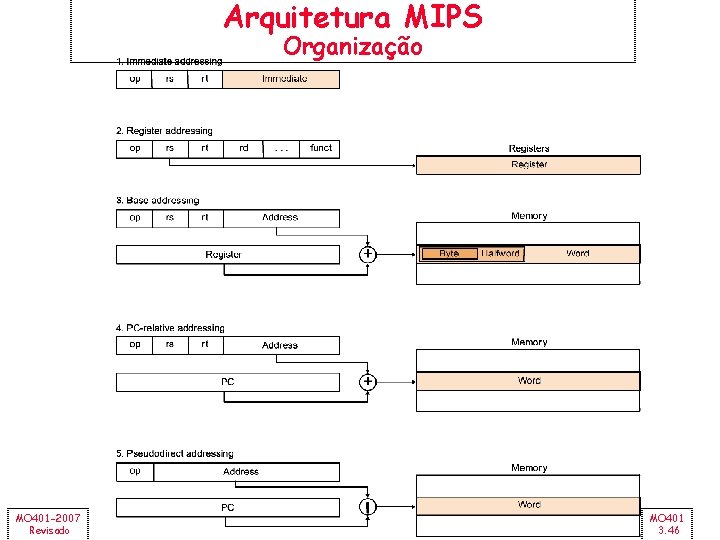

Arquitetura MIPS Organização MO 401 -2007 Revisado MO 401 3. 46

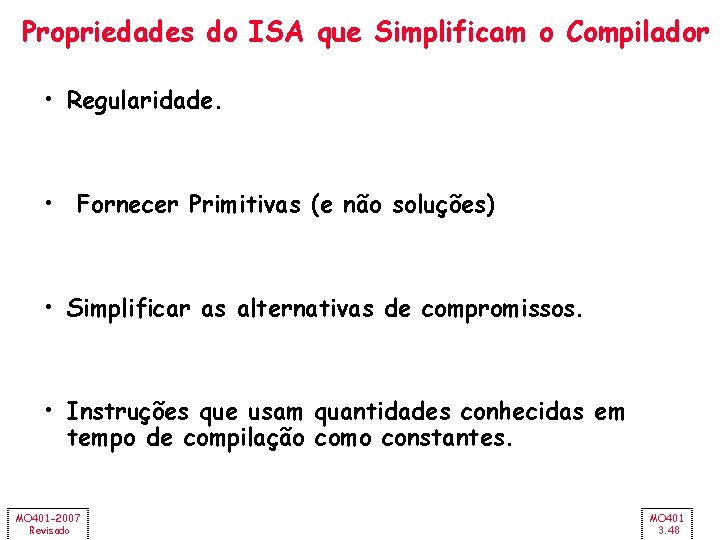

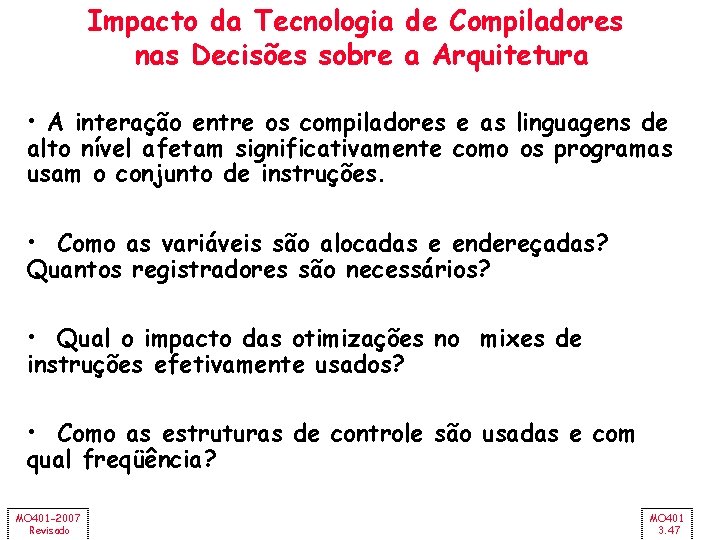

Impacto da Tecnologia de Compiladores nas Decisões sobre a Arquitetura • A interação entre os compiladores e as linguagens de alto nível afetam significativamente como os programas usam o conjunto de instruções. • Como as variáveis são alocadas e endereçadas? Quantos registradores são necessários? • Qual o impacto das otimizações no mixes de instruções efetivamente usados? • Como as estruturas de controle são usadas e com qual freqüência? MO 401 -2007 Revisado MO 401 3. 47

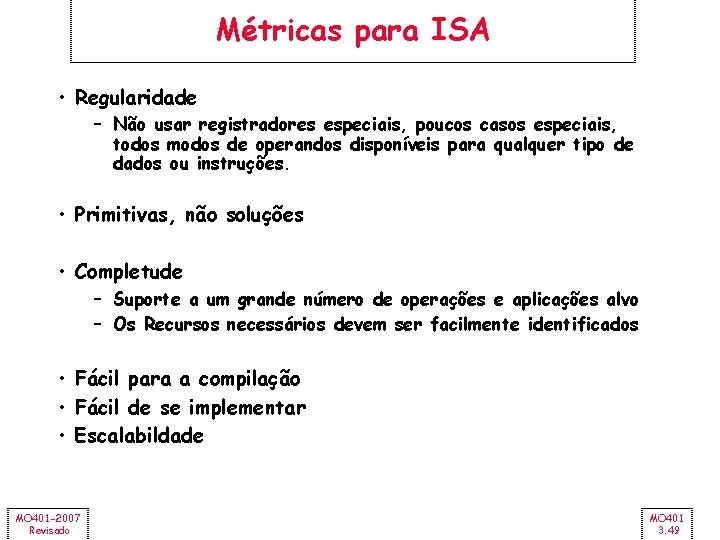

Propriedades do ISA que Simplificam o Compilador • Regularidade. • Fornecer Primitivas (e não soluções) • Simplificar as alternativas de compromissos. • Instruções que usam quantidades conhecidas em tempo de compilação como constantes. MO 401 -2007 Revisado MO 401 3. 48

Métricas para ISA • Regularidade – Não usar registradores especiais, poucos casos especiais, todos modos de operandos disponíveis para qualquer tipo de dados ou instruções. • Primitivas, não soluções • Completude – Suporte a um grande número de operações e aplicações alvo – Os Recursos necessários devem ser facilmente identificados • Fácil para a compilação • Fácil de se implementar • Escalabildade MO 401 -2007 Revisado MO 401 3. 49

IBM 360 MO 401 -2007 Revisado MO 401 3. 50

Cray MO 401 -2007 Revisado MO 401 3. 51