Microprocessorbased systems Course 2 General structure of a

Microprocessor-based systems Course 2 General structure of a computer 1

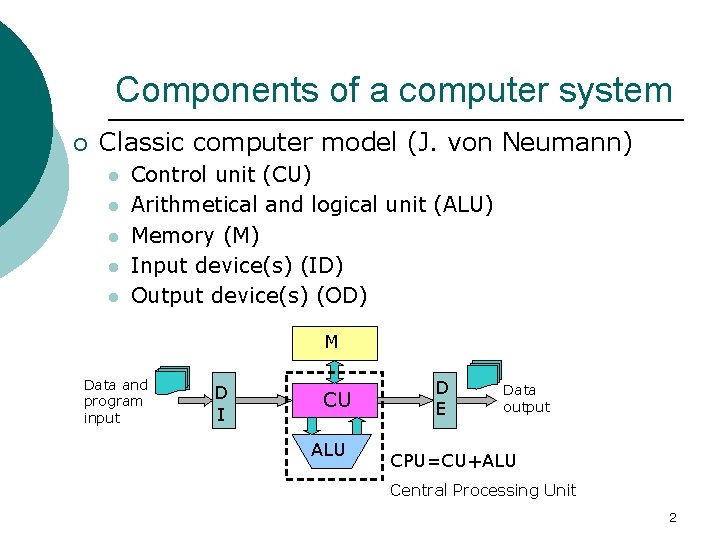

Components of a computer system ¡ Classic computer model (J. von Neumann) l l l Control unit (CU) Arithmetical and logical unit (ALU) Memory (M) Input device(s) (ID) Output device(s) (OD) M Data and program input D I CU ALU D E Data output CPU=CU+ALU Central Processing Unit 2

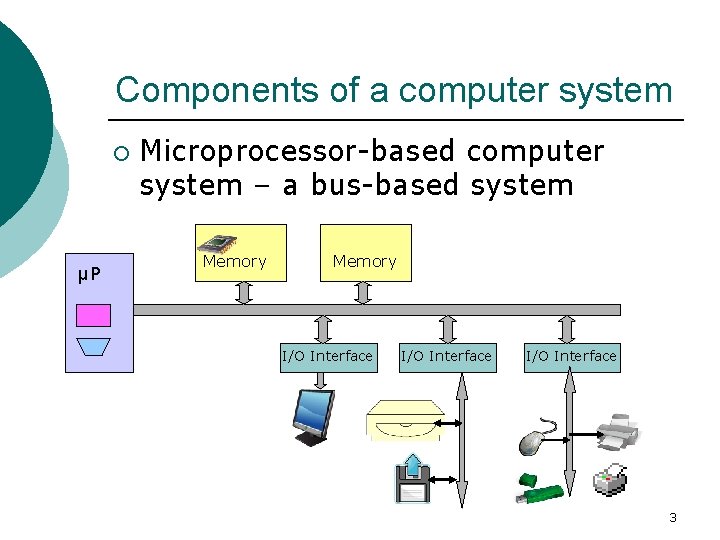

Components of a computer system ¡ μP Microprocessor-based computer system – a bus-based system Memory I/O Interface 3

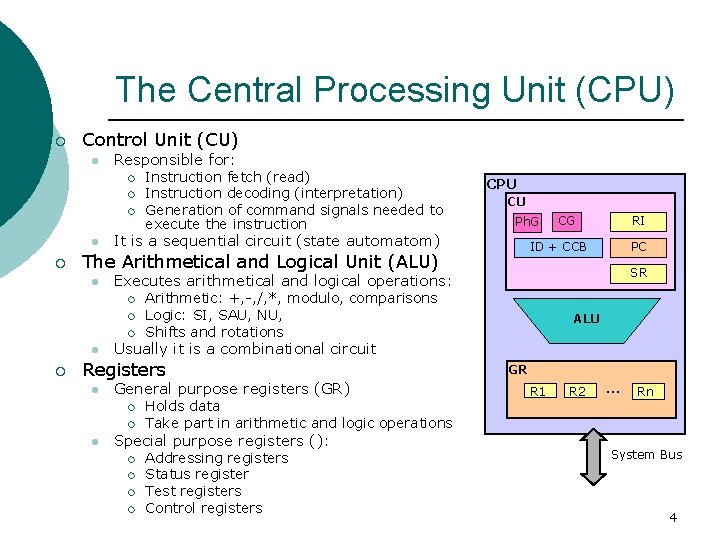

The Central Processing Unit (CPU) ¡ Control Unit (CU) l Responsible for: ¡ ¡ ¡ l ¡ CPU CU Ph. G It is a sequential circuit (state automatom) ¡ ¡ ALU Usually it is a combinational circuit General purpose registers (GR) ¡ ¡ l PC SR Arithmetic: +, -, /, *, modulo, comparisons Logic: SI, SAU, NU, Shifts and rotations Registers l RI Executes arithmetical and logical operations: ¡ l CG ID + CCB The Arithmetical and Logical Unit (ALU) l ¡ Instruction fetch (read) Instruction decoding (interpretation) Generation of command signals needed to execute the instruction Holds data Take part in arithmetic and logic operations Special purpose registers (): ¡ ¡ Addressing registers Status register Test registers Control registers GR R 1 R 2 … Rn System Bus 4

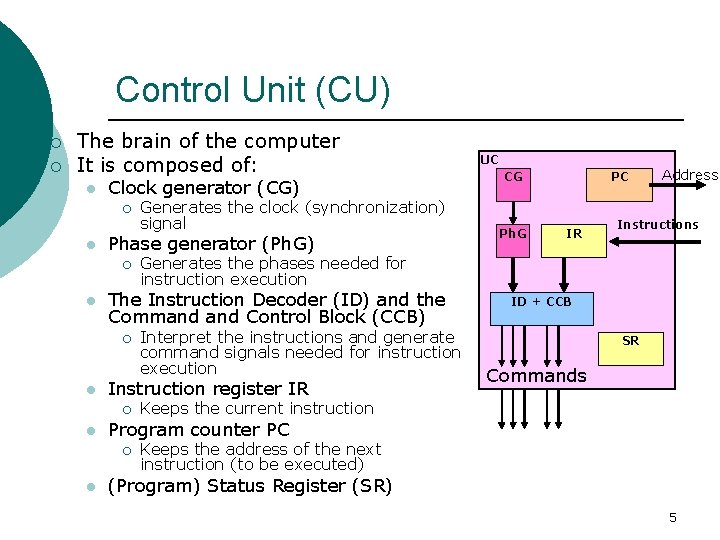

Control Unit (CU) ¡ ¡ The brain of the computer It is composed of: l Clock generator (CG) ¡ l Phase generator (Ph. G) ¡ l l Ph. G PC IR Address Instructions ID + CCB SR Commands Keeps the current instruction Program counter PC ¡ l Interpret the instructions and generate command signals needed for instruction execution Instruction register IR ¡ CG Generates the phases needed for instruction execution The Instruction Decoder (ID) and the Command Control Block (CCB) ¡ l Generates the clock (synchronization) signal UC Keeps the address of the next instruction (to be executed) (Program) Status Register (SR) 5

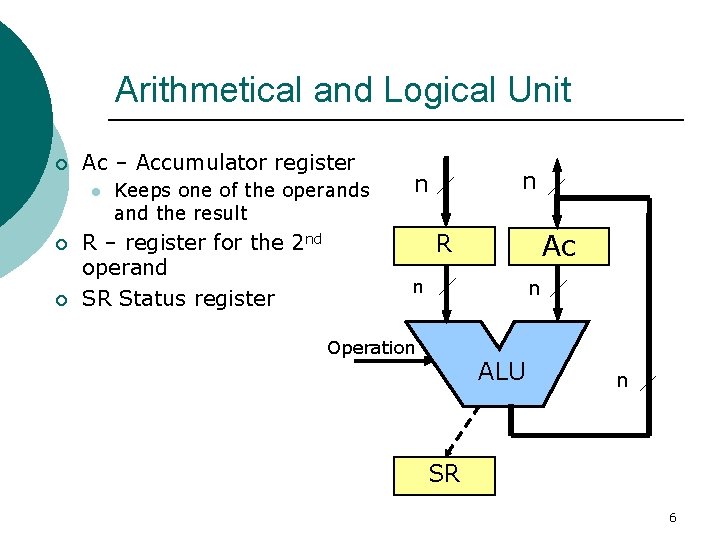

Arithmetical and Logical Unit ¡ Ac – Accumulator register l ¡ ¡ Keeps one of the operands and the result R – register for the 2 nd operand SR Status register n n R Ac n n Operation ALU n SR 6

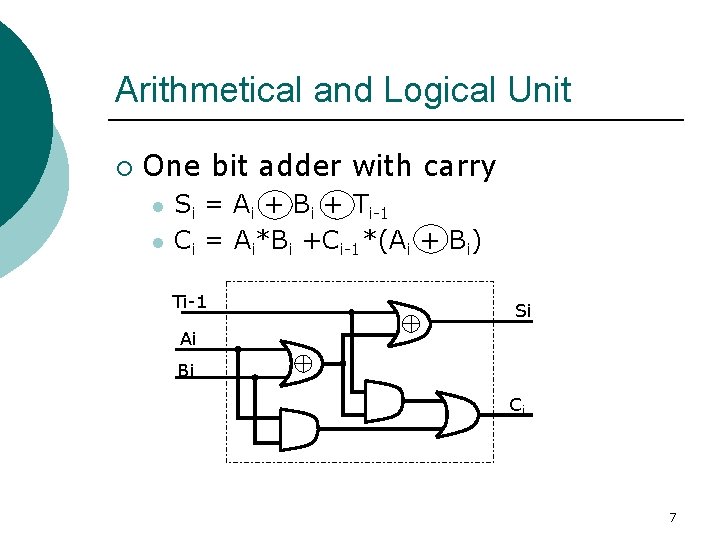

Arithmetical and Logical Unit ¡ One bit adder with carry l l Si = Ai + Bi + Ti-1 Ci = Ai*Bi +Ci-1*(Ai + Bi) Ti-1 Si Ai Bi Ci 7

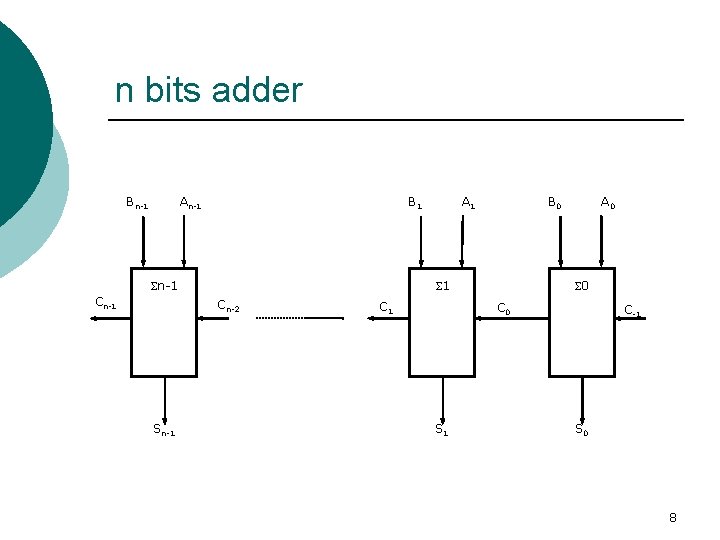

n bits adder Bn-1 An-1 B 1 n-1 Cn-1 B 0 1 Cn-2 Sn-1 A 1 C 1 A 0 0 C 0 S 1 C-1 S 0 8

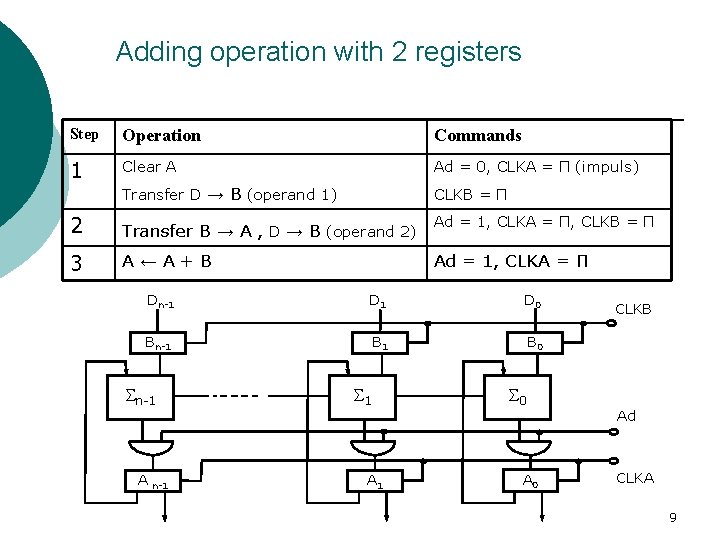

Adding operation with 2 registers Step Operation Commands 1 Clear A Ad = 0, CLKA = П (impuls) Transfer D → B (operand 1) CLKB = П 2 Transfer B → A , D → B (operand 2) 3 A←A+B Ad = 1, CLKA = П, CLKB = П Ad = 1, CLKA = П Dn-1 D 0 Bn-1 B 0 n-1 A n-1 1 A 1 0 A 0 CLKB Ad CLKA 9

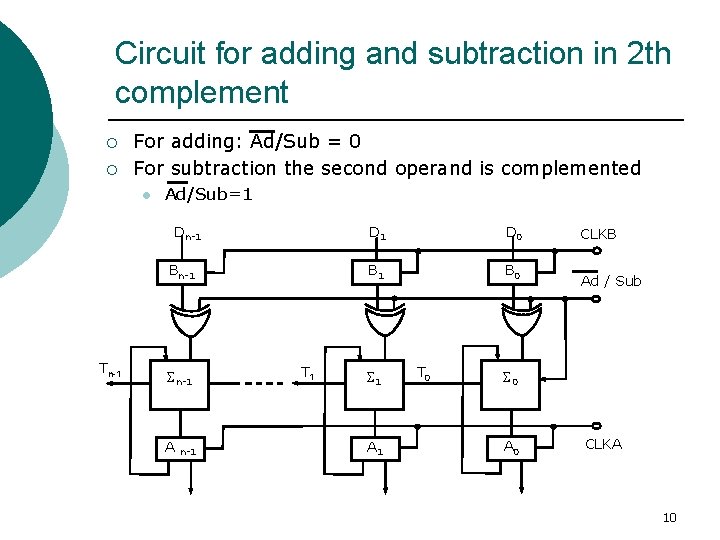

Circuit for adding and subtraction in 2 th complement ¡ ¡ For adding: Ad/Sub = 0 For subtraction the second operand is complemented l Ad/Sub=1 Dn-1 Bn-1 Tn-1 A n-1 T 1 D 0 B 1 B 0 1 A 1 T 0 CLKB Ad / Sub 0 A 0 CLKA 10

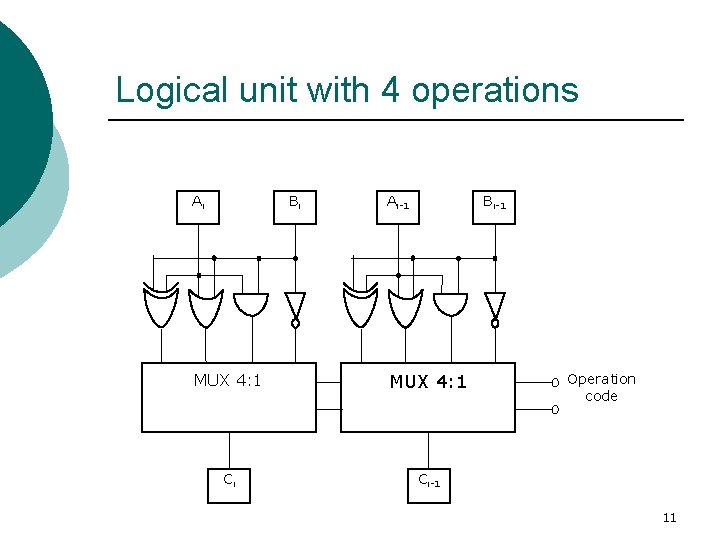

Logical unit with 4 operations Ai Bi Ai-1 Bi-1 MUX 4: 1 Ci Ci-1 Operation code 11

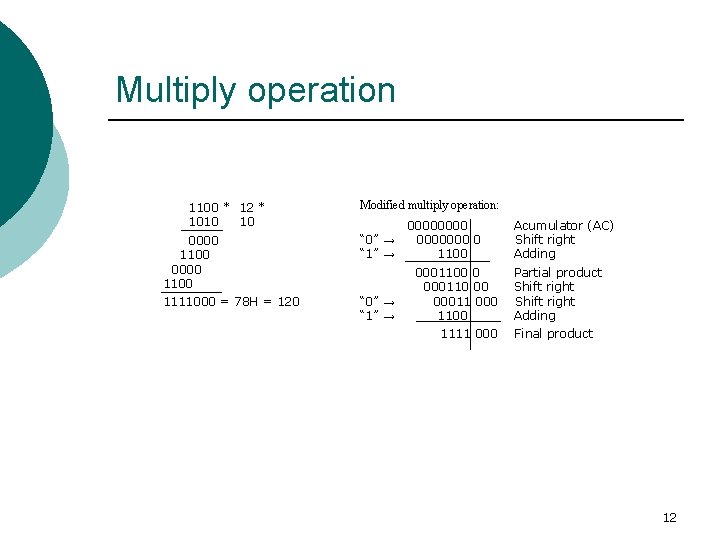

Multiply operation 1100 * 12 * 1010 10 Modified multiply operation: 0000 1100 “ 0” → “ 1” → 1111000 = 78 H = 120 “ 0” → “ 1” → 0000000 0 1100 0001100 0 000110 00 00011 000 1111 000 Acumulator (AC) Shift right Adding Partial product Shift right Adding Final product 12

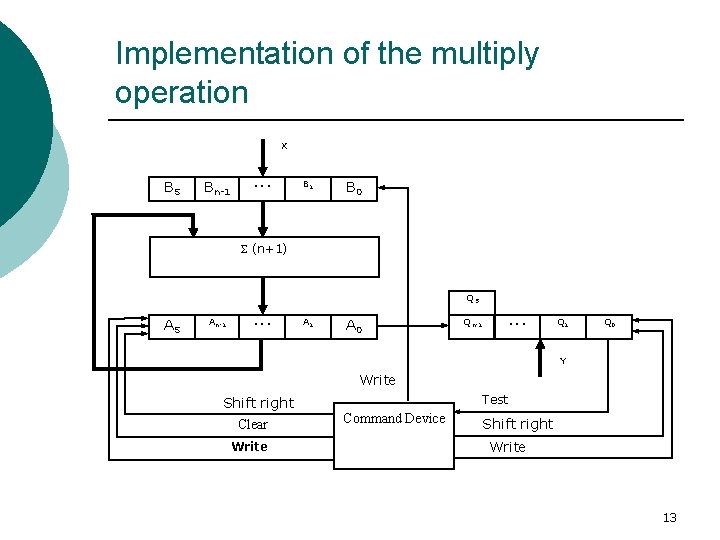

Implementation of the multiply operation X BS Bn-1 . . . B 1 B 0 (n+1) QS AS An-1 . . . A 1 A 0 Q n-1 . . . Q 1 Q 0 Y Write Shift right Clear Write Test Command Device Shift right Write 13

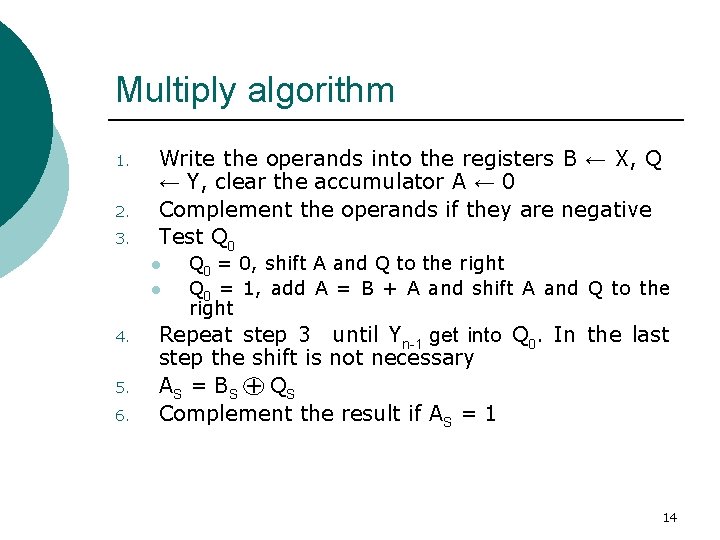

Multiply algorithm 1. 2. 3. Write the operands into the registers B ← X, Q ← Y, clear the accumulator A ← 0 Complement the operands if they are negative Test Q 0 l l 4. 5. 6. Q 0 = 0, shift A and Q to the right Q 0 = 1, add A = B + A and shift A and Q to the right Repeat step 3 until Yn-1 get into Q 0. In the last step the shift is not necessary AS = B S + Q S Complement the result if AS = 1 14

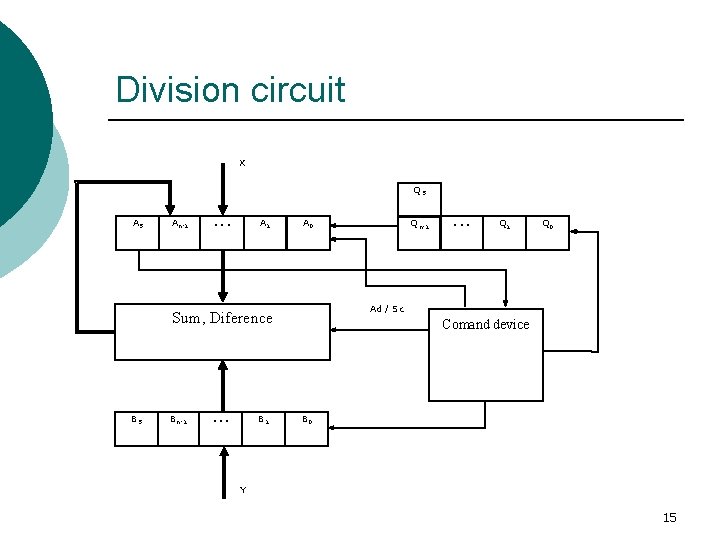

Division circuit X QS AS An-1 . . . A 1 A 0 Bn-1 . . . B 1 . . . Q 1 Q 0 Ad / Sc Sum, Diference BS Q n-1 Comand device B 0 Y 15

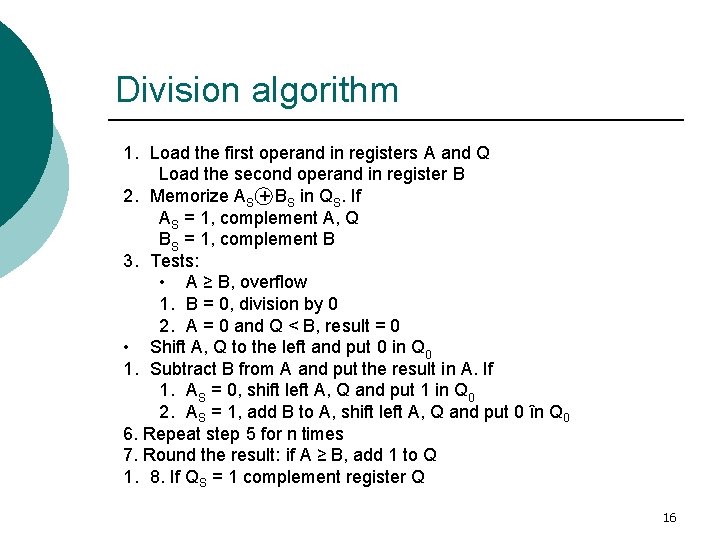

Division algorithm 1. Load the first operand in registers A and Q Load the second operand in register B 2. Memorize AS + BS in QS. If AS = 1, complement A, Q BS = 1, complement B 3. Tests: • A ≥ B, overflow 1. B = 0, division by 0 2. A = 0 and Q < B, result = 0 • Shift A, Q to the left and put 0 in Q 0 1. Subtract B from A and put the result in A. If 1. AS = 0, shift left A, Q and put 1 in Q 0 2. AS = 1, add B to A, shift left A, Q and put 0 în Q 0 6. Repeat step 5 for n times 7. Round the result: if A ≥ B, add 1 to Q 1. 8. If QS = 1 complement register Q 16

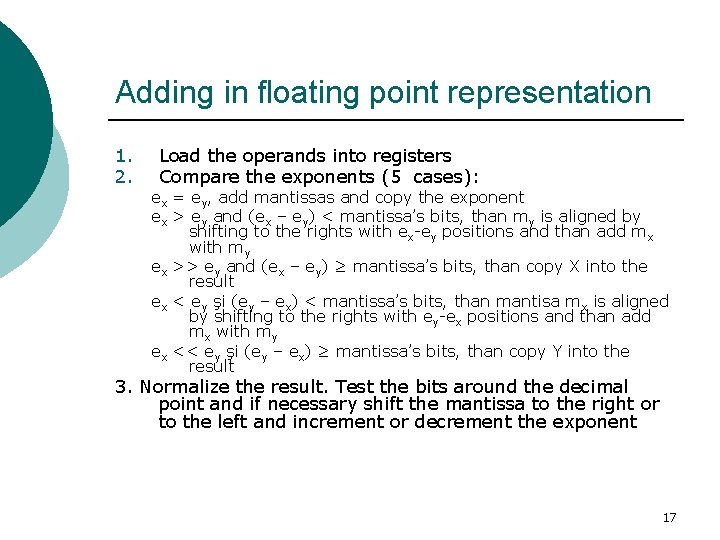

Adding in floating point representation 1. 2. Load the operands into registers Compare the exponents (5 cases): ex = ey, add mantissas and copy the exponent ex > ey and (ex – ey) < mantissa’s bits, than my is aligned by shifting to the rights with ex-ey positions and than add mx with my ex >> ey and (ex – ey) ≥ mantissa’s bits, than copy X into the result ex < ey şi (ey – ex) < mantissa’s bits, than mantisa mx is aligned by shifting to the rights with ey-ex positions and than add mx with my ex << ey şi (ey – ex) ≥ mantissa’s bits, than copy Y into the result 3. Normalize the result. Test the bits around the decimal point and if necessary shift the mantissa to the right or to the left and increment or decrement the exponent 17

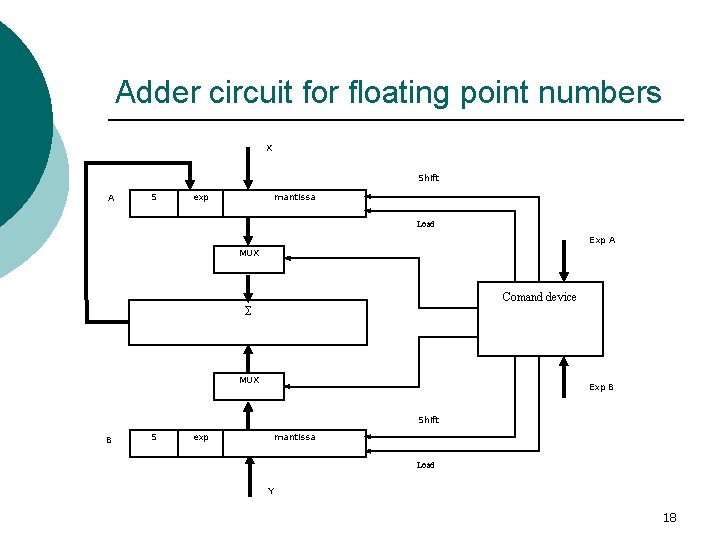

Adder circuit for floating point numbers X Shift A S exp mantissa Load Exp A MUX Comand device Σ MUX Exp B Shift B S exp mantissa Load Y 18

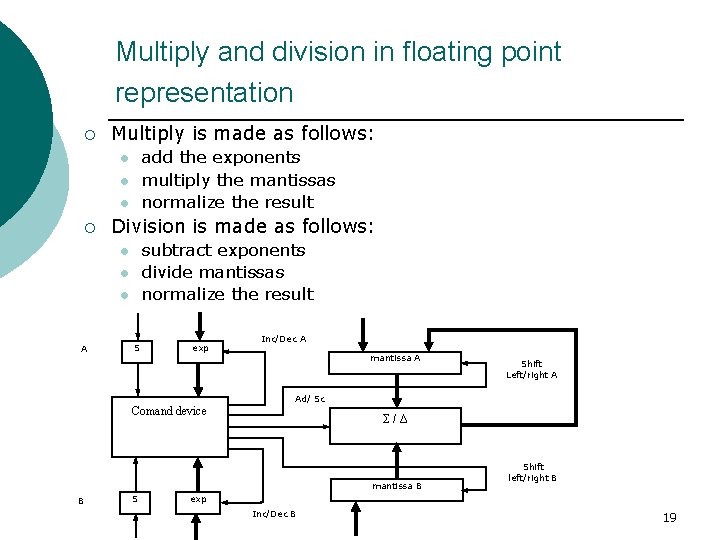

Multiply and division in floating point representation ¡ Multiply is made as follows: add the exponents multiply the mantissas normalize the result l l l ¡ Division is made as follows: subtract exponents divide mantissas normalize the result l l l A S exp Inc/Dec A mantissa A Shift Left/right A Ad/ Sc Comand device Σ/Δ mantissa B B S Shift left/right B exp Inc/Dec B 19

Design of a simple computer Design steps: 1. Establish the destination and the domain of use for the computer; 2 Define the instruction set and instruction format; 3 Design the block scheme of the central processing unit; 4 Decompose instructions into micro-operations and phases; 5 Define the logical equations/functions for the micro-comands; 6 Design the logical scheme for the Ph. G and CCB; 7 design the other modules: IR, PC, GR, ALU, SR, CG; 8 Design of memory modules; 9 Design of I/O interfaces; 10 Optimize the scheme through steps 2 -9 20

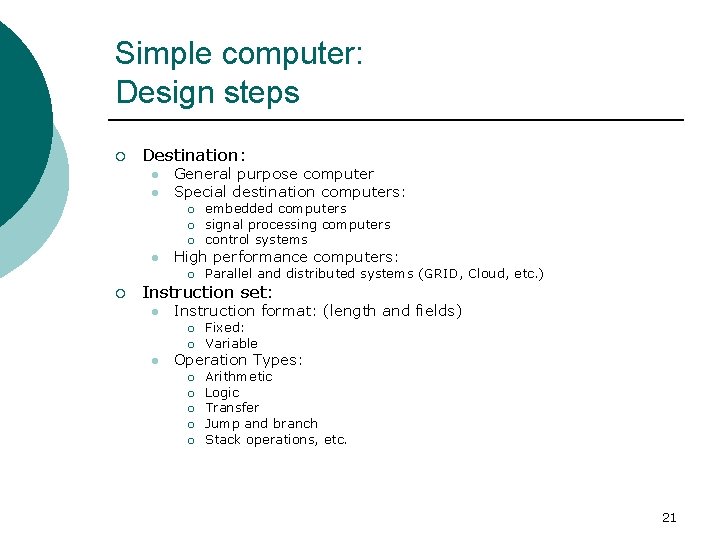

Simple computer: Design steps ¡ Destination: l l General purpose computer Special destination computers: ¡ ¡ ¡ l High performance computers: ¡ ¡ embedded computers signal processing computers control systems Parallel and distributed systems (GRID, Cloud, etc. ) Instruction set: l Instruction format: (length and fields) ¡ ¡ l Fixed: Variable Operation Types: ¡ ¡ ¡ Arithmetic Logic Transfer Jump and branch Stack operations, etc. 21

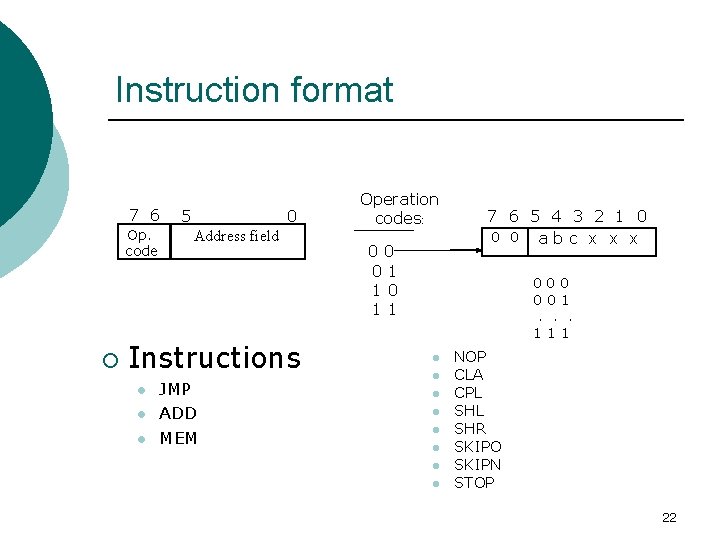

Instruction format 7 6 Op. code ¡ 5 0 Address field Instructions l l l JMP ADD MEM Operation codes: 00 01 10 11 7 6 5 4 3 2 1 0 0 0 a b c x x x 000 001. . . 111 l l l l NOP CLA CPL SHR SKIPO SKIPN STOP 22

- Slides: 22