MICROPROCESADORES Y CONTROL DE PERIFRICOS MICROPROCESADORES DE 32

- Slides: 67

MICROPROCESADORES Y CONTROL DE PERIFÉRICOS MICROPROCESADORES DE 32 BITS Prof. Juan Álvarez

MICROPROCESADORES DE 32 BITS • • Microprocesador 80386 Microprocesador 80486 Diagrama de bloques y registros Diagrama de patillas Paginación y memoria virtual El coprocesador Memoria caché

MICROPROCESADOR 80386 El microprocesador 80386 aparece en 1985 y presenta un bus de datos de 32 bits, un bus de direcciones de 32 bits y tiene una mayor velocidad de procesamiento que el 80286. Maneja aplicaciones como la Interfaz Gráfica de Usuario, tratando 256000 píxeles de formato de pantalla de 640 píxeles por cada una de las 480 líneas.

MICROPROCESADOR 80386 El 80386 consta de más de 275. 000 transistores y está fabricado en tecnología CHMOS. Existen dos versiones iniciales para funcionar a 12, 5 y 16 MHz. Su velocidad de funcionamiento oscila entre 3 y 4 MIPS (Millones de Instrucciones por Segundo) y la capacidad de direccionamiento de memoria virtual supera los 64 trillones de bytes.

MICROPROCESADOR 80386 Soporta una configuración multitarea que permite realizar distintos programas escritos en entornos correspondientes a diversos sistemas operativos. La Unidad de Manejo de Memoria (MMU) soporta los dos métodos de gestión de memoria más empleados: la segmentación y la paginación.

MICROPROCESADOR 80386 Otra característica avanzada del 80386 la constituye la propia comprobación de más de las tres cuartas partes de las funciones internas y se procede en el momento de aplicar la tensión de alimentación. Una novedad de este microprocesador es la de permitir generar interrupciones cuando se accede a la memoria de datos.

MICROPROCESADOR 80386 En este procesador se potencia el repertorio de instrucciones orientado a la simplificación de las tareas más comunes: • Los cálculos aritméticos de gran precisión (64 bits). • Las operaciones complejas de manipulación de bits orientadas hacia los sistemas gráficos. • La transferencia de información usada en los sistemas de comunicación de datos.

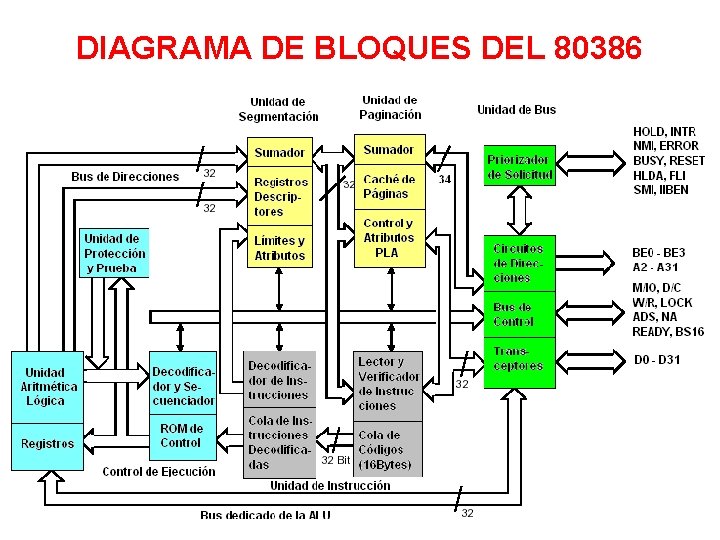

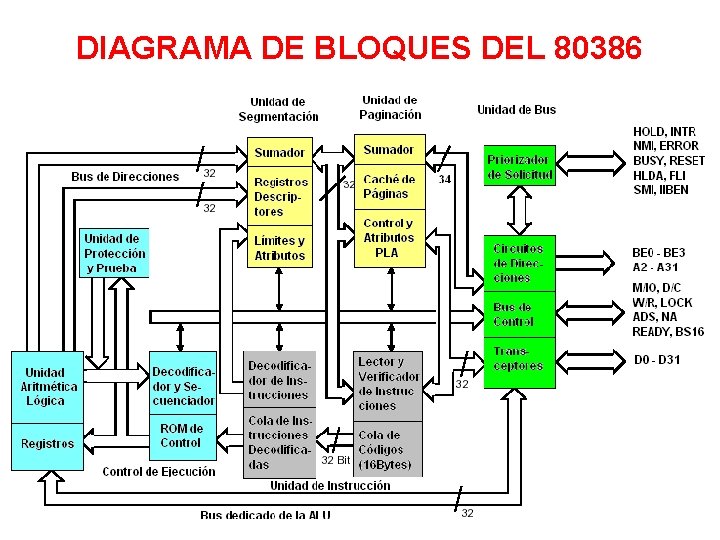

DIAGRAMA DE BLOQUES DEL 80386 El 80386 consta de tres grandes bloques: • Unidad Central de Proceso (CPU) donde figura la ALU, el control de ejecución y la unidad de instrucción. • Unidad de Manejo de Memoria (MMU) que comprende la unidad de segmentación y la unidad de paginación. • Unidad de Interfaz de Bus (BIU).

DIAGRAMA DE BLOQUES DEL 80386

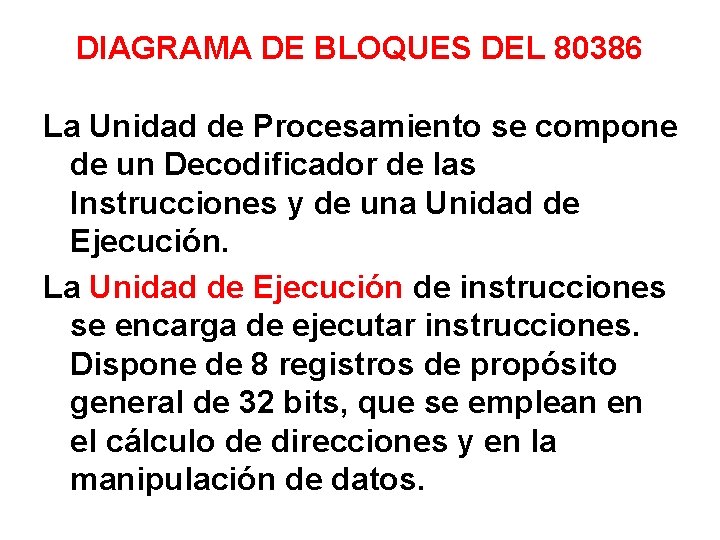

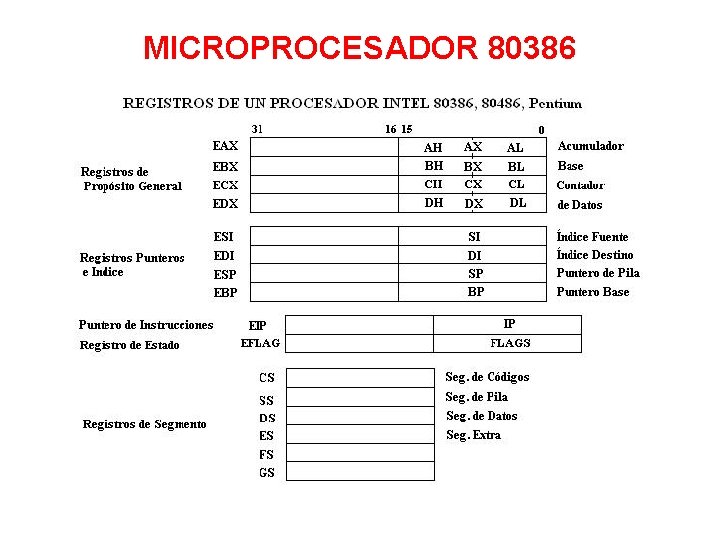

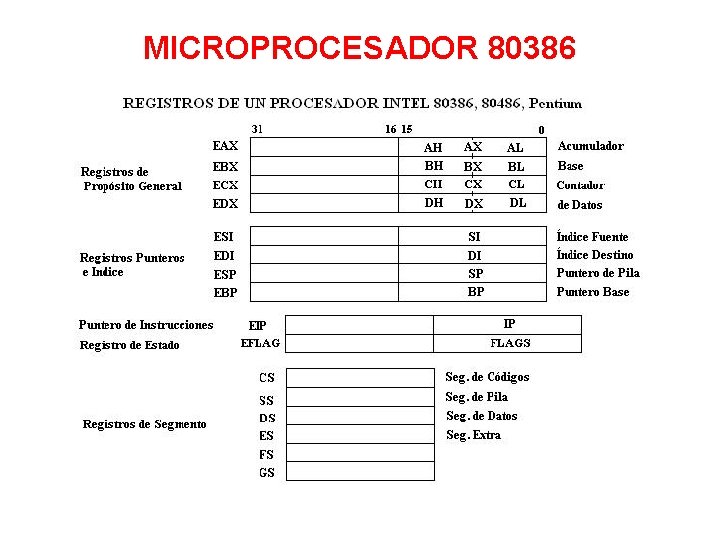

DIAGRAMA DE BLOQUES DEL 80386 La Unidad de Procesamiento se compone de un Decodificador de las Instrucciones y de una Unidad de Ejecución. La Unidad de Ejecución de instrucciones se encarga de ejecutar instrucciones. Dispone de 8 registros de propósito general de 32 bits, que se emplean en el cálculo de direcciones y en la manipulación de datos.

MICROPROCESADOR 80386

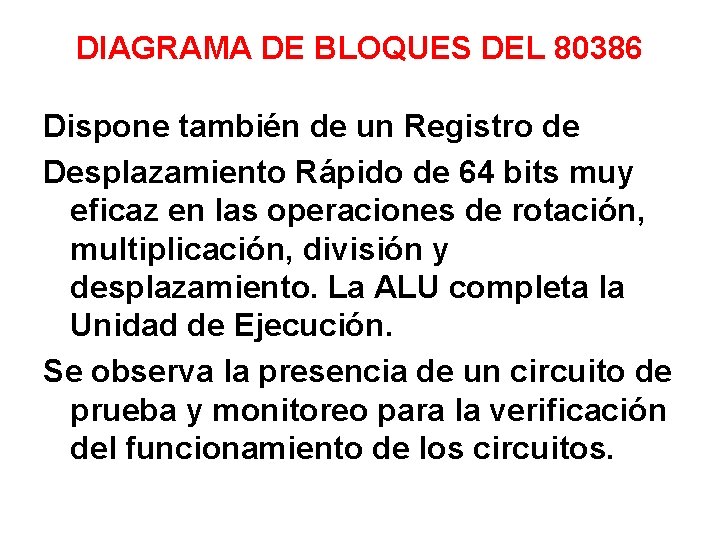

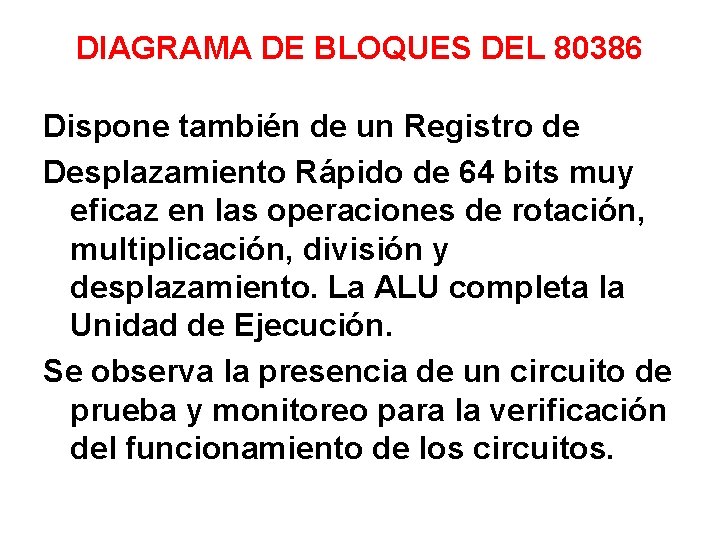

DIAGRAMA DE BLOQUES DEL 80386 Dispone también de un Registro de Desplazamiento Rápido de 64 bits muy eficaz en las operaciones de rotación, multiplicación, división y desplazamiento. La ALU completa la Unidad de Ejecución. Se observa la presencia de un circuito de prueba y monitoreo para la verificación del funcionamiento de los circuitos.

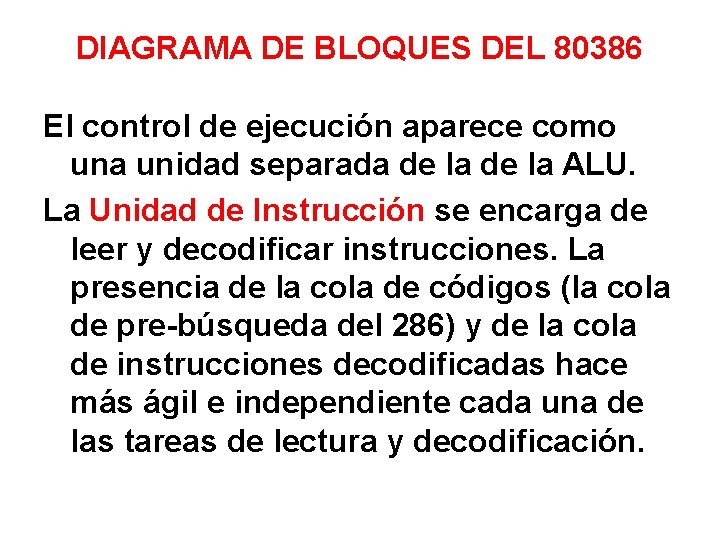

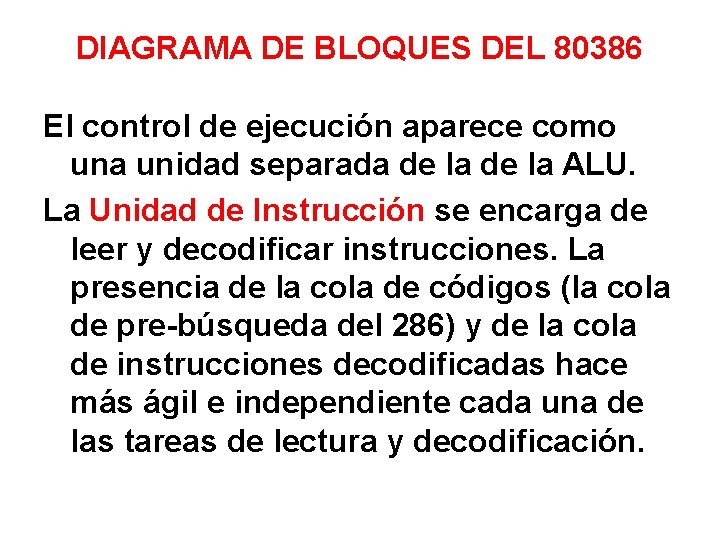

DIAGRAMA DE BLOQUES DEL 80386 El control de ejecución aparece como una unidad separada de la ALU. La Unidad de Instrucción se encarga de leer y decodificar instrucciones. La presencia de la cola de códigos (la cola de pre-búsqueda del 286) y de la cola de instrucciones decodificadas hace más ágil e independiente cada una de las tareas de lectura y decodificación.

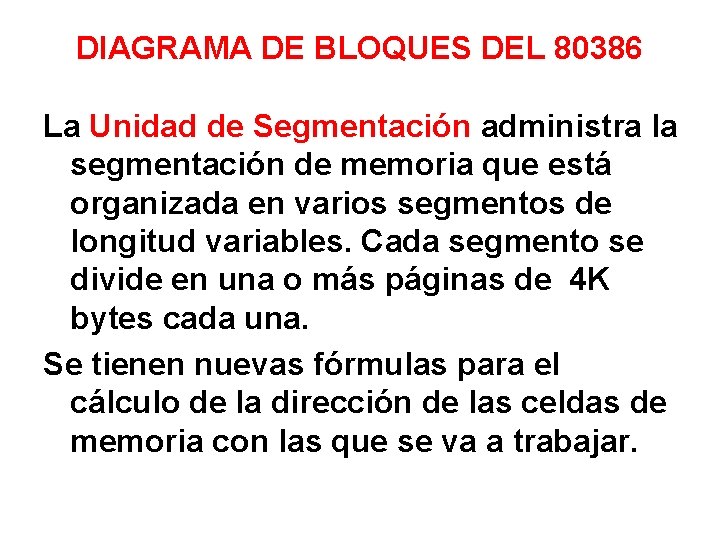

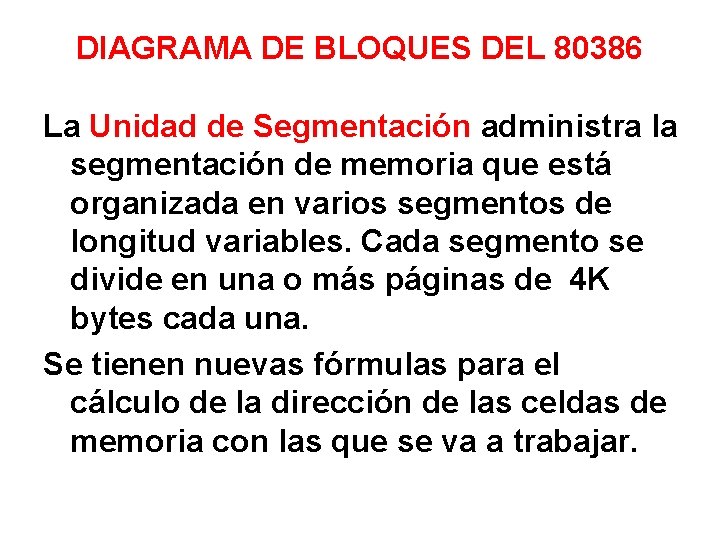

DIAGRAMA DE BLOQUES DEL 80386 La Unidad de Segmentación administra la segmentación de memoria que está organizada en varios segmentos de longitud variables. Cada segmento se divide en una o más páginas de 4 K bytes cada una. Se tienen nuevas fórmulas para el cálculo de la dirección de las celdas de memoria con las que se va a trabajar.

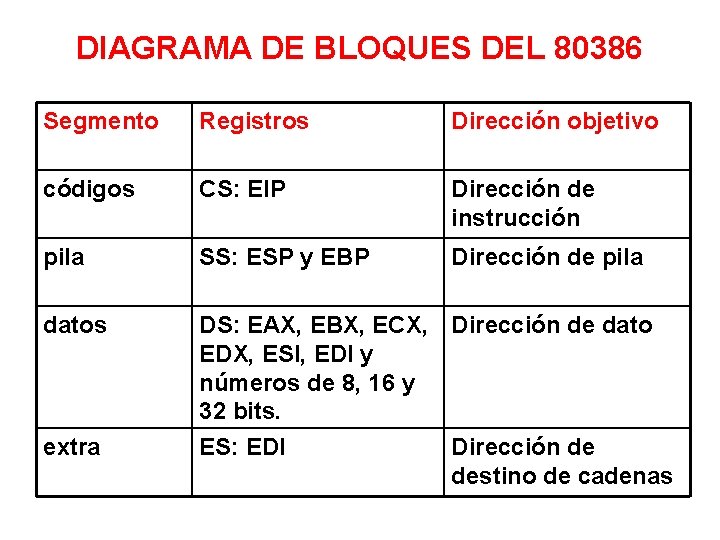

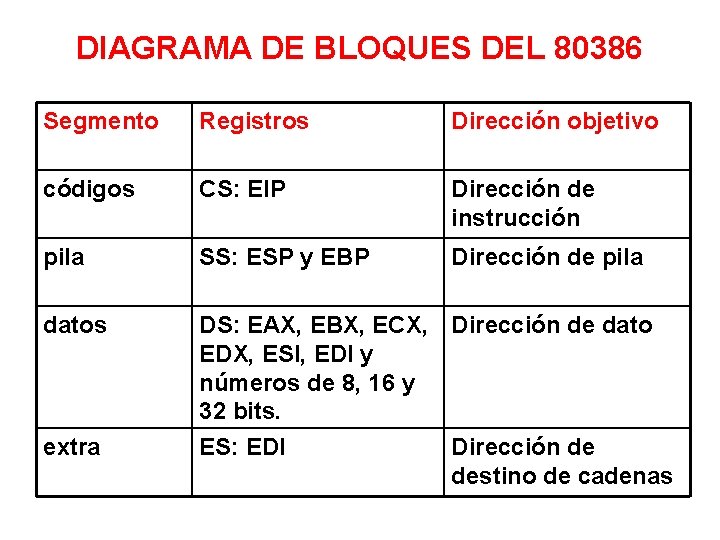

DIAGRAMA DE BLOQUES DEL 80386 Segmento Registros Dirección objetivo códigos CS: EIP Dirección de instrucción pila SS: ESP y EBP Dirección de pila datos DS: EAX, EBX, ECX, Dirección de dato EDX, ESI, EDI y números de 8, 16 y 32 bits. ES: EDI Dirección de destino de cadenas extra

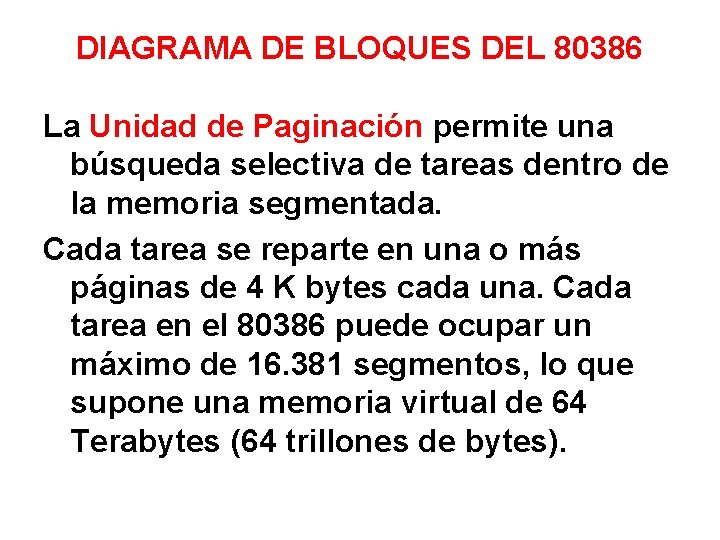

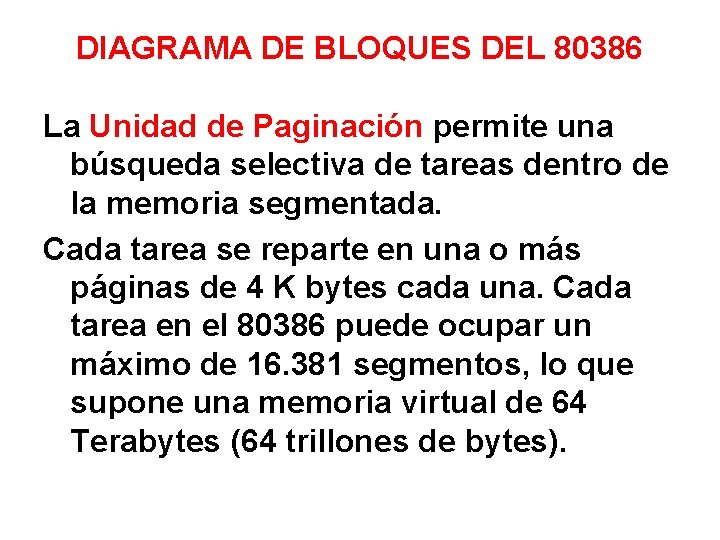

DIAGRAMA DE BLOQUES DEL 80386 La Unidad de Paginación permite una búsqueda selectiva de tareas dentro de la memoria segmentada. Cada tarea se reparte en una o más páginas de 4 K bytes cada una. Cada tarea en el 80386 puede ocupar un máximo de 16. 381 segmentos, lo que supone una memoria virtual de 64 Terabytes (64 trillones de bytes).

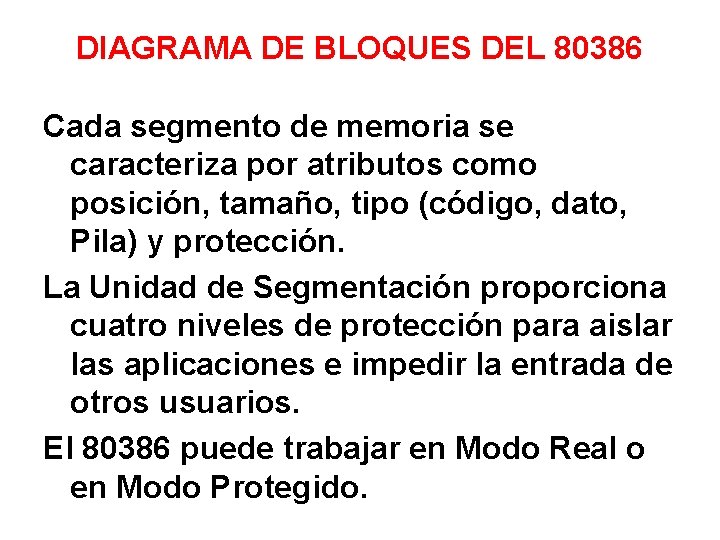

DIAGRAMA DE BLOQUES DEL 80386 Cada segmento de memoria se caracteriza por atributos como posición, tamaño, tipo (código, dato, Pila) y protección. La Unidad de Segmentación proporciona cuatro niveles de protección para aislar las aplicaciones e impedir la entrada de otros usuarios. El 80386 puede trabajar en Modo Real o en Modo Protegido.

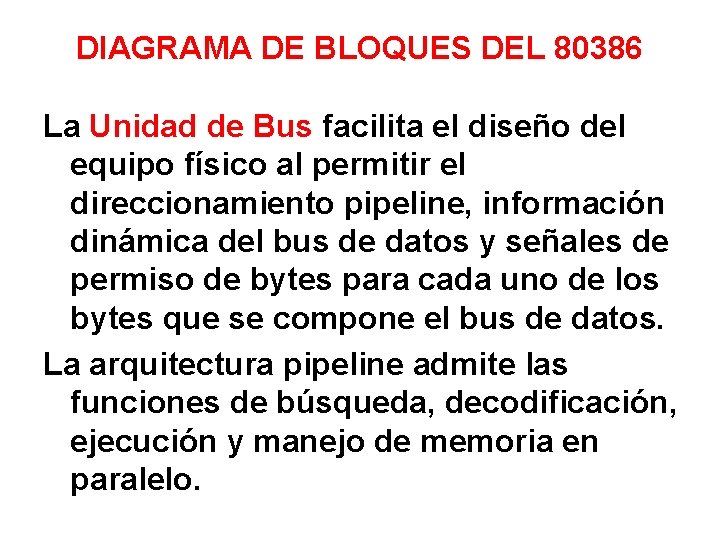

DIAGRAMA DE BLOQUES DEL 80386 La Unidad de Bus facilita el diseño del equipo físico al permitir el direccionamiento pipeline, información dinámica del bus de datos y señales de permiso de bytes para cada uno de los bytes que se compone el bus de datos. La arquitectura pipeline admite las funciones de búsqueda, decodificación, ejecución y manejo de memoria en paralelo.

MICROPROCESADOR 80486 El 80486 tiene 32 bits en el bus de direcciones y 32 bits en el bus de datos. Es un circuito integrado conformado por 1'200, 000 transistores. Con respecto al 80386, este procesador incluye una Unidad de Punto Flotante, que es el Coprocesador Matemático, similar al 80387. La Unidad de Administración de memoria incluye una Unidad de Memoria Caché de alta velocidad de 8 Kbytes.

MICROPROCESADOR 80486 Opera en las frecuencias de 25, 33, 50 o 66 MHz. Se encuentra en un encapsulado PGA de 168 patillas. El consumo de corriente es de 1. 2 Amperios para una fuente de 5 Voltios en la versión de 33 MHz (el consumo promedio es de 625 m. A).

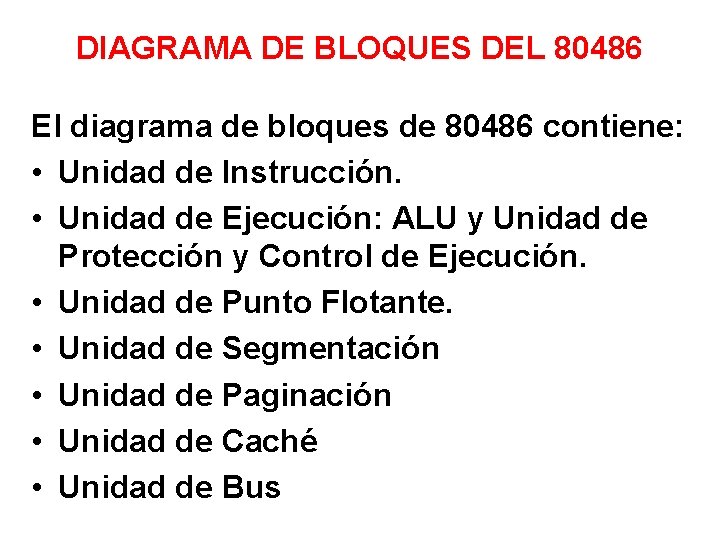

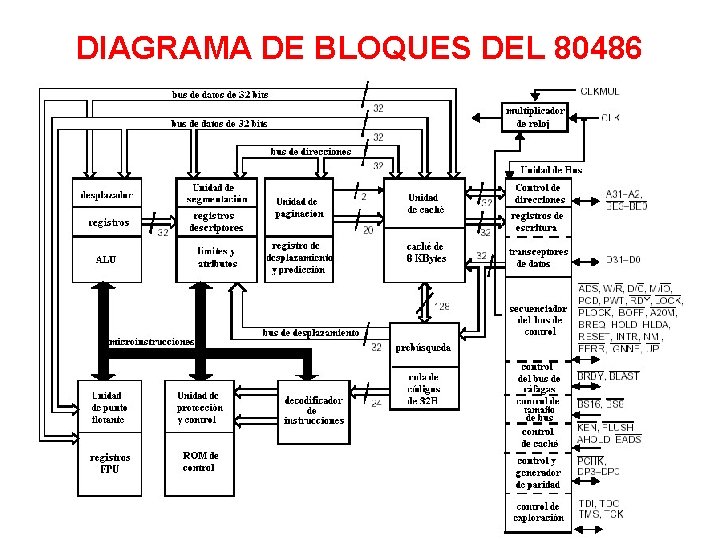

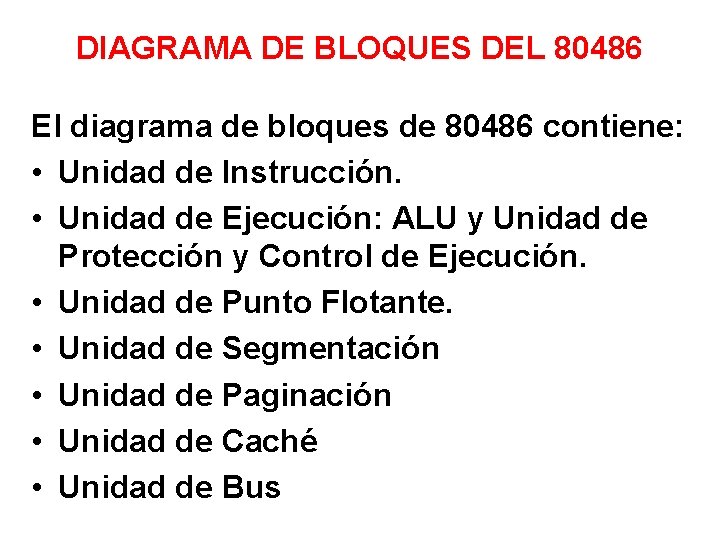

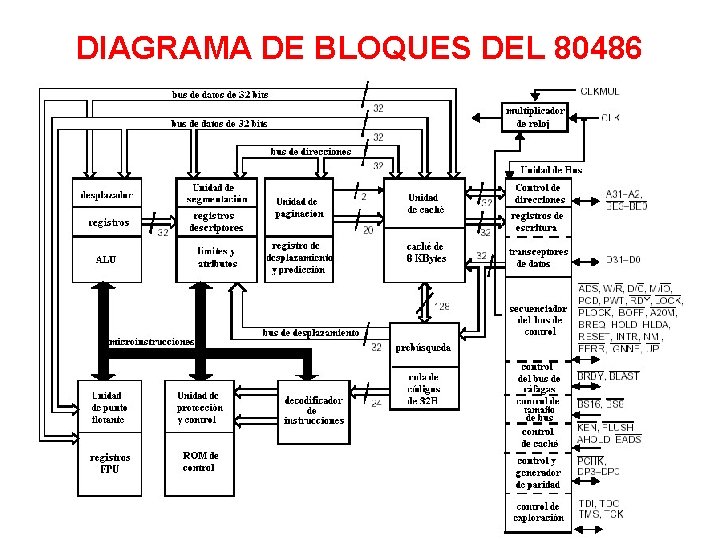

DIAGRAMA DE BLOQUES DEL 80486 El diagrama de bloques de 80486 contiene: • Unidad de Instrucción. • Unidad de Ejecución: ALU y Unidad de Protección y Control de Ejecución. • Unidad de Punto Flotante. • Unidad de Segmentación • Unidad de Paginación • Unidad de Caché • Unidad de Bus

DIAGRAMA DE BLOQUES DEL 80486

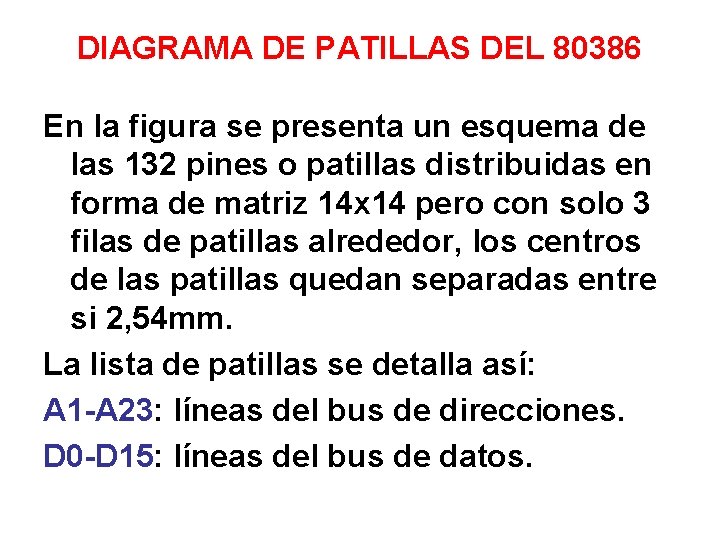

DIAGRAMA DE PATILLAS DEL 80386

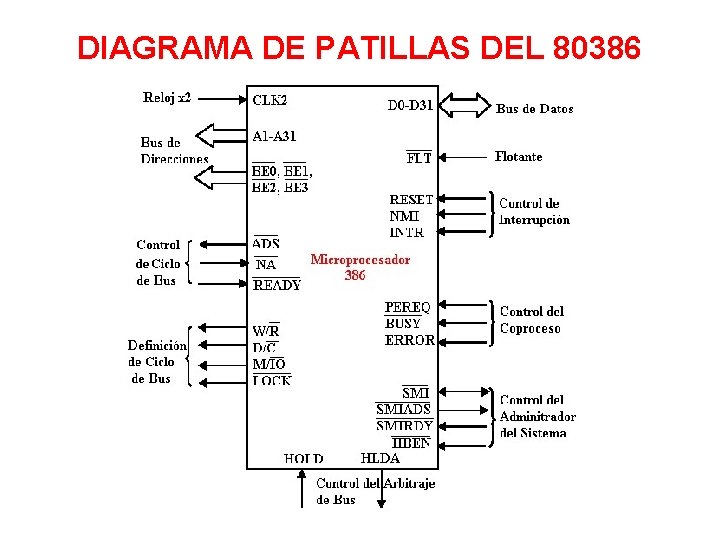

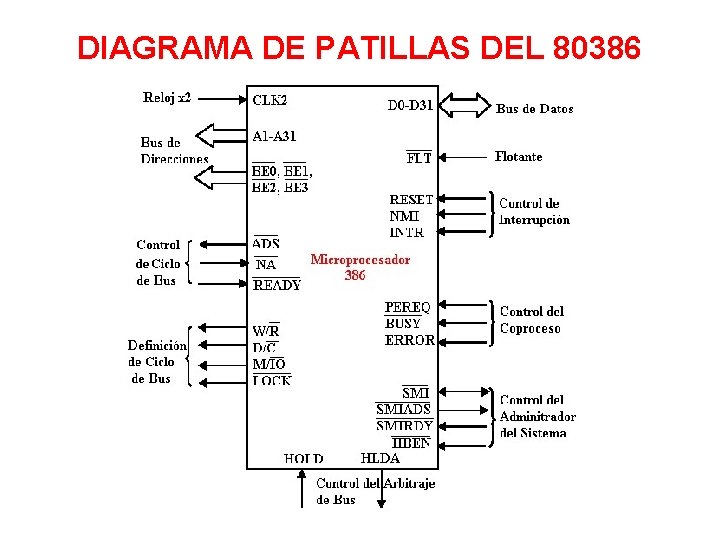

DIAGRAMA DE PATILLAS DEL 80386 En la figura se presenta un esquema de las 132 pines o patillas distribuidas en forma de matriz 14 x 14 pero con solo 3 filas de patillas alrededor, los centros de las patillas quedan separadas entre si 2, 54 mm. La lista de patillas se detalla así: A 1 -A 23: líneas del bus de direcciones. D 0 -D 15: líneas del bus de datos.

DIAGRAMA DE PATILLAS DEL 80386

DIAGRAMA DE PATILLAS DEL 80386 BE 0 -BE 3: habilitan los bancos de memoria de 8, 16 y 32 bits. M/IO: selecciona un dispositivo de memoria cuando su valor es uno, o un dispositivo de E/S cuando es cero. W/R: indica solicitud de lectura (0) o de escritura (1) ADS: pulso de direccionamiento activo cuando el procesador emite una dirección de memoria o de E/S

DIAGRAMA DE PATILLAS DEL 80386 Reset: reinicialización, borra el contenido de la memoria y comienza a ejecutar los programas a partir de la localidad de memoria FFFFFFF 0 h. CLK 2: Reloj externo cuya frecuencia es el doble de la frecuencia de operación del procesador. READY: controla el estado de espera del procesador en un ciclo de acceso a la memoria.

DIAGRAMA DE PATILLAS DEL 80386 LOCK: se utiliza durante los accesos del DMA y asume el valor cero cuando una instrucción tiene el prefijo Lock. D/C: indica que el bus de datos tiene datos para la memoria o un puerto E/S. BS 16: selecciona un bus de datos de 32 bits o un bus de datos de 16 bits. NA: se emite la dirección de la siguiente instrucción.

DIAGRAMA DE PATILLAS DEL 80386 HOLD: solicita los buses para el uso del DMA. HLDA: aviso de ceder el control de los buses. PEREQ: el procesador está detenido. BUSY: el coprocesador está trabajando. ERROR: el coprocesador ha detectado un error. INTR: solicitud de interrupción. NMI: interrupción no enmascarable.

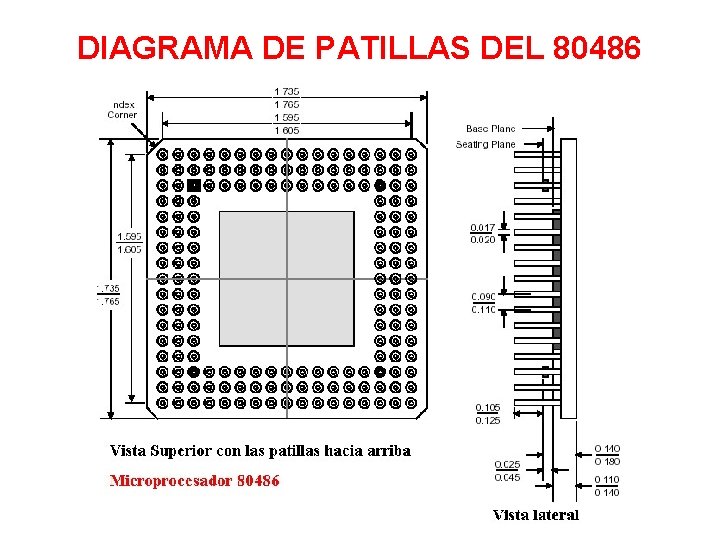

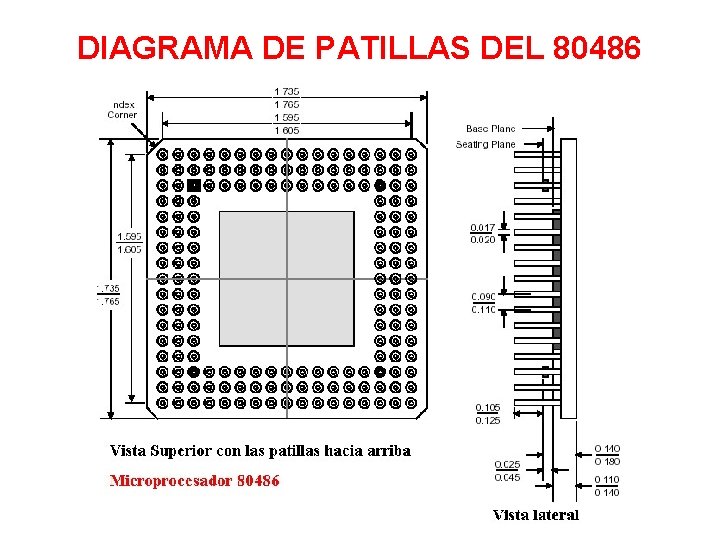

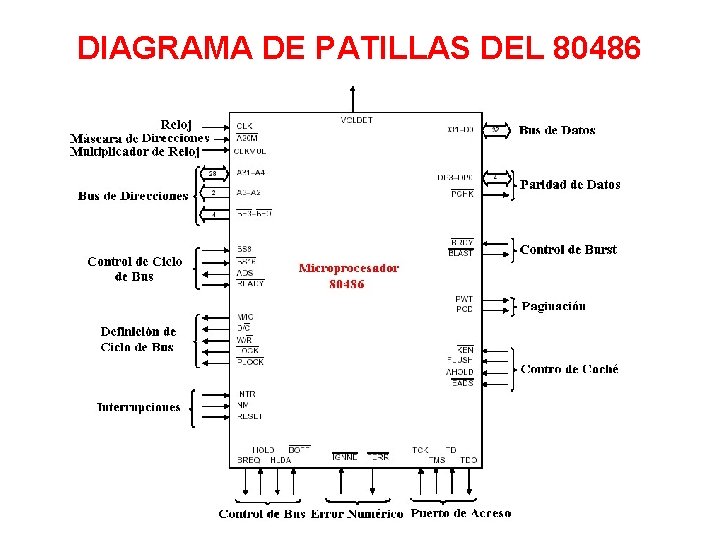

DIAGRAMA DE PATILLAS DEL 80486 La siguiente figura ilustra el chip del procesador 80486 que es una PGA (arreglo de malla de pines) de 168 patillas. La fuente de alimentación debe proporcionar 5 V con una corriente pico de 1. 2 A para la versión de 33 MHz y una corriente promedio de 650 m. A. El diagrama de patillas se ilustra en la siguiente figura, las mismas que se decriben a continuación.

DIAGRAMA DE PATILLAS DEL 80486

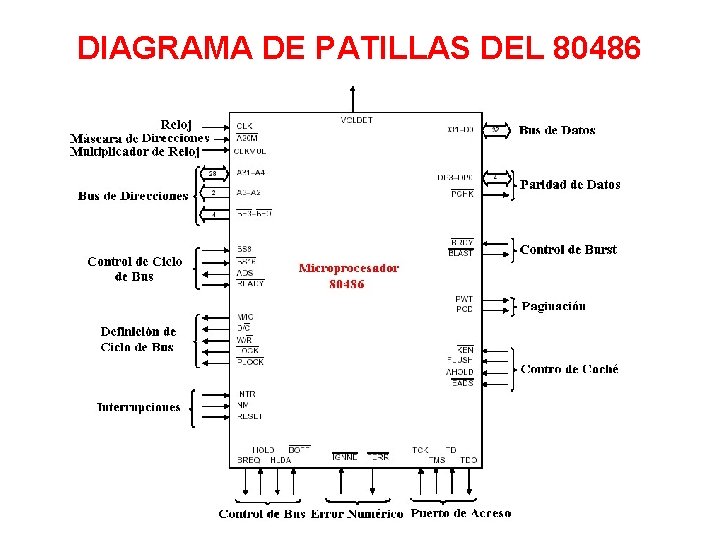

DIAGRAMA DE PATILLAS DEL 80486

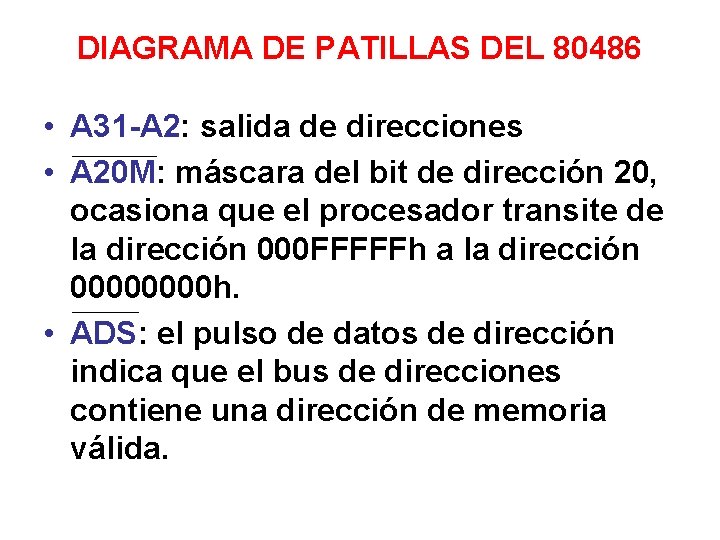

DIAGRAMA DE PATILLAS DEL 80486 • A 31 -A 2: salida de direcciones • A 20 M: máscara del bit de dirección 20, ocasiona que el procesador transite de la dirección 000 FFFFFh a la dirección 0000 h. • ADS: el pulso de datos de dirección indica que el bus de direcciones contiene una dirección de memoria válida.

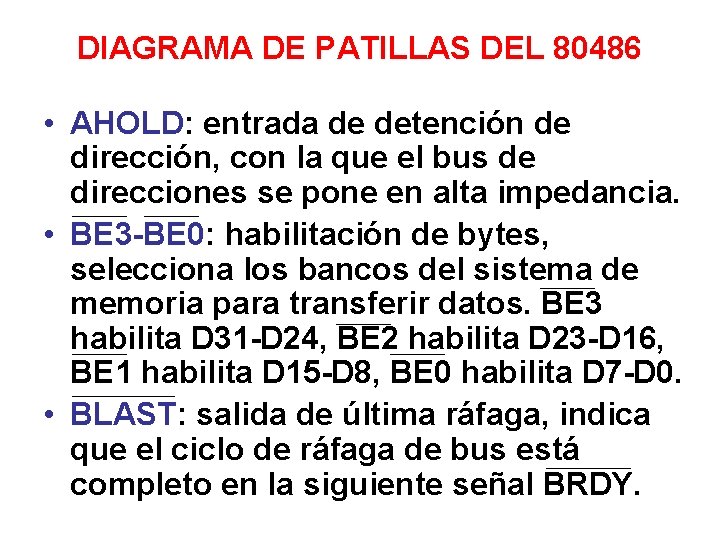

DIAGRAMA DE PATILLAS DEL 80486 • AHOLD: entrada de detención de dirección, con la que el bus de direcciones se pone en alta impedancia. • BE 3 -BE 0: habilitación de bytes, selecciona los bancos del sistema de memoria para transferir datos. BE 3 habilita D 31 -D 24, BE 2 habilita D 23 -D 16, BE 1 habilita D 15 -D 8, BE 0 habilita D 7 -D 0. • BLAST: salida de última ráfaga, indica que el ciclo de ráfaga de bus está completo en la siguiente señal BRDY.

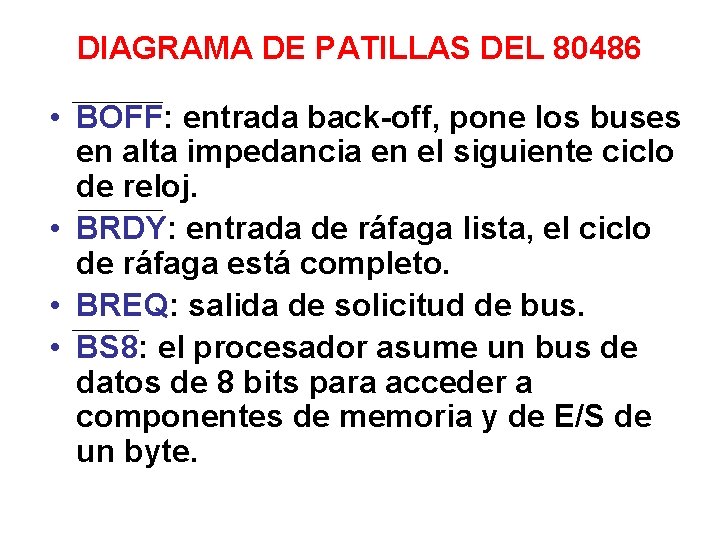

DIAGRAMA DE PATILLAS DEL 80486 • BOFF: entrada back-off, pone los buses en alta impedancia en el siguiente ciclo de reloj. • BRDY: entrada de ráfaga lista, el ciclo de ráfaga está completo. • BREQ: salida de solicitud de bus. • BS 8: el procesador asume un bus de datos de 8 bits para acceder a componentes de memoria y de E/S de un byte.

DIAGRAMA DE PATILLAS DEL 80486 • BS 16: el procesador asume un bus de datos de 16 bits. • CLK: entrada de reloj. • D 31 -D 0: bus de datos • D/C: datos/control, indica si la operación actual es una transferencia de datos o un ciclo de control. • DP 3 -DP 0: entrada/salida de paridad de datos, provee paridad para una operación de escritura.

DIAGRAMA DE PATILLAS DEL 80486 • EADS: entrada pulso dirección externa se utiliza con AHOLD para indicar que una dirección externa se utiliza para realizar un ciclo de invalidación de memoria caché. • FERR: salida de error de punto flotante. • FLUSH: entrada de borrado de caché. • HLDA: salida de reconocimiento de que los buses están en alta impedancia.

DIAGRAMA DE PATILLAS DEL 80486 • HOLD: entrada de solicitud de acción del DMA. • IGNNE: entrada que ignora error numérico y continúa con el proceso. • INTR: solicitud de interrupción. • KEN: entrada de habilitación de caché. • LOCK: salida de bloqueo. • M/IO: define si el bus de direcciones es para memoria o para interfaz de E/S.

DIAGRAMA DE PATILLAS DEL 80486 • NMI: interrupción no enmascarable • PCD: salida de deshabilitación de caché de página. • PCHK: salida de verificación de paridad indicando la detección de un error de paridad. • PLOCK: salida de seudo-bloqueo, indicando que la operación actual requiere de más de un ciclo de bus para su ejecución.

DIAGRAMA DE PATILLAS DEL 80486 • PWT: salida de estructura transparente de página. • RDY: entrada que indica disponibilidad. • RESET: entrada de reinicialización. • W/R: solicitud de lectura/escritura.

PAGINACIÓN Y MEMORIA VIRTUAL La memoria física del 386 tiene una capacidad de 64 GB. En el modo virtual, la unidad de administración de memoria y los descriptores mapean 64 TB en los 4 GB de espacio físico. La memoria física se divide en bloques de tamaño fijo, denominados marcos de página. El tamaño es una potencia de dos, puede variar entre 0. 5 y 8 KB.

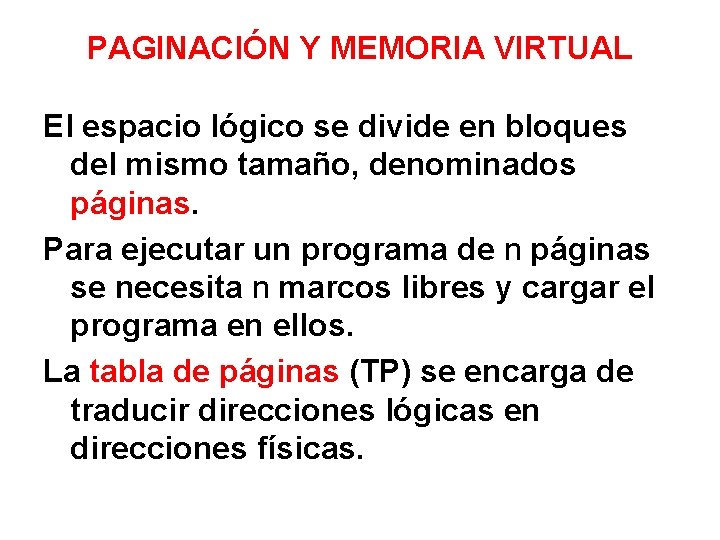

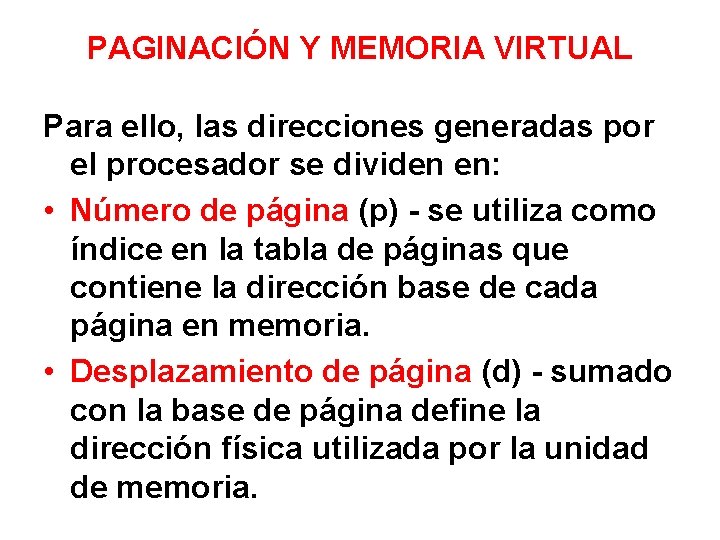

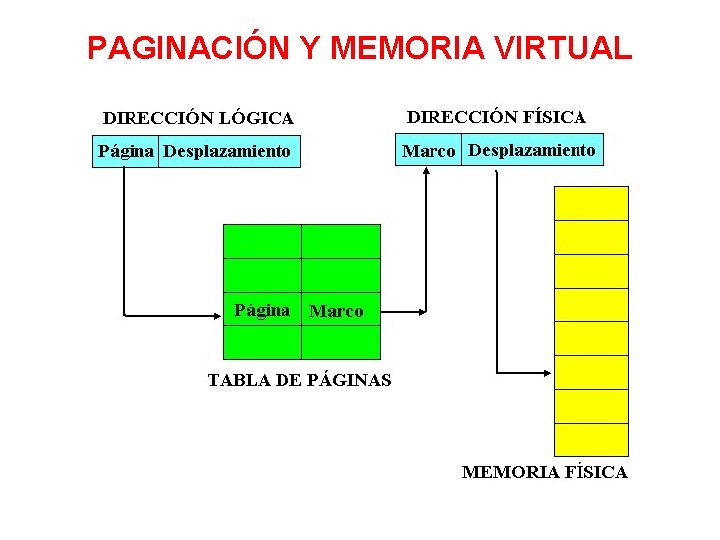

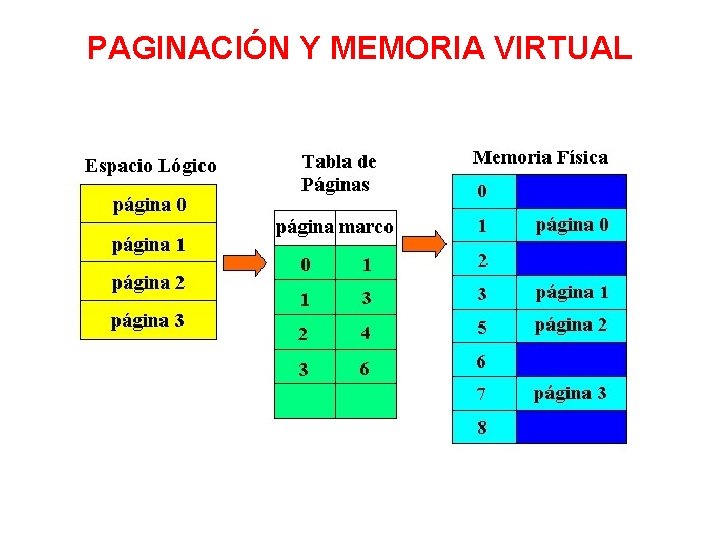

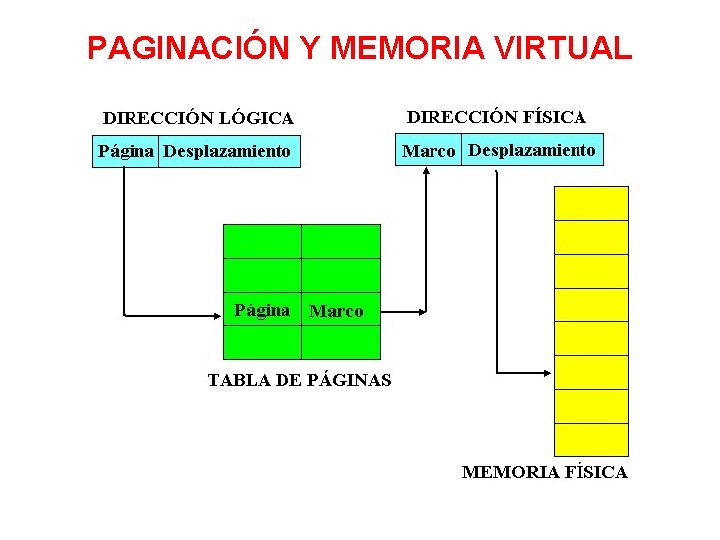

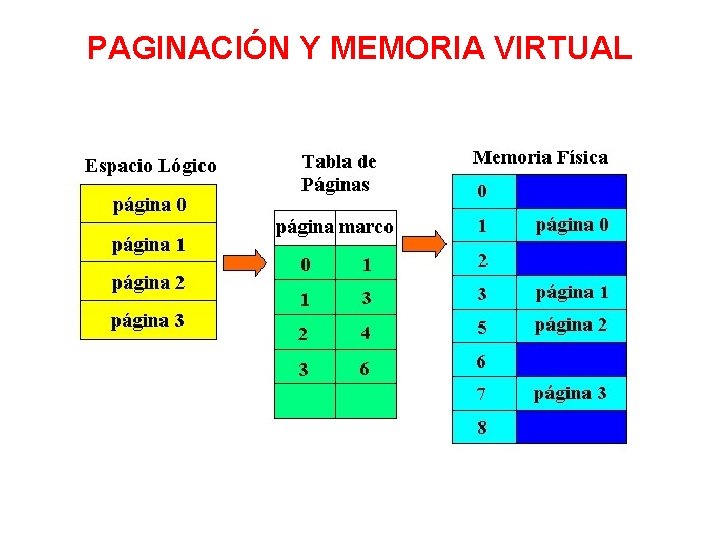

PAGINACIÓN Y MEMORIA VIRTUAL El espacio lógico se divide en bloques del mismo tamaño, denominados páginas. Para ejecutar un programa de n páginas se necesita n marcos libres y cargar el programa en ellos. La tabla de páginas (TP) se encarga de traducir direcciones lógicas en direcciones físicas.

PAGINACIÓN Y MEMORIA VIRTUAL Para ello, las direcciones generadas por el procesador se dividen en: • Número de página (p) - se utiliza como índice en la tabla de páginas que contiene la dirección base de cada página en memoria. • Desplazamiento de página (d) - sumado con la base de página define la dirección física utilizada por la unidad de memoria.

PAGINACIÓN Y MEMORIA VIRTUAL

PAGINACIÓN Y MEMORIA VIRTUAL

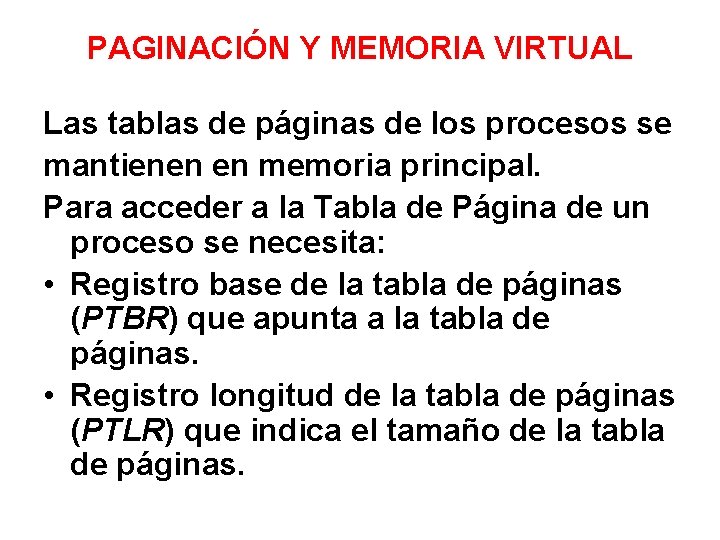

PAGINACIÓN Y MEMORIA VIRTUAL Las tablas de páginas de los procesos se mantienen en memoria principal. Para acceder a la Tabla de Página de un proceso se necesita: • Registro base de la tabla de páginas (PTBR) que apunta a la tabla de páginas. • Registro longitud de la tabla de páginas (PTLR) que indica el tamaño de la tabla de páginas.

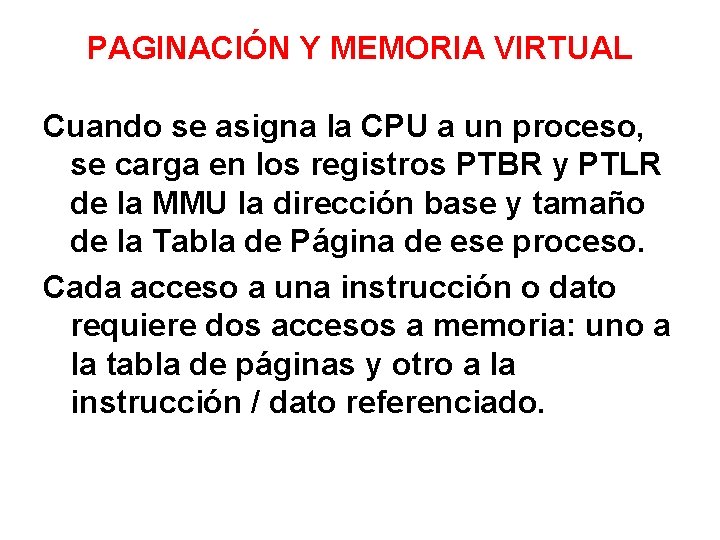

PAGINACIÓN Y MEMORIA VIRTUAL Cuando se asigna la CPU a un proceso, se carga en los registros PTBR y PTLR de la MMU la dirección base y tamaño de la Tabla de Página de ese proceso. Cada acceso a una instrucción o dato requiere dos accesos a memoria: uno a la tabla de páginas y otro a la instrucción / dato referenciado.

PAGINACIÓN Y MEMORIA VIRTUAL El tiempo de los dos accesos se disminuye con el uso de una caché hardware de consulta rápida denominada buffer de reconocimiento de traducciones (TLB -Translation Look -aside Buffer ). Para traducir una dirección: Si existe ya en el TLB, se tiene el marco. Si no, se busca en la Tabla de Página y se ajusta el TLB.

PAGINACIÓN Y MEMORIA VIRTUAL En el manejo de la memoria virtual, cada página de un proceso se introduce en memoria sólo cuando se necesita. Cuando se tiene un programa grande o un conjunto de datos a procesar muy grande, no se carga todo el programa o los datos en memoria sino sólo unas pocas páginas que se trabajarán en el futuro próximo.

PAGINACIÓN Y MEMORIA VIRTUAL Si después se requieren más páginas del programa o más datos, estos se pueden cargar en memoria en los espacios físicos que ya han sido utilizados y no se usan. Esto hace que se utilice un espacio de memoria física pequeño para procesar un gran volumen de información.

UNIDAD DE PUNTO FLOTANTE La arquitectura del 80486 contiene los bloques básicos encontrados en el 80386. Se distingue la potenciación de la Unidad de Ejecución al incluir la Unidad de Punto Flotante que actúa como un microprocesador interno distinto con sus propios registros y con sus propios buses internos, incorpora instrucciones nuevas que trabajan con números reales.

UNIDAD DE PUNTO FLOTANTE La FPU es capaz de sumar, restar, multiplicar, dividir, obtener raíz cuadrada, calcular la tangente, el arco tangente y logaritmos. Los tipos de datos incluyen números enteros de 16, 32 y 64 bits con signo; datos BCD de 18 dígitos, números de punto flotante de 32, 64 y 80 bits. Las instrucciones del FPU son instrucciones de ESC.

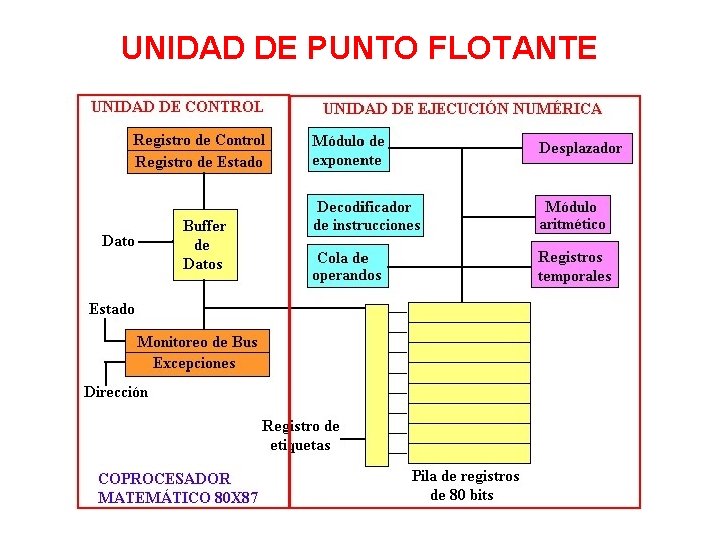

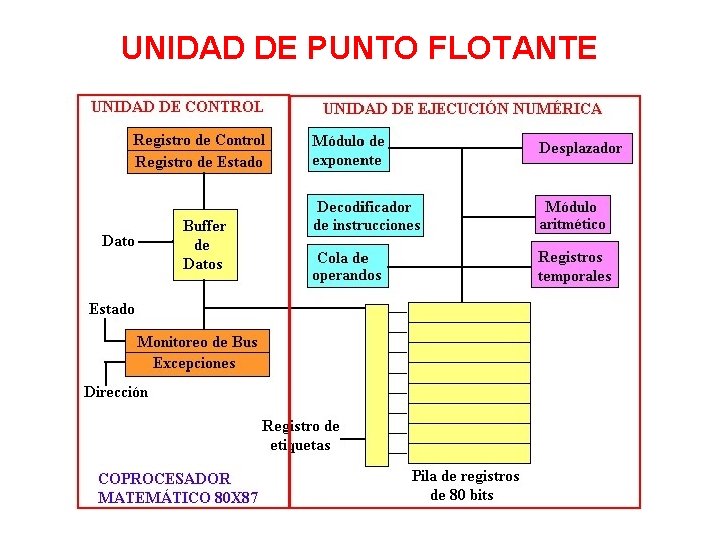

COPROCESADOR MATEMÁTICO El microprocesador y la FPU pueden ejecutar sus respectivas instrucciones en forma concurrente. En el siguiente diagrama se ilustra la estructura del FPU compuesta de una Unidad de Control y una Unidad de Ejecución Numérica. La Unidad de Control establece una interfaz entre el FPU y el bus de datos del sistema.

UNIDAD DE PUNTO FLOTANTE

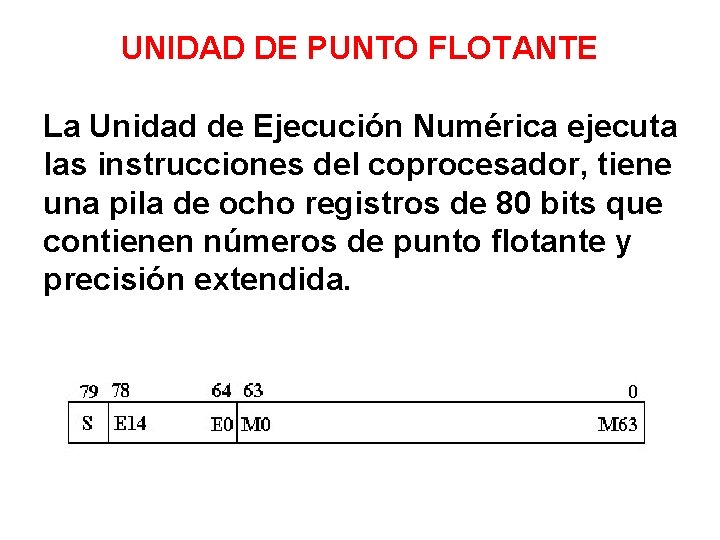

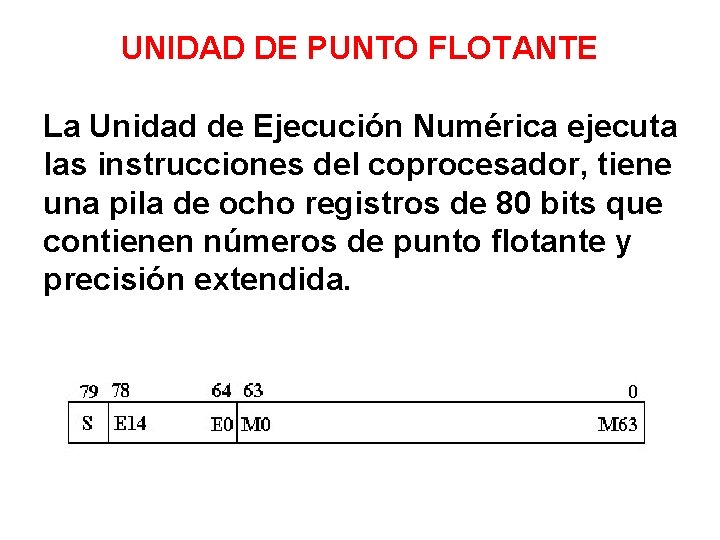

UNIDAD DE PUNTO FLOTANTE La Unidad de Ejecución Numérica ejecuta las instrucciones del coprocesador, tiene una pila de ocho registros de 80 bits que contienen números de punto flotante y precisión extendida.

UNIDAD DE PUNTO FLOTANTE En el coprocesador los datos se almacenan siempre como un número de punto flotante y precisión extendida de 80 bits. Existen cuatro instrucciones de transferencia de datos de punto flotante: FLD (carga real), FST (almacena real), FSTP (almacena real y extrae de la pila), FXCH (intercambia).

UNIDAD DE PUNTO FLOTANTE Para la transferencia de datos de números enteros se cuenta con: FILD (cargar número entero), FIST (almacena número entero), FISTP (almacena número entero y extrae de la pila). Para transferencia de datos BCD se tiene: FBLD (carga en la pila un dato BCD de la memoria), FBSTP (almacena al tope de la pila y realiza una extracción de la pila).

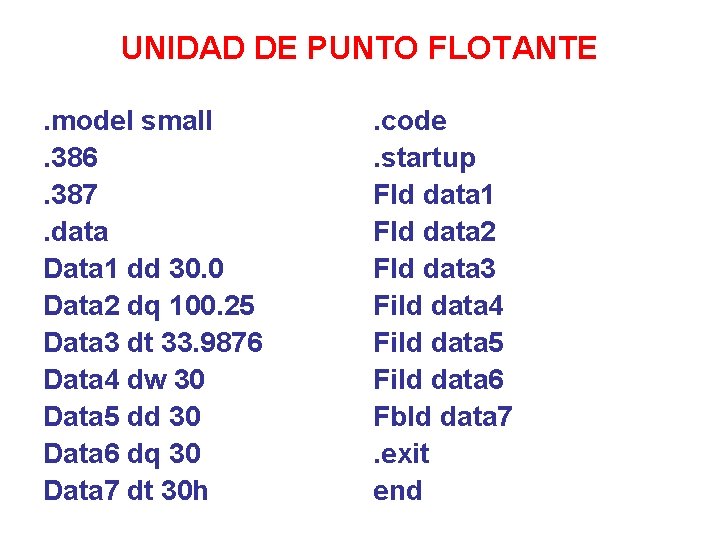

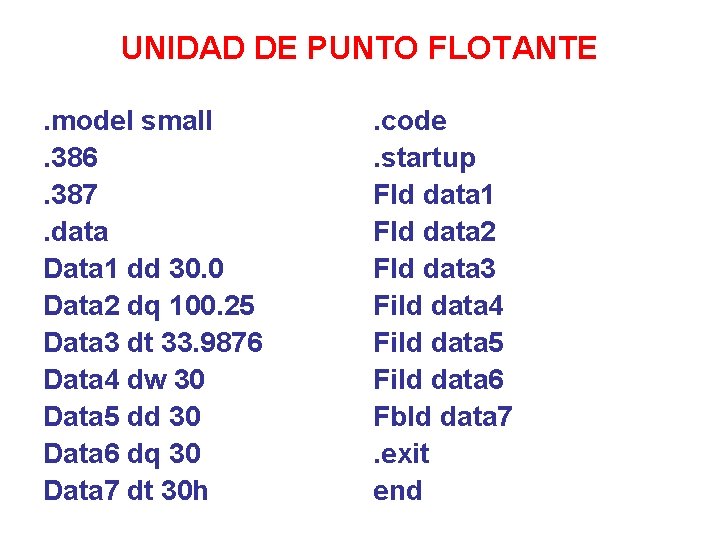

UNIDAD DE PUNTO FLOTANTE. model small. 386. 387. data Data 1 dd 30. 0 Data 2 dq 100. 25 Data 3 dt 33. 9876 Data 4 dw 30 Data 5 dd 30 Data 6 dq 30 Data 7 dt 30 h . code. startup Fld data 1 Fld data 2 Fld data 3 Fild data 4 Fild data 5 Fild data 6 Fbld data 7. exit end

UNIDAD DE PUNTO FLOTANTE Las instrucciones aritméticas recurre a cuatro modos de direccionamiento: • Pila: FADD (el tope de la pila es la fuente ST(0), el siguiente tope de la pila es el destino ST(1)) • Registro: FADD ST, ST(2) • Extracción de Registro: FADDP ST(3), ST • Memoria: FADD data 2 (suma data al tope de la pila)

UNIDAD DE PUNTO FLOTANTE Instrucciones aritméticas: FADD, FSUB, FMUL, FDIV. FSQRT (raíz cuadrada), FSCALE (escala un número), FPREM (encuentra residuo parcial), FRNDINT (redondea a entero), FXTRACT (extrae exponente y significando), FABS (encuentra valor absoluto), FCHG (cambia signo). FCOM (comparación de punto flotante).

UNIDAD DE PUNTO FLOTANTE FCOMP (comparación de punto flotante con extracción de pila), FICOM (comparación de enteros), FSTS (verificación contra cero), FXAM (examina y modifica signo). FPTAN (tangente parcial), FPATAN (arco tangente parcial), FSIN (seno), FCOS (coseno), F 2 XM 1 (2 x-1), FYL 2 X (Ylog 2 X).

UNIDAD DE PUNTO FLOTANTE El coprocesador tiene instrucciones de control para inicialización FINIT, FSTSW (almacena registro de control en el operando de memoria), FSTSW AX (copia contenido del registro de control al registro AX), FSAVE (escribe el estado completo de la máquina en la memoria, FRSTOR (restaura el estado de la máquina desde la memoria), FNOP, FWAIT.

MEMORIA CACHÉ El 80486 posee una memoria caché interna de 8 KB que acelera la ejecución de instrucciones y la adquisición de datos. El sistema de memoria caché almacena los datos y también las instrucciones utilizados por un programa. La caché está organizada como una memoria asociativa por conjunto de cuatro vías donde cada línea contiene 16 bytes.

MEMORIA CACHÉ Gran parte de la porción activa de un programa se encuentra completamente en la memoria caché. Esto ocasiona que muchas de las instrucciones comúnmente utilizadas en un programa se ejecuten a una velocidad de un ciclo de reloj. El registro de control cero (CR 0) se emplea para controlar la caché con dos bits de control nuevos: CD (deshabilita caché), NW (no escritura de caché).

MEMORIA CACHÉ La caché se llena con ciclos de ráfaga. Al llenar una línea, el 80486 debe adquirir cuatro números de 32 bits desde el sistema de memoria para llenar una línea en la memoria caché. El ciclo de ráfaga es un ciclo en el cuatro números de 32 bits se obtienen del sistema de memoria en cinco periodos de reloj. Si la frecuencia de reloj es de 33 MHz, se llena una línea en 167 ns.

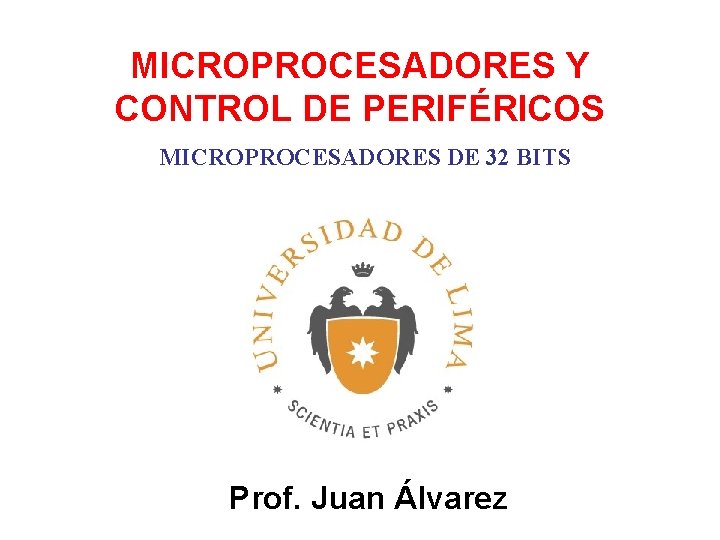

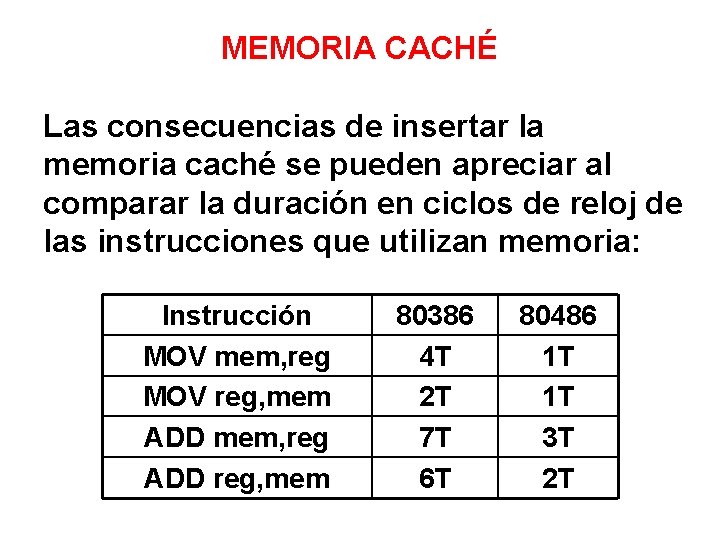

MEMORIA CACHÉ Las consecuencias de insertar la memoria caché se pueden apreciar al comparar la duración en ciclos de reloj de las instrucciones que utilizan memoria: Instrucción MOV mem, reg MOV reg, mem ADD mem, reg ADD reg, mem 80386 4 T 2 T 7 T 6 T 80486 1 T 1 T 3 T 2 T

PROBLEMAS PROPUESTOS 1. Responder a las siguientes preguntas: a) ¿Indicar cuatro diferencias arquitectónicas que se pueden observar entre el 80386 y el 80486? b) ¿Porqué y en qué casos la memoria caché acelera la ejecución de instrucciones? c) ¿Porqué la paginación es importante para el proceso de memoria virtual? d) Explique como puede usted utilizar las flechas del teclado para tomar decisiones en la bifurcación de programas. e) ¿Cómo ayuda la paginación a un uso más económico de la memoria?