ME 44476405 Interrupts and Resets Suzanne Price Scott

- Slides: 30

ME 4447/6405 Interrupts and Resets Suzanne Price Scott Gilliliand Greg Graf

Overview n n n n Polling Interrupts Vector Tables Highest Priority Interrupt Register ADC Example with Interrupts Resets Standby Modes Suzanne Price

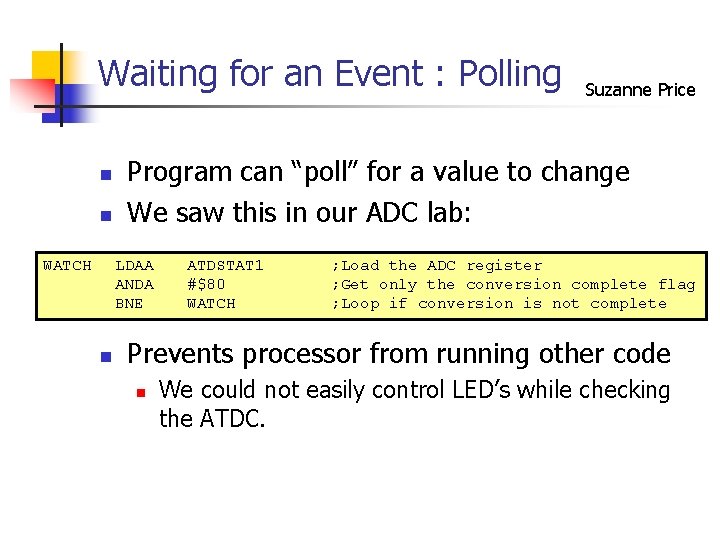

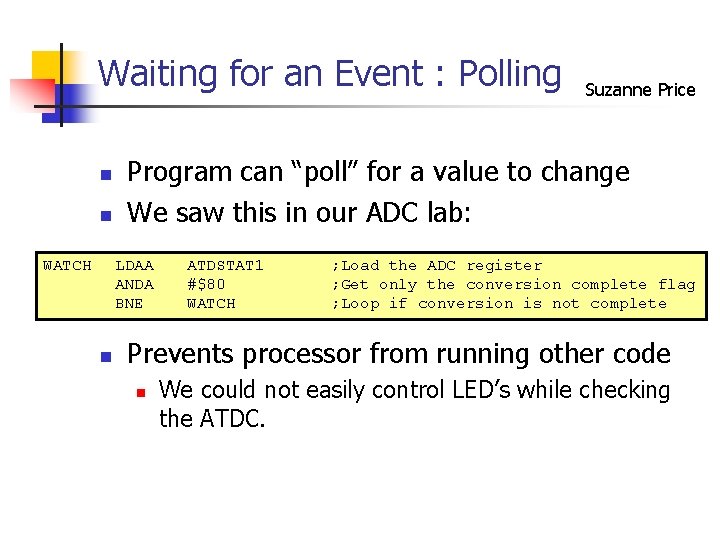

Waiting for an Event : Polling n n WATCH Program can “poll” for a value to change We saw this in our ADC lab: LDAA ANDA BNE n Suzanne Price ATDSTAT 1 #$80 WATCH ; Load the ADC register ; Get only the conversion complete flag ; Loop if conversion is not complete Prevents processor from running other code n We could not easily control LED’s while checking the ATDC.

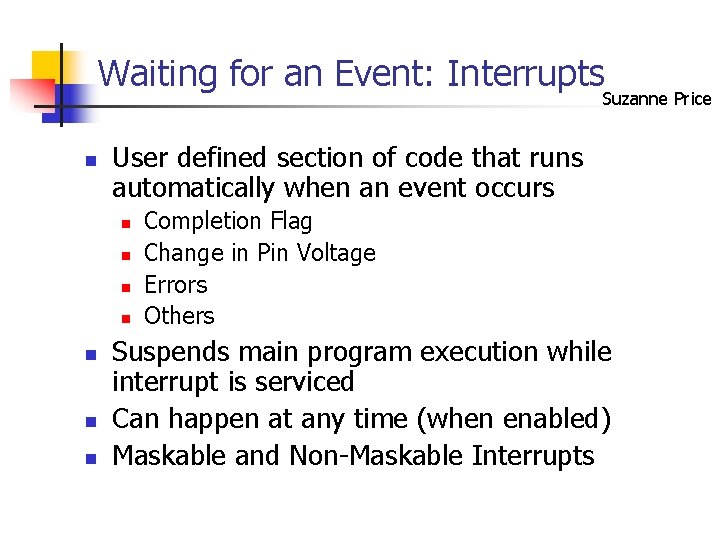

Waiting for an Event: Interrupts Suzanne Price n User defined section of code that runs automatically when an event occurs n n n n Completion Flag Change in Pin Voltage Errors Others Suspends main program execution while interrupt is serviced Can happen at any time (when enabled) Maskable and Non-Maskable Interrupts

How Interrupts Work: Review n n n Event occurs Current instruction finishes If interrupts are enabled: n n n Suzanne Price Push registers to stack Set interrupt bit(s) in CCR Run Interrupt Service Routine (ISR) until RTI Pull register values back from stack Main program continues to run

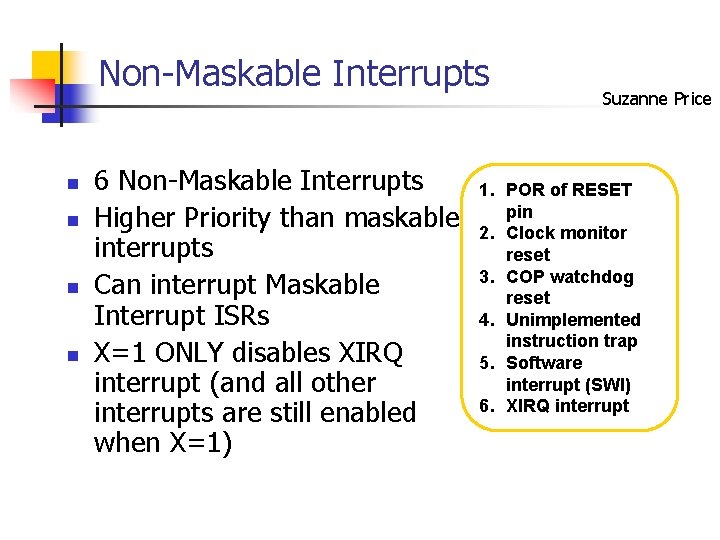

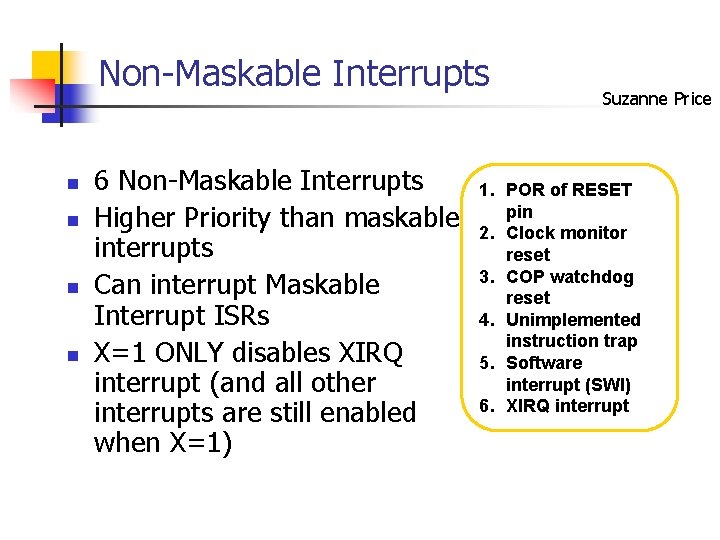

Non-Maskable Interrupts n n 6 Non-Maskable Interrupts Higher Priority than maskable interrupts Can interrupt Maskable Interrupt ISRs X=1 ONLY disables XIRQ interrupt (and all other interrupts are still enabled when X=1) Suzanne Price 1. POR of RESET pin 2. Clock monitor reset 3. COP watchdog reset 4. Unimplemented instruction trap 5. Software interrupt (SWI) 6. XIRQ interrupt

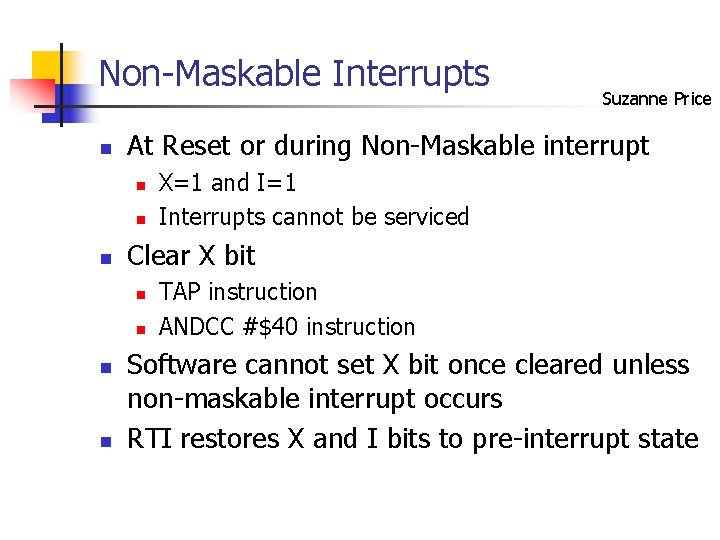

Non-Maskable Interrupts n At Reset or during Non-Maskable interrupt n n n X=1 and I=1 Interrupts cannot be serviced Clear X bit n n Suzanne Price TAP instruction ANDCC #$40 instruction Software cannot set X bit once cleared unless non-maskable interrupt occurs RTI restores X and I bits to pre-interrupt state

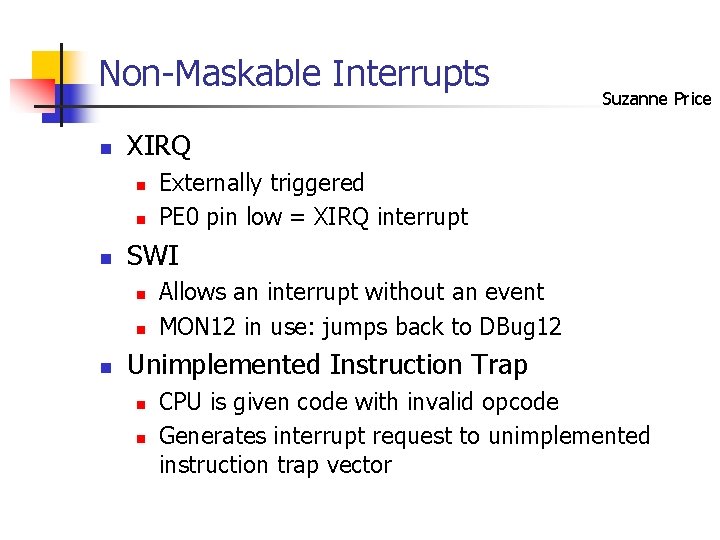

Non-Maskable Interrupts n XIRQ n n n Externally triggered PE 0 pin low = XIRQ interrupt SWI n n n Suzanne Price Allows an interrupt without an event MON 12 in use: jumps back to DBug 12 Unimplemented Instruction Trap n n CPU is given code with invalid opcode Generates interrupt request to unimplemented instruction trap vector

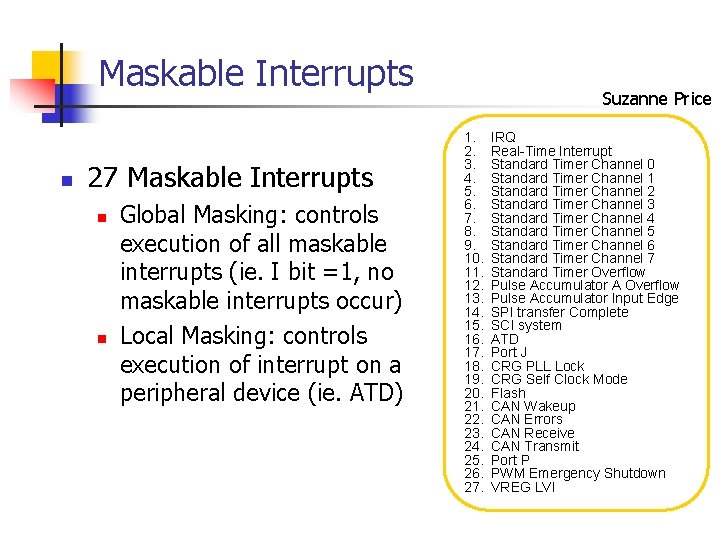

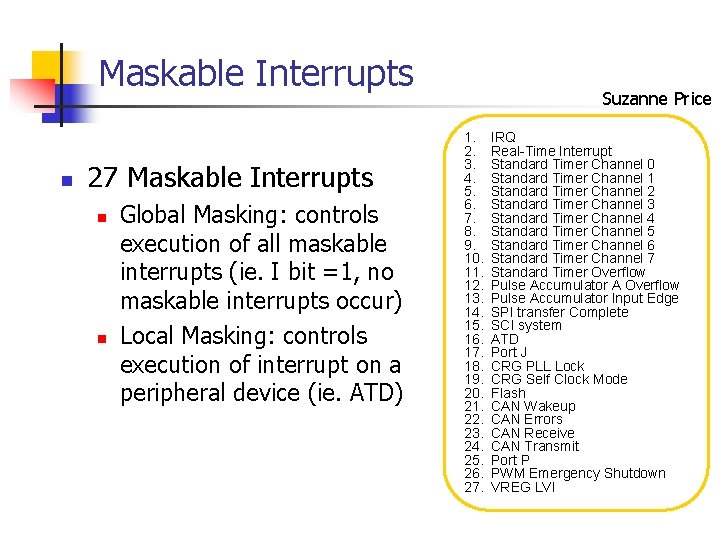

Maskable Interrupts n 27 Maskable Interrupts n n Global Masking: controls execution of all maskable interrupts (ie. I bit =1, no maskable interrupts occur) Local Masking: controls execution of interrupt on a peripheral device (ie. ATD) Suzanne Price 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. 26. 27. IRQ Real-Time Interrupt Standard Timer Channel 0 Standard Timer Channel 1 Standard Timer Channel 2 Standard Timer Channel 3 Standard Timer Channel 4 Standard Timer Channel 5 Standard Timer Channel 6 Standard Timer Channel 7 Standard Timer Overflow Pulse Accumulator A Overflow Pulse Accumulator Input Edge SPI transfer Complete SCI system ATD Port J CRG PLL Lock CRG Self Clock Mode Flash CAN Wakeup CAN Errors CAN Receive CAN Transmit Port P PWM Emergency Shutdown VREG LVI

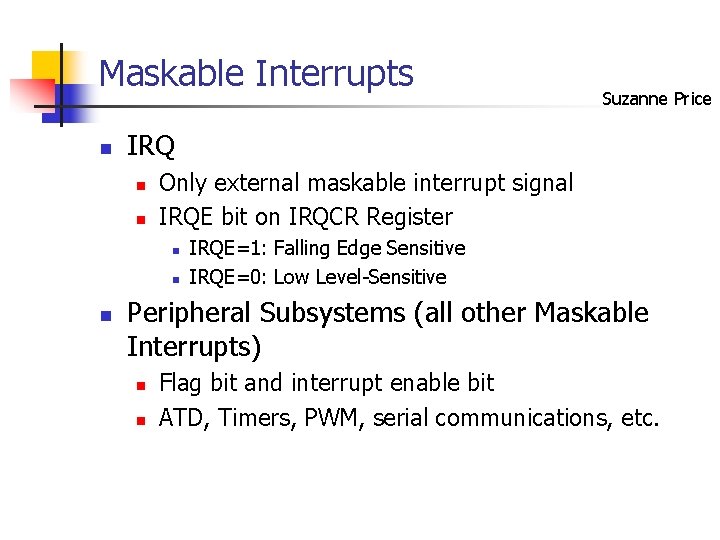

Maskable Interrupts n IRQ n n Only external maskable interrupt signal IRQE bit on IRQCR Register n n n Suzanne Price IRQE=1: Falling Edge Sensitive IRQE=0: Low Level-Sensitive Peripheral Subsystems (all other Maskable Interrupts) n n Flag bit and interrupt enable bit ATD, Timers, PWM, serial communications, etc.

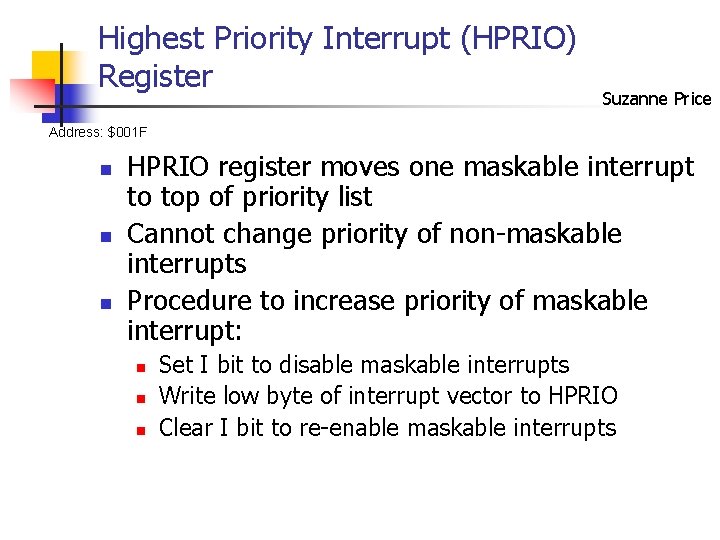

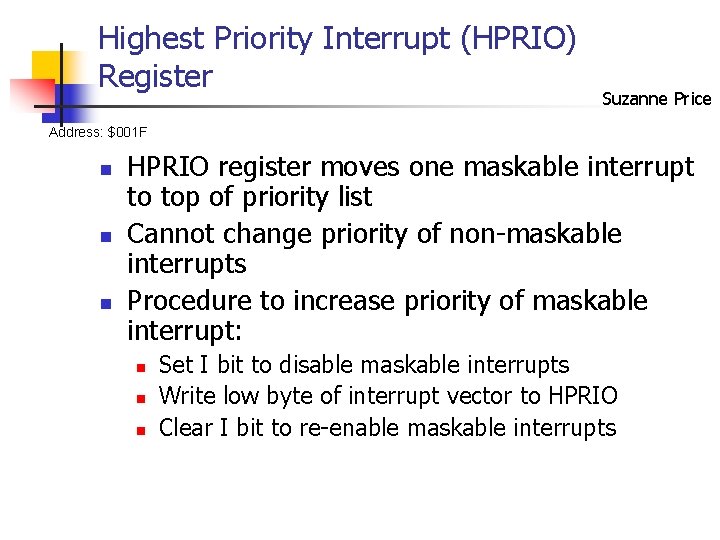

Highest Priority Interrupt (HPRIO) Register Suzanne Price Address: $001 F n n n HPRIO register moves one maskable interrupt to top of priority list Cannot change priority of non-maskable interrupts Procedure to increase priority of maskable interrupt: n n n Set I bit to disable maskable interrupts Write low byte of interrupt vector to HPRIO Clear I bit to re-enable maskable interrupts

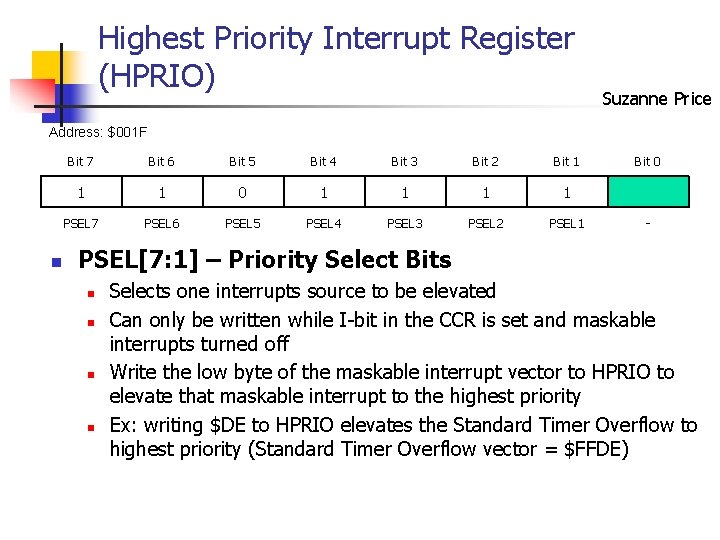

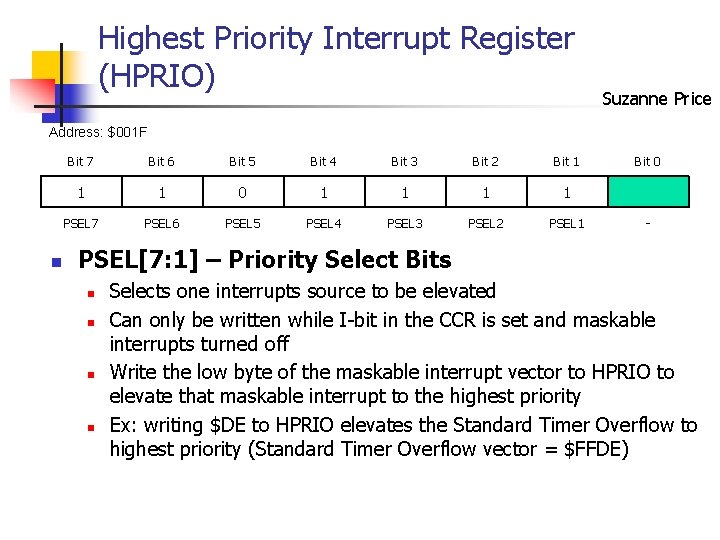

Highest Priority Interrupt Register (HPRIO) Suzanne Price Address: $001 F n Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 1 1 0 1 1 PSEL 7 PSEL 6 PSEL 5 PSEL 4 PSEL 3 PSEL 2 PSEL 1 Bit 0 - PSEL[7: 1] – Priority Select Bits n n Selects one interrupts source to be elevated Can only be written while I-bit in the CCR is set and maskable interrupts turned off Write the low byte of the maskable interrupt vector to HPRIO to elevate that maskable interrupt to the highest priority Ex: writing $DE to HPRIO elevates the Standard Timer Overflow to highest priority (Standard Timer Overflow vector = $FFDE)

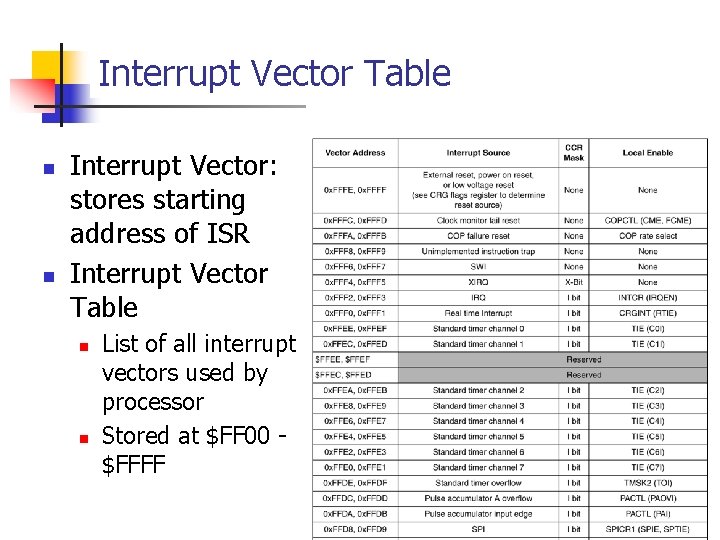

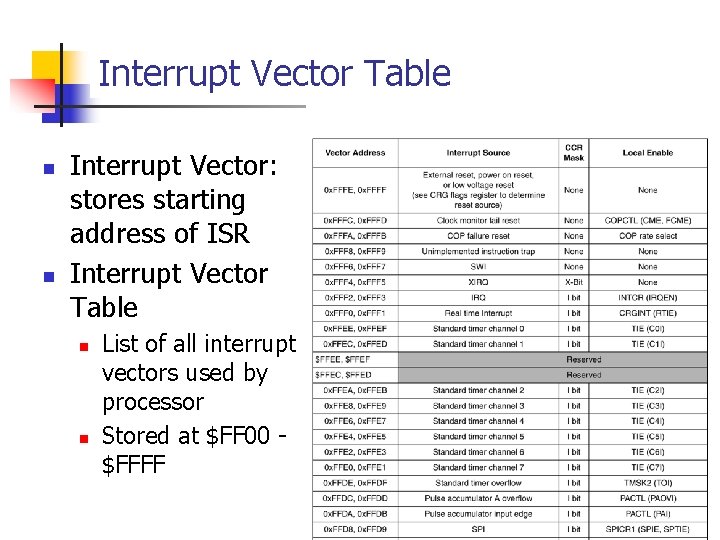

Interrupt Vector Table n n Interrupt Vector: stores starting address of ISR Interrupt Vector Table n n List of all interrupt vectors used by processor Stored at $FF 00 $FFFF

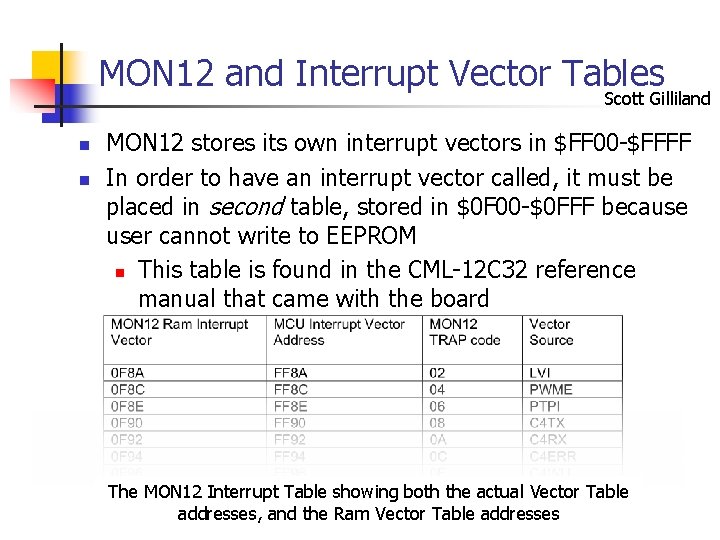

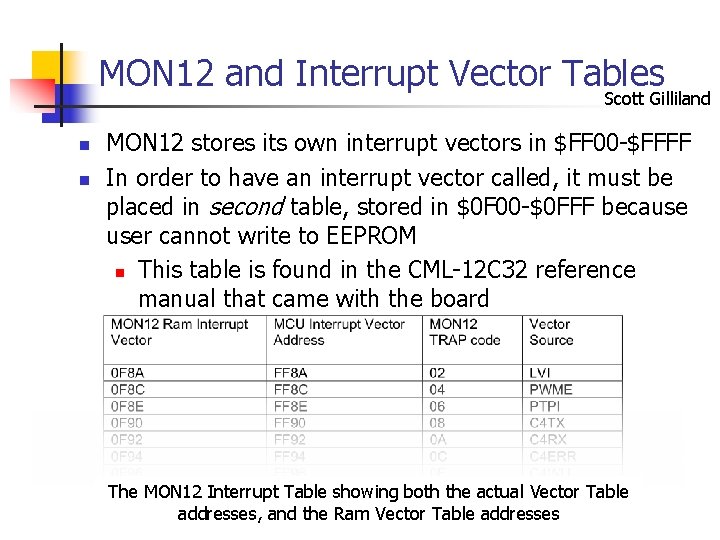

MON 12 and Interrupt Vector Tables Scott Gilliland n n MON 12 stores its own interrupt vectors in $FF 00 -$FFFF In order to have an interrupt vector called, it must be placed in second table, stored in $0 F 00 -$0 FFF because user cannot write to EEPROM n This table is found in the CML-12 C 32 reference manual that came with the board The MON 12 Interrupt Table showing both the actual Vector Table addresses, and the Ram Vector Table addresses

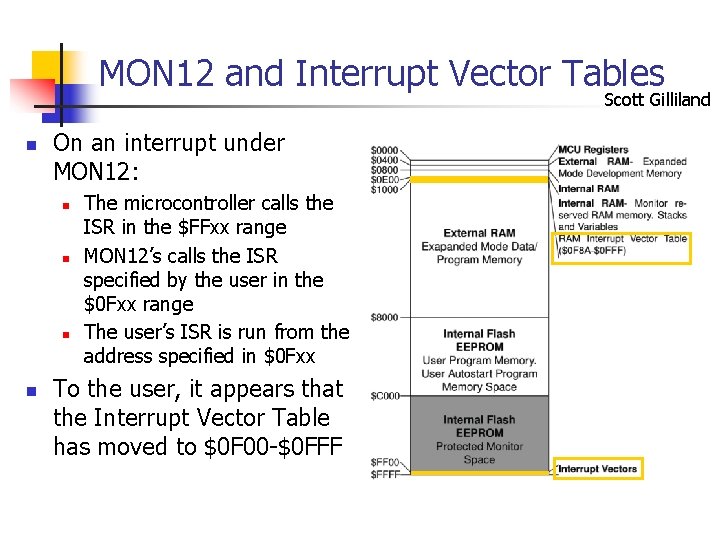

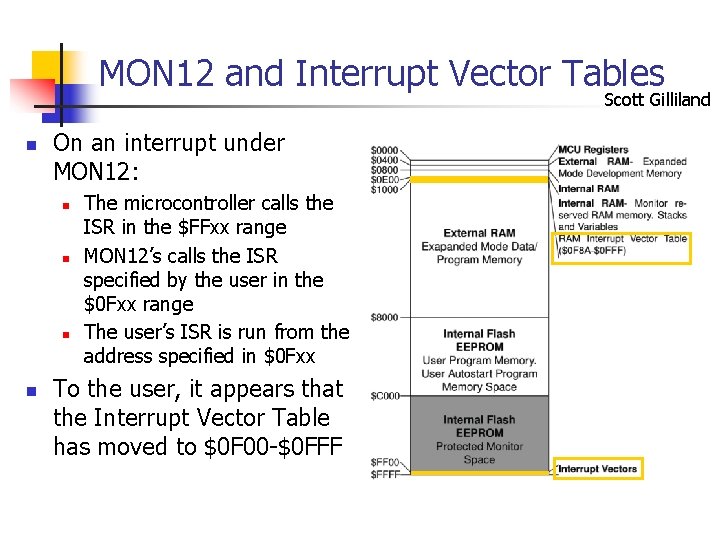

MON 12 and Interrupt Vector Tables Scott Gilliland n On an interrupt under MON 12: n n The microcontroller calls the ISR in the $FFxx range MON 12’s calls the ISR specified by the user in the $0 Fxx range The user’s ISR is run from the address specified in $0 Fxx To the user, it appears that the Interrupt Vector Table has moved to $0 F 00 -$0 FFF

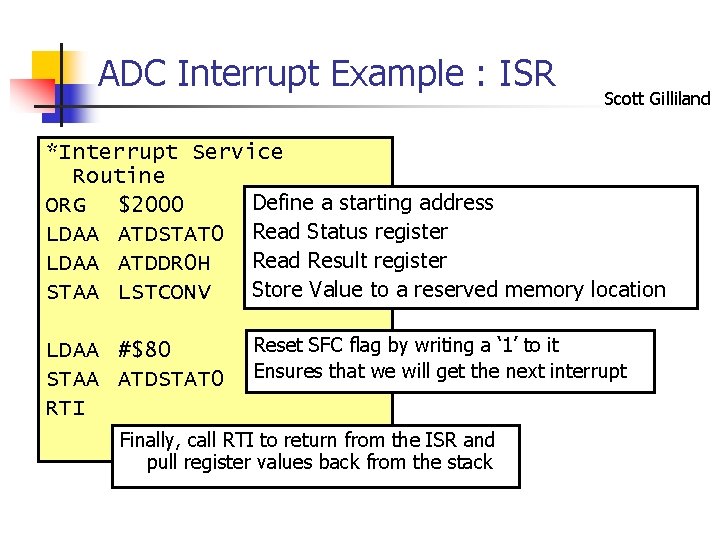

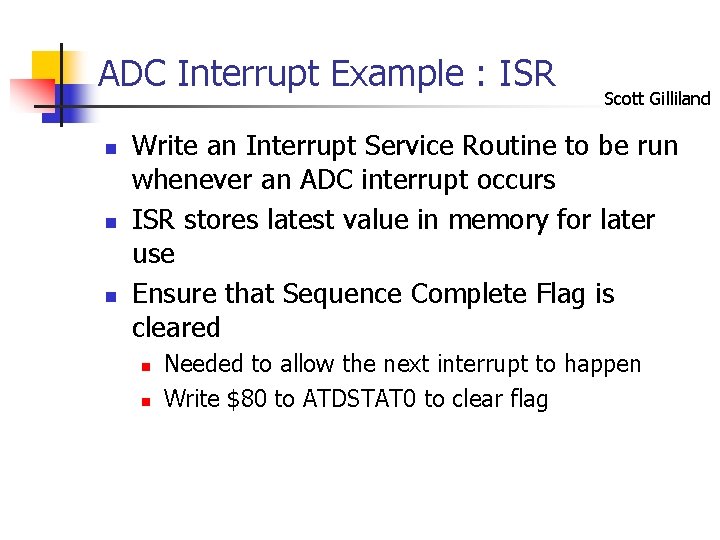

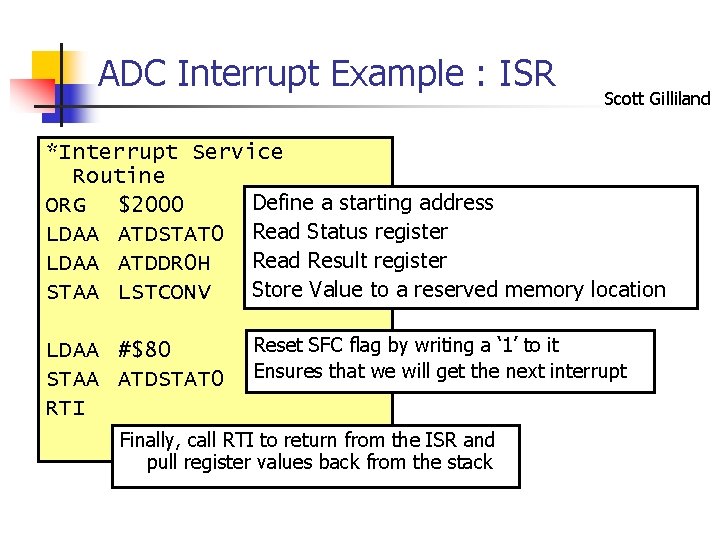

ADC Interrupt Example : ISR n n n Scott Gilliland Write an Interrupt Service Routine to be run whenever an ADC interrupt occurs ISR stores latest value in memory for later use Ensure that Sequence Complete Flag is cleared n n Needed to allow the next interrupt to happen Write $80 to ATDSTAT 0 to clear flag

ADC Interrupt Example : ISR Scott Gilliland *Interrupt Service Routine Define a starting address ORG $2000 LDAA ATDSTAT 0 Read Status register Read Result register LDAA ATDDR 0 H Store Value to a reserved memory location STAA LSTCONV LDAA #$80 STAA ATDSTAT 0 RTI Reset SFC flag by writing a ‘ 1’ to it Ensures that we will get the next interrupt Finally, call RTI to return from the ISR and pull register values back from the stack

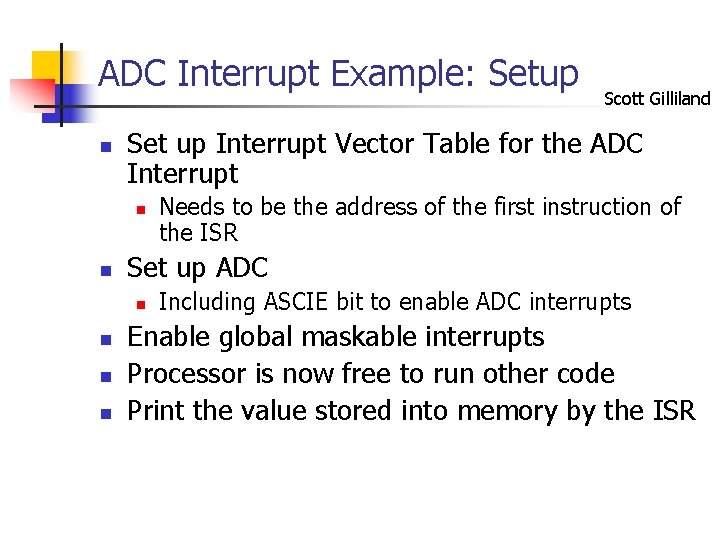

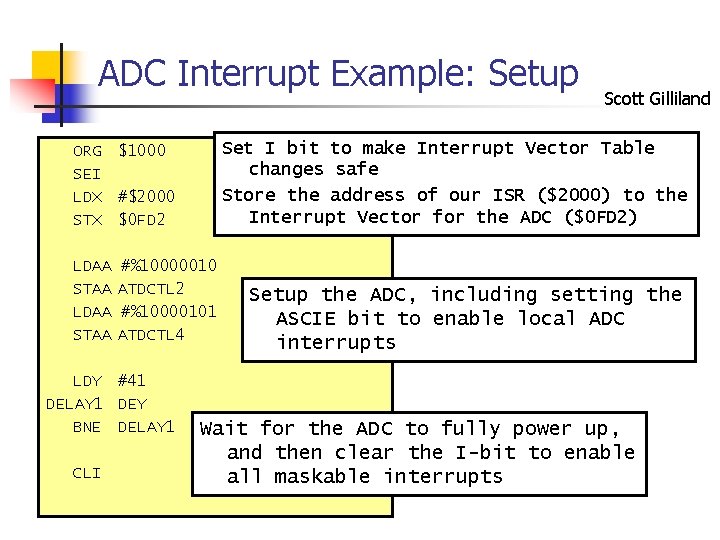

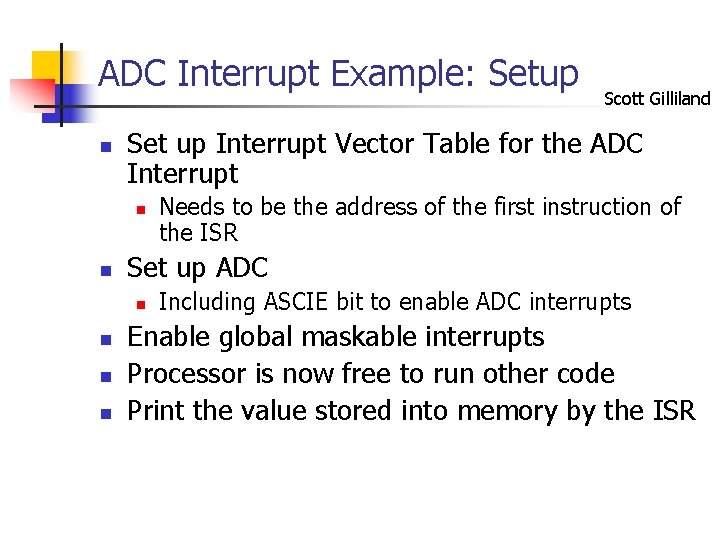

ADC Interrupt Example: Setup n Set up Interrupt Vector Table for the ADC Interrupt n n Needs to be the address of the first instruction of the ISR Set up ADC n n Scott Gilliland Including ASCIE bit to enable ADC interrupts Enable global maskable interrupts Processor is now free to run other code Print the value stored into memory by the ISR

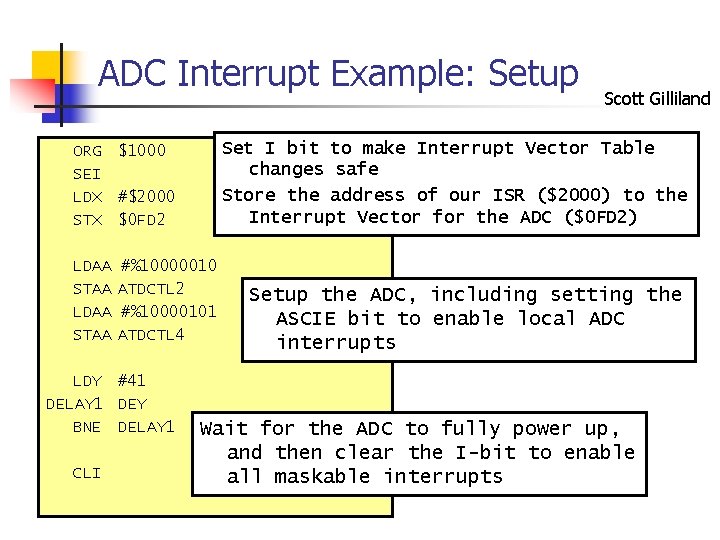

ADC Interrupt Example: Setup Set I bit to make Interrupt Vector Table changes safe Store the address of our ISR ($2000) to the Interrupt Vector for the ADC ($0 FD 2) ORG SEI LDX STX $1000 LDAA STAA #%10000010 ATDCTL 2 #%10000101 ATDCTL 4 #$2000 $0 FD 2 LDY #41 DELAY 1 DEY BNE DELAY 1 CLI Scott Gilliland Setup the ADC, including setting the ASCIE bit to enable local ADC interrupts Wait for the ADC to fully power up, and then clear the I-bit to enable all maskable interrupts

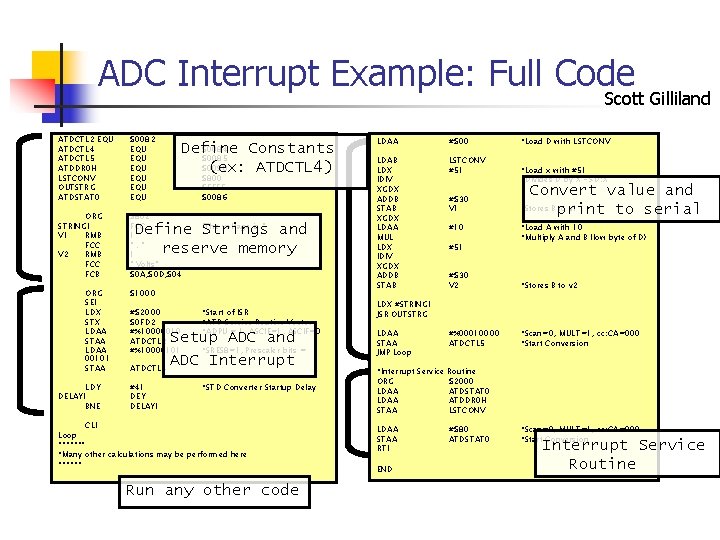

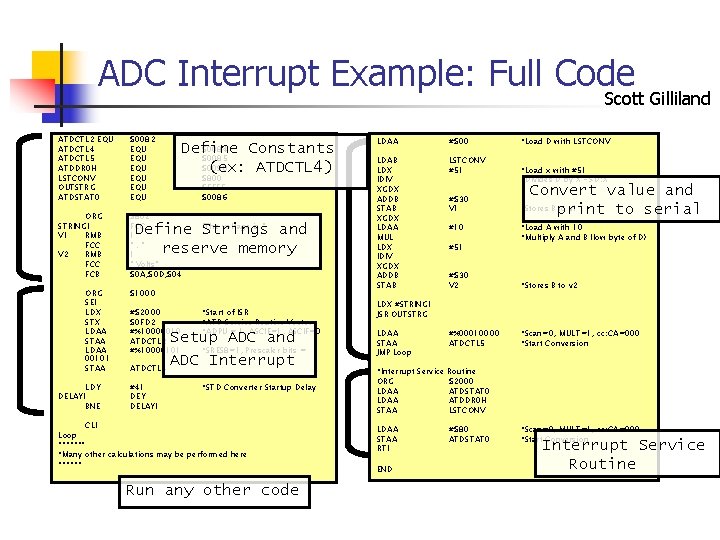

ADC Interrupt Example: Full Code Scott Gilliland ATDCTL 2 EQU ATDCTL 4 ATDCTL 5 ATDDR 0 H LSTCONV OUTSTRG ATDSTAT 0 $0082 EQU EQU EQU ORG STRING 1 V 1 RMB FCC V 2 RMB FCC FCB $802 FCC 1 ". " 1 " Volts" $0 A, $0 D, $04 ORG SEI LDX STX LDAA STAA LDAA 00101 STAA LDY DELAY 1 BNE $0084 Define Constants $0085 $0090 (ex: ATDCTL 4) $800 $FF 5 E $0086 "The voltage is " Define Strings and reserve memory $1000 #$2000 $0 FD 2 #%10000010 ATDCTL 2 #%10000101 *Start of ISR *ATD Service Routine Vector *ADPU = 1, ASCIE=1, ASCIF=0 Setup ADC and *SRES 8=1, Prescaler bits = ADC Interrupt ATDCTL 4 #41 DEY DELAY 1 *STD Converter Startup Delay CLI Loop ******* *Many other calculations may be performed here ****** Run any other code LDAA #$00 LDAB LDX IDIV XGDX ADDB STAB XGDX LDAA MUL LDX IDIV XGDX ADDB STAB LSTCONV #51 #$30 V 1 #10 #51 *Load D with LSTCONV *Load x with #51 *Divides D by X ->D: X Convert value and *Stores B print to v 1 to serial *Load A with 10 *Multiply A and B (low byte of D) #$30 V 2 *Stores B to v 2 #%00010000 ATDCTL 5 *Scan=0, MULT=1, cc: CA=000 *Start Conversion LDX #STRING 1 JSR OUTSTRG LDAA STAA JMP Loop *Interrupt Service Routine ORG $2000 LDAA ATDSTAT 0 LDAA ATDDR 0 H STAA LSTCONV LDAA STAA RTI END #$80 ATDSTAT 0 *Scan=0, MULT=1, cc: CA=000 *Start Conversion Interrupt Service Routine

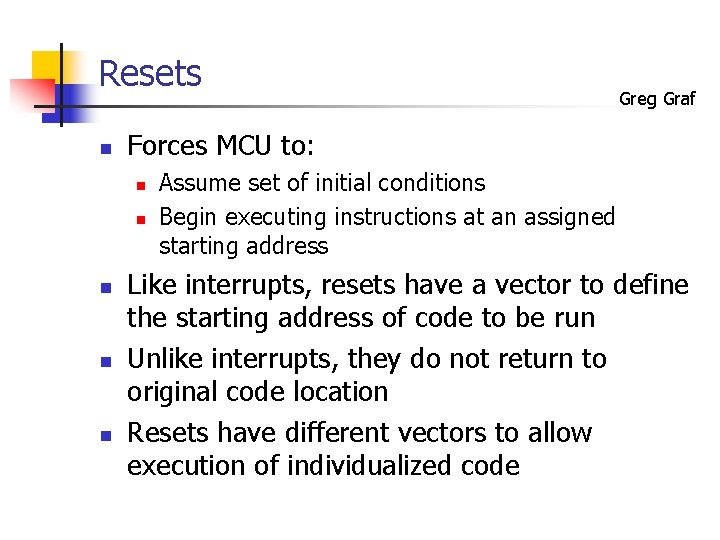

Resets n Forces MCU to: n n n Greg Graf Assume set of initial conditions Begin executing instructions at an assigned starting address Like interrupts, resets have a vector to define the starting address of code to be run Unlike interrupts, they do not return to original code location Resets have different vectors to allow execution of individualized code

Resets: Process Flow Greg Graf When a reset is triggered: n The address from the vector is loaded into the program counter n S, X, and I bits are set in the CCR n MCU hardware is initialized to reset state n Check for any interrupts that have occurred

Resets: POR, External, Low Power Greg Graf n Power on Reset (POR) n n n External Reset (RESET) n n n Triggered when Vdd is applied Timing circuit is initialized, and allowed to settle for 4064 cycles Same vector as POR Reset pin must be pulled low for a total of 6 cycles Low Power Reset n n Same vector as POR Triggered when Vdd drops below acceptable limit

Resets: COP, Clock Monitor n Computer operating Properly (COP) Reset n n Greg Graf Protects against software failures (infinite loops, etc) When enabled (NOCOP bit in CONFIG register), resets if free-running watchdog timer rolls over $FFFF Timer rate is set in the OPTION register. System Eclock is divided by 215 and further scaled by 1, 2, or 4 Clock Monitor Reset n n n Protects against clock failure Set by CME control bit If enabled, system resets if no clock edges are detected within a set period.

Standby Modes n n Suspends CPU operation until reset or interrupt occurs Reduces power consumption CPU registers are stacked to speed up recovery into interrupts Two modes: Wait, Stop Greg Graf

Standby Modes: WAIT (WAI) n n Suspends CPU Processing On-chip crystal oscillator remains active n n Greg Graf Peripherals keep running Wait mode is exited through IRQ, XIRQ, or any internally generated interrupts

Standby Modes: Stop (STOP) n n All clocks and peripherals stopped I/O pin levels remain static Stop is exited through external interrupts, edge-triggered IRQ or RESET pin XIRQ always exits stop mode, but XIRQ interrupts are only executed if X bit is clear n n Greg Graf Otherwise, code continues from STOP command If S-bit in CCR is set, STOP is treated as NOP

References n n ME 4447/6405 Interrupts and Resets Lecture HCS 12 Reference Manuals

Appendix: Full Code $0082 EQU EQU EQU $0084 $0085 $0090 $800 $FF 5 E $0086 ORG FCC RMB $802 "The voltage is " 1 ". " 1 n FCC FCB " Volts" $0 A, $0 D, $04 n ORG $1000 SEI LDX STX #$2000 $0 FD 2 LDAA STAA #%10000010 ATDCTL 2 #%10000101 ATDCTL 4 LDY DEY BNE #41 n n n n ATDCTL 2 EQU ATDCTL 4 ATDCTL 5 ATDDR 0 H LSTCONV OUTSTRG ATDSTAT 0 n n n STRING 1 V 1 n n V 2 n n n *Start of ISR *ATD Service Routine Vector n n n *ADPU = 1, ASCIE=1, ASCIF=0 *SRES 8=1, Prescaler bits = 00101 n n n DELAY 1 n n n Loop *STD Converter Startup Delay DELAY 1 CLI n n ******* *Many other calculations may be performed here n n n n n n n ****** LDAA LDAB LDX IDIV XGDX ADDB STAB XGDX #$00 LSTCONV #51 LDAA MUL LDX IDIV XGDX ADDB STAB #10 LDAA STAA JMP Loop *Interrupt Service Routine ORG LDAA STAA RTI n End n *Load x with #51 *Divides D by X. Stores remainder to D and the result in X #$30 V 1 *Stores B to v 1 *Load A with 10 *Multiply A and B (low byte of Remainder in D) #51 #$30 V 2 *Stores B to v 2 LDX #STRING 1 JSR OUTSTRG n n *Load D with LSTCONV #%00010000 ATDCTL 5 *Scan=0, MULT=1, cc: CA=000 *Start Conversion $2000 ATDSTAT 0 ATDDR 0 H LSTCONV #$80 ATDSTAT 0 *Scan=0, MULT=1, cc: CA=000 *Start Conversion

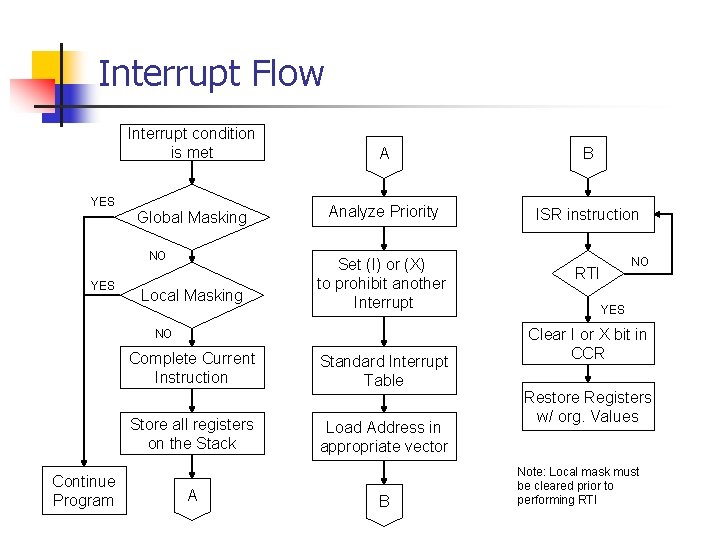

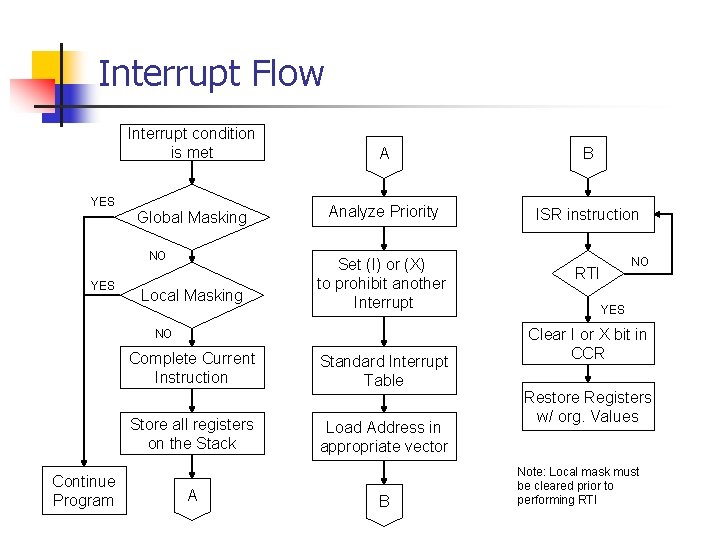

Interrupt Flow Interrupt condition is met A B Global Masking Analyze Priority ISR instruction YES NO YES Local Masking Set (I) or (X) to prohibit another Interrupt NO Complete Current Instruction Store all registers on the Stack Continue Program A Standard Interrupt Table Load Address in appropriate vector B NO RTI YES Clear I or X bit in CCR Restore Registers w/ org. Values Note: Local mask must be cleared prior to performing RTI