Lab 5 FSM and BCD counters Implement the

Lab 5: FSM and BCD counters • Implement the vending machine of lab 2 • A two-digit BCD counter – two BCD counters – can load data in parallel 1 張明峰 交大資 系 lab 5 -1

![Vending Machine module machine (ti, fi, out, state, rst); output out; output [1: 0] Vending Machine module machine (ti, fi, out, state, rst); output out; output [1: 0]](http://slidetodoc.com/presentation_image/4639fea3fd9851163b57ce9d1d96f5a7/image-2.jpg)

Vending Machine module machine (ti, fi, out, state, rst); output out; output [1: 0] state; input ti, fi; input rst; reg [1: 0] state , nextstate; reg t 1, t 2, f 1, f 2; 2 張明峰 交大資 系 lab 5 -2

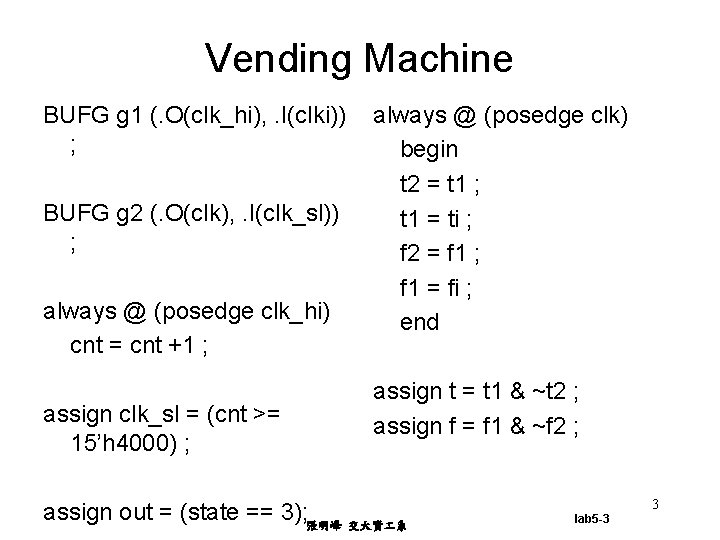

Vending Machine BUFG g 1 (. O(clk_hi), . I(clki)) ; BUFG g 2 (. O(clk), . I(clk_sl)) ; always @ (posedge clk_hi) cnt = cnt +1 ; assign clk_sl = (cnt >= 15’h 4000) ; always @ (posedge clk) begin t 2 = t 1 ; t 1 = ti ; f 2 = f 1 ; f 1 = fi ; end assign t = t 1 & ~t 2 ; assign f = f 1 & ~f 2 ; assign out = (state == 3); 張明峰 交大資 系 3 lab 5 -3

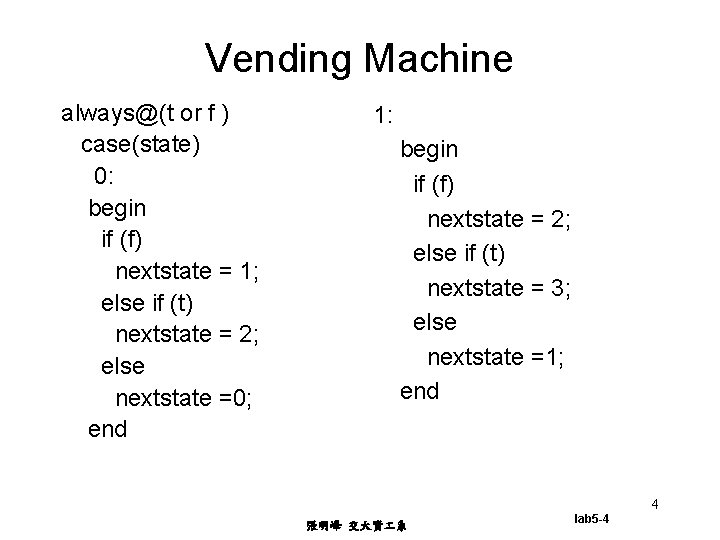

Vending Machine always@(t or f ) case(state) 0: begin if (f) nextstate = 1; else if (t) nextstate = 2; else nextstate =0; end 1: begin if (f) nextstate = 2; else if (t) nextstate = 3; else nextstate =1; end 4 張明峰 交大資 系 lab 5 -4

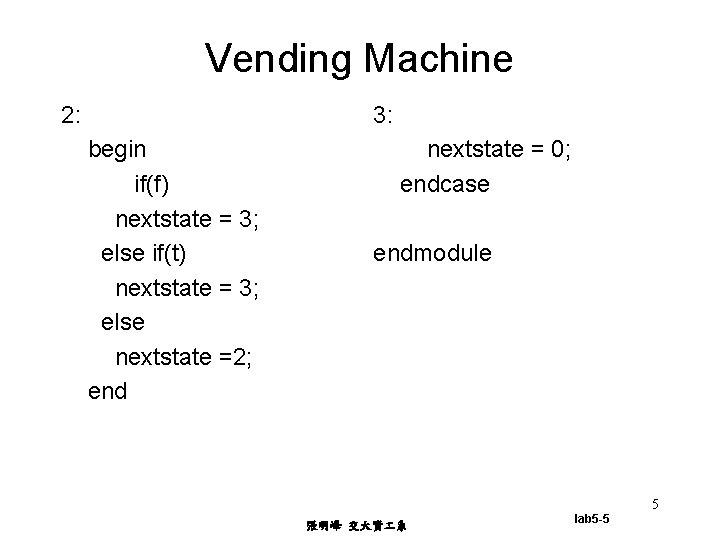

Vending Machine 2: 3: begin if(f) nextstate = 3; else if(t) nextstate = 3; else nextstate =2; end nextstate = 0; endcase endmodule 5 張明峰 交大資 系 lab 5 -5

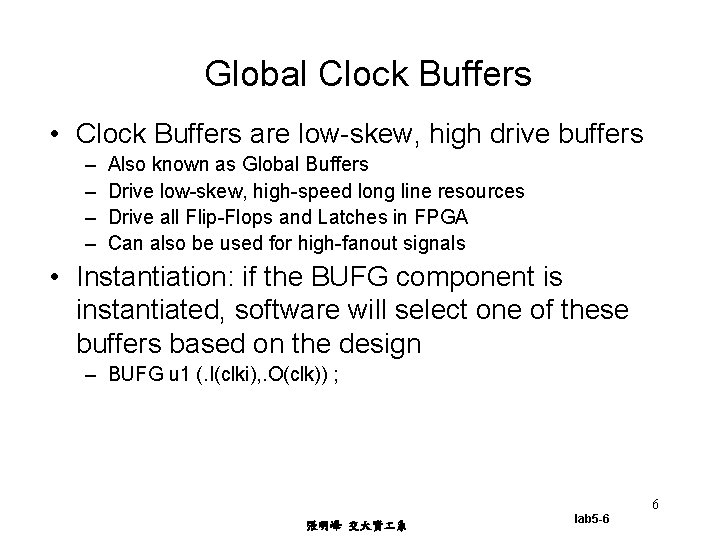

Global Clock Buffers • Clock Buffers are low-skew, high drive buffers – – Also known as Global Buffers Drive low-skew, high-speed long line resources Drive all Flip-Flops and Latches in FPGA Can also be used for high-fanout signals • Instantiation: if the BUFG component is instantiated, software will select one of these buffers based on the design – BUFG u 1 (. I(clki), . O(clk)) ; 6 張明峰 交大資 系 lab 5 -6

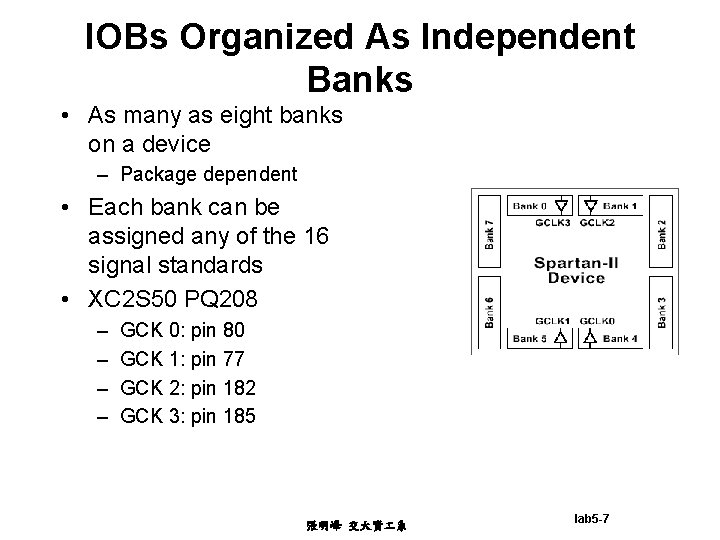

IOBs Organized As Independent Banks • As many as eight banks on a device – Package dependent • Each bank can be assigned any of the 16 signal standards • XC 2 S 50 PQ 208 – – GCK 0: pin 80 GCK 1: pin 77 GCK 2: pin 182 GCK 3: pin 185 張明峰 交大資 系 lab 5 -7

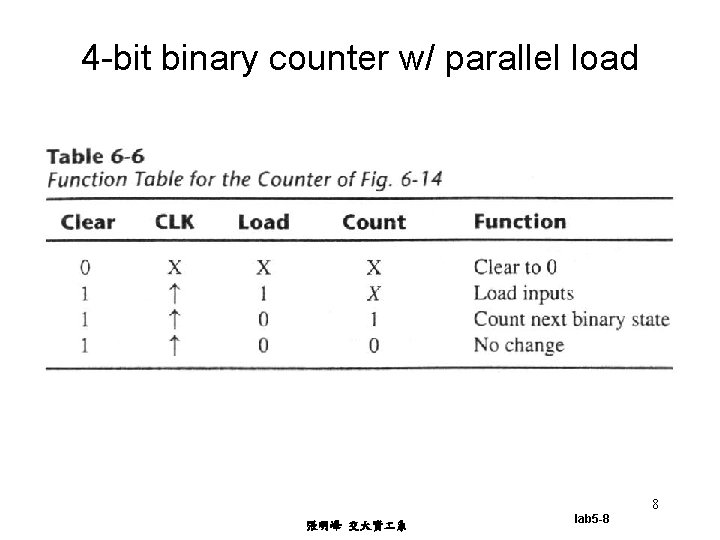

4 -bit binary counter w/ parallel load 8 張明峰 交大資 系 lab 5 -8

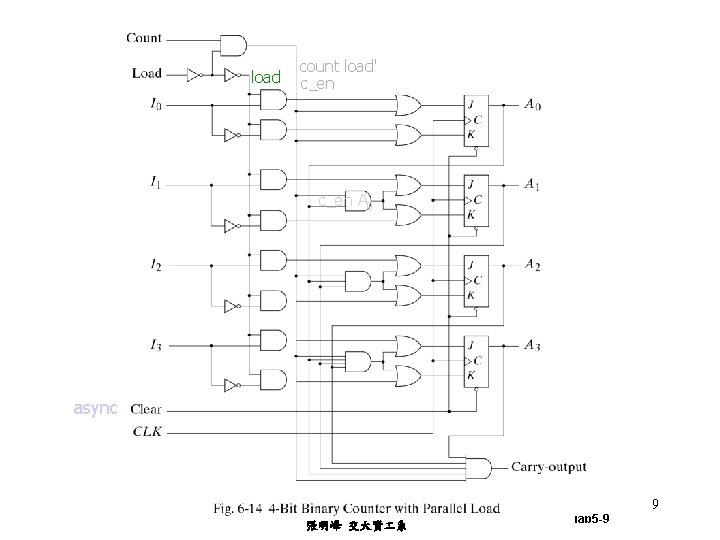

load count load' c_en A 0 async 9 張明峰 交大資 系 lab 5 -9

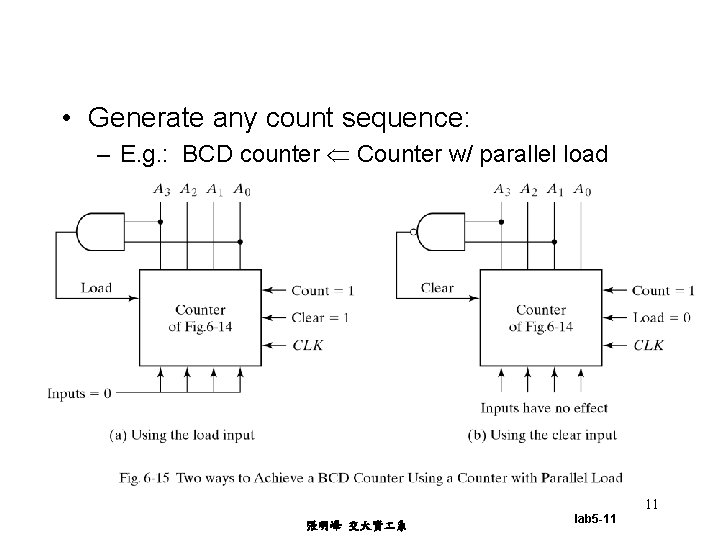

• Generate any count sequence: – E. g. : BCD counter Counter w/ parallel load 11 張明峰 交大資 系 lab 5 -11

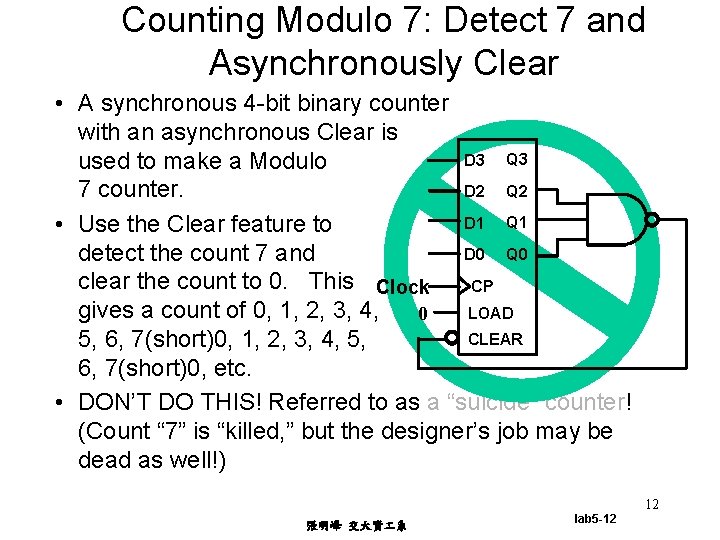

Counting Modulo 7: Detect 7 and Asynchronously Clear • A synchronous 4 -bit binary counter with an asynchronous Clear is D 3 Q 3 used to make a Modulo D 2 Q 2 7 counter. D 1 Q 1 • Use the Clear feature to D 0 Q 0 detect the count 7 and clear the count to 0. This Clock CP gives a count of 0, 1, 2, 3, 4, LOAD 0 CLEAR 5, 6, 7(short)0, 1, 2, 3, 4, 5, 6, 7(short)0, etc. • DON’T DO THIS! Referred to as a “suicide” counter! (Count “ 7” is “killed, ” but the designer’s job may be dead as well!) 12 張明峰 交大資 系 lab 5 -12

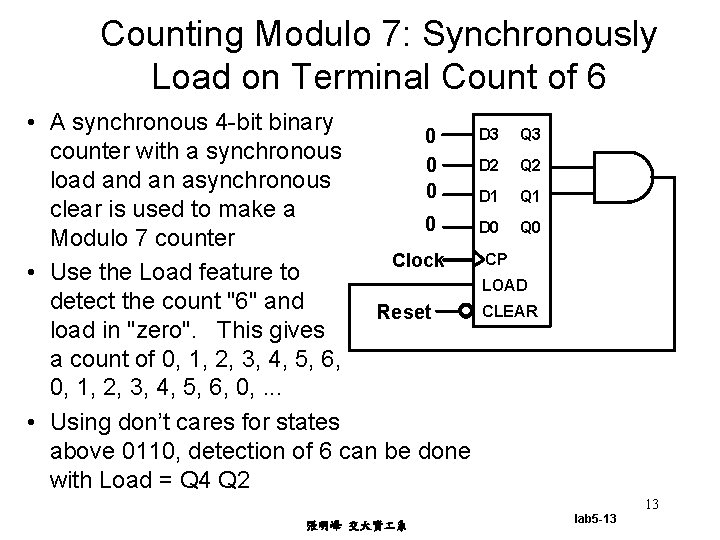

Counting Modulo 7: Synchronously Load on Terminal Count of 6 • A synchronous 4 -bit binary 0 counter with a synchronous 0 load an asynchronous 0 clear is used to make a 0 Modulo 7 counter Clock • Use the Load feature to detect the count "6" and Reset load in "zero". This gives a count of 0, 1, 2, 3, 4, 5, 6, 0, . . . • Using don’t cares for states above 0110, detection of 6 can be done with Load = Q 4 Q 2 D 3 Q 3 D 2 Q 2 D 1 Q 1 D 0 Q 0 CP LOAD CLEAR 13 張明峰 交大資 系 lab 5 -13

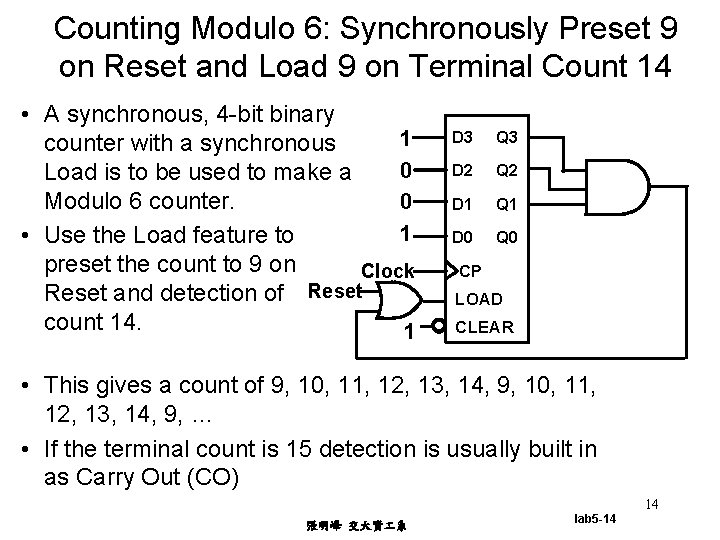

Counting Modulo 6: Synchronously Preset 9 on Reset and Load 9 on Terminal Count 14 • A synchronous, 4 -bit binary 1 counter with a synchronous 0 Load is to be used to make a Modulo 6 counter. 0 1 • Use the Load feature to preset the count to 9 on Clock Reset and detection of Reset count 14. 1 D 3 Q 3 D 2 Q 2 D 1 Q 1 D 0 Q 0 CP LOAD CLEAR • This gives a count of 9, 10, 11, 12, 13, 14, 9, … • If the terminal count is 15 detection is usually built in as Carry Out (CO) 14 張明峰 交大資 系 lab 5 -14

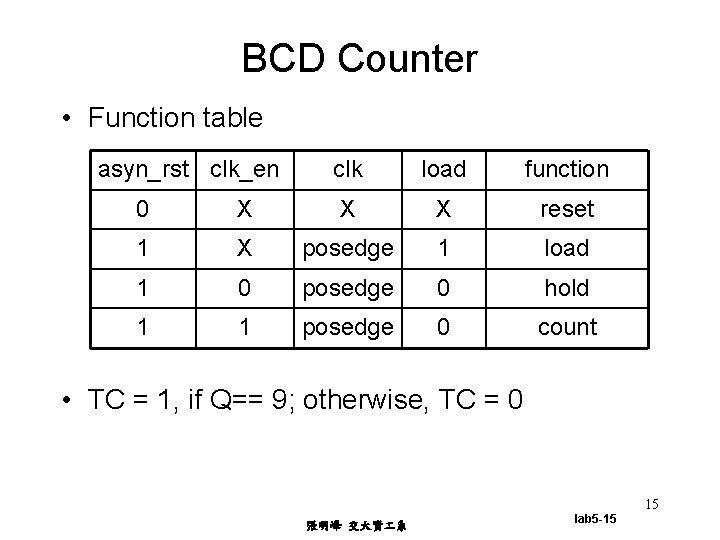

BCD Counter • Function table asyn_rst clk_en clk load function 0 X X X reset 1 X posedge 1 load 1 0 posedge 0 hold 1 1 posedge 0 count • TC = 1, if Q== 9; otherwise, TC = 0 15 張明峰 交大資 系 lab 5 -15

• A two-digit BCD counter – two synchronous BCD counters – two 7 -segment decoders 16 張明峰 交大資 系 lab 5 -16

- Slides: 16