Redesign control FSM of a multicycle MIPS processor

- Slides: 21

Redesign control FSM of a multicycle MIPS processor with low power state encoding

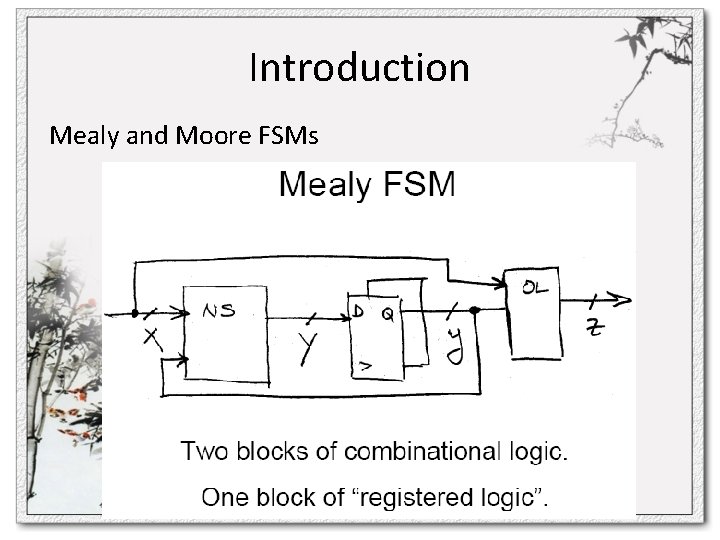

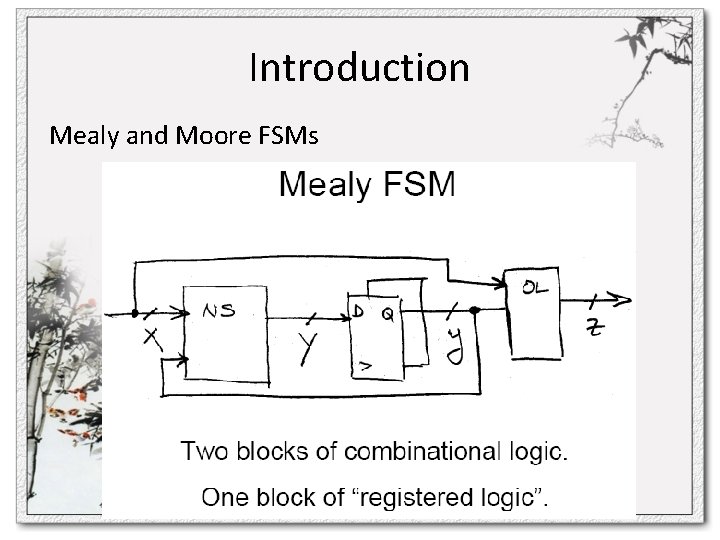

Introduction Mealy and Moore FSMs

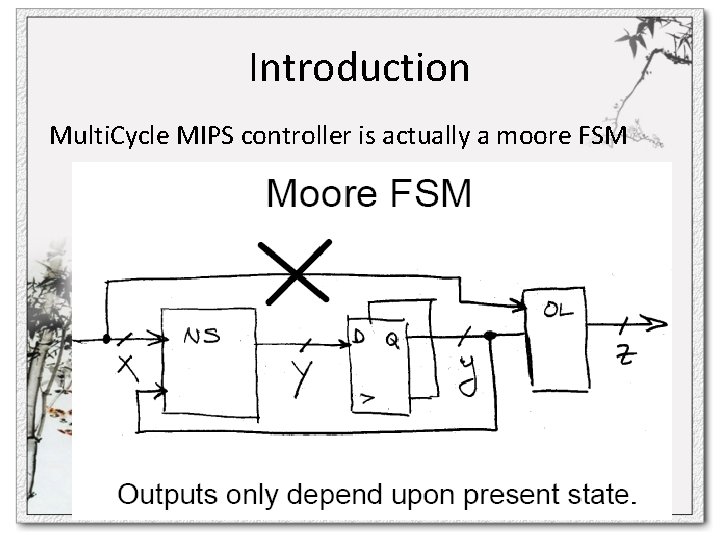

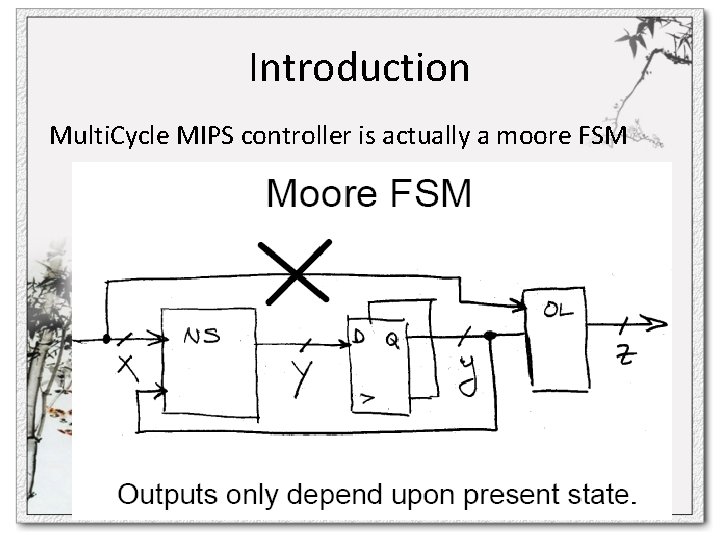

Introduction Multi. Cycle MIPS controller is actually a moore FSM

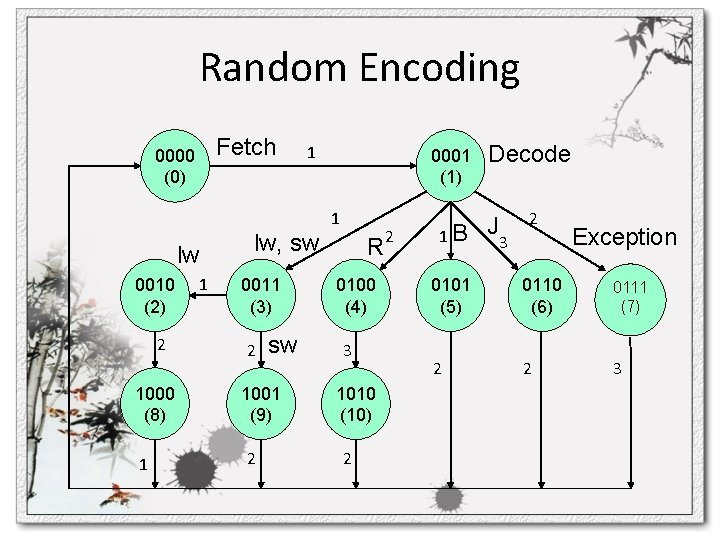

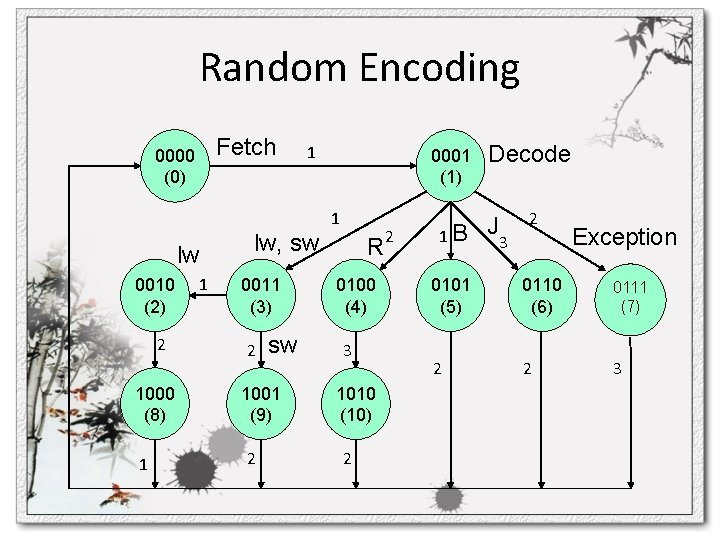

Random Encoding Fetch 0000 (0) lw 0010 (2) 2 1000 (8) 1 1 1 lw, sw 0011 (3) 2 sw 1001 (9) 2 0001 (1) 1 R 0100 (4) 3 1010 (10) 2 2 Decode 1 B J 3 2 Exception 0101 (5) 0110 (6) 0111 (7) 2 2 3

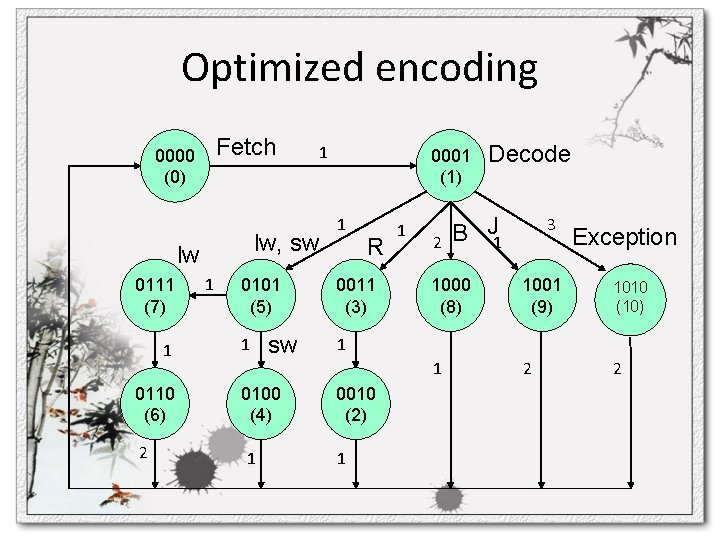

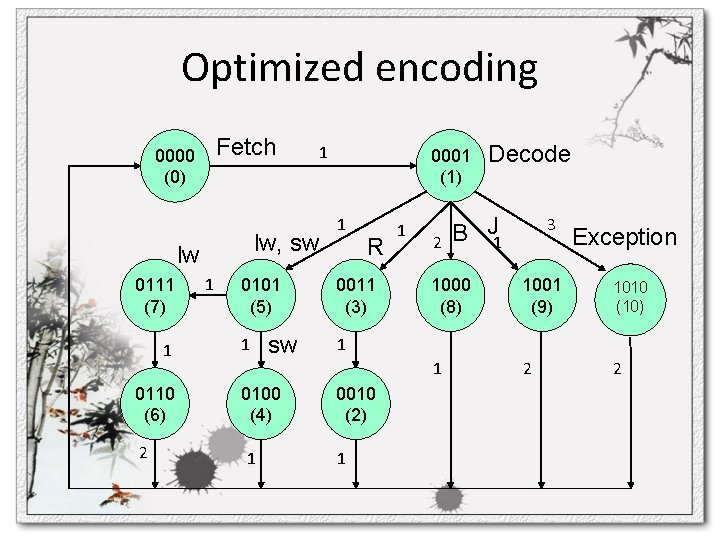

Optimized encoding Fetch 0000 (0) lw, sw lw 0111 (7) 1 0110 (6) 2 1 0101 (5) 1 sw 0100 (4) 1 1 0001 (1) 1 R 0011 (3) 1 2 Decode B J 1 3 Exception 1000 (8) 1001 (9) 1010 (10) 1 2 2 1 0010 (2) 1

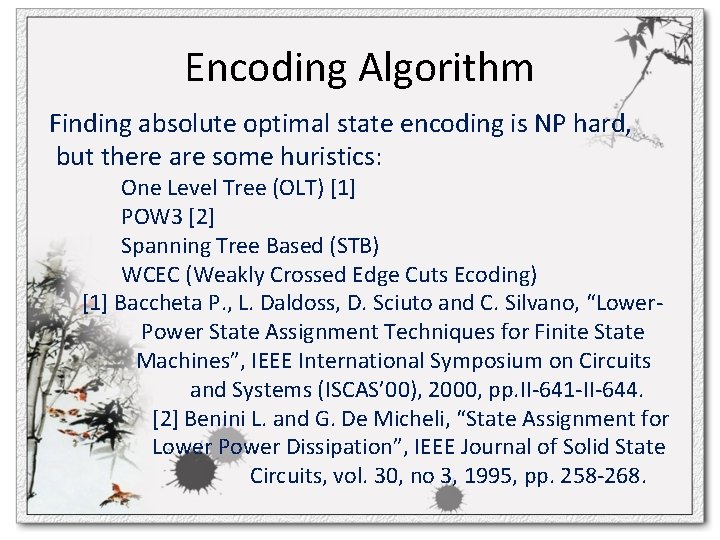

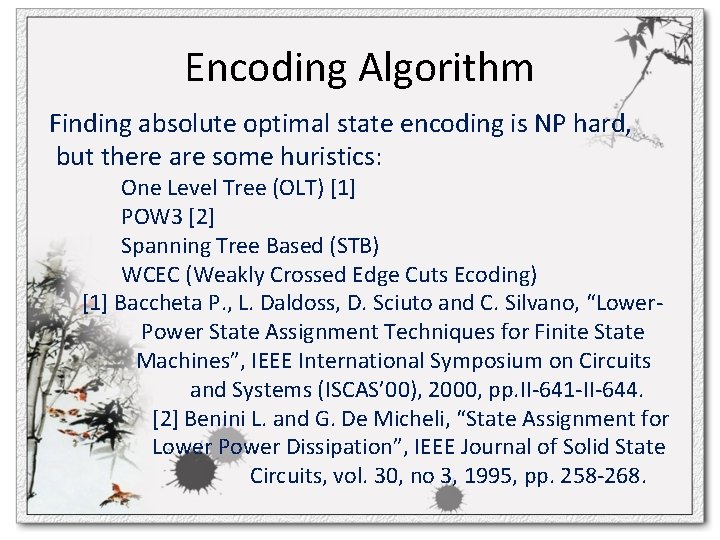

Encoding Algorithm Finding absolute optimal state encoding is NP hard, but there are some huristics: One Level Tree (OLT) [1] POW 3 [2] Spanning Tree Based (STB) WCEC (Weakly Crossed Edge Cuts Ecoding) [1] Baccheta P. , L. Daldoss, D. Sciuto and C. Silvano, “Lower. Power State Assignment Techniques for Finite State Machines”, IEEE International Symposium on Circuits and Systems (ISCAS’ 00), 2000, pp. II-641 -II-644. [2] Benini L. and G. De Micheli, “State Assignment for Lower Power Dissipation”, IEEE Journal of Solid State Circuits, vol. 30, no 3, 1995, pp. 258 -268.

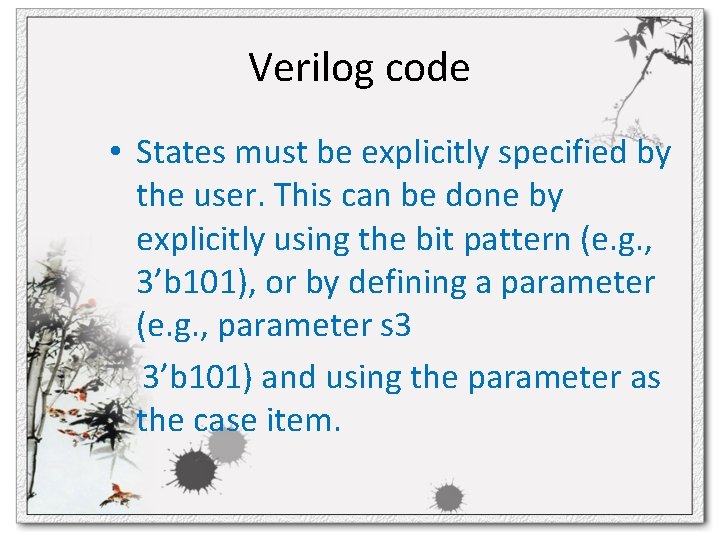

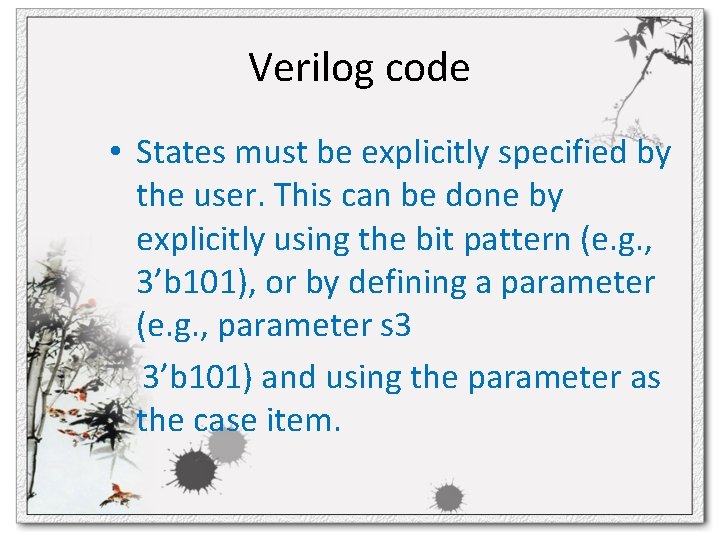

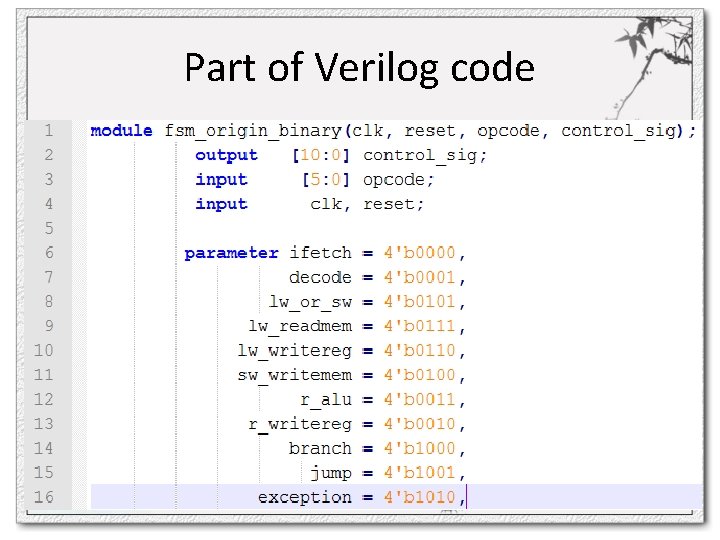

Verilog code • States must be explicitly specified by the user. This can be done by explicitly using the bit pattern (e. g. , 3’b 101), or by defining a parameter (e. g. , parameter s 3 3’b 101) and using the parameter as the case item.

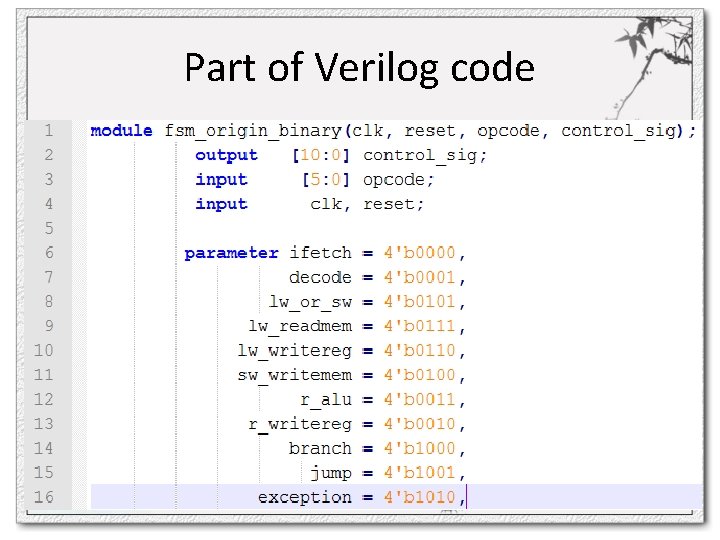

Part of Verilog code

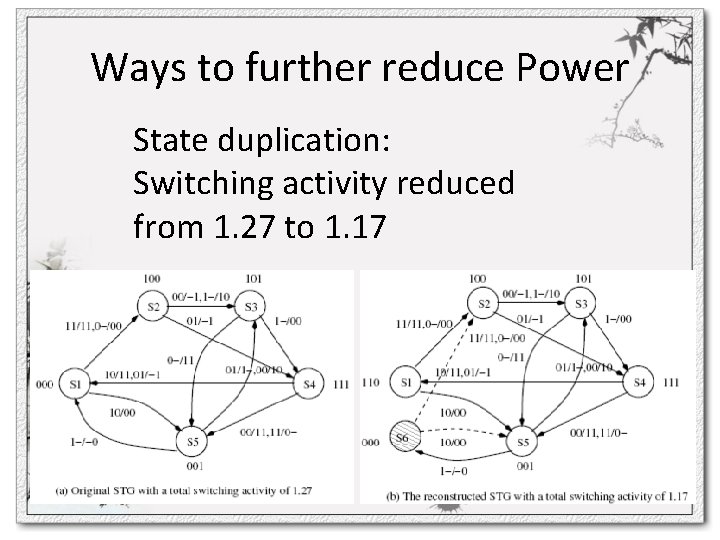

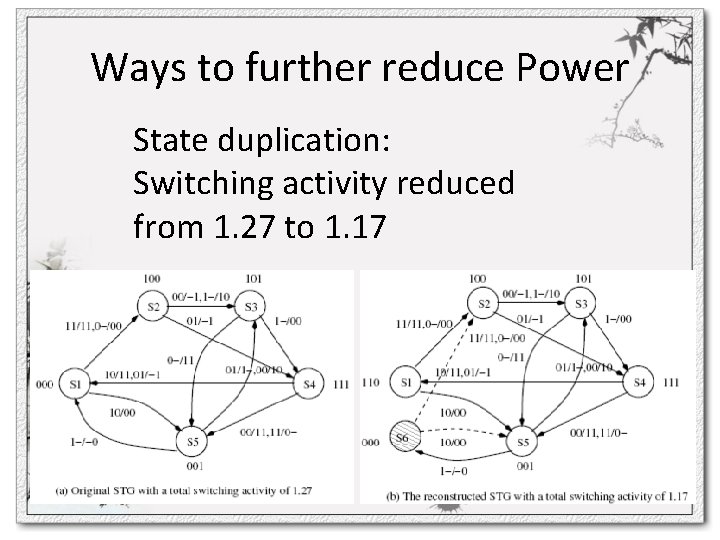

Ways to further reduce Power State duplication: Switching activity reduced from 1. 27 to 1. 17

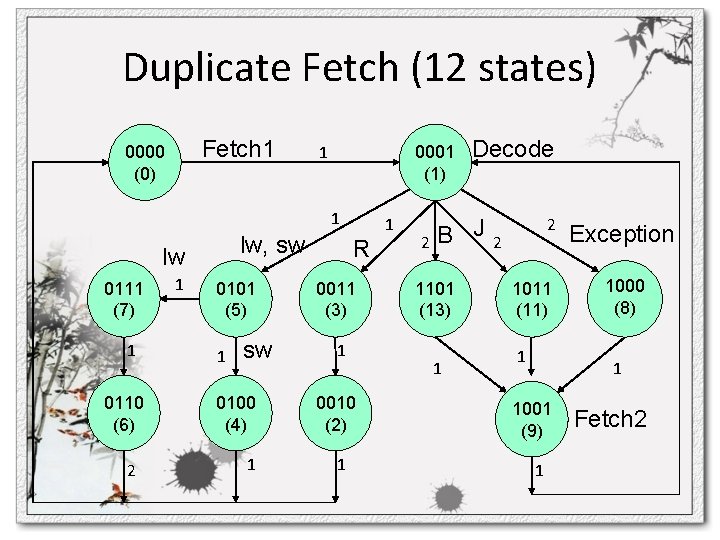

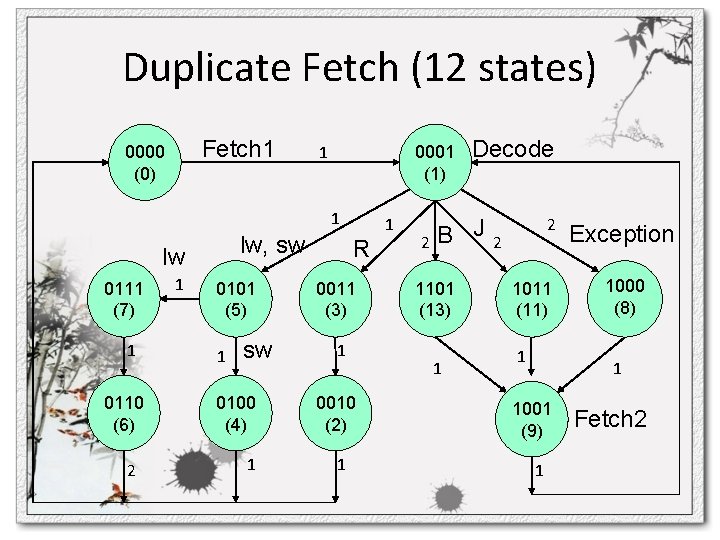

Duplicate Fetch (12 states) Fetch 1 0000 (0) 1 0001 (1) 1 lw, sw lw 0111 (7) 1 0110 (6) 2 1 0101 (5) 1 sw 0100 (4) 1 1 R 0011 (3) 1 0010 (2) 1 Decode J B 2 1101 (13) 1 2 2 1011 (11) 1 Exception 1000 (8) 1 1001 (9) 1 Fetch 2

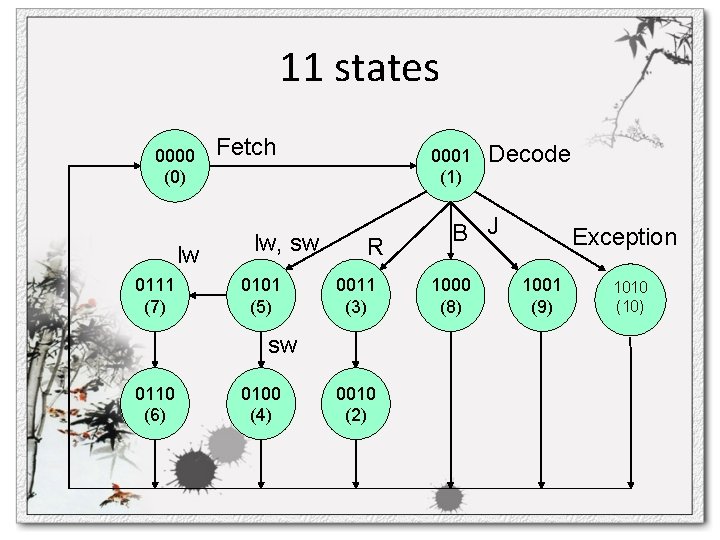

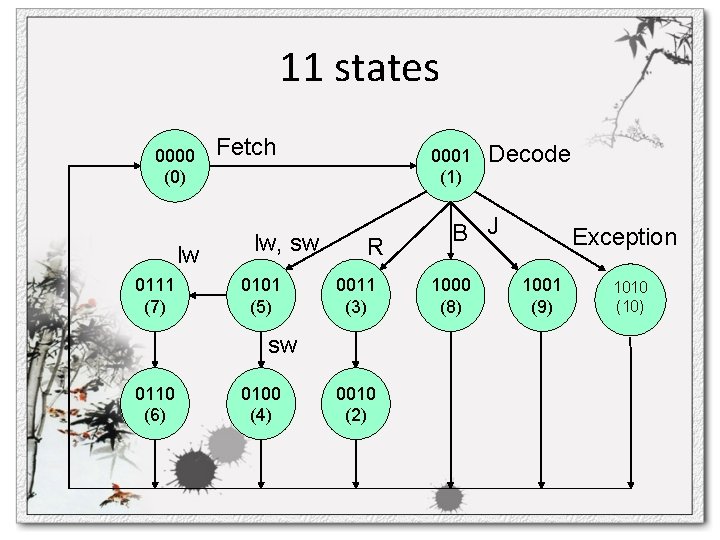

11 states 0000 (0) lw 0111 (7) Fetch lw, sw 0101 (5) 0001 (1) R 0011 (3) sw 0110 (6) 0100 (4) 0010 (2) Decode B J 1000 (8) Exception 1001 (9) 1010 (10)

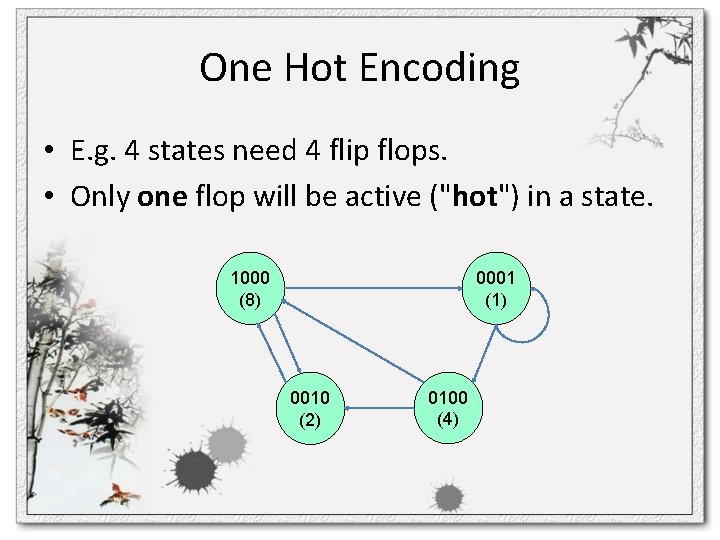

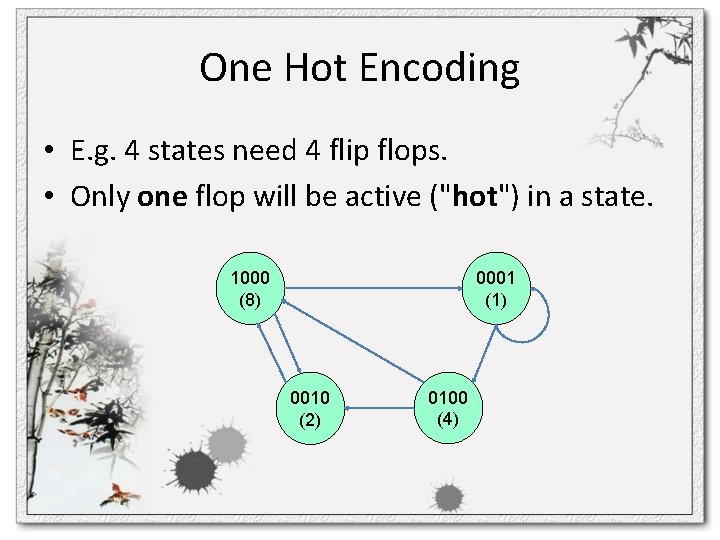

One Hot Encoding • E. g. 4 states need 4 flip flops. • Only one flop will be active ("hot") in a state. 1000 (8) 0001 (1) 0010 (2) 0100 (4)

Advantages Low power (since only one toggle when state changes) Simple decoding logic. (Greatly reduces the complexity of CL) Popular method is onehot. FPGA has lot of registers compared to CPLD. so onehot is more suitable for FPGA

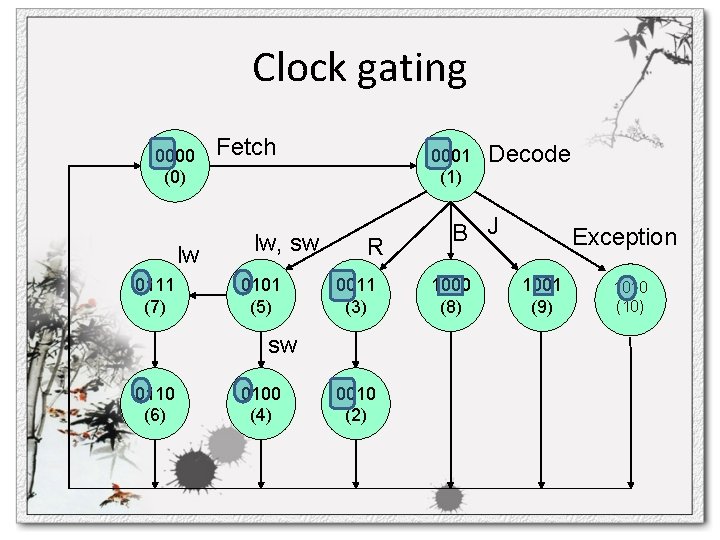

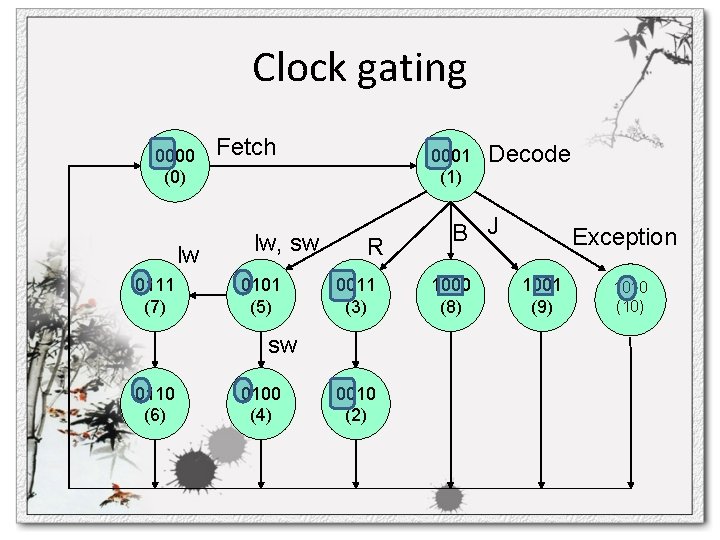

Clock gating 0000 (0) lw 0111 (7) Fetch lw, sw 0101 (5) 0001 (1) R 0011 (3) sw 0110 (6) 0100 (4) 0010 (2) Decode B J 1000 (8) Exception 1001 (9) 1010 (10)

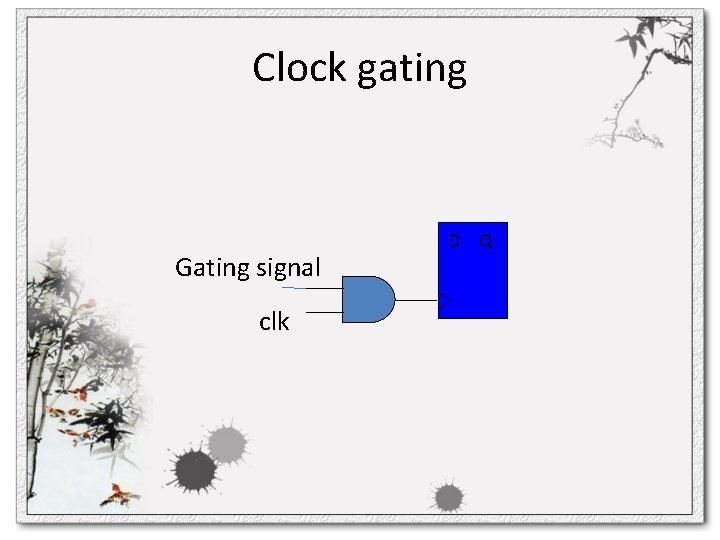

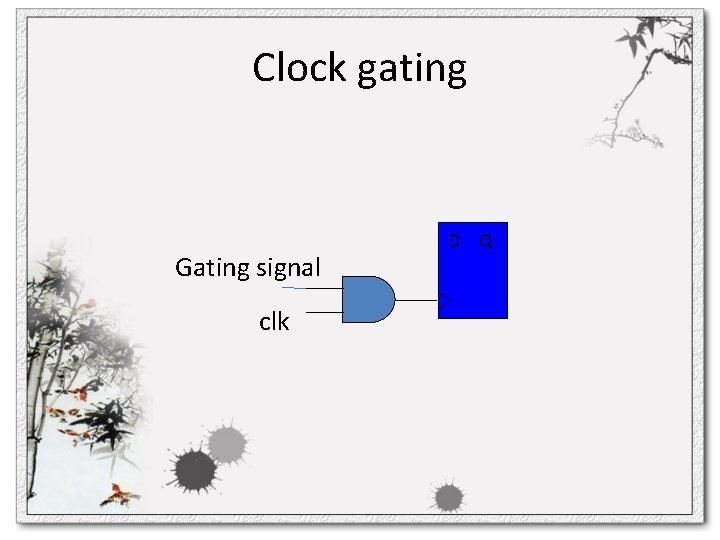

Clock gating Gating signal clk D Q

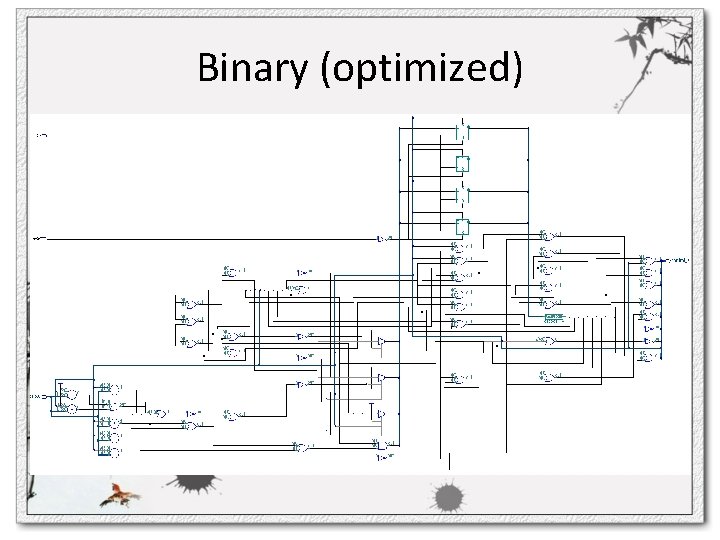

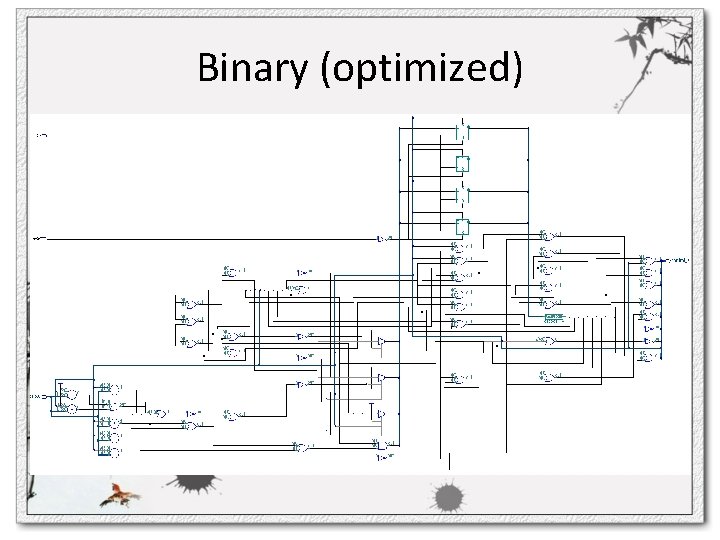

Binary (optimized)

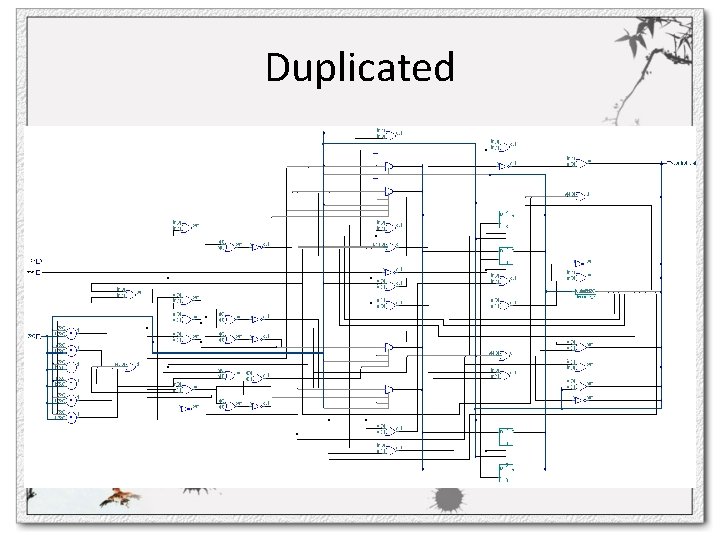

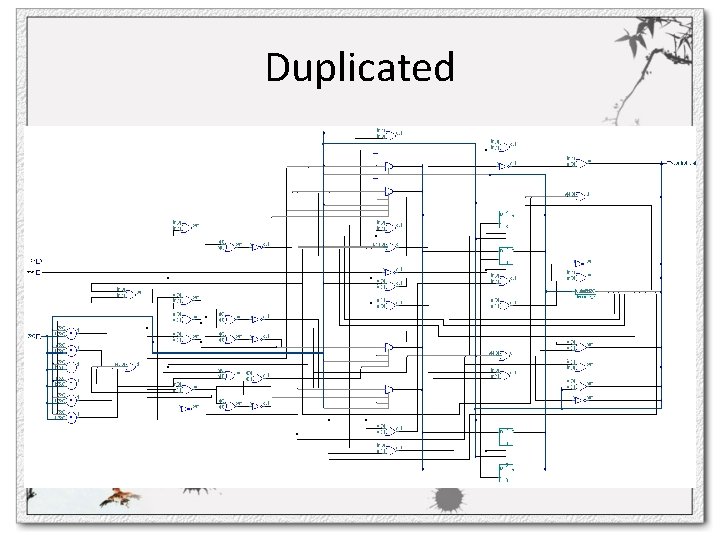

Duplicated

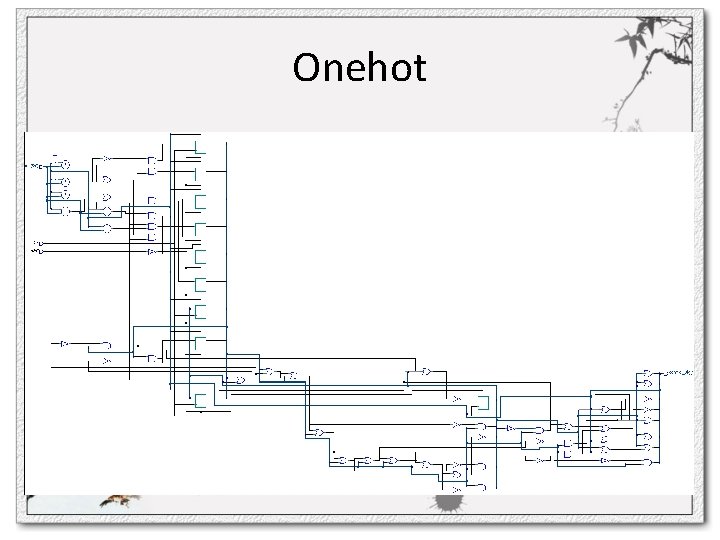

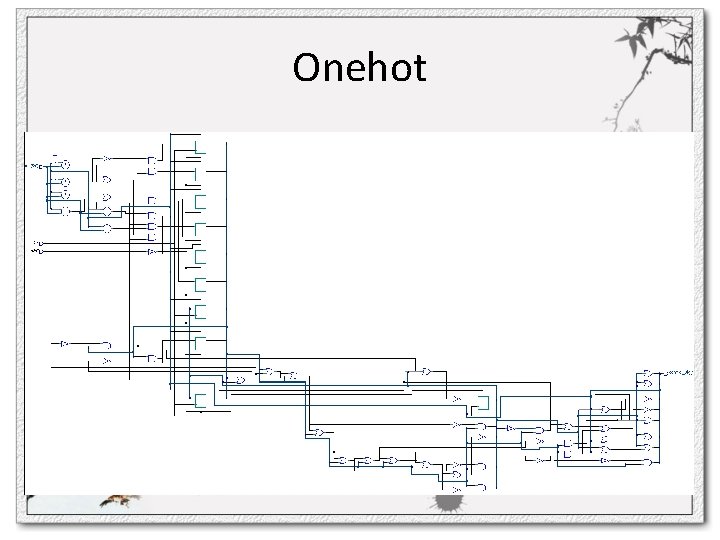

Onehot

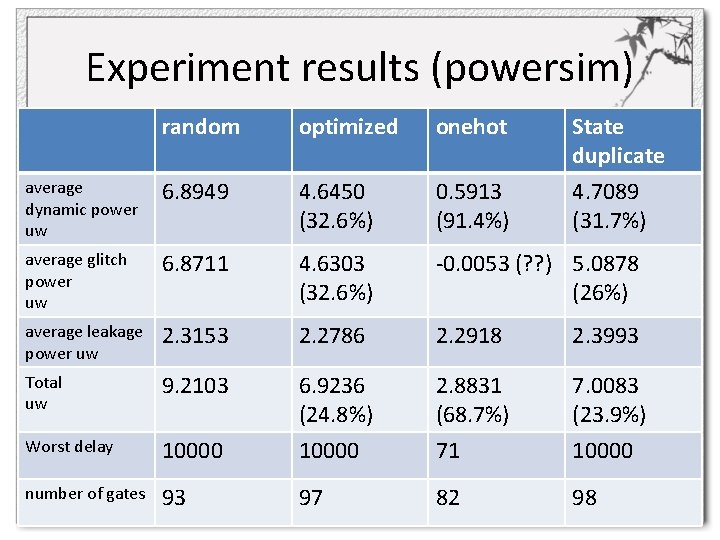

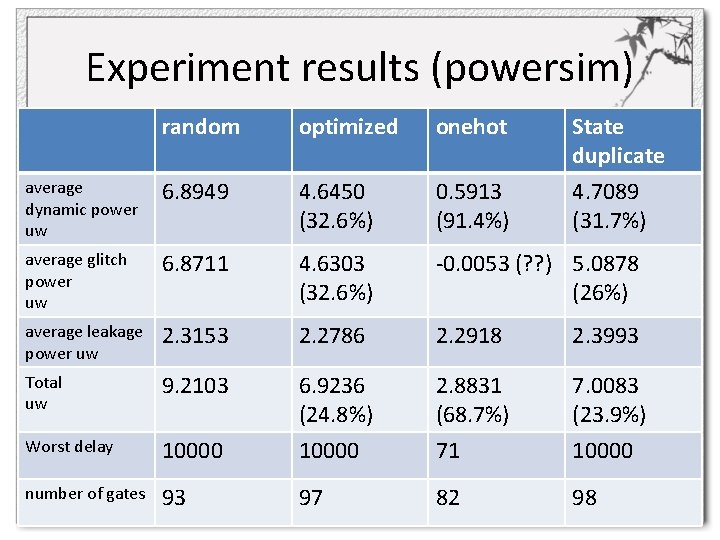

Experiment results (powersim) random optimized onehot State duplicate 4. 7089 (31. 7%) average dynamic power uw 6. 8949 4. 6450 (32. 6%) 0. 5913 (91. 4%) average glitch power uw 6. 8711 4. 6303 (32. 6%) -0. 0053 (? ? ) 5. 0878 (26%) average leakage power uw 2. 3153 2. 2786 2. 2918 2. 3993 Total uw 9. 2103 6. 9236 (24. 8%) 2. 8831 (68. 7%) 7. 0083 (23. 9%) Worst delay 10000 71 10000 number of gates 93 97 82 98

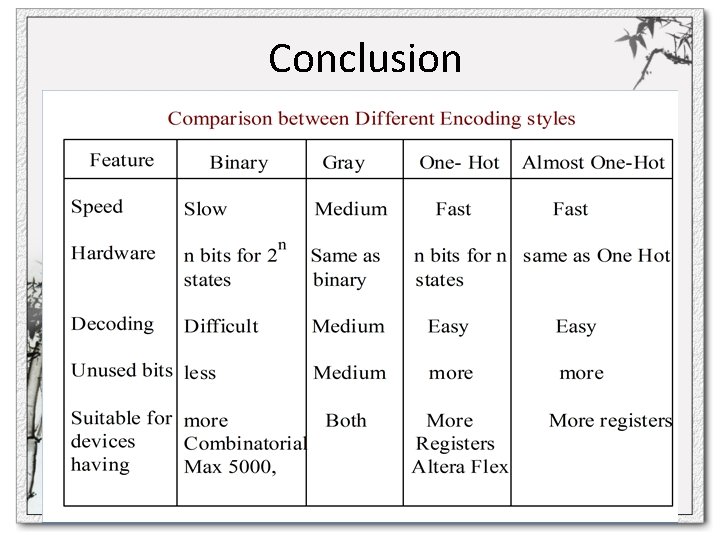

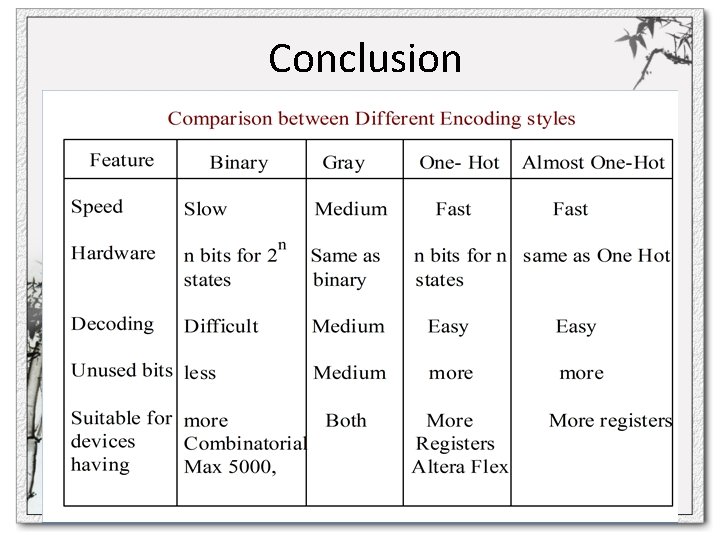

Conclusion

Thank You! Questions?