JESD 204 B Link Bring UP and Debug

JESD 204 B Link Bring UP and Debug June 2014

PART 1 : UNDERSTANDING AND DEBUGGING JESD 204 B

content • Introduction – Test. Bench description • Getting started: Achieving CGS – What to expect – Debugging tips during CGS phase • Getting pass ILAS – What to expect during ILAS – Tips for debugging ILAS phase • User data phase – Understanding alignment character insertion and replacement – Tips for debugging user data phase

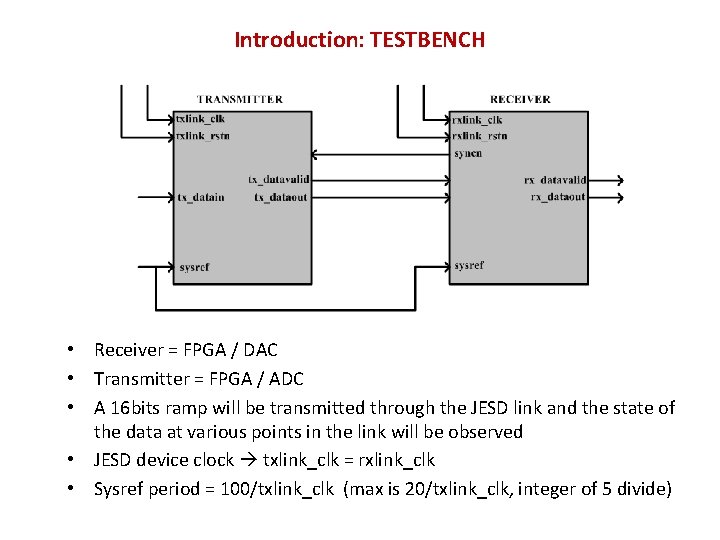

Introduction: TESTBENCH • Receiver = FPGA / DAC • Transmitter = FPGA / ADC • A 16 bits ramp will be transmitted through the JESD link and the state of the data at various points in the link will be observed • JESD device clock txlink_clk = rxlink_clk • Sysref period = 100/txlink_clk (max is 20/txlink_clk, integer of 5 divide)

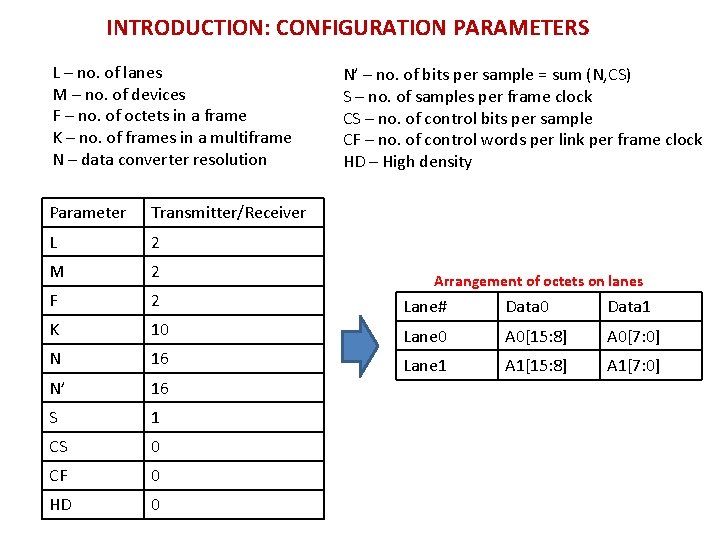

INTRODUCTION: CONFIGURATION PARAMETERS L – no. of lanes M – no. of devices F – no. of octets in a frame K – no. of frames in a multiframe N – data converter resolution N’ – no. of bits per sample = sum (N, CS) S – no. of samples per frame clock CS – no. of control bits per sample CF – no. of control words per link per frame clock HD – High density Parameter Transmitter/Receiver L 2 M 2 F 2 Lane# Data 0 Data 1 K 10 Lane 0 A 0[15: 8] A 0[7: 0] N 16 Lane 1 A 1[15: 8] A 1[7: 0] N’ 16 S 1 CS 0 CF 0 HD 0 Arrangement of octets on lanes

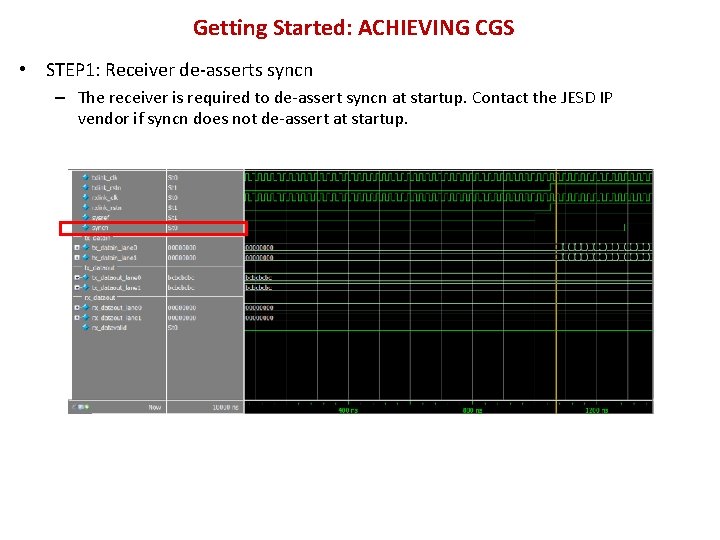

Getting Started: ACHIEVING CGS • STEP 1: Receiver de-asserts syncn – The receiver is required to de-assert syncn at startup. Contact the JESD IP vendor if syncn does not de-assert at startup.

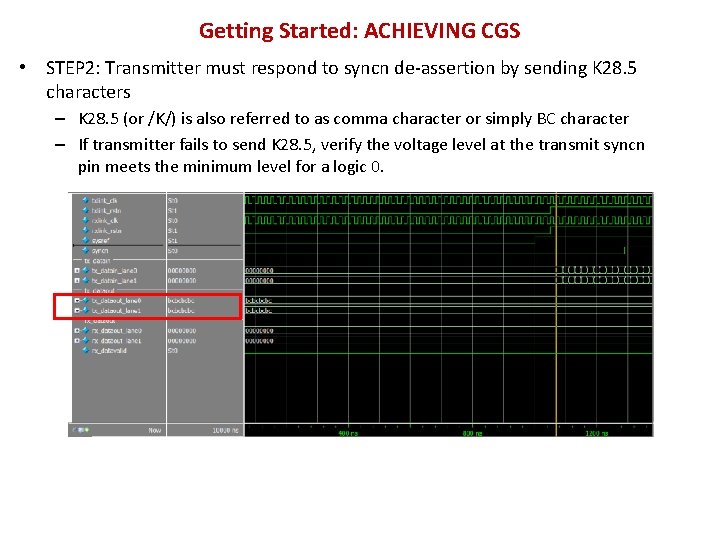

Getting Started: ACHIEVING CGS • STEP 2: Transmitter must respond to syncn de-assertion by sending K 28. 5 characters – K 28. 5 (or /K/) is also referred to as comma character or simply BC character – If transmitter fails to send K 28. 5, verify the voltage level at the transmit syncn pin meets the minimum level for a logic 0.

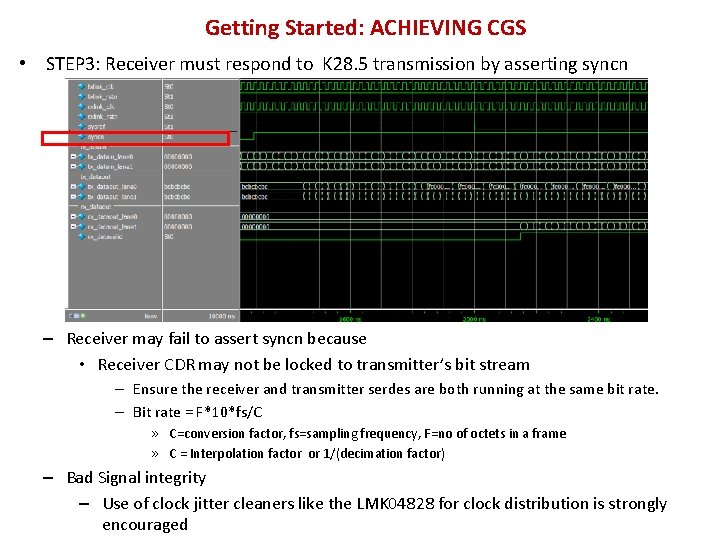

Getting Started: ACHIEVING CGS • STEP 3: Receiver must respond to K 28. 5 transmission by asserting syncn – Receiver may fail to assert syncn because • Receiver CDR may not be locked to transmitter’s bit stream – Ensure the receiver and transmitter serdes are both running at the same bit rate. – Bit rate = F*10*fs/C » C=conversion factor, fs=sampling frequency, F=no of octets in a frame » C = Interpolation factor or 1/(decimation factor) – Bad Signal integrity – Use of clock jitter cleaners like the LMK 04828 for clock distribution is strongly encouraged

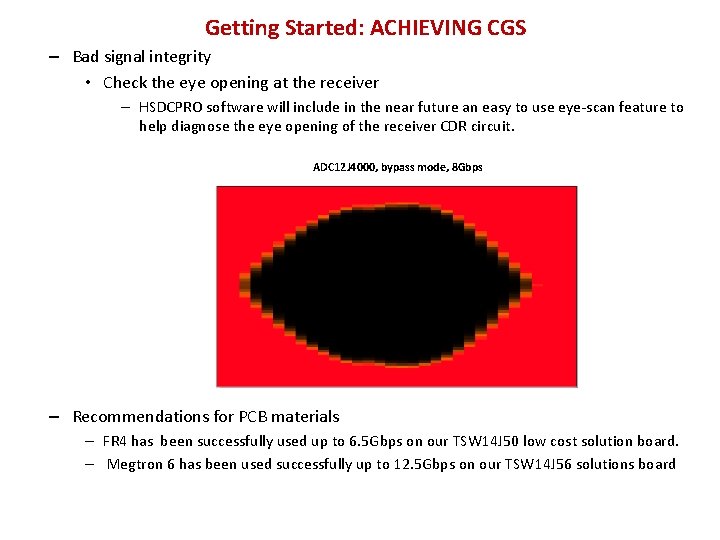

Getting Started: ACHIEVING CGS – Bad signal integrity • Check the eye opening at the receiver – HSDCPRO software will include in the near future an easy to use eye-scan feature to help diagnose the eye opening of the receiver CDR circuit. ADC 12 J 4000, bypass mode, 8 Gbps – Recommendations for PCB materials – FR 4 has been successfully used up to 6. 5 Gbps on our TSW 14 J 50 low cost solution board. – Megtron 6 has been used successfully up to 12. 5 Gbps on our TSW 14 J 56 solutions board

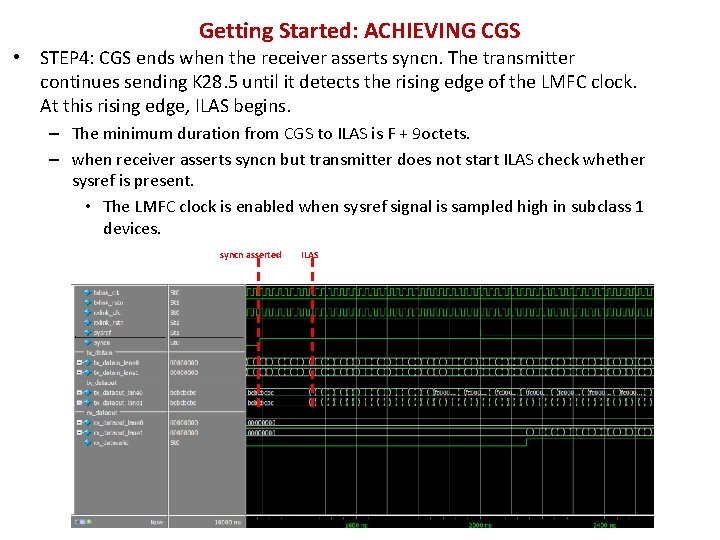

Getting Started: ACHIEVING CGS • STEP 4: CGS ends when the receiver asserts syncn. The transmitter continues sending K 28. 5 until it detects the rising edge of the LMFC clock. At this rising edge, ILAS begins. – The minimum duration from CGS to ILAS is F + 9 octets. – when receiver asserts syncn but transmitter does not start ILAS check whether sysref is present. • The LMFC clock is enabled when sysref signal is sampled high in subclass 1 devices. syncn asserted ILAS

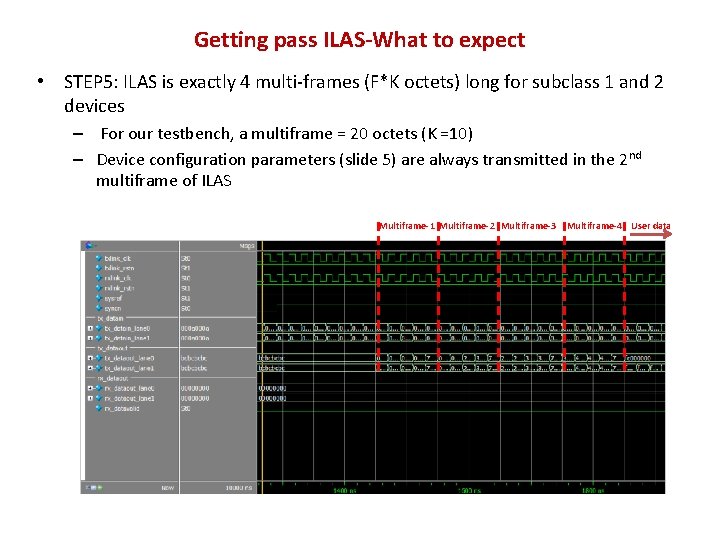

Getting pass ILAS-What to expect • STEP 5: ILAS is exactly 4 multi-frames (F*K octets) long for subclass 1 and 2 devices – For our testbench, a multiframe = 20 octets (K =10) – Device configuration parameters (slide 5) are always transmitted in the 2 nd multiframe of ILAS Multiframe-1 Multiframe-2 Multiframe-3 Multiframe-4 User data

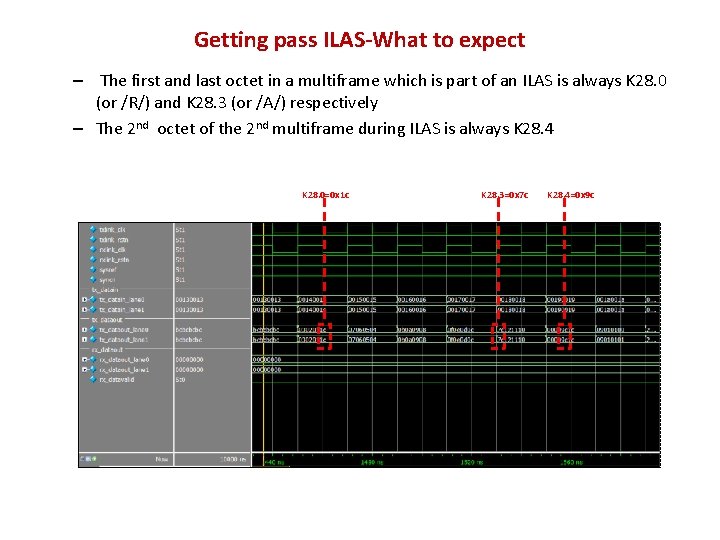

Getting pass ILAS-What to expect – The first and last octet in a multiframe which is part of an ILAS is always K 28. 0 (or /R/) and K 28. 3 (or /A/) respectively – The 2 nd octet of the 2 nd multiframe during ILAS is always K 28. 4 K 28. 0=0 x 1 c K 28. 3=0 x 7 c K 28. 4=0 x 9 c

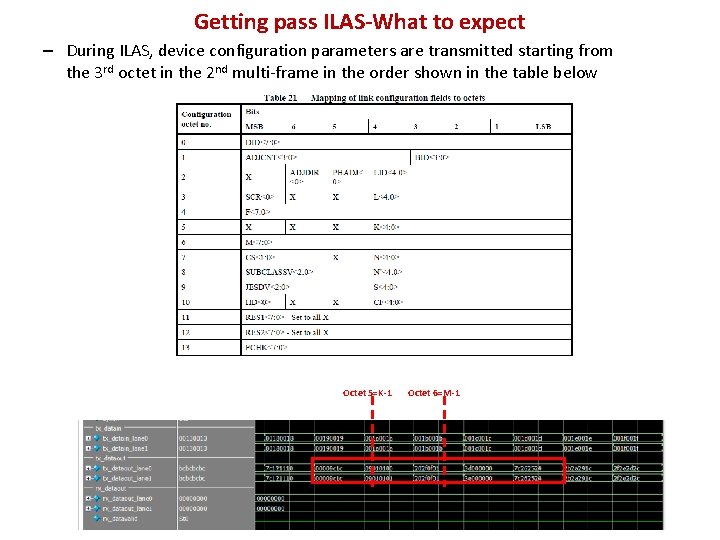

Getting pass ILAS-What to expect – During ILAS, device configuration parameters are transmitted starting from the 3 rd octet in the 2 nd multi-frame in the order shown in the table below Octet 5=K-1 Octet 6=M-1

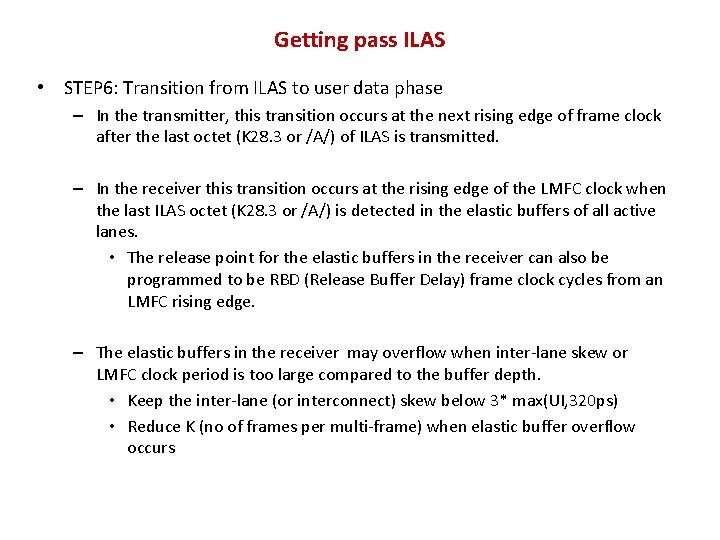

Getting pass ILAS • STEP 6: Transition from ILAS to user data phase – In the transmitter, this transition occurs at the next rising edge of frame clock after the last octet (K 28. 3 or /A/) of ILAS is transmitted. – In the receiver this transition occurs at the rising edge of the LMFC clock when the last ILAS octet (K 28. 3 or /A/) is detected in the elastic buffers of all active lanes. • The release point for the elastic buffers in the receiver can also be programmed to be RBD (Release Buffer Delay) frame clock cycles from an LMFC rising edge. – The elastic buffers in the receiver may overflow when inter-lane skew or LMFC clock period is too large compared to the buffer depth. • Keep the inter-lane (or interconnect) skew below 3* max(UI, 320 ps) • Reduce K (no of frames per multi-frame) when elastic buffer overflow occurs

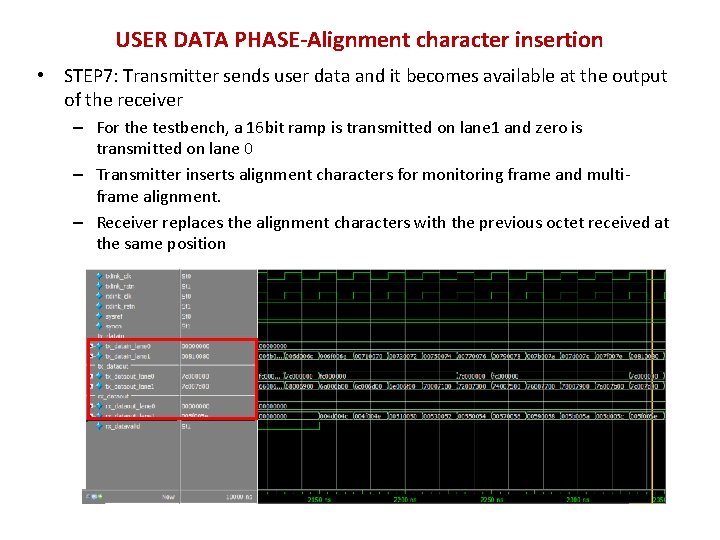

USER DATA PHASE-Alignment character insertion • STEP 7: Transmitter sends user data and it becomes available at the output of the receiver – For the testbench, a 16 bit ramp is transmitted on lane 1 and zero is transmitted on lane 0 – Transmitter inserts alignment characters for monitoring frame and multiframe alignment. – Receiver replaces the alignment characters with the previous octet received at the same position

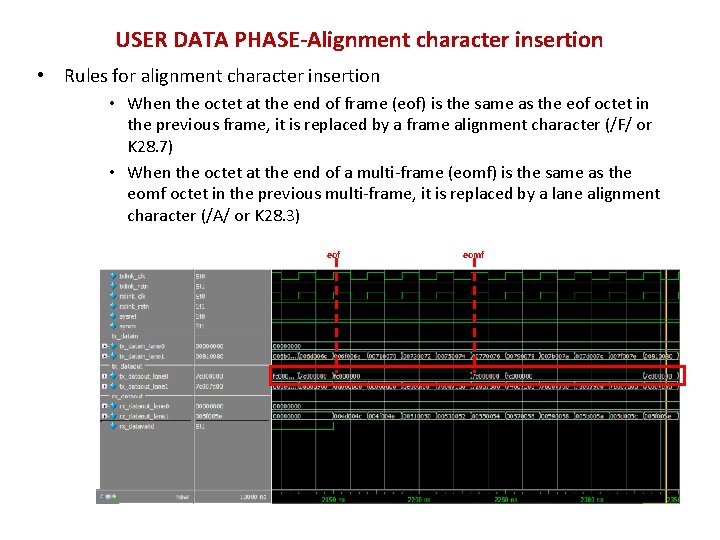

USER DATA PHASE-Alignment character insertion • Rules for alignment character insertion • When the octet at the end of frame (eof) is the same as the eof octet in the previous frame, it is replaced by a frame alignment character (/F/ or K 28. 7) • When the octet at the end of a multi-frame (eomf) is the same as the eomf octet in the previous multi-frame, it is replaced by a lane alignment character (/A/ or K 28. 3) eof eomf

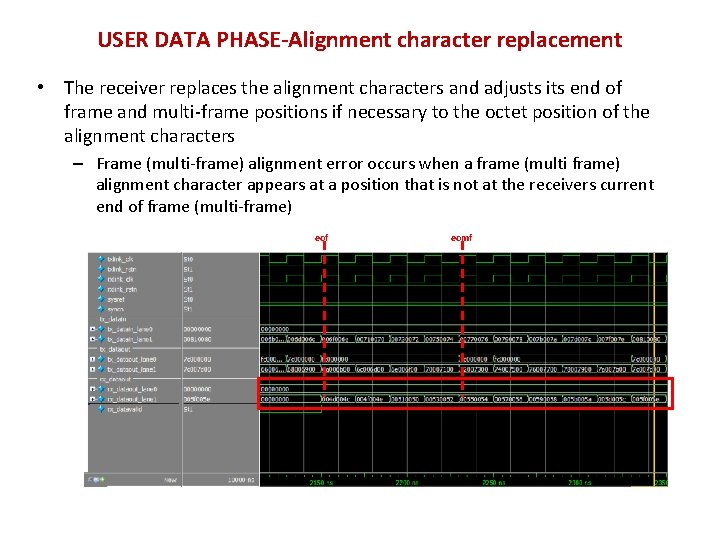

USER DATA PHASE-Alignment character replacement • The receiver replaces the alignment characters and adjusts its end of frame and multi-frame positions if necessary to the octet position of the alignment characters – Frame (multi-frame) alignment error occurs when a frame (multi frame) alignment character appears at a position that is not at the receivers current end of frame (multi-frame) eof eomf

PART 2 : UNDERSTANDING AND DEBUGGING THE PHYSICAL LINK

content • Introduction – Test. Bench description for physical link debug • 8 B 10 B encoder/decoder • Word alignment in receiver

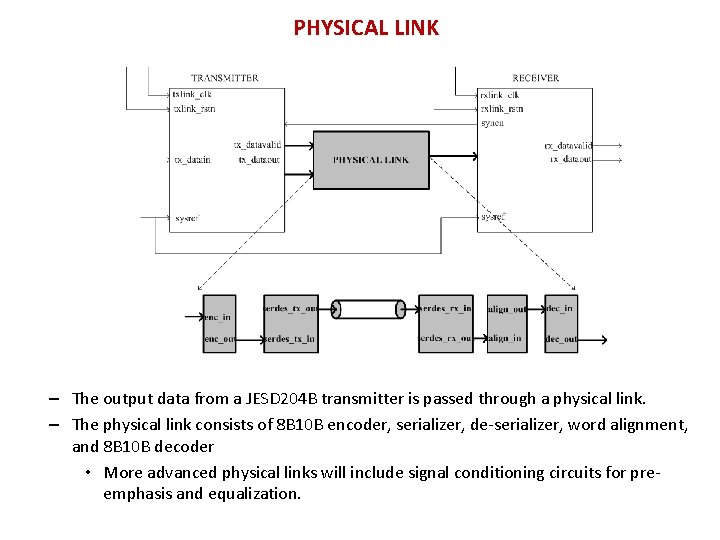

PHYSICAL LINK – The output data from a JESD 204 B transmitter is passed through a physical link. – The physical link consists of 8 B 10 B encoder, serializer, de-serializer, word alignment, and 8 B 10 B decoder • More advanced physical links will include signal conditioning circuits for preemphasis and equalization.

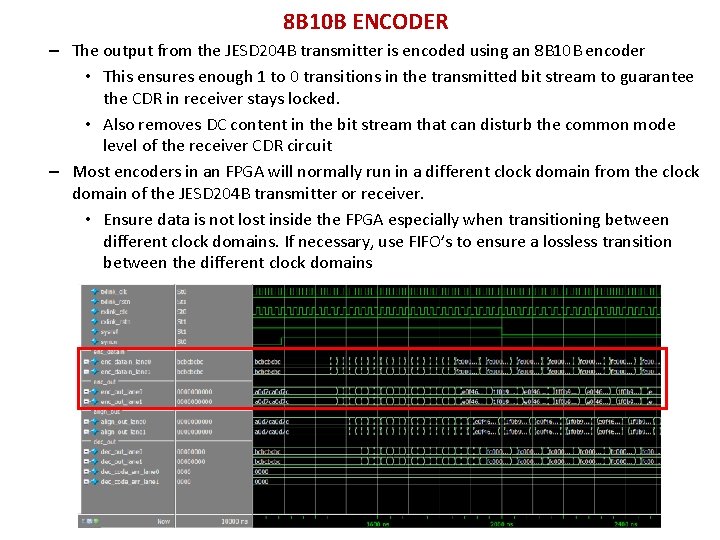

8 B 10 B ENCODER – The output from the JESD 204 B transmitter is encoded using an 8 B 10 B encoder • This ensures enough 1 to 0 transitions in the transmitted bit stream to guarantee the CDR in receiver stays locked. • Also removes DC content in the bit stream that can disturb the common mode level of the receiver CDR circuit – Most encoders in an FPGA will normally run in a different clock domain from the clock domain of the JESD 204 B transmitter or receiver. • Ensure data is not lost inside the FPGA especially when transitioning between different clock domains. If necessary, use FIFO’s to ensure a lossless transition between the different clock domains

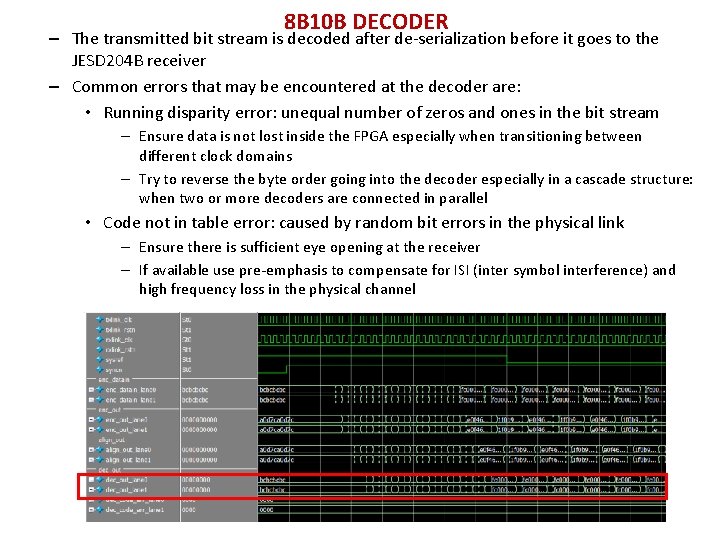

8 B 10 B DECODER – The transmitted bit stream is decoded after de-serialization before it goes to the JESD 204 B receiver – Common errors that may be encountered at the decoder are: • Running disparity error: unequal number of zeros and ones in the bit stream – Ensure data is not lost inside the FPGA especially when transitioning between different clock domains – Try to reverse the byte order going into the decoder especially in a cascade structure: when two or more decoders are connected in parallel • Code not in table error: caused by random bit errors in the physical link – Ensure there is sufficient eye opening at the receiver – If available use pre-emphasis to compensate for ISI (inter symbol interference) and high frequency loss in the physical channel

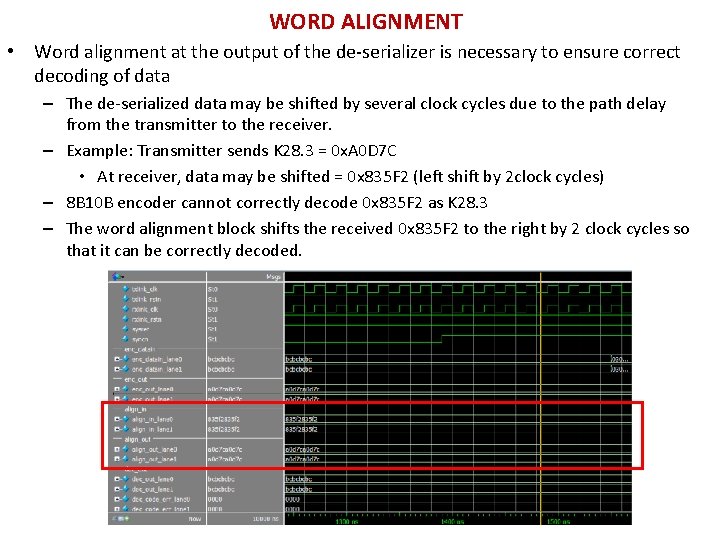

WORD ALIGNMENT • Word alignment at the output of the de-serializer is necessary to ensure correct decoding of data – The de-serialized data may be shifted by several clock cycles due to the path delay from the transmitter to the receiver. – Example: Transmitter sends K 28. 3 = 0 x. A 0 D 7 C • At receiver, data may be shifted = 0 x 835 F 2 (left shift by 2 clock cycles) – 8 B 10 B encoder cannot correctly decode 0 x 835 F 2 as K 28. 3 – The word alignment block shifts the received 0 x 835 F 2 to the right by 2 clock cycles so that it can be correctly decoded.

PART 3 : WORKING WITH TI DATA CONVERTERS AND COMMON FPGAs

content • Working with Altera FPGA – Parameterize and Instantiate JESD 204 B IP – Clocking – Recommended pin constraint settings • Working with Xilinx FPGA – Description of JESD 204 B IP – Clocking – Recommended pin constraint settings

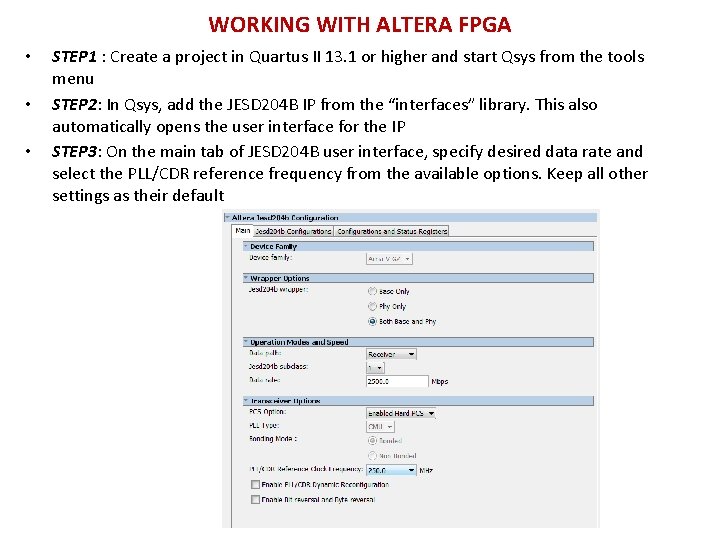

WORKING WITH ALTERA FPGA • • • STEP 1 : Create a project in Quartus II 13. 1 or higher and start Qsys from the tools menu STEP 2: In Qsys, add the JESD 204 B IP from the “interfaces” library. This also automatically opens the user interface for the IP STEP 3: On the main tab of JESD 204 B user interface, specify desired data rate and select the PLL/CDR reference frequency from the available options. Keep all other settings as their default

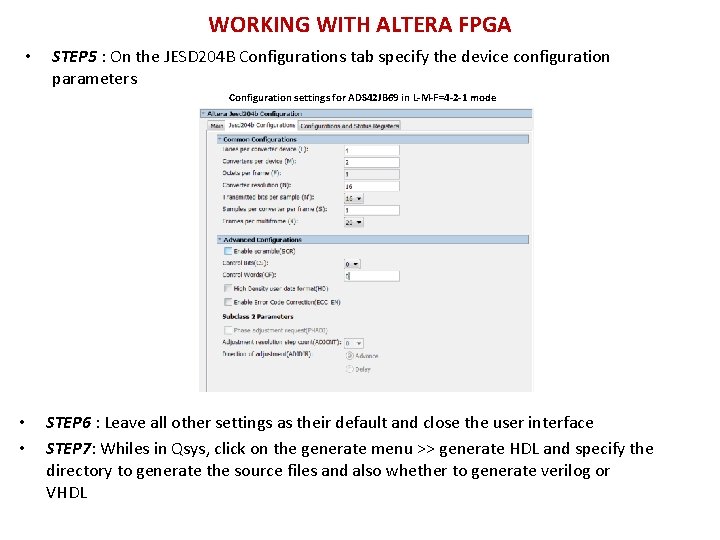

WORKING WITH ALTERA FPGA • STEP 5 : On the JESD 204 B Configurations tab specify the device configuration parameters Configuration settings for ADS 42 JB 69 in L-M-F=4 -2 -1 mode • • STEP 6 : Leave all other settings as their default and close the user interface STEP 7: Whiles in Qsys, click on the generate menu >> generate HDL and specify the directory to generate the source files and also whether to generate verilog or VHDL

WORKING WITH ALTERA FPGA • • STEP 8 : From the generate menu, click on HDL example to generate an instantiation template that will be used later in Quartus. Copy this template and close Qsys STEP 9: In Quartus, browse to the directory where the JESD 204 B files were generated and add the. qip and. sip files to the project. STEP 10: Instantiate the JESD 204 B IP in your system with the instantiation template generated in step 8. STEP 11: – Connect the PLL reference clock (specified in step 3) and the output of the transceivers to their dedicated pins. – Connect sync and sysref to corresponding pins from the data converter. – Connect rx_link_clk (or tx_link_clk) to a clock source at data rate / 40. For this design since data rate is selected as 2500 Mbps (in step 3), rx_link_clk will be connected to a 62. 5 MHz source • • STEP 12: In the. qsf file for the project, specify I/O standards for the transceiver pins as 1. 5 V or 1. 4 V PCML, LVDS for the sysref and syncn pin. Sync can also be 2. 5 V/3 V CMOS if the data converter supports this. STEP 13: Compile the design and generate the programming files in Quartus

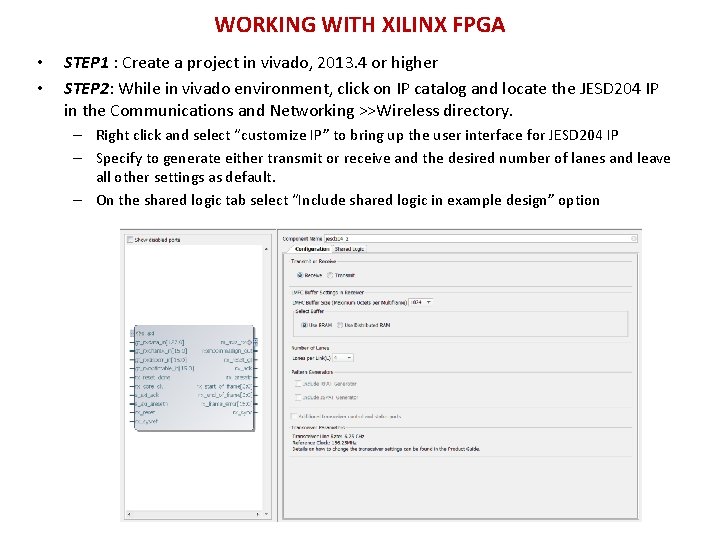

WORKING WITH XILINX FPGA • • STEP 1 : Create a project in vivado, 2013. 4 or higher STEP 2: While in vivado environment, click on IP catalog and locate the JESD 204 IP in the Communications and Networking >>Wireless directory. – Right click and select “customize IP” to bring up the user interface for JESD 204 IP – Specify to generate either transmit or receive and the desired number of lanes and leave all other settings as default. – On the shared logic tab select “Include shared logic in example design” option

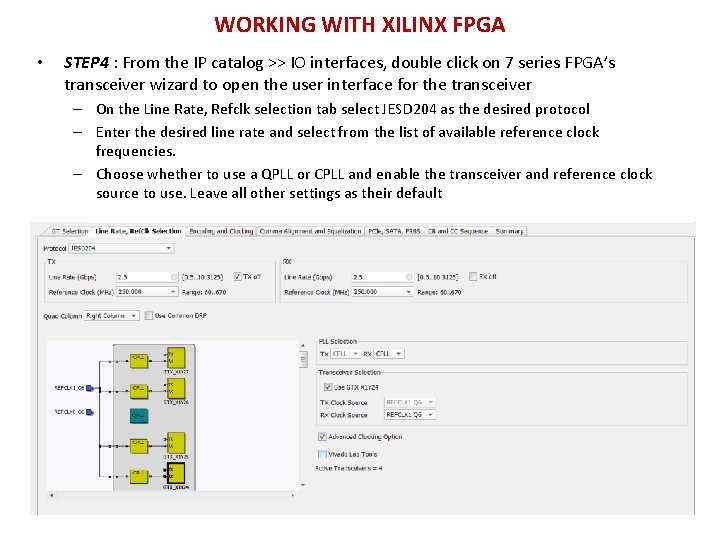

WORKING WITH XILINX FPGA • STEP 4 : From the IP catalog >> IO interfaces, double click on 7 series FPGA’s transceiver wizard to open the user interface for the transceiver – On the Line Rate, Refclk selection tab select JESD 204 as the desired protocol – Enter the desired line rate and select from the list of available reference clock frequencies. – Choose whether to use a QPLL or CPLL and enable the transceiver and reference clock source to use. Leave all other settings as their default

WORKING WITH XILINX FPGA • STEP 5 : Use the generated instantiation templates to create instances of the JESD 204 and transceiver in your design. • STEP 6 : Connect the JESD 204 serdes ports to the transceiver. – The rx_core_clk or tx_core_clk clock input of the JESD 204 B instance should be connected to a clock source at a frequency of lane rate/ 40. • STEP 7 : Open the. xdc file for the project and specify the pin names and IO standards for the transceiver, sysref, syncn and reference clocks. • STEP 8 : Compile the design and generate the needed programming file.

THANK YOU!!!

- Slides: 32