ITEC 352 Lecture 22 Pipelining Review Questions Homework

- Slides: 17

ITEC 352 Lecture 22 Pipelining

Review • • Questions? Homework 3 due next Wed. Control units for RISC Pipeline – Why? Problems? • Video Pipelining

Outline • Pipelining – Problems – Branching – Performance Pipelining

Example • Pipelining is not always efficient. Sometimes an instruction depends on its previous instruction’s results. – Implement the pipeline for the following: srl %r 3, %r 5 addcc %r 1, 10, %r 1 ld %r 1, %r 2 subcc %r 2, %r 4 • E. g. , CPUcycle Unit 1 Unit 2 Unit 3 Unit 4 Unit 5 Pipelining © Prem Uppuluri, Derived from Doug Comer

More problems • Another major problem: branch instructions. – E. g. , consider the following program snippet: addcc %r 1, %r 2, %r 3 be done srl %r 1, 10, %r 1 ba done 2 done: sll %r 1, 10, %r 1 done 2: halt. Can you see why the instructions cannot execute in 1 cpu cycle…draw the pipeline diagram Pipelining

Branches • Branch instructions thus cause the pipeline to be flushed. • Usually, after a branch a bunch of NOPs (no operations) are filled. • Similar problem with load (ld) and store (st). Since these instructions access the memory (which is slow to access), they need additional cycles (usually 1 additional cycle). Pipelining

Load/store • The extra cycles for load and store are called delayed loads/stores. • Any solutions to the branch problem? – Speculative branches. – One approach: load the next instruction after branch. If however, the branch fails, then undo the damage…. Pipelining

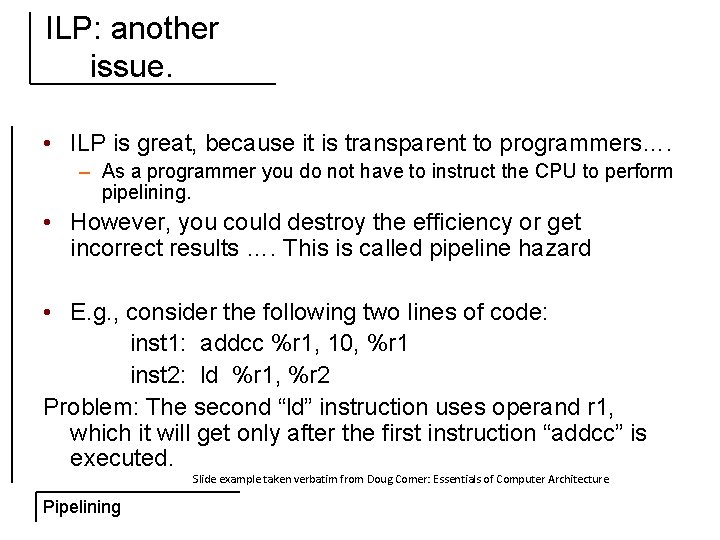

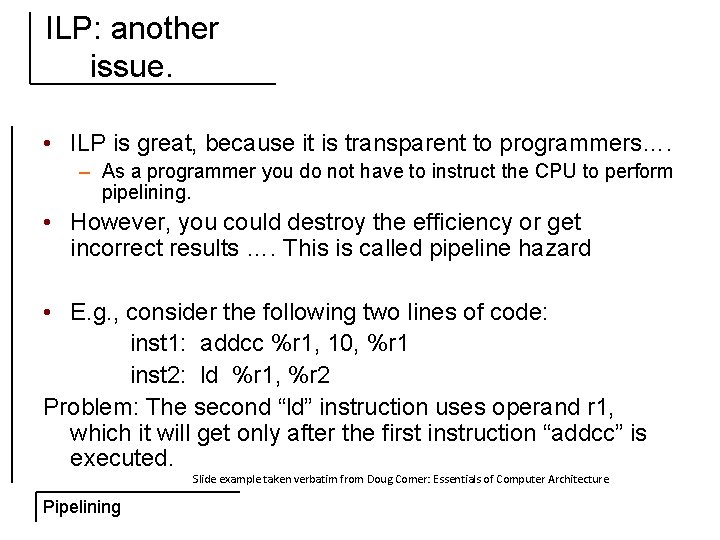

ILP: another issue. • ILP is great, because it is transparent to programmers…. – As a programmer you do not have to instruct the CPU to perform pipelining. • However, you could destroy the efficiency or get incorrect results …. This is called pipeline hazard • E. g. , consider the following two lines of code: inst 1: addcc %r 1, 10, %r 1 inst 2: ld %r 1, %r 2 Can you see any problems with these two instructions in a pipleline? Slide example taken verbatim from Doug Comer: Essentials of Computer Architecture Pipelining

ILP: another issue. • ILP is great, because it is transparent to programmers…. – As a programmer you do not have to instruct the CPU to perform pipelining. • However, you could destroy the efficiency or get incorrect results …. This is called pipeline hazard • E. g. , consider the following two lines of code: inst 1: addcc %r 1, 10, %r 1 inst 2: ld %r 1, %r 2 Problem: The second “ld” instruction uses operand r 1, which it will get only after the first instruction “addcc” is executed. Slide example taken verbatim from Doug Comer: Essentials of Computer Architecture Pipelining

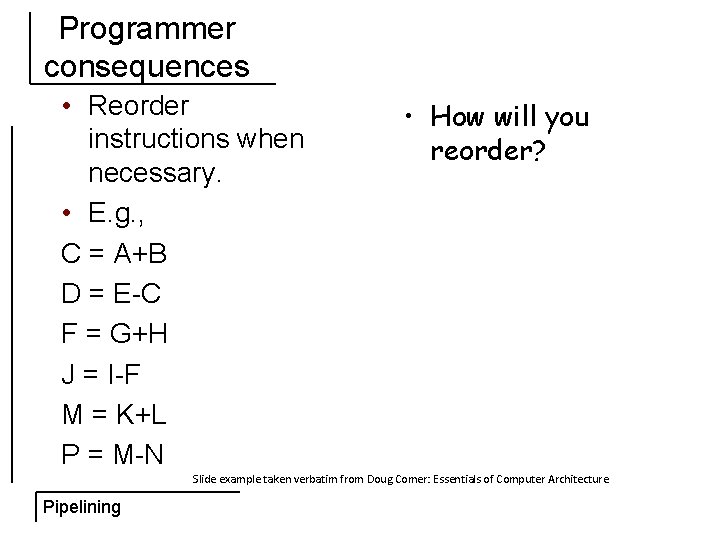

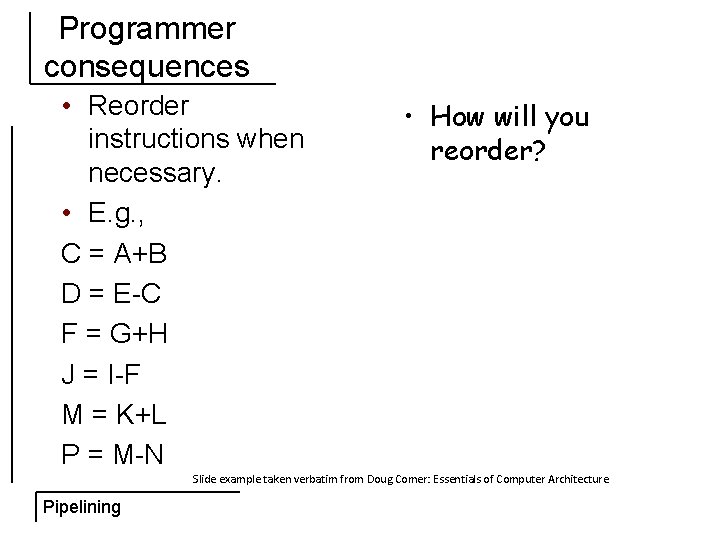

Programmer consequences • Reorder instructions when necessary. • E. g. , C = A+B D = E-C F = G+H J = I-F M = K+L P = M-N • How will you reorder? Slide example taken verbatim from Doug Comer: Essentials of Computer Architecture Pipelining

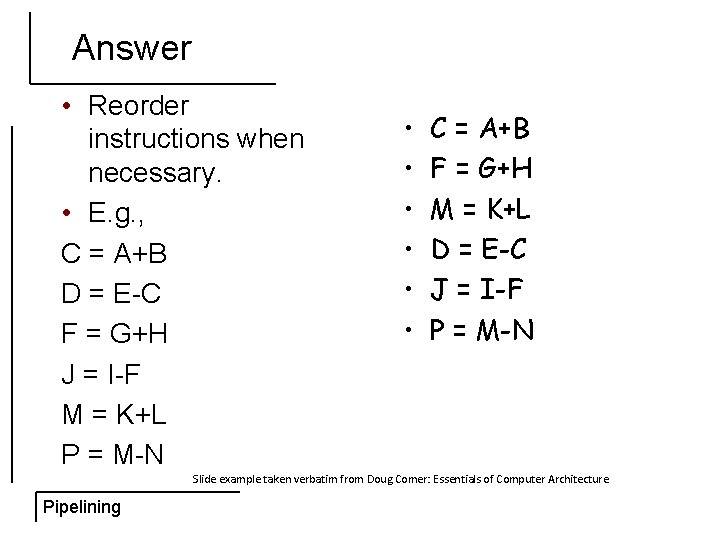

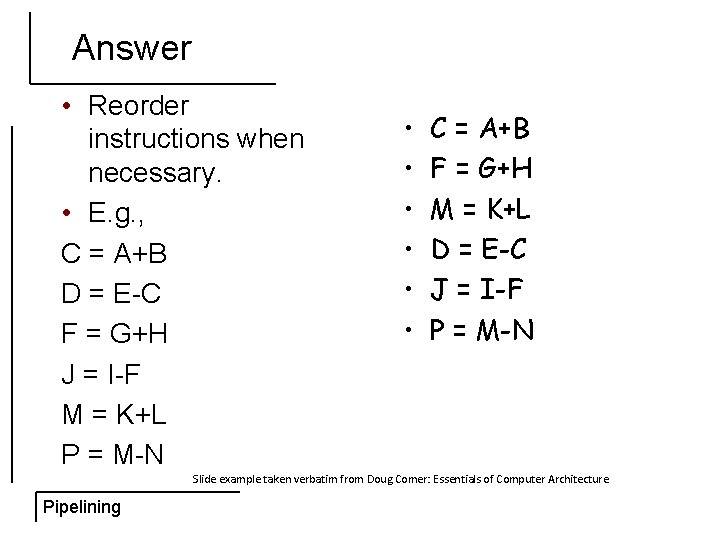

Answer • Reorder instructions when necessary. • E. g. , C = A+B D = E-C F = G+H J = I-F M = K+L P = M-N • • • C = A+B F = G+H M = K+L D = E-C J = I-F P = M-N Slide example taken verbatim from Doug Comer: Essentials of Computer Architecture Pipelining

Pipeline efficiency • Efficiency of a pipeline is given by a value: CPIavg = average cycles per instruction. • Ideally, CPIavg = 1. Why? – We want to execute one instruction per one clock cycle. • What if a branch is taken? Pipelining

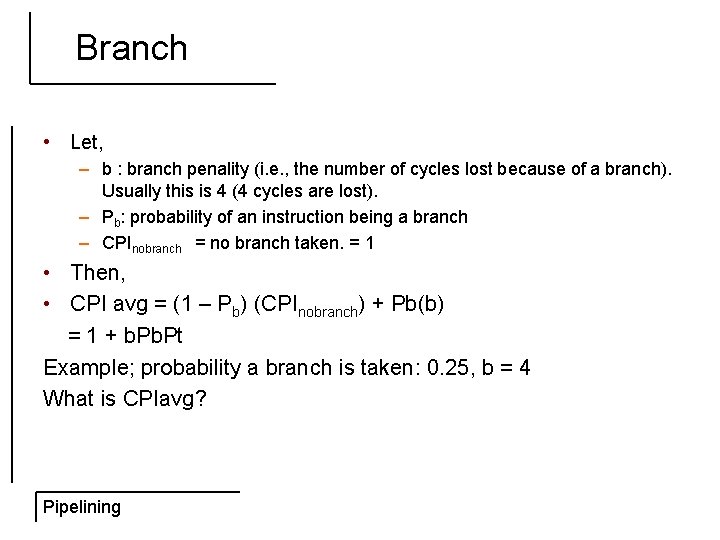

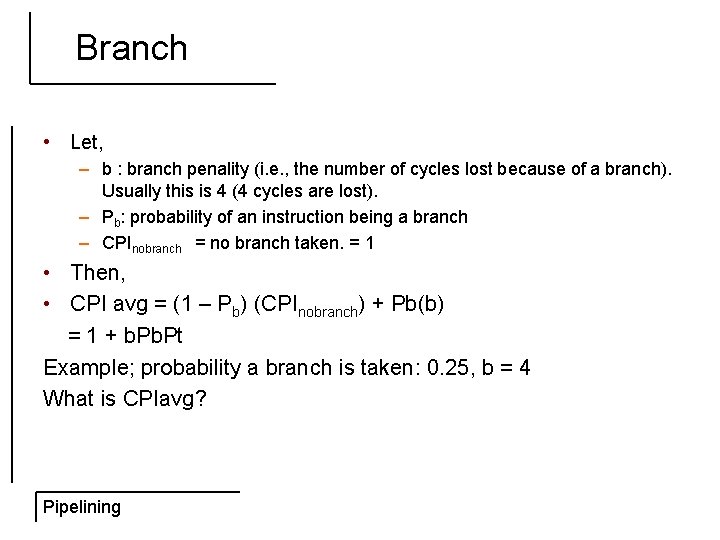

Branch • Let, – b : branch penality (i. e. , the number of cycles lost because of a branch). Usually this is 4 (4 cycles are lost). – Pb: probability of an instruction being a branch – CPInobranch = no branch taken. = 1 • Then, • CPI avg = (1 – Pb) (CPInobranch) + Pb(b) = 1 + b. Pt Example; probability a branch is taken: 0. 25, b = 4 What is CPIavg? Pipelining

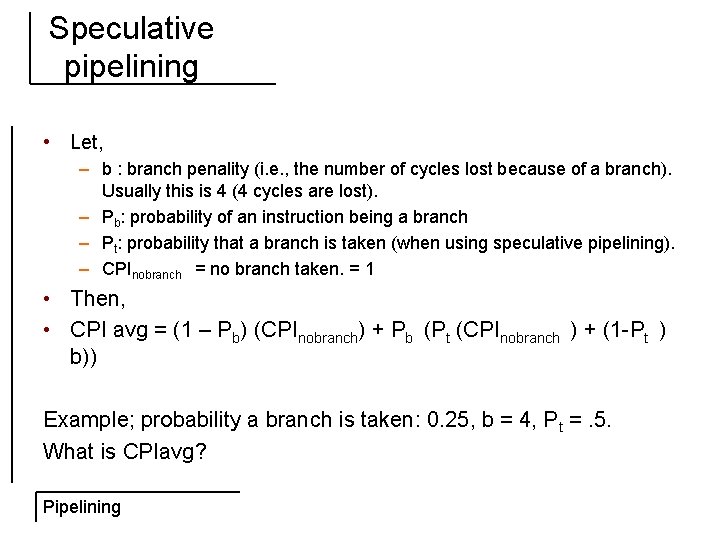

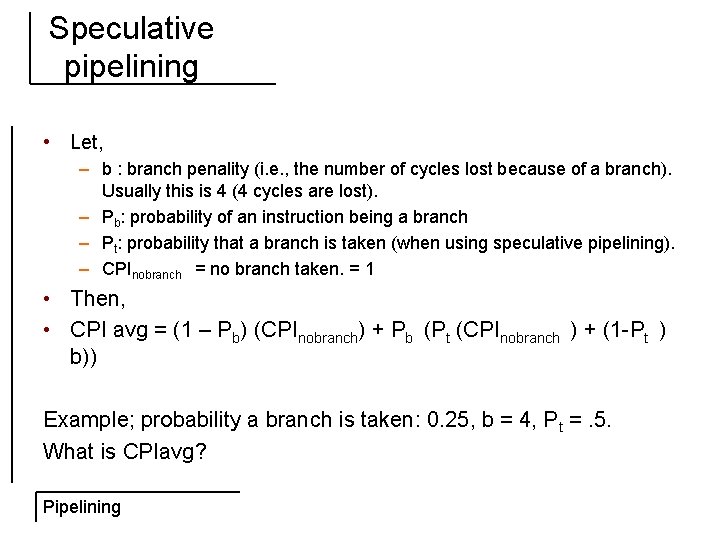

Speculative pipelining • Let, – b : branch penality (i. e. , the number of cycles lost because of a branch). Usually this is 4 (4 cycles are lost). – Pb: probability of an instruction being a branch – Pt: probability that a branch is taken (when using speculative pipelining). – CPInobranch = no branch taken. = 1 • Then, • CPI avg = (1 – Pb) (CPInobranch) + Pb (Pt (CPInobranch ) + (1 -Pt ) b)) Example; probability a branch is taken: 0. 25, b = 4, Pt =. 5. What is CPIavg? Pipelining

Execution Efficiency • Any processors execution efficiency is given as the ratio of CPInobranch/CPI avg. Pipelining

Next … • We are done with Assembly. – Next: • Memory (Chapter 7) Pipelining

Review • Pipelining