Faculty of Computer Science The Instruction Set Architecture

- Slides: 20

Faculty of Computer Science The Instruction Set Architecture Registers, Addressing Modes, and Instructions Add footer here 12/22/2021 © 2006

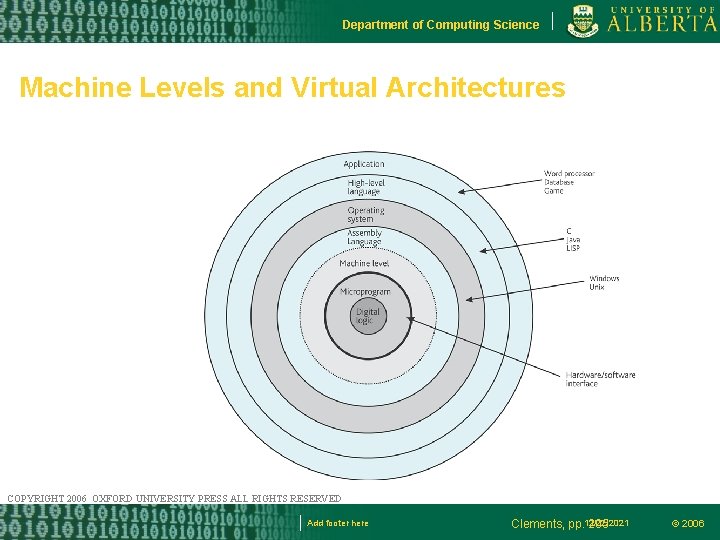

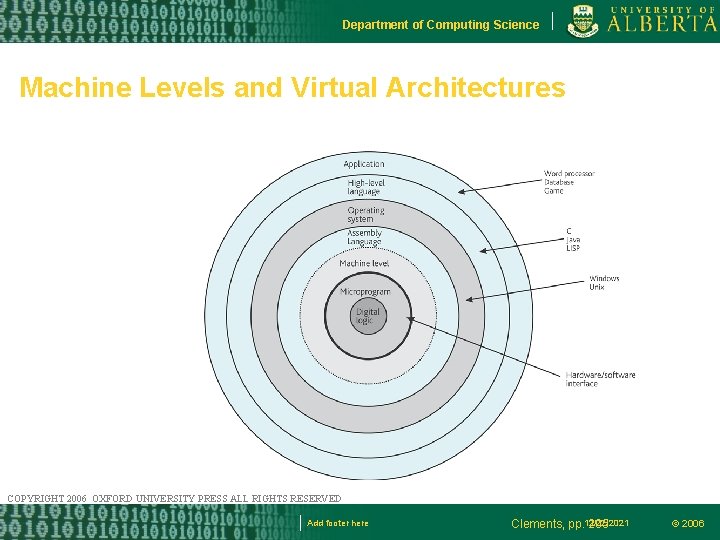

Department of Computing Science Machine Levels and Virtual Architectures COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 12/22/2021 205 © 2006

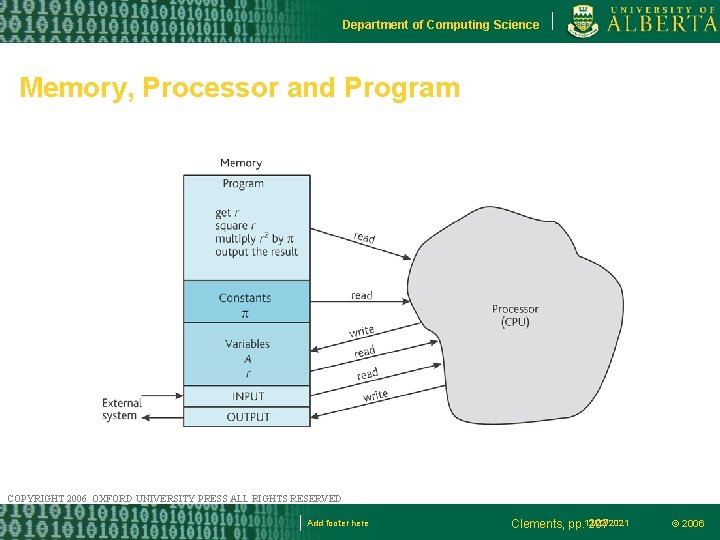

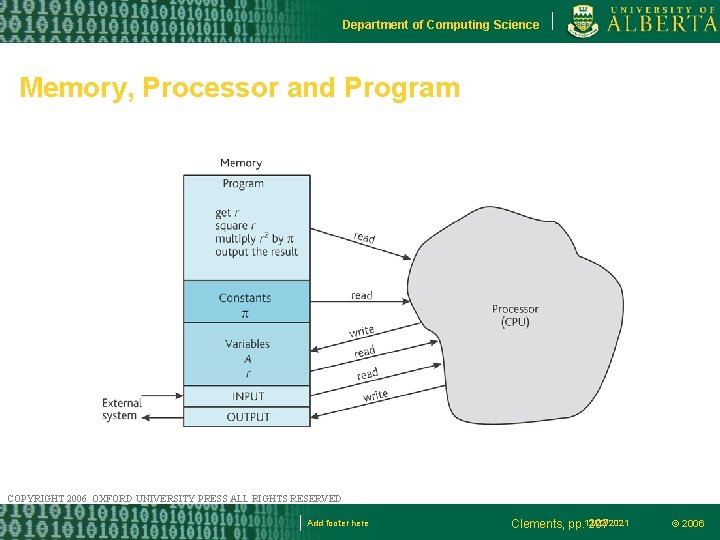

Department of Computing Science Memory, Processor and Program COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 12/22/2021 207 © 2006

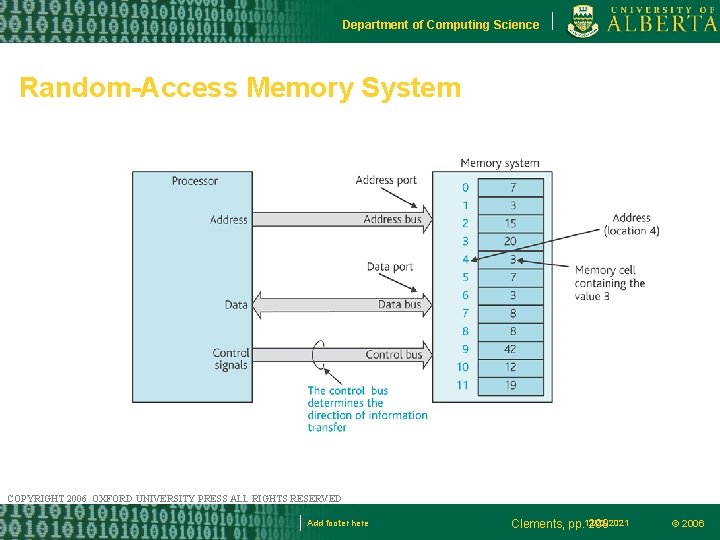

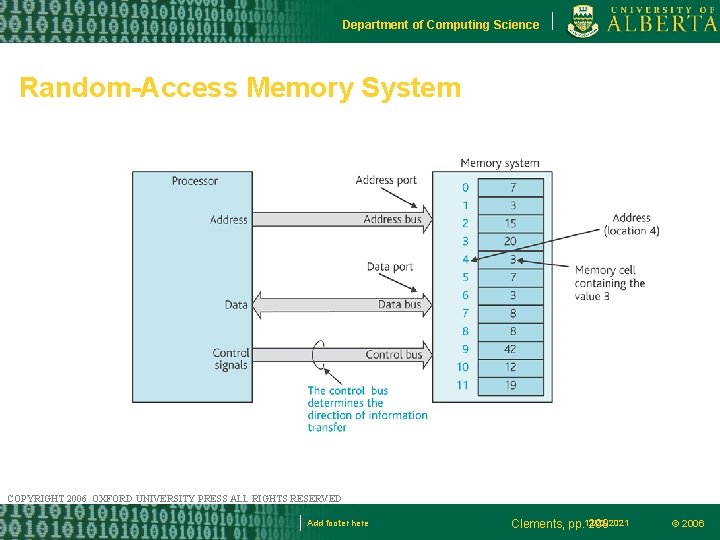

Department of Computing Science Random-Access Memory System COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 12/22/2021 208 © 2006

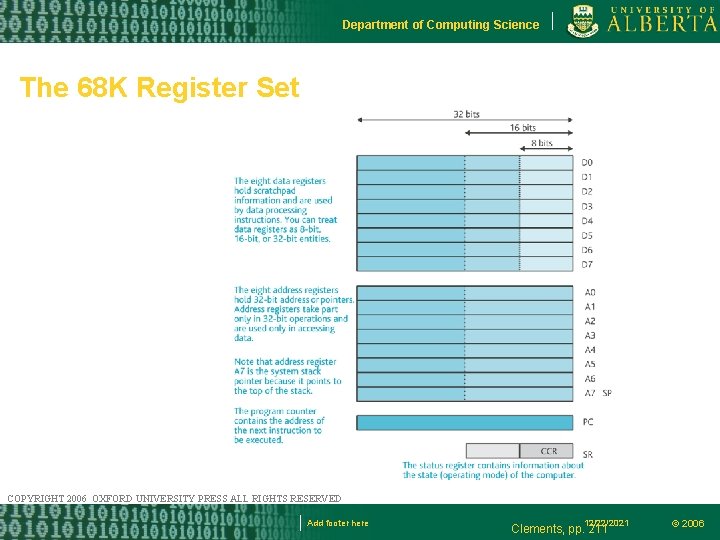

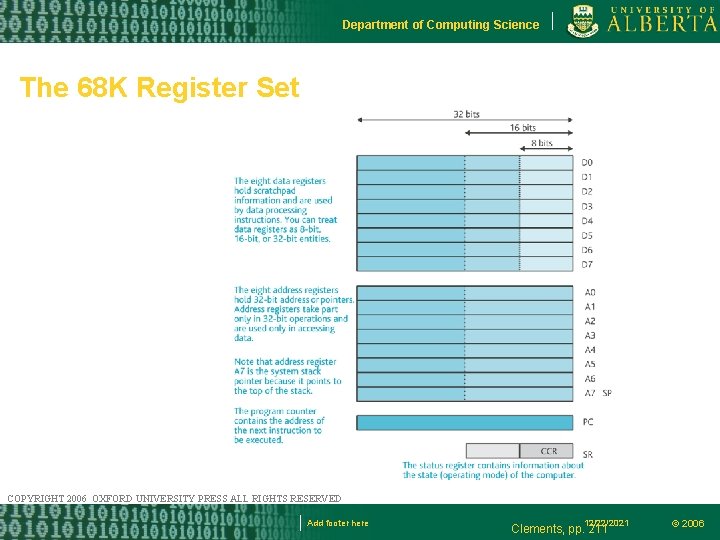

Department of Computing Science The 68 K Register Set COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here 12/22/2021 Clements, pp. 211 © 2006

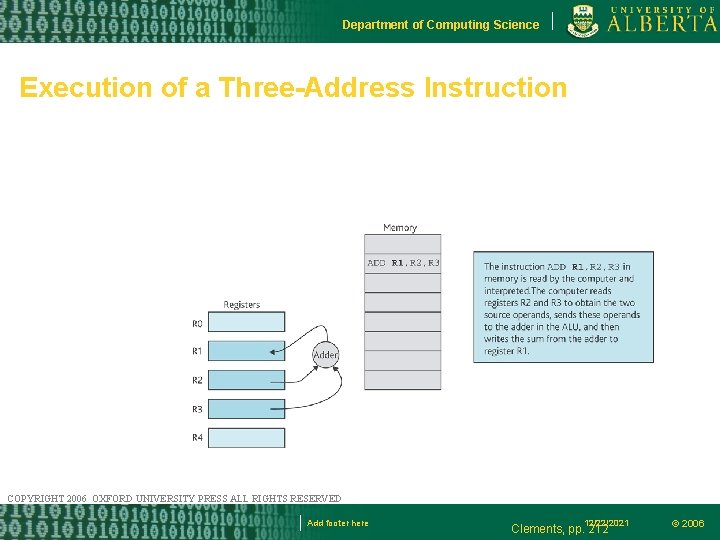

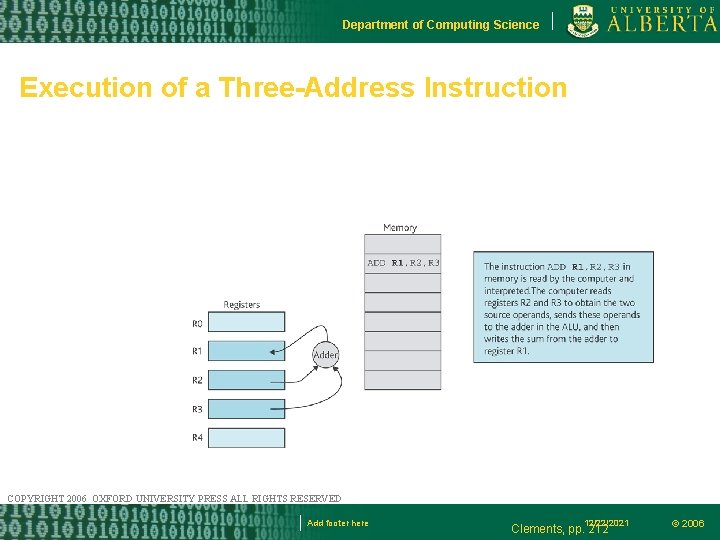

Department of Computing Science Execution of a Three-Address Instruction COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here 12/22/2021 Clements, pp. 212 © 2006

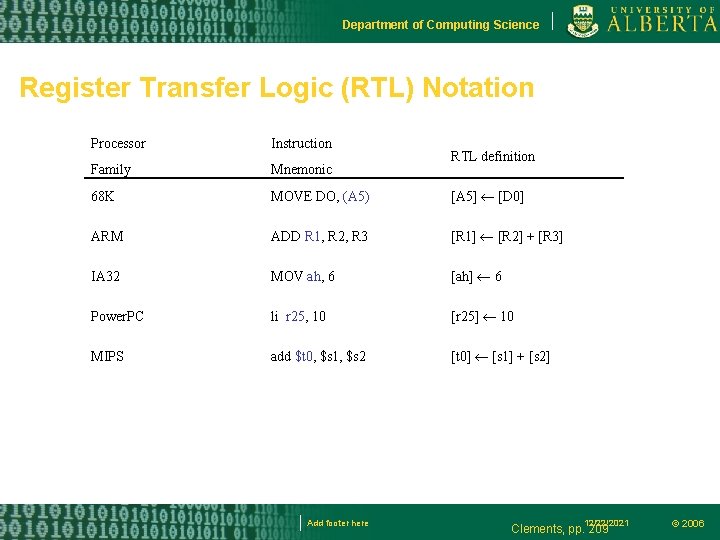

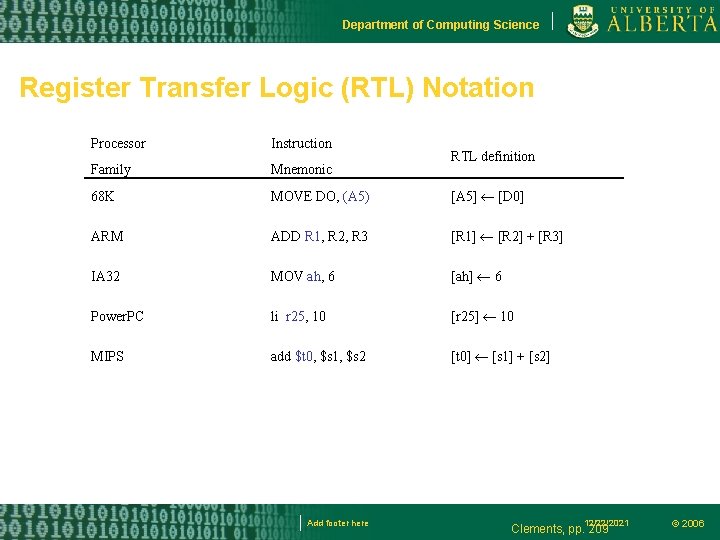

Department of Computing Science Register Transfer Logic (RTL) Notation Processor Instruction Family Mnemonic 68 K MOVE DO, (A 5) [A 5] [D 0] ARM ADD R 1, R 2, R 3 [R 1] [R 2] + [R 3] IA 32 MOV ah, 6 [ah] 6 Power. PC li r 25, 10 [r 25] 10 MIPS add $t 0, $s 1, $s 2 [t 0] [s 1] + [s 2] Add footer here RTL definition 12/22/2021 Clements, pp. 209 © 2006

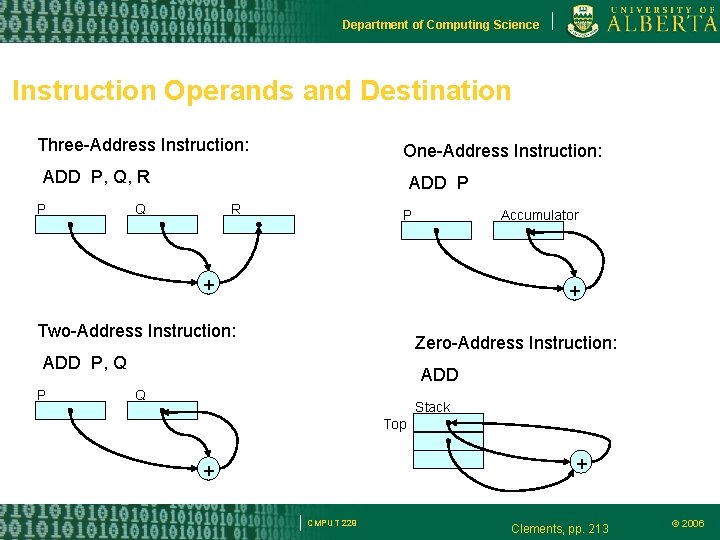

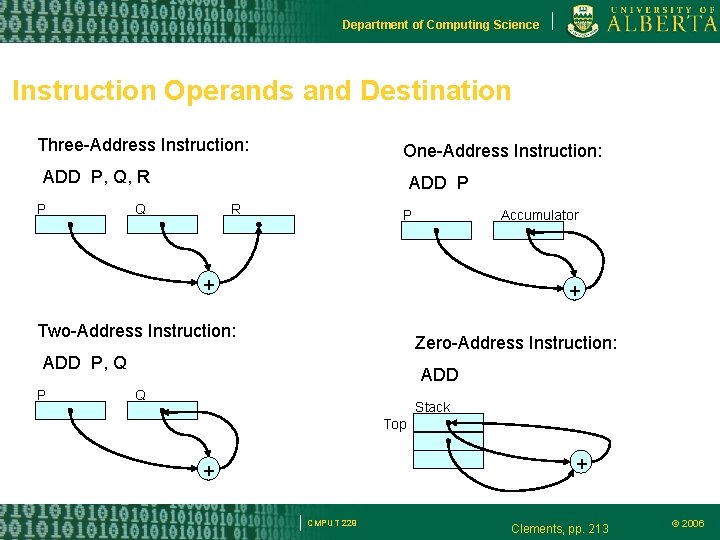

Department of Computing Science Instruction Operands and Destination Three-Address Instruction: One-Address Instruction: ADD P, Q, R P ADD P Q R P Accumulator + + Two-Address Instruction: Zero-Address Instruction: ADD P, Q P ADD Q Stack Top + + CMPUT 229 Clements, pp. 213 © 2006

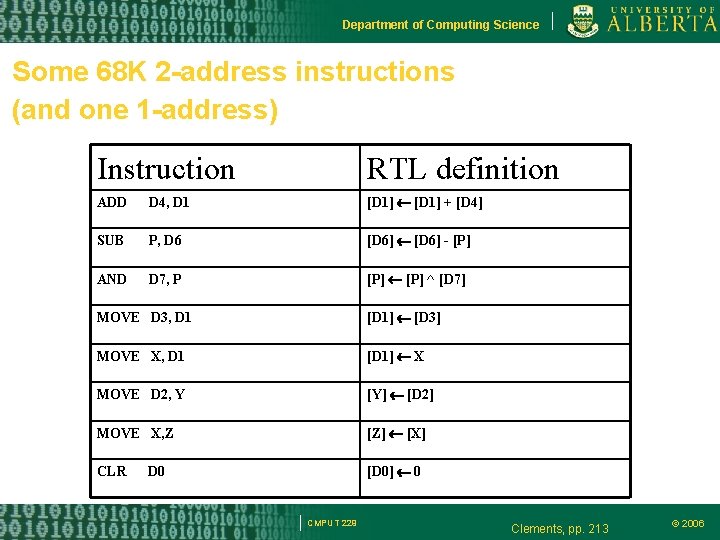

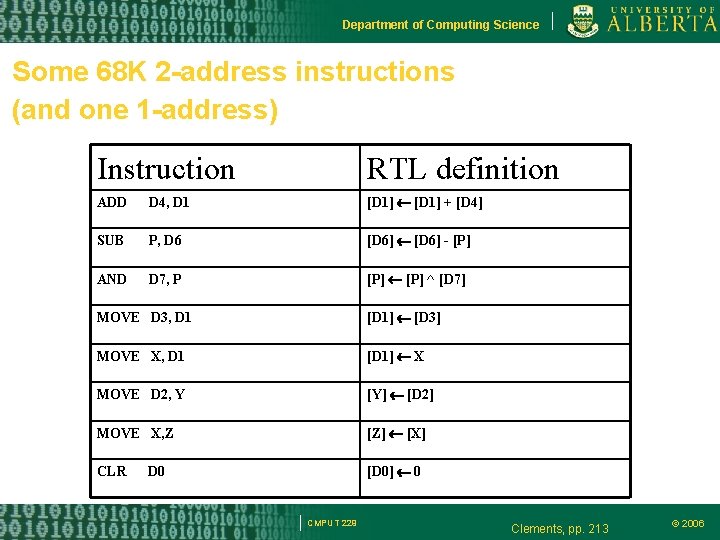

Department of Computing Science Some 68 K 2 -address instructions (and one 1 -address) Instruction RTL definition ADD D 4, D 1 [D 1] + [D 4] SUB P, D 6 [D 6] - [P] AND D 7, P [P] ^ [D 7] MOVE D 3, D 1 [D 1] [D 3] MOVE X, D 1 [D 1] X MOVE D 2, Y [Y] [D 2] MOVE X, Z [Z] [X] CLR [D 0] 0 D 0 CMPUT 229 Clements, pp. 213 © 2006

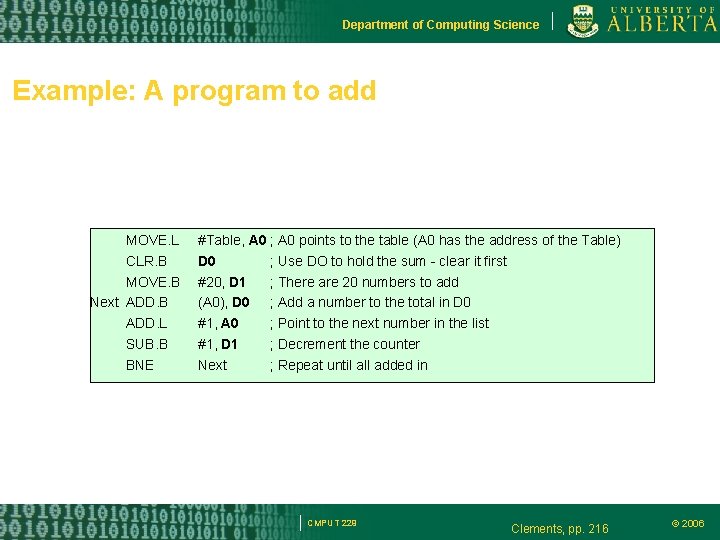

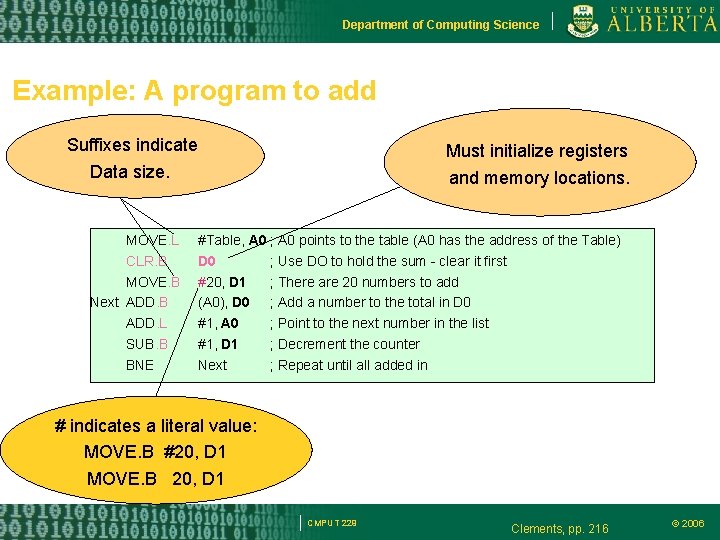

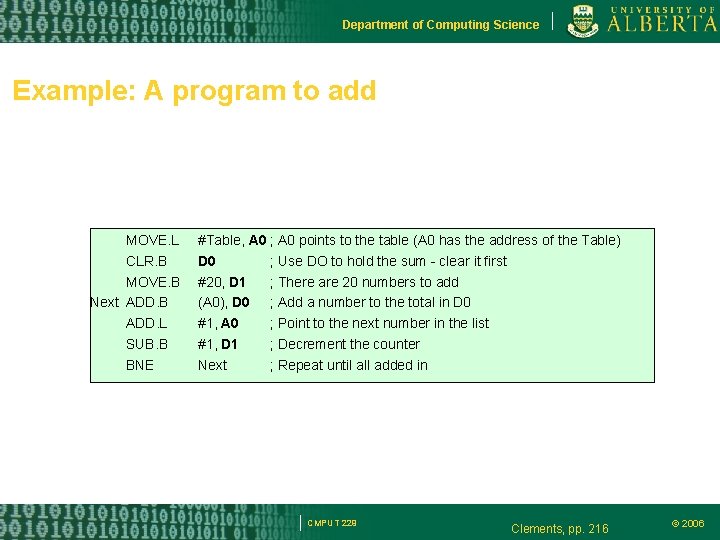

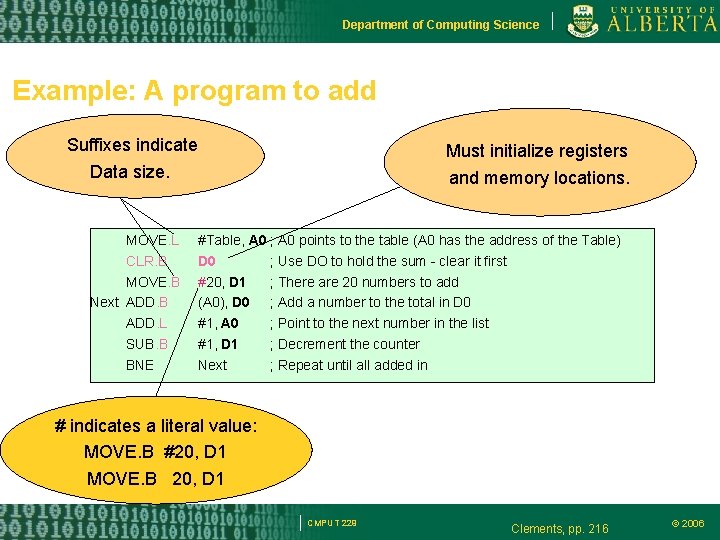

Department of Computing Science Example: A program to add MOVE. L CLR. B MOVE. B Next ADD. B ADD. L SUB. B BNE #Table, A 0 ; A 0 points to the table (A 0 has the address of the Table) D 0 ; Use DO to hold the sum - clear it first #20, D 1 ; There are 20 numbers to add (A 0), D 0 ; Add a number to the total in D 0 #1, A 0 ; Point to the next number in the list #1, D 1 ; Decrement the counter Next ; Repeat until all added in CMPUT 229 Clements, pp. 216 © 2006

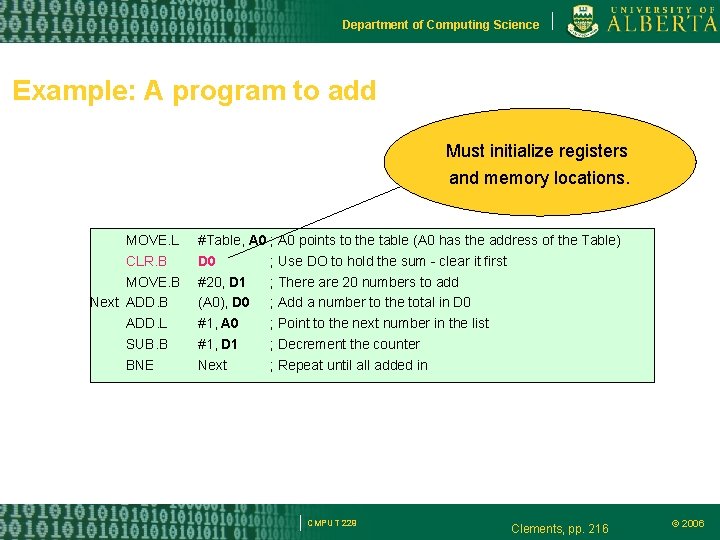

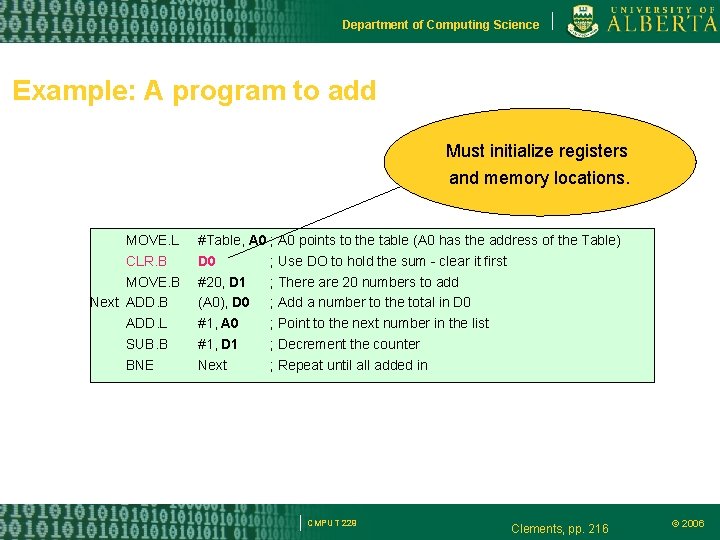

Department of Computing Science Example: A program to add Must initialize registers and memory locations. MOVE. L CLR. B MOVE. B Next ADD. B ADD. L SUB. B BNE #Table, A 0 ; A 0 points to the table (A 0 has the address of the Table) D 0 ; Use DO to hold the sum - clear it first #20, D 1 ; There are 20 numbers to add (A 0), D 0 ; Add a number to the total in D 0 #1, A 0 ; Point to the next number in the list #1, D 1 ; Decrement the counter Next ; Repeat until all added in CMPUT 229 Clements, pp. 216 © 2006

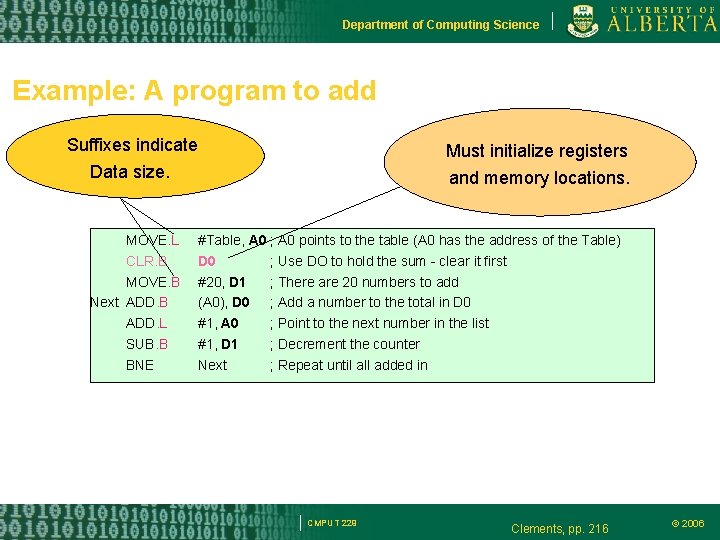

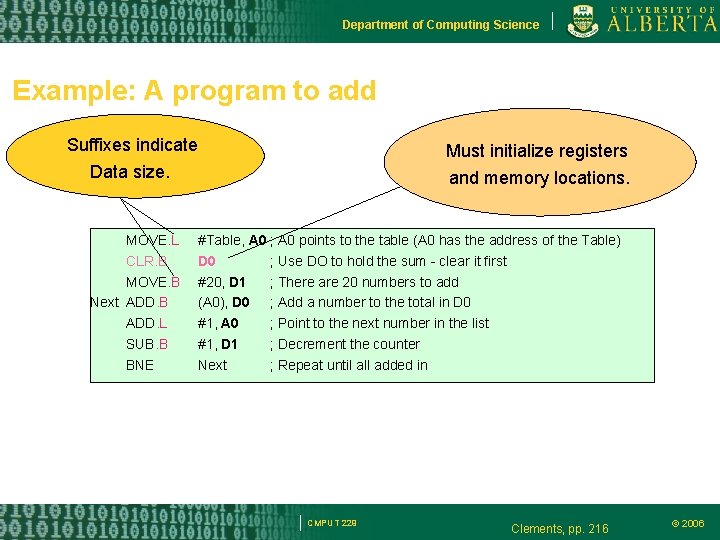

Department of Computing Science Example: A program to add Suffixes indicate Data size. MOVE. L CLR. B MOVE. B Next ADD. B ADD. L SUB. B BNE Must initialize registers and memory locations. #Table, A 0 ; A 0 points to the table (A 0 has the address of the Table) D 0 ; Use DO to hold the sum - clear it first #20, D 1 ; There are 20 numbers to add (A 0), D 0 ; Add a number to the total in D 0 #1, A 0 ; Point to the next number in the list #1, D 1 ; Decrement the counter Next ; Repeat until all added in CMPUT 229 Clements, pp. 216 © 2006

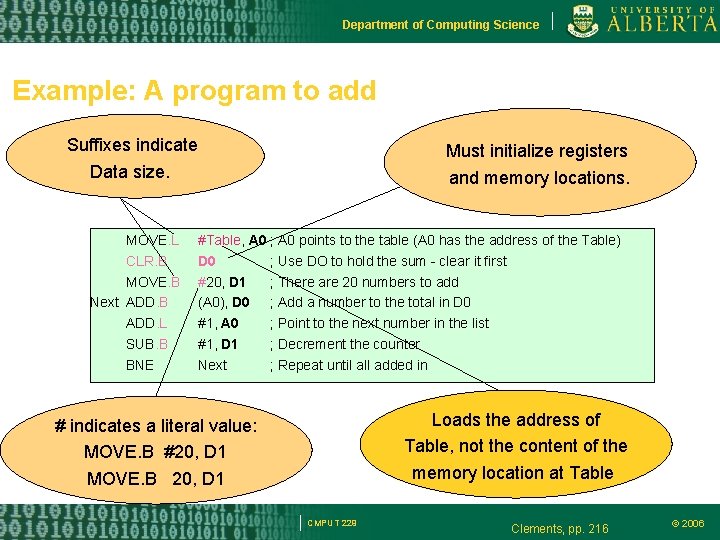

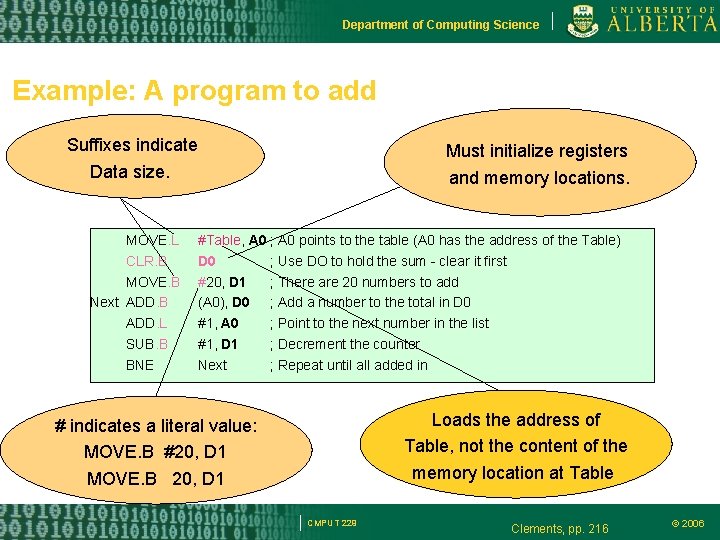

Department of Computing Science Example: A program to add Suffixes indicate Data size. MOVE. L CLR. B MOVE. B Next ADD. B ADD. L SUB. B BNE Must initialize registers and memory locations. #Table, A 0 ; A 0 points to the table (A 0 has the address of the Table) D 0 ; Use DO to hold the sum - clear it first #20, D 1 ; There are 20 numbers to add (A 0), D 0 ; Add a number to the total in D 0 #1, A 0 ; Point to the next number in the list #1, D 1 ; Decrement the counter Next ; Repeat until all added in # indicates a literal value: MOVE. B #20, D 1 MOVE. B 20, D 1 CMPUT 229 Clements, pp. 216 © 2006

Department of Computing Science Example: A program to add Suffixes indicate Data size. MOVE. L CLR. B MOVE. B Next ADD. B ADD. L SUB. B BNE Must initialize registers and memory locations. #Table, A 0 ; A 0 points to the table (A 0 has the address of the Table) D 0 ; Use DO to hold the sum - clear it first #20, D 1 ; There are 20 numbers to add (A 0), D 0 ; Add a number to the total in D 0 #1, A 0 ; Point to the next number in the list #1, D 1 ; Decrement the counter Next ; Repeat until all added in Loads the address of Table, not the content of the memory location at Table # indicates a literal value: MOVE. B #20, D 1 MOVE. B 20, D 1 CMPUT 229 Clements, pp. 216 © 2006

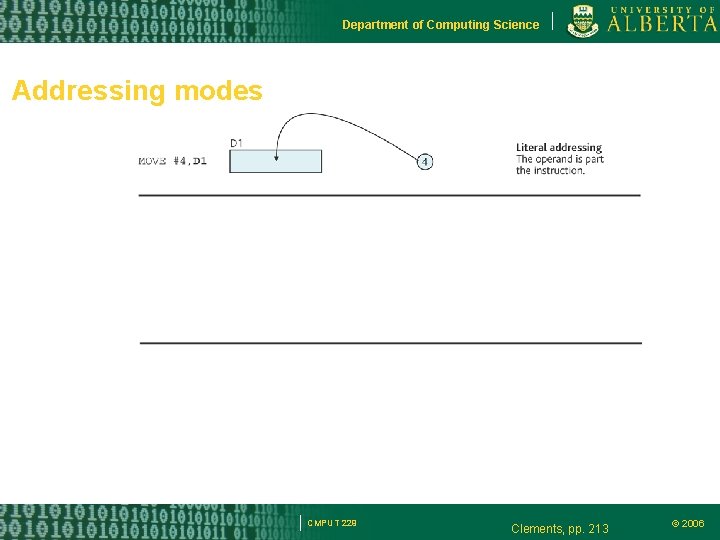

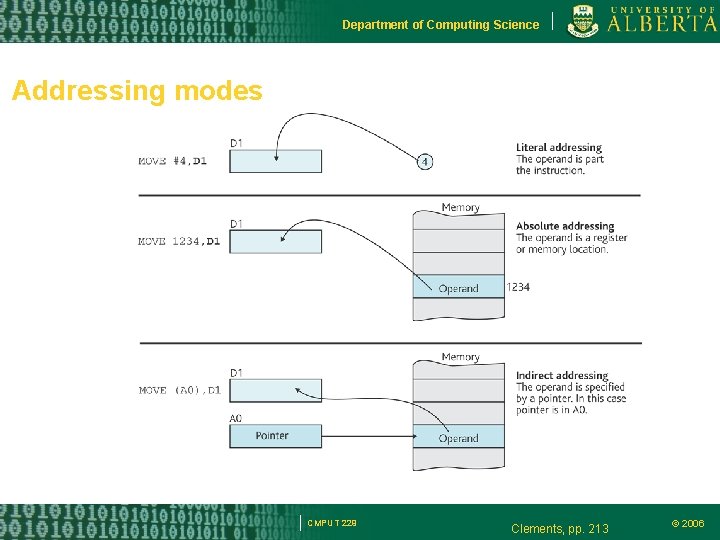

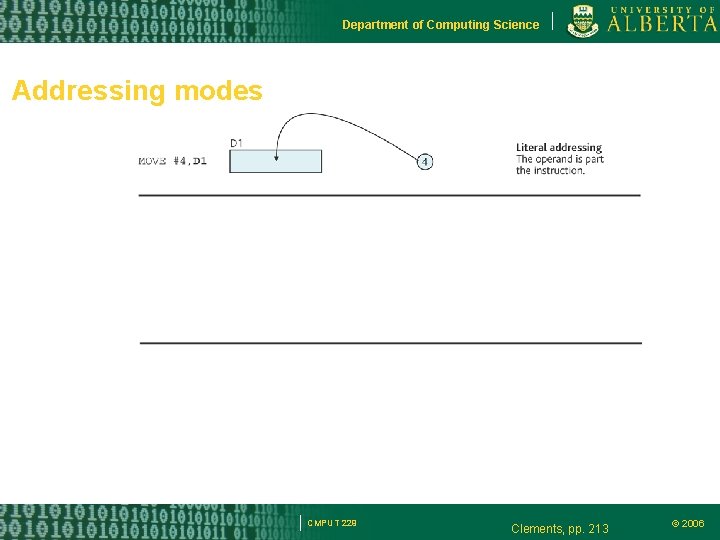

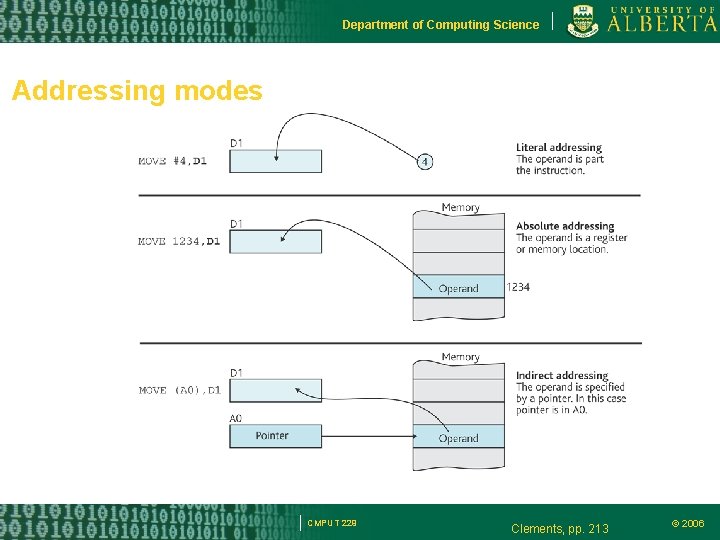

Department of Computing Science Addressing modes CMPUT 229 Clements, pp. 213 © 2006

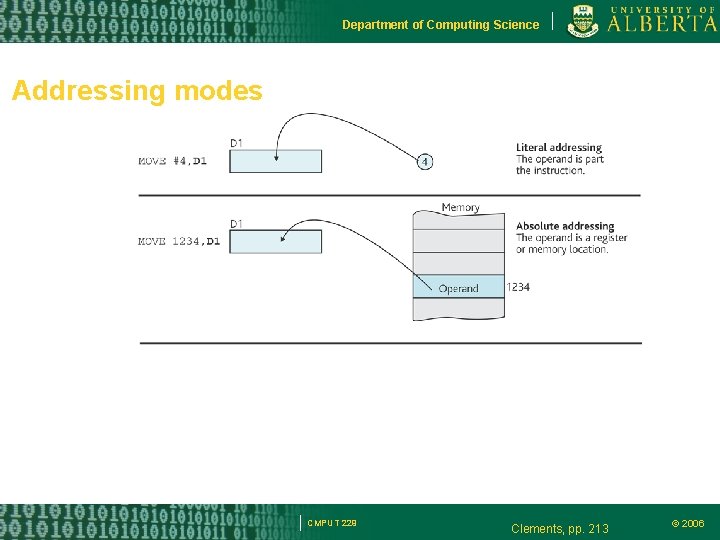

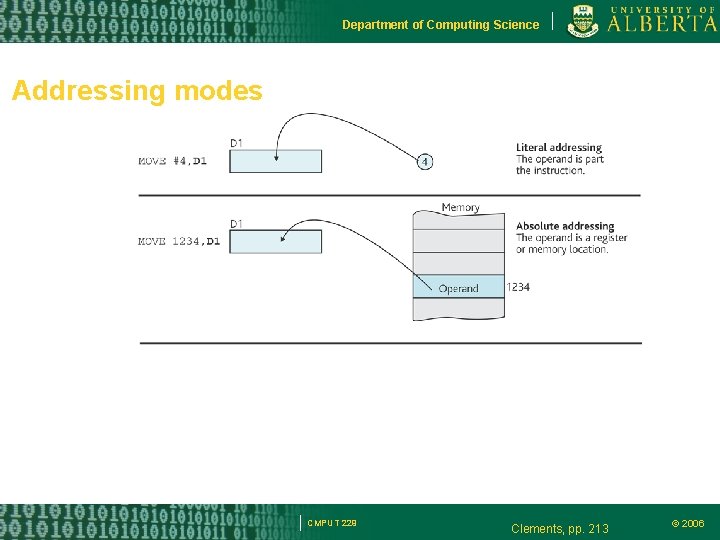

Department of Computing Science Addressing modes CMPUT 229 Clements, pp. 213 © 2006

Department of Computing Science Addressing modes CMPUT 229 Clements, pp. 213 © 2006

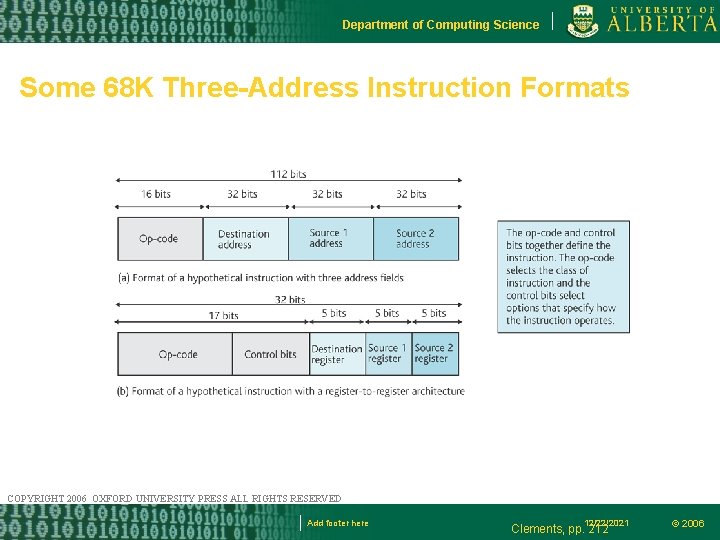

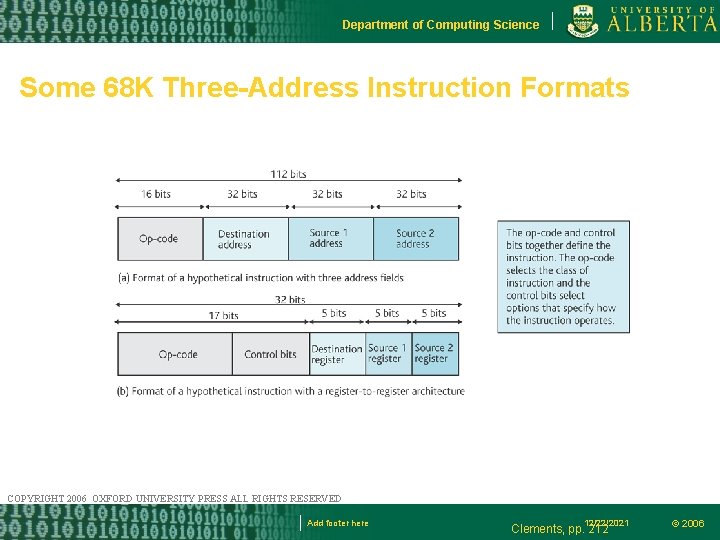

Department of Computing Science Some 68 K Three-Address Instruction Formats COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here 12/22/2021 Clements, pp. 212 © 2006

Department of Computing Science Overview of the 68 K’s instructions Instruction Categories: – Data movement – Arithmetic – Logical – Shift – Bit – Compare – Control CMPUT 229 © 2006

Department of Computing Science Status Register Status bits: Z-bit: Set if the result is zero N-bit: Set if the result is negative C-bit: Set if the result yields a carry-out V-bit: Set if the result is out of range (overflow) CMPUT 229 © 2006