Embedded System Spring 2011 Lecture 11 Bank Switching

Embedded System Spring, 2011 Lecture 11: Bank Switching Eng. Wazen M. Shbair

Today’s Lecture o List all addressing modes of PIC 18 u. Cs o Contrast and compare the addressing modes o Code PIC 18 instructions to manipulate a lookup table. o Access fixed data residing in ROM space. IUG- Embedded System 2

Introduction o Data could be in n A register n In memory n Provided as an immediate values o PIC 18 provides 4 addressing modes n n Immediate Direct Register indirect Indexed-ROM 3 6 -3

Immediate and Direct Addressing mode o In immediate addressing mode, the operands comes after the opcode n MOVLW 0 x 25 n SUBLW D’ 34’ n ADDLW 0 x 86 o In direct addressing mode, the operand data is in a RAM location whose address is known and given as a part of the instruction. 4

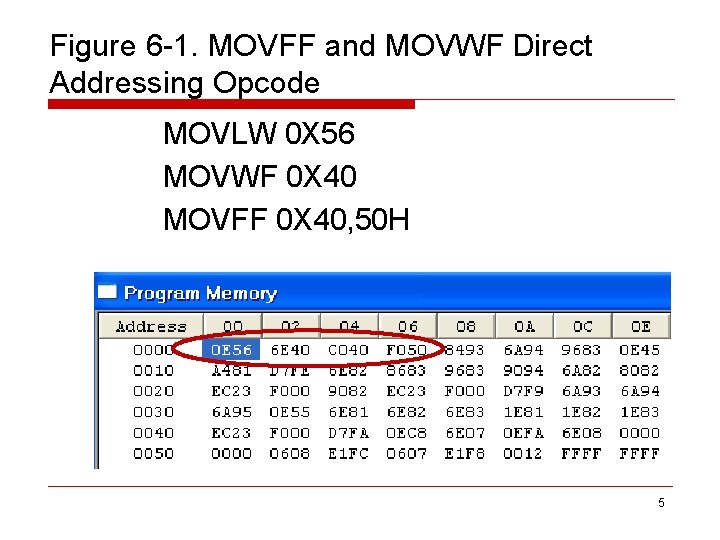

Figure 6 -1. MOVFF and MOVWF Direct Addressing Opcode MOVLW 0 X 56 MOVWF 0 X 40 MOVFF 0 X 40, 50 H 5

Immediate and Direct Addressing mode o What is the difference between n INCF file. Reg, W n INCF file. Reg, F o What is the default destination? o What is the difference between DECFSZ and DECF? n Operation n Branch 6

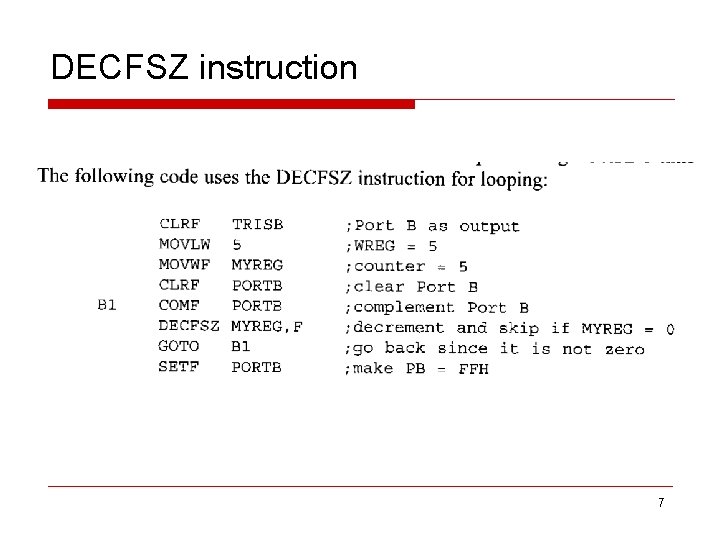

DECFSZ instruction 7

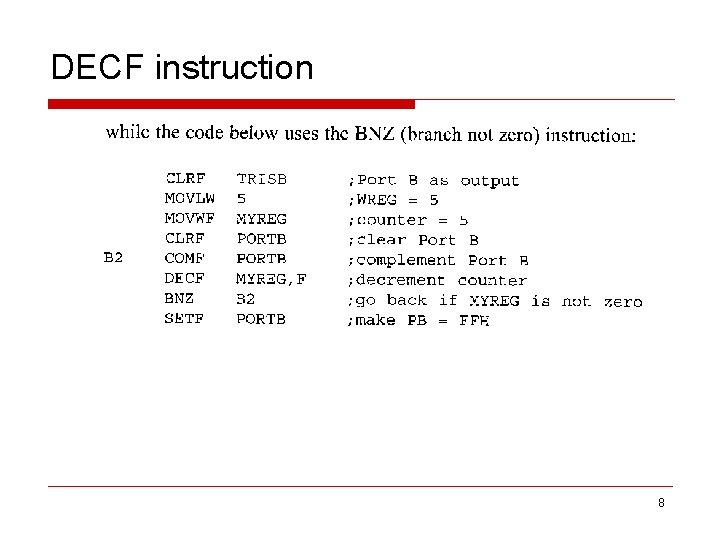

DECF instruction 8

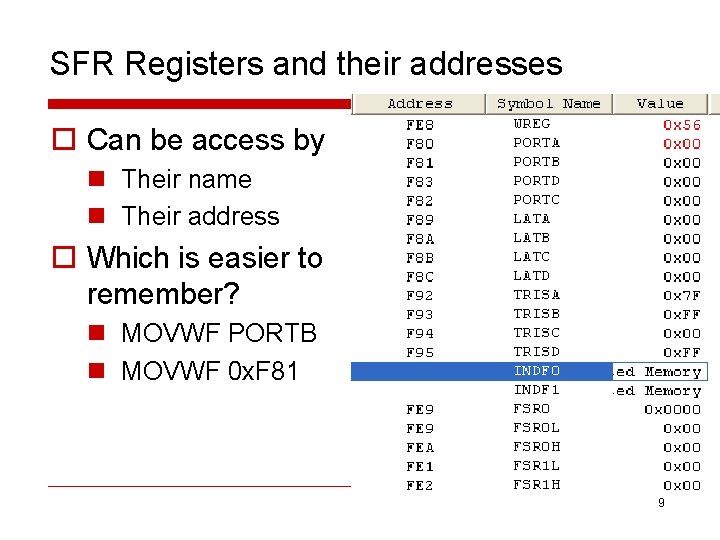

SFR Registers and their addresses o Can be access by n Their name n Their address o Which is easier to remember? n MOVWF PORTB n MOVWF 0 x. F 81 9

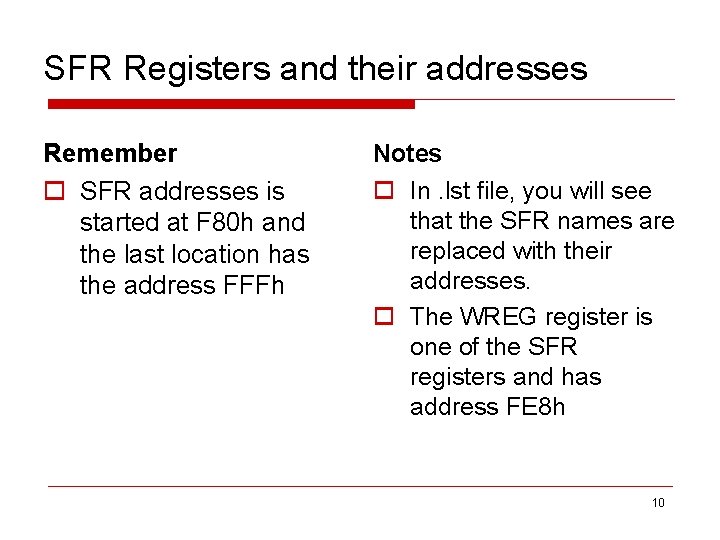

SFR Registers and their addresses Remember o SFR addresses is started at F 80 h and the last location has the address FFFh Notes o In. lst file, you will see that the SFR names are replaced with their addresses. o The WREG register is one of the SFR registers and has address FE 8 h 10

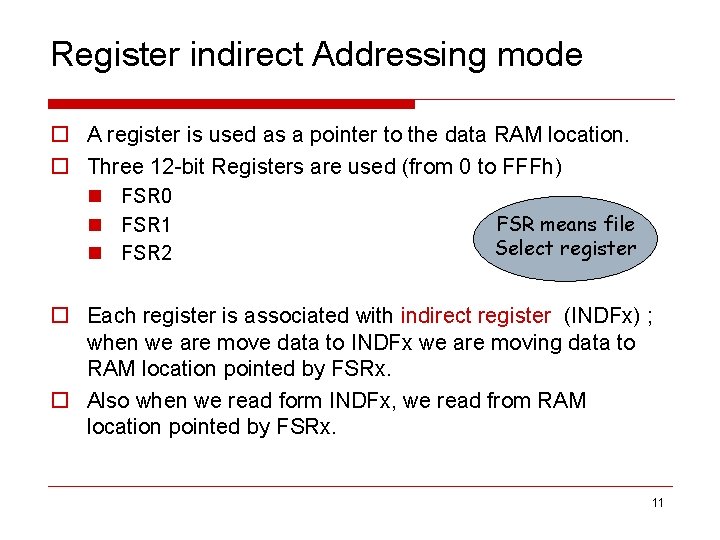

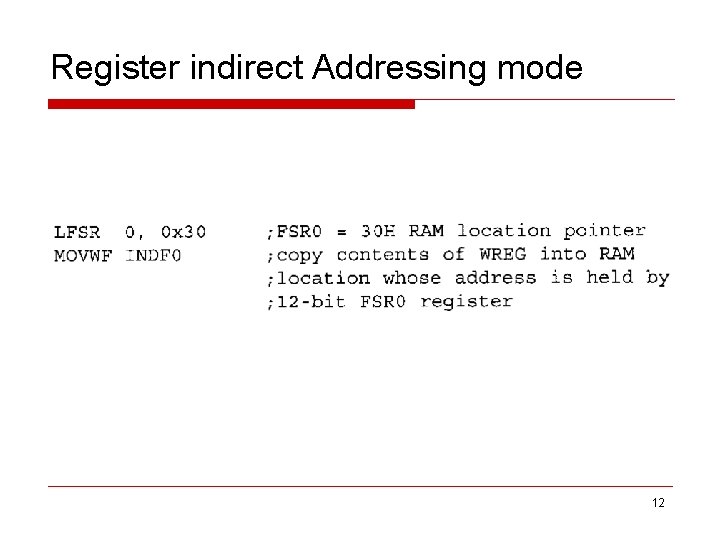

Register indirect Addressing mode o A register is used as a pointer to the data RAM location. o Three 12 -bit Registers are used (from 0 to FFFh) n FSR 0 n FSR 1 n FSR 2 FSR means file Select register o Each register is associated with indirect register (INDFx) ; when we are move data to INDFx we are moving data to RAM location pointed by FSRx. o Also when we read form INDFx, we read from RAM location pointed by FSRx. 11

Register indirect Addressing mode 12

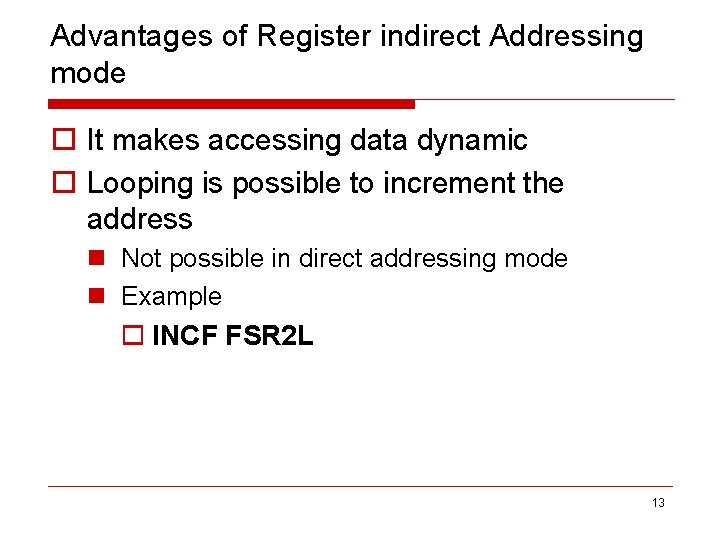

Advantages of Register indirect Addressing mode o It makes accessing data dynamic o Looping is possible to increment the address n Not possible in direct addressing mode n Example o INCF FSR 2 L 13

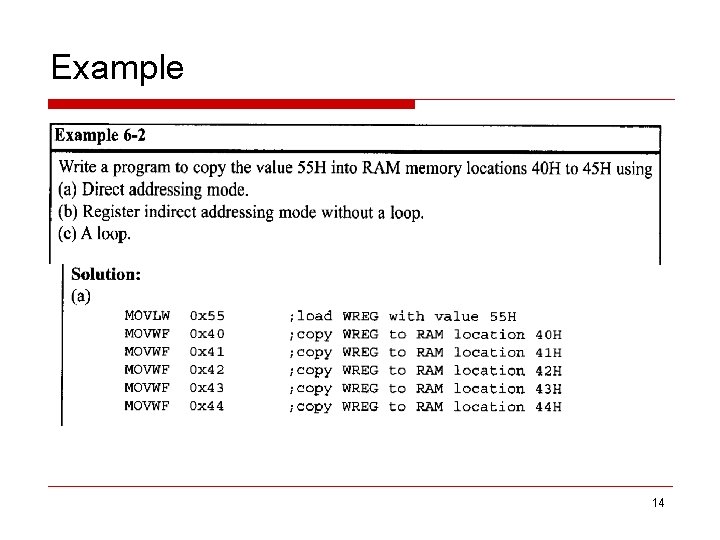

Example 14

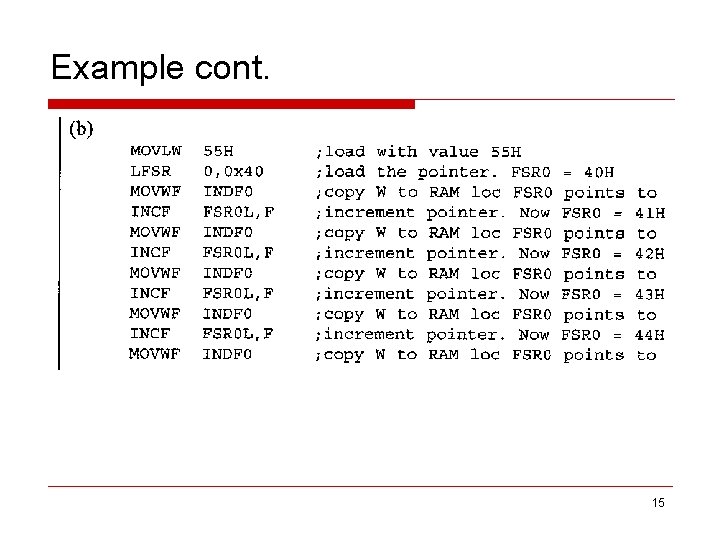

Example cont. 15

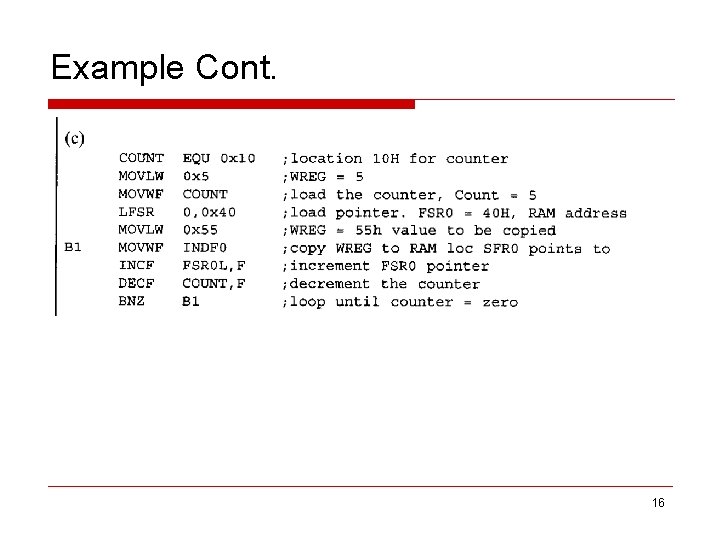

Example Cont. 16

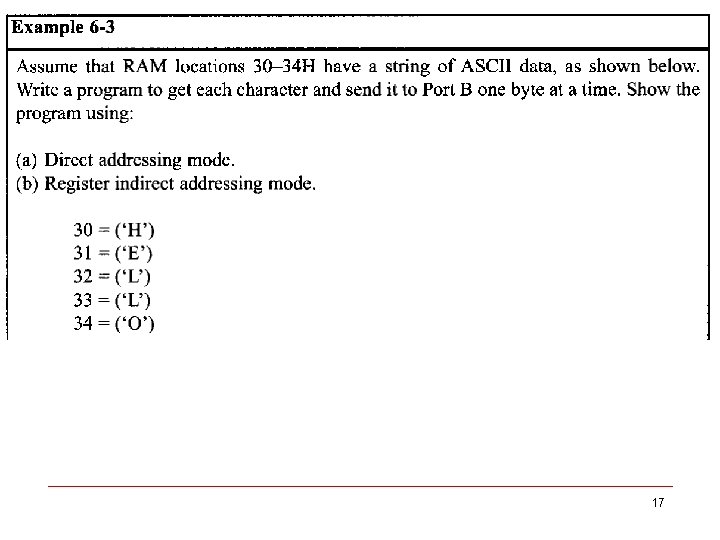

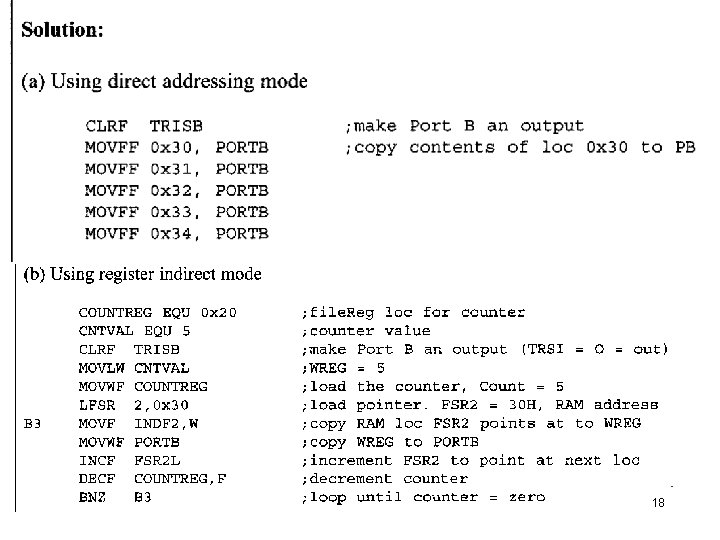

17

18

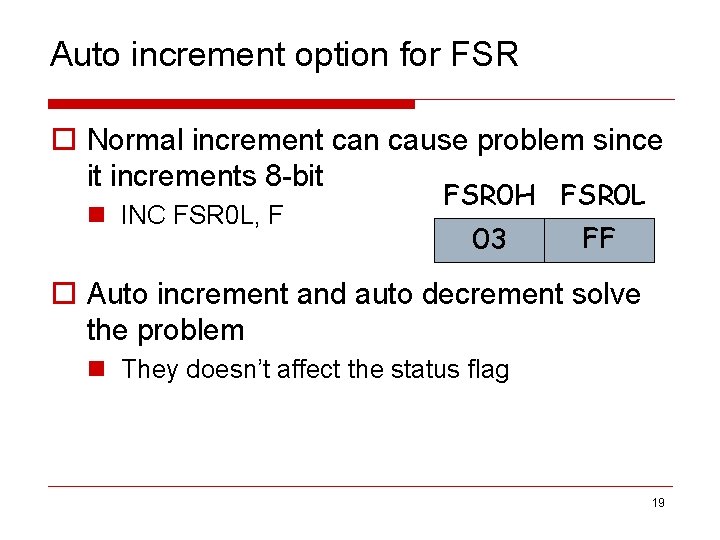

Auto increment option for FSR o Normal increment can cause problem since it increments 8 -bit n INC FSR 0 L, F FSR 0 H FSR 0 L 03 FF o Auto increment and auto decrement solve the problem n They doesn’t affect the status flag 19

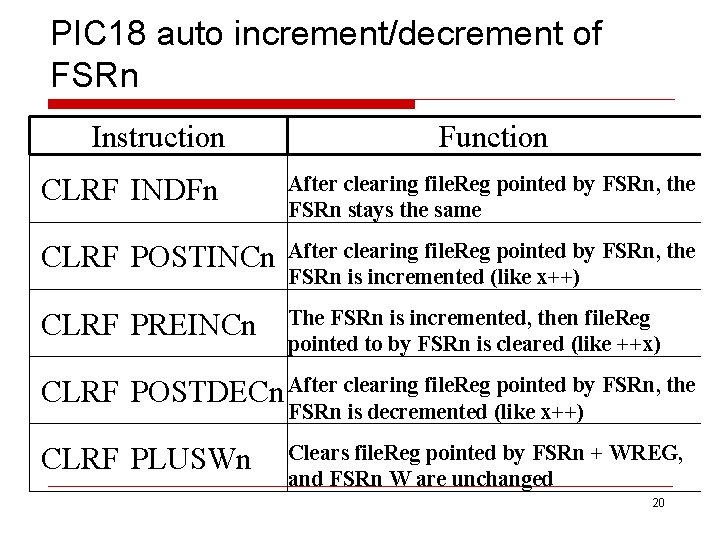

PIC 18 auto increment/decrement of FSRn Instruction Function CLRF INDFn After clearing file. Reg pointed by FSRn, the FSRn stays the same CLRF POSTINCn After clearing file. Reg pointed by FSRn, the FSRn is incremented (like x++) CLRF PREINCn The FSRn is incremented, then file. Reg pointed to by FSRn is cleared (like ++x) CLRF POSTDECn After clearing file. Reg pointed by FSRn, the FSRn is decremented (like x++) CLRF PLUSWn Clears file. Reg pointed by FSRn + WREG, and FSRn W are unchanged 20

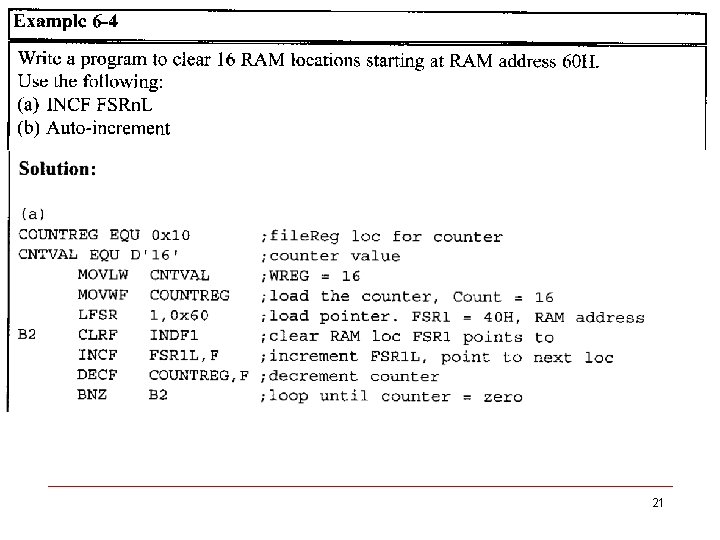

21

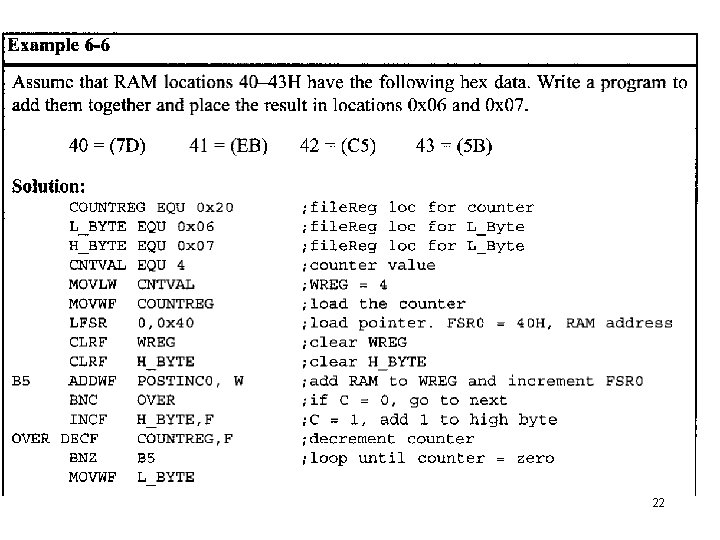

22

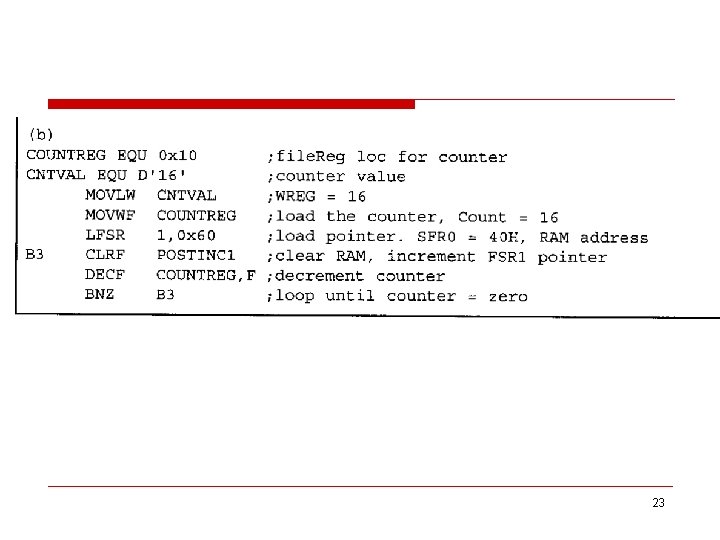

23

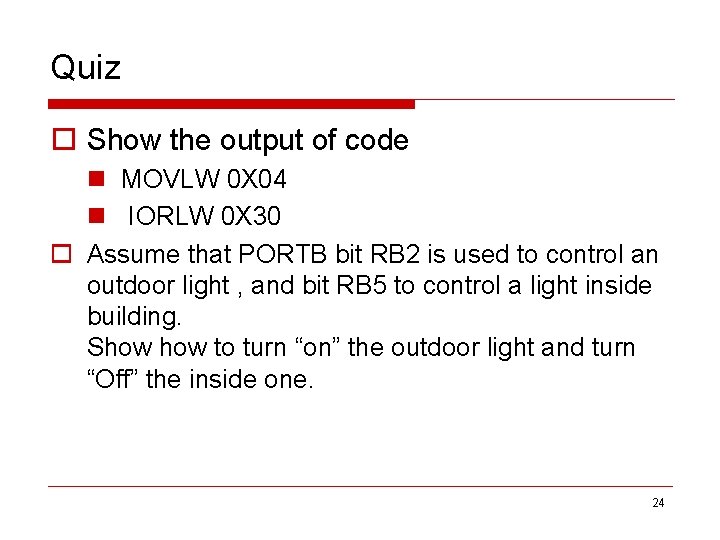

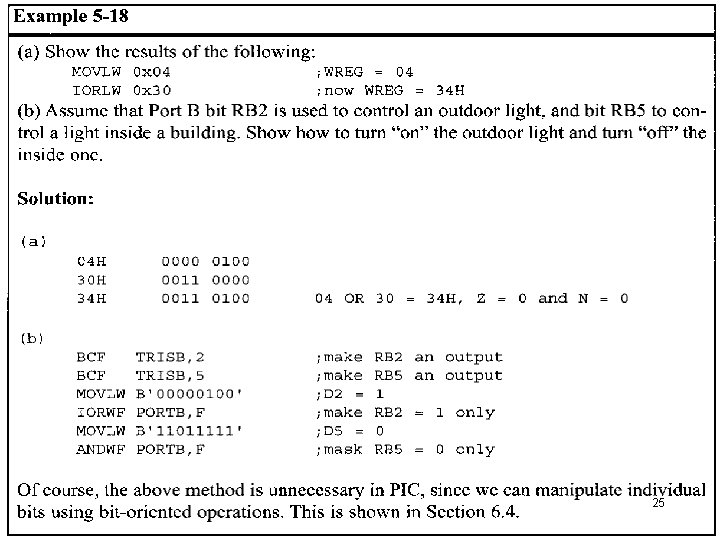

Quiz o Show the output of code n MOVLW 0 X 04 n IORLW 0 X 30 o Assume that PORTB bit RB 2 is used to control an outdoor light , and bit RB 5 to control a light inside building. Show to turn “on” the outdoor light and turn “Off” the inside one. 24

25

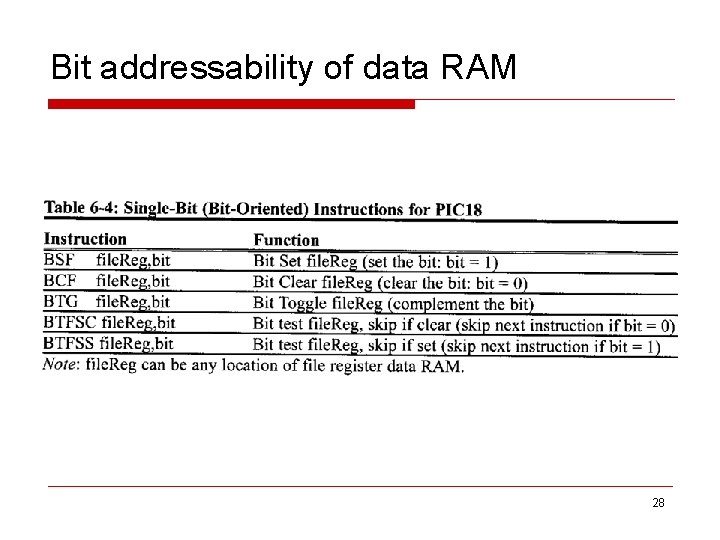

Bit addressability of data RAM o One of the basic feathers of the PIC 18 is the bit addressability of RAM. n Bit-addressable instructions o Use only direct addressing mode n Byte-addressable instructions 26

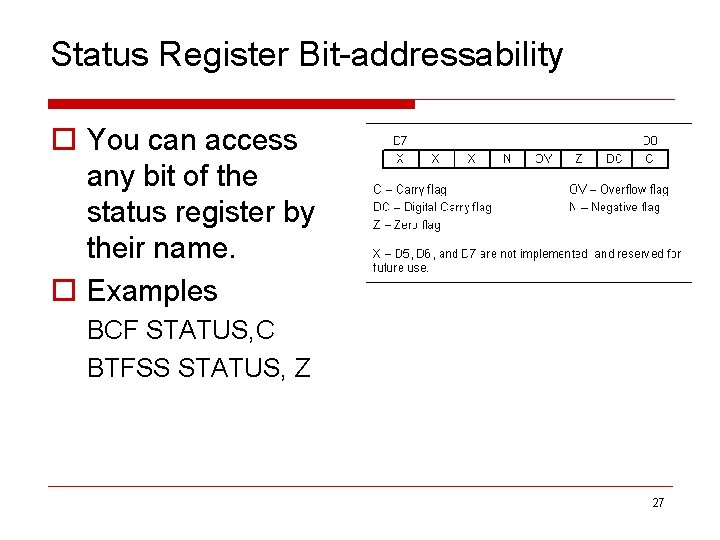

Status Register Bit-addressability o You can access any bit of the status register by their name. o Examples BCF STATUS, C BTFSS STATUS, Z 27

Bit addressability of data RAM 28

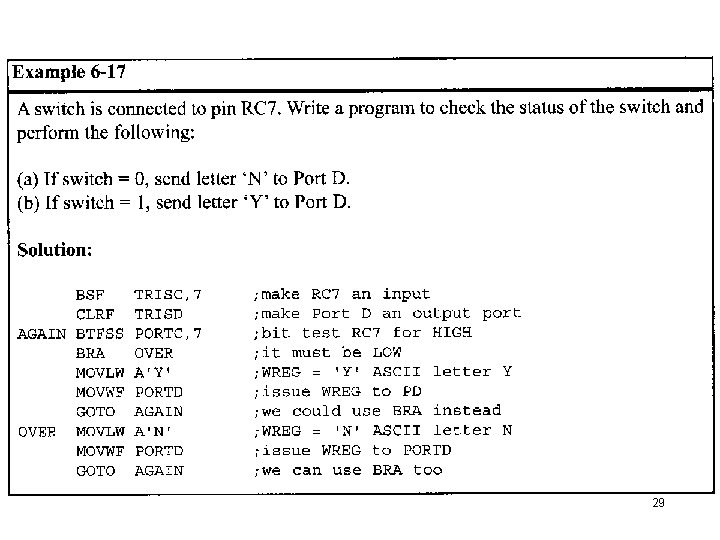

29

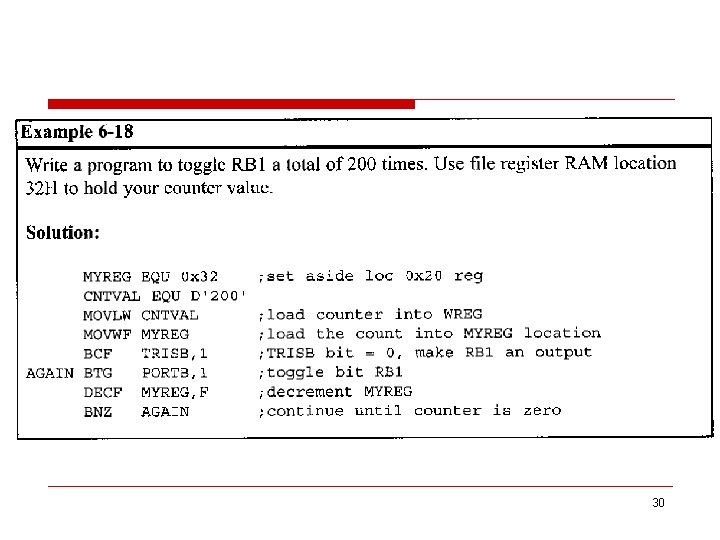

30

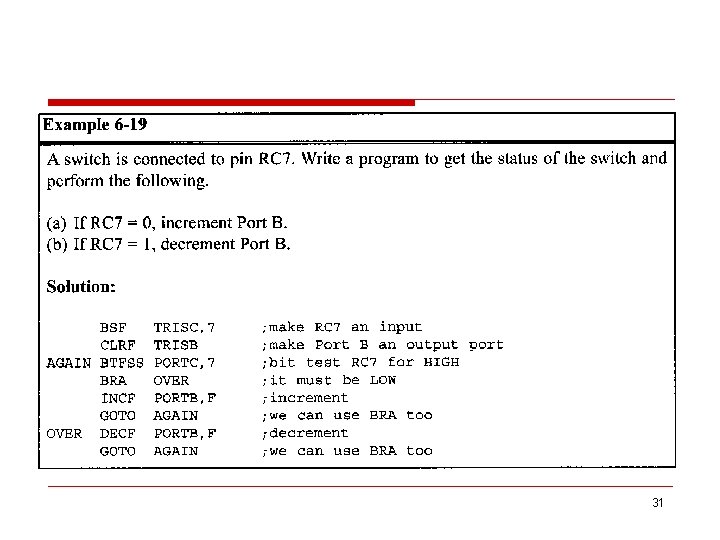

31

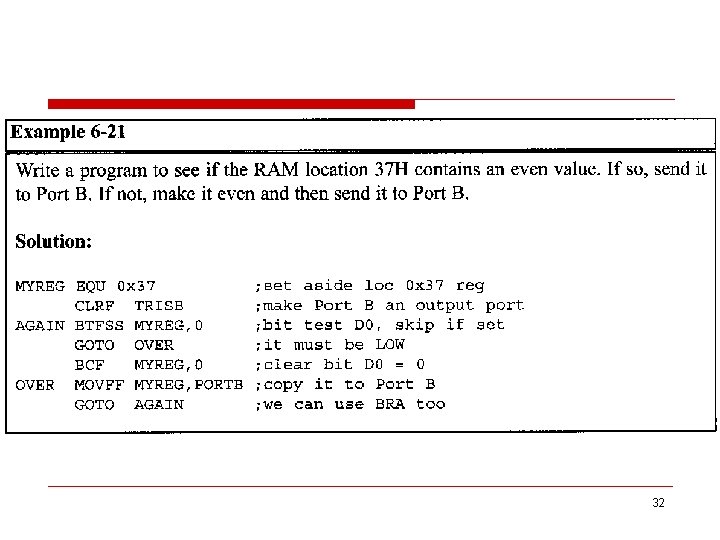

32

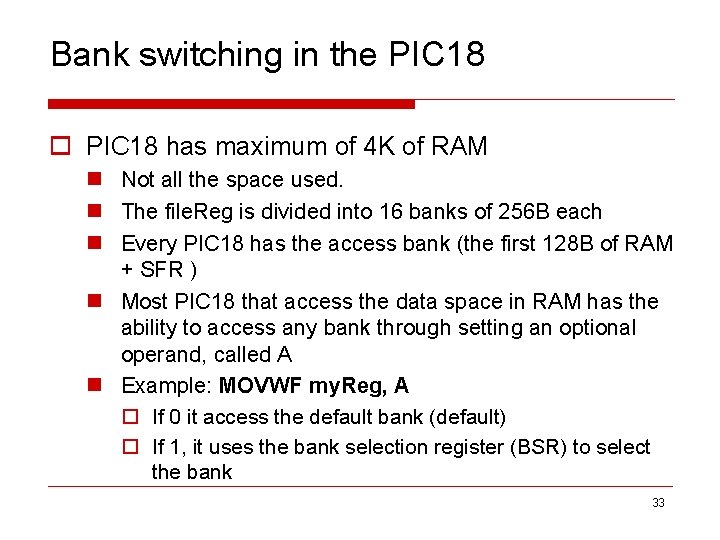

Bank switching in the PIC 18 o PIC 18 has maximum of 4 K of RAM n Not all the space used. n The file. Reg is divided into 16 banks of 256 B each n Every PIC 18 has the access bank (the first 128 B of RAM + SFR ) n Most PIC 18 that access the data space in RAM has the ability to access any bank through setting an optional operand, called A n Example: MOVWF my. Reg, A o If 0 it access the default bank (default) o If 1, it uses the bank selection register (BSR) to select the bank 33

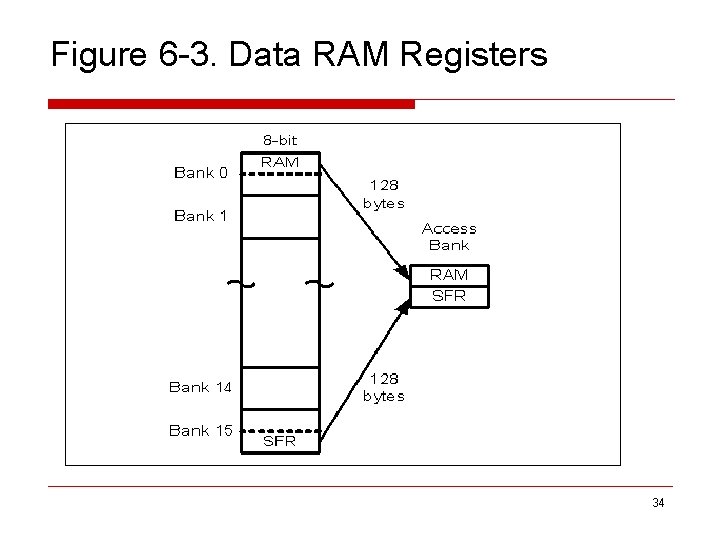

Figure 6 -3. Data RAM Registers 34

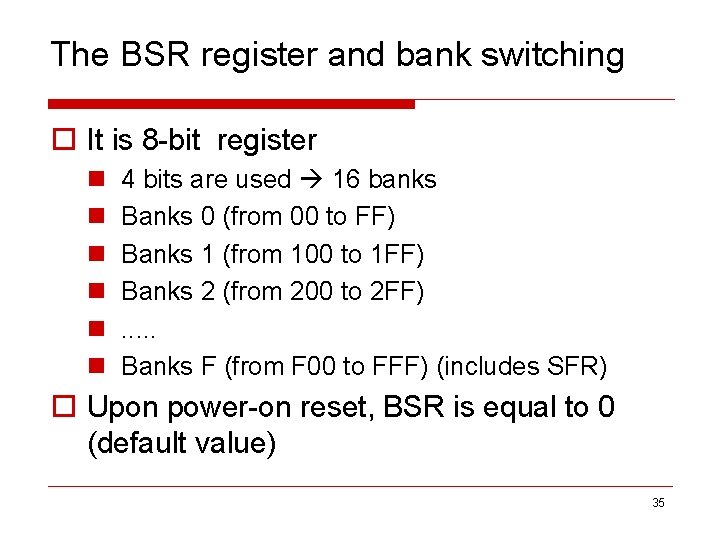

The BSR register and bank switching o It is 8 -bit register n n n 4 bits are used 16 banks Banks 0 (from 00 to FF) Banks 1 (from 100 to 1 FF) Banks 2 (from 200 to 2 FF). . . Banks F (from F 00 to FFF) (includes SFR) o Upon power-on reset, BSR is equal to 0 (default value) 35

A Bit in the Instruction Field for INCF F, D, A o. Two thing must be done n Load BSR with desired bank n Make A = 1 in the instruction itself. 36 6 -36

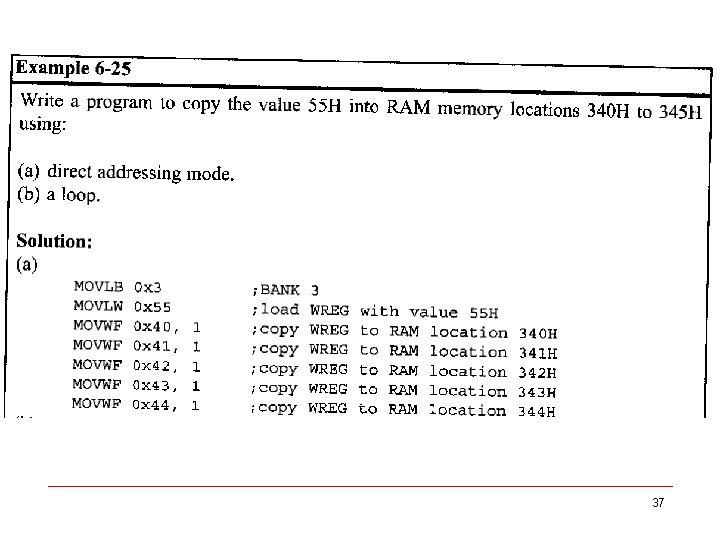

37

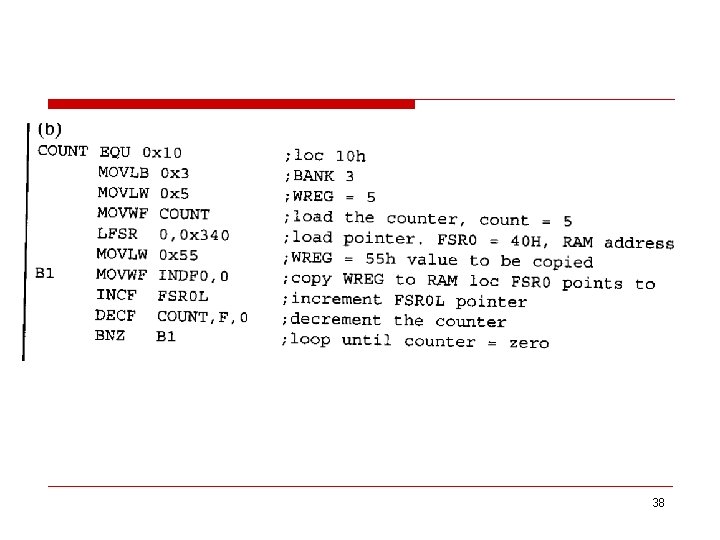

38

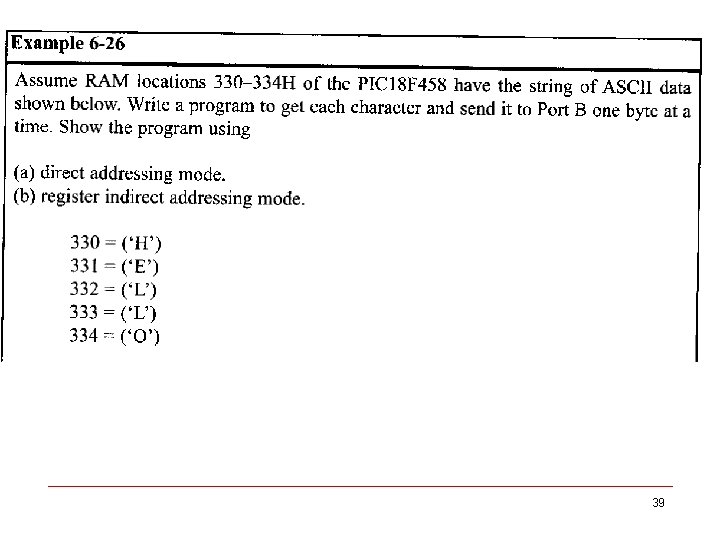

39

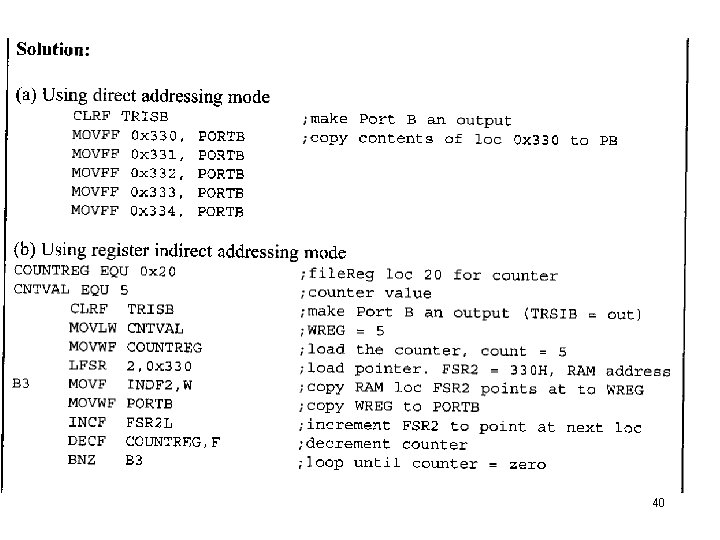

40

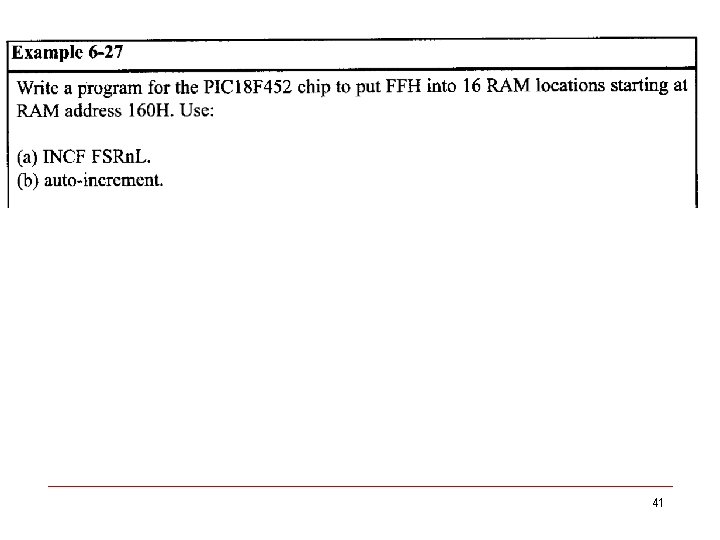

41

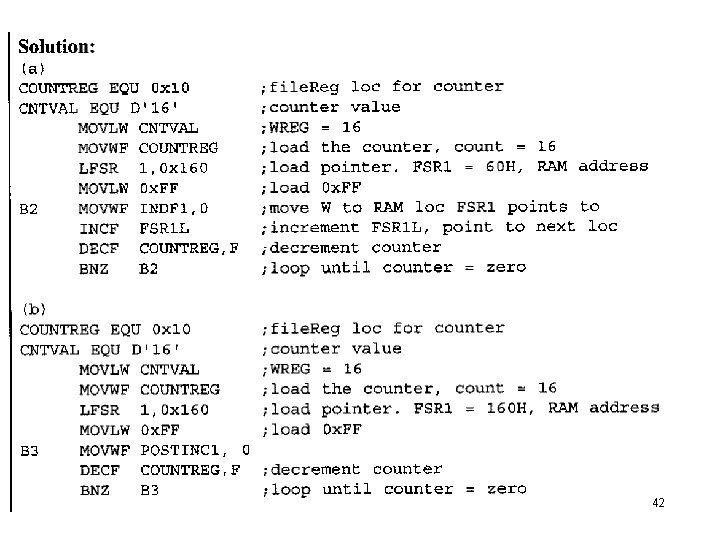

42

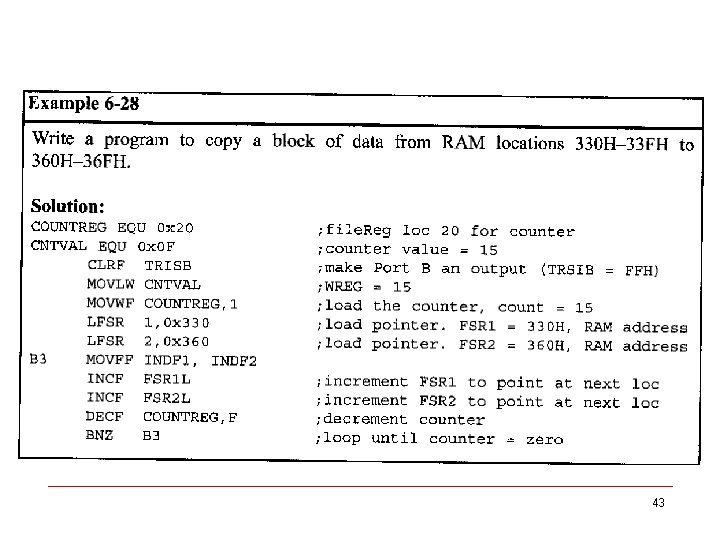

43

References o Jie Hu , ECE 692 Embedded Computing Systems , Fall 2010. o PIC Microcontroller And Embedded Systems: using Assembly and C for PIC 18, M. Mazidi, R. Mc. Kinlay and D. Causey, Prentice Fall, 2008. o Eng. Husam Alzaq, Embedded System Course, IUG, 2010 IUG- Embedded System 44

- Slides: 44