Decoders and Encoders Discussion D 4 2 Decoders

![3 -to-8 Decoder input [2: 0] A ; wire [2: 0] A ; Behavior 3 -to-8 Decoder input [2: 0] A ; wire [2: 0] A ; Behavior](https://slidetodoc.com/presentation_image_h2/d07b42d91720553883fd1c4b89f77baa/image-4.jpg)

- Slides: 30

Decoders and Encoders Discussion D 4. 2

Decoders and Encoders • Binary Decoders • Binary Encoders • Priority Encoders

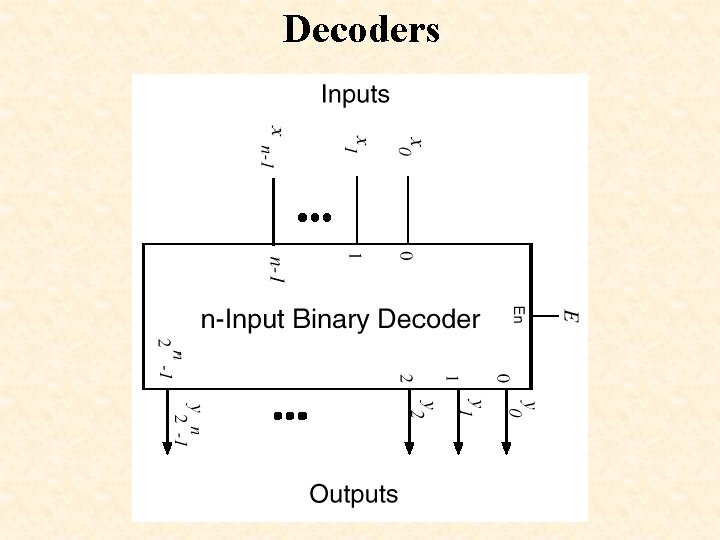

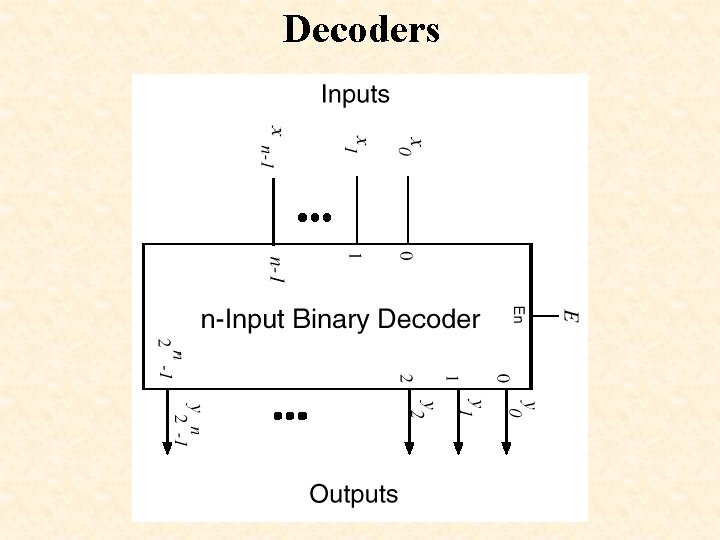

Decoders

![3 to8 Decoder input 2 0 A wire 2 0 A Behavior 3 -to-8 Decoder input [2: 0] A ; wire [2: 0] A ; Behavior](https://slidetodoc.com/presentation_image_h2/d07b42d91720553883fd1c4b89f77baa/image-4.jpg)

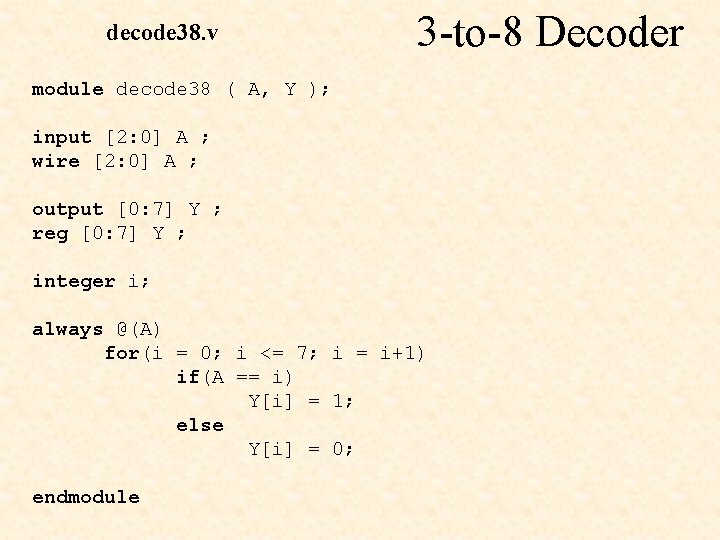

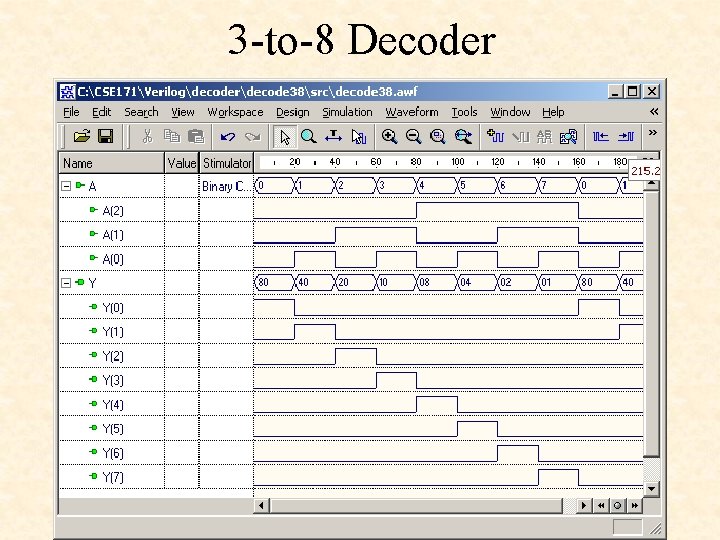

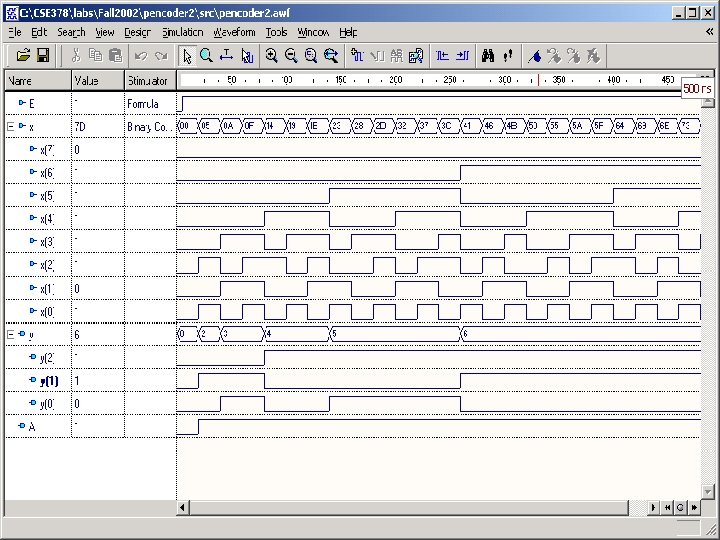

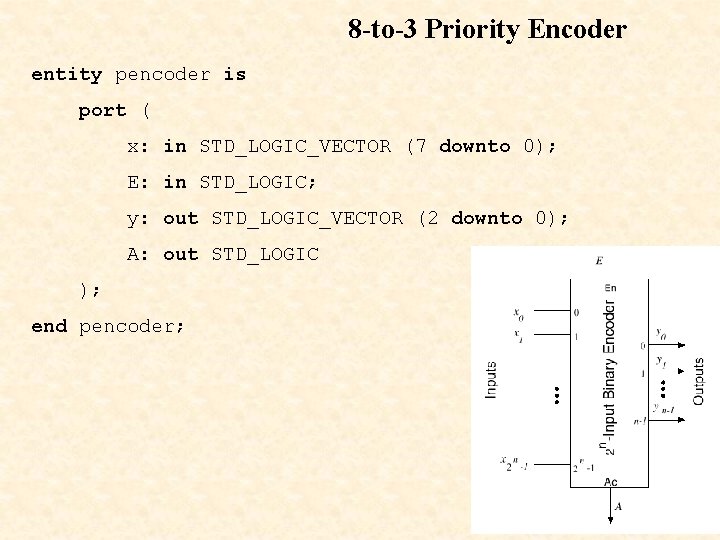

3 -to-8 Decoder input [2: 0] A ; wire [2: 0] A ; Behavior for(i = 0; i <= 7; i = i+1) if(A == i) Y[i] = 1; else Y[i] = 0; output [0: 7] Y ; reg [0: 7] Y ;

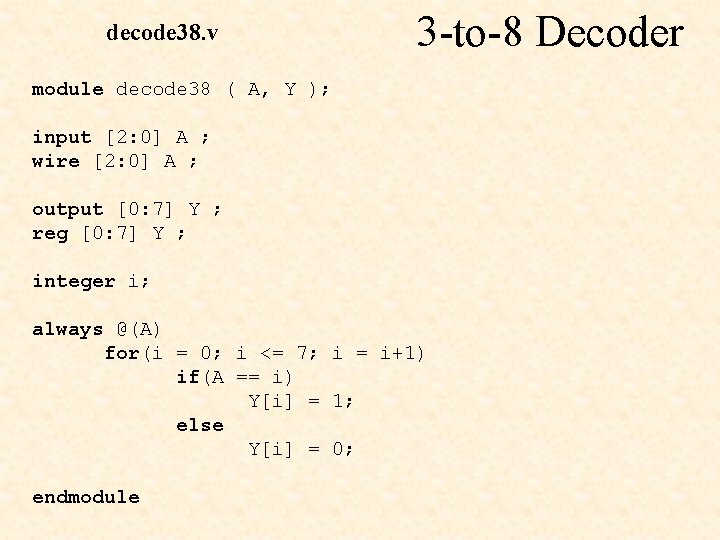

decode 38. v 3 -to-8 Decoder module decode 38 ( A, Y ); input [2: 0] A ; wire [2: 0] A ; output [0: 7] Y ; reg [0: 7] Y ; integer i; always @(A) for(i = 0; i <= 7; i = i+1) if(A == i) Y[i] = 1; else Y[i] = 0; endmodule

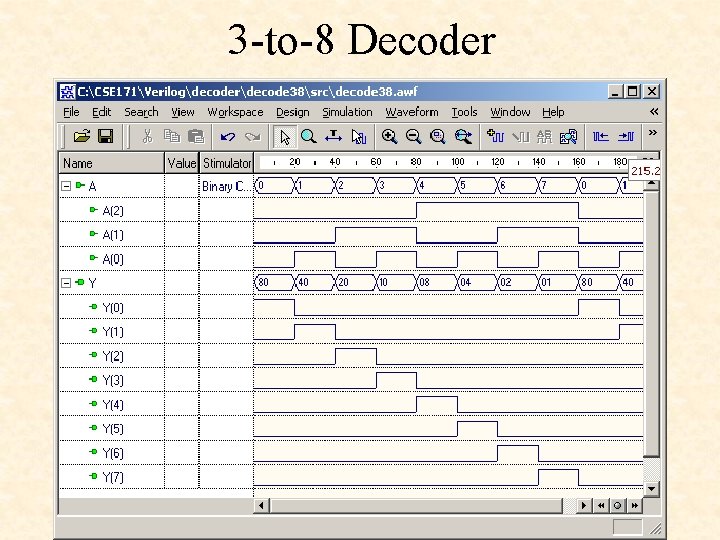

3 -to-8 Decoder

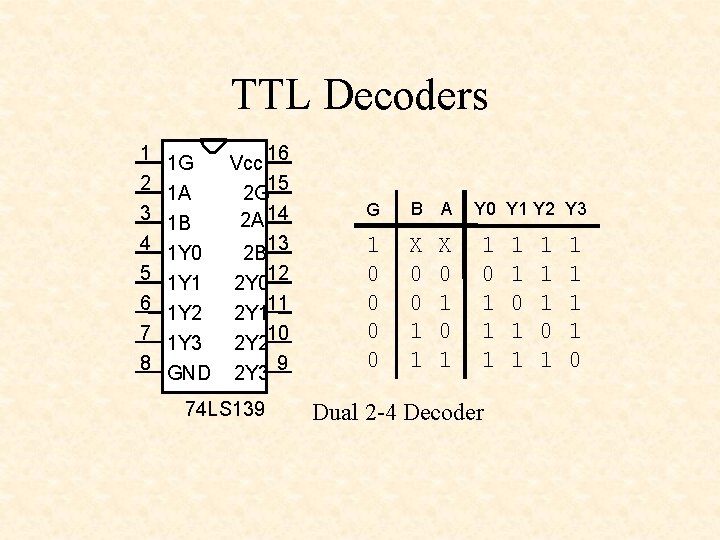

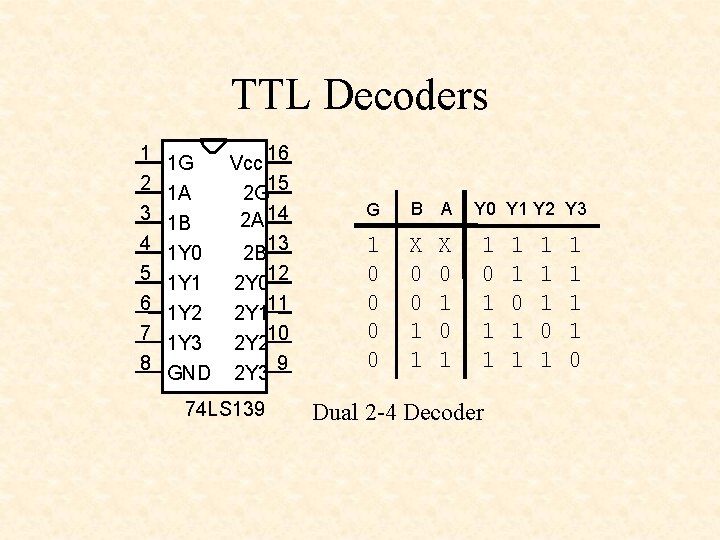

TTL Decoders 1 2 3 4 5 6 7 8 16 1 G Vcc 1 A 2 G 15 2 A 14 1 B 1 Y 0 2 B 13 1 Y 1 2 Y 012 1 Y 2 2 Y 111 1 Y 3 2 Y 210 GND 2 Y 3 9 74 LS 139 G B A 1 0 0 X 0 0 1 1 X 0 1 Y 0 Y 1 Y 2 Y 3 1 0 1 1 1 Dual 2 -4 Decoder 1 1 0 1 1 1 1 1 0

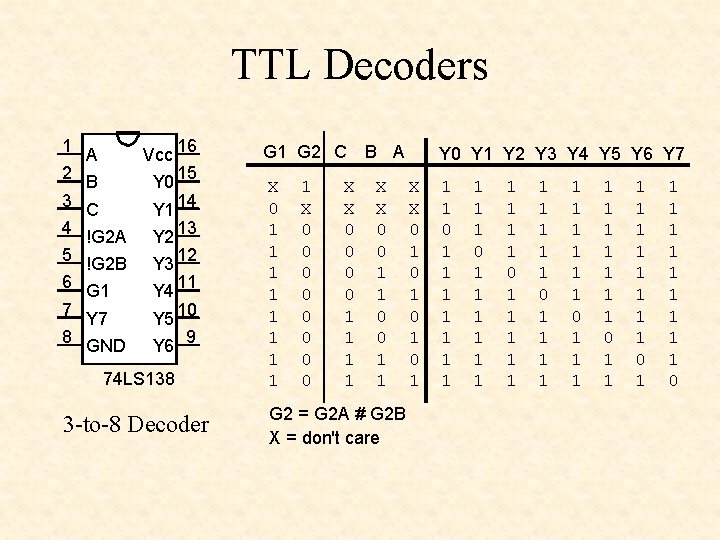

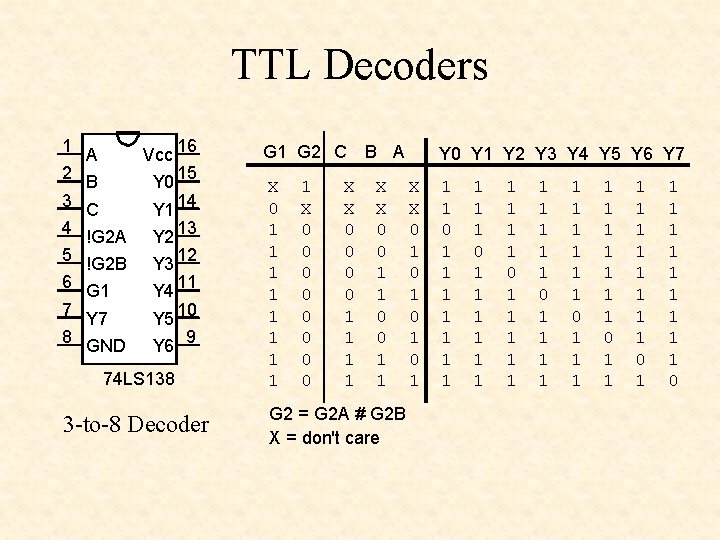

TTL Decoders 1 A 2 B 3 4 Vcc 16 Y 0 15 C Y 1 !G 2 A Y 2 5 !G 2 B 6 G 1 7 Y 7 8 GND 14 13 Y 3 12 Y 4 11 Y 5 10 9 Y 6 74 LS 138 3 -to-8 Decoder G 1 G 2 C B A X 0 1 1 1 1 1 X 0 0 0 0 X X 0 0 1 1 G 2 = G 2 A # G 2 B X = don't care Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 X X 0 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 0

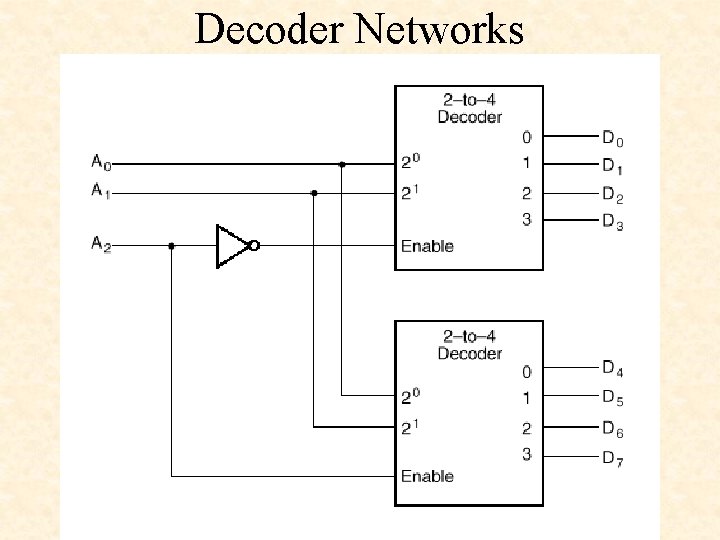

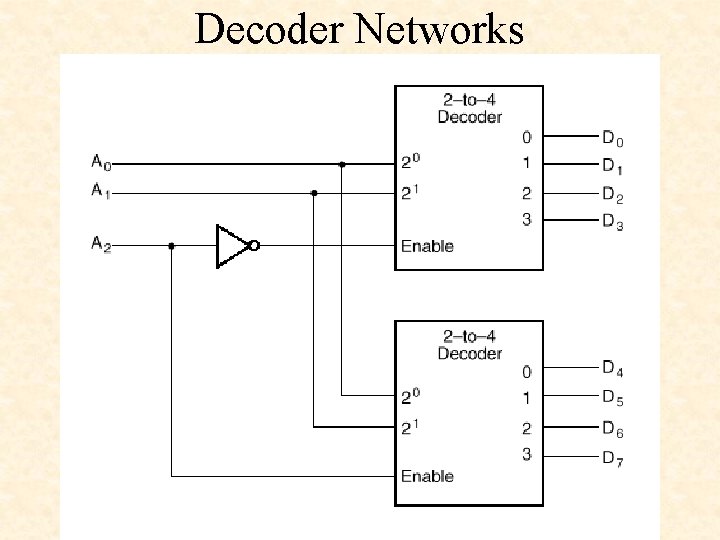

Decoder Networks

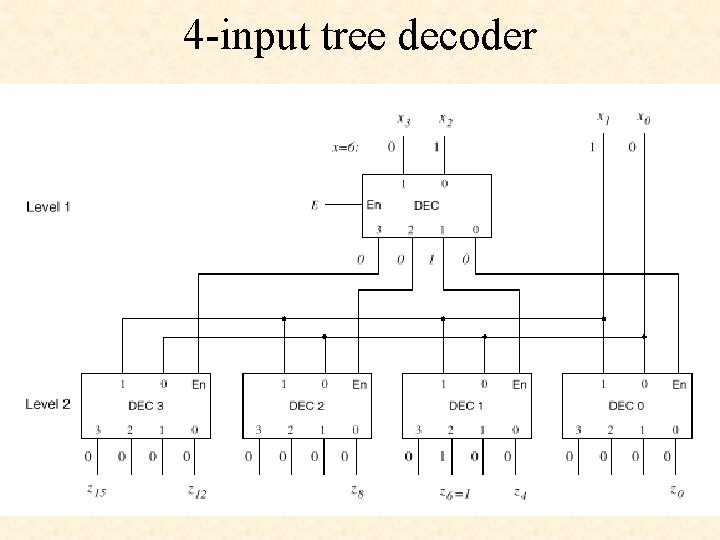

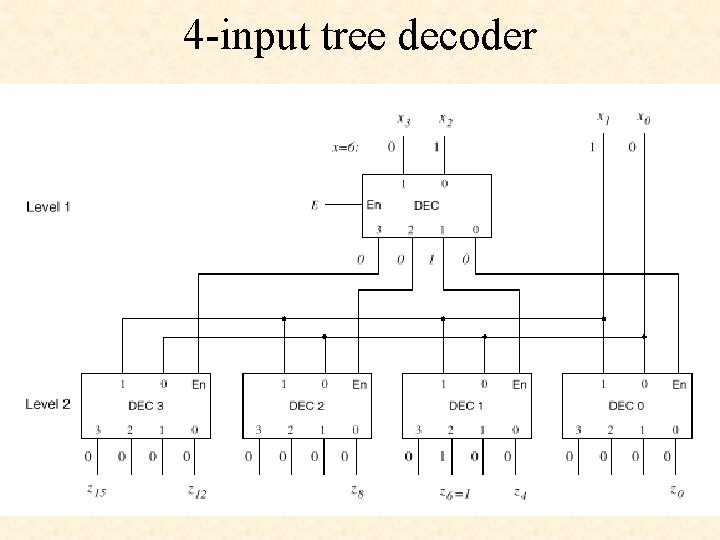

4 -input tree decoder

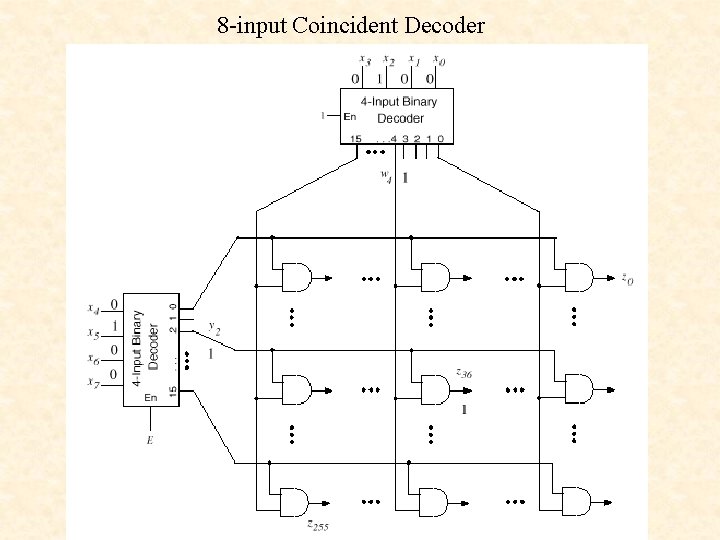

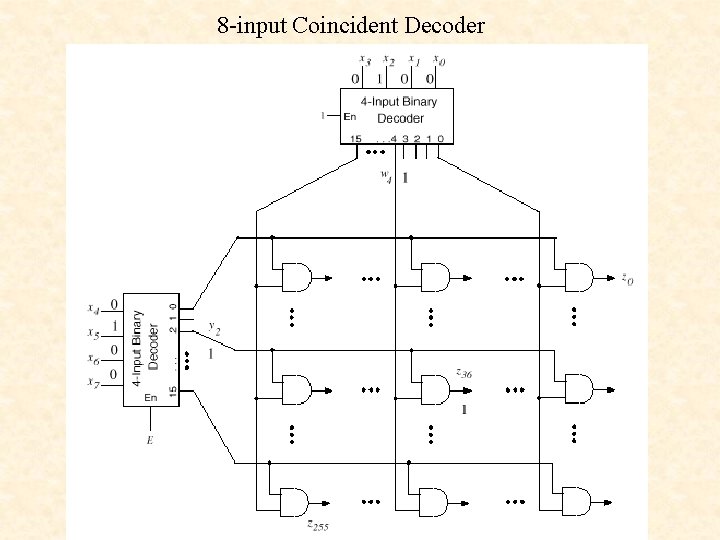

8 -input Coincident Decoder

Decoders and Encoders • Binary Decoders • Binary Encoders • Priority Encoders

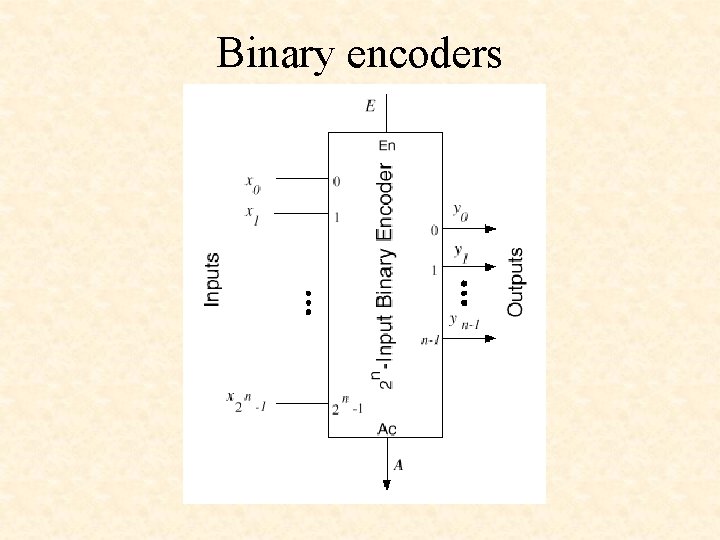

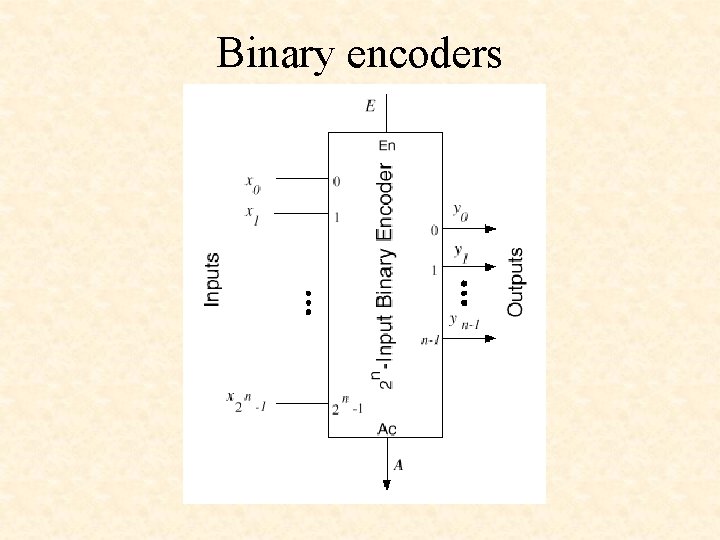

Binary encoders

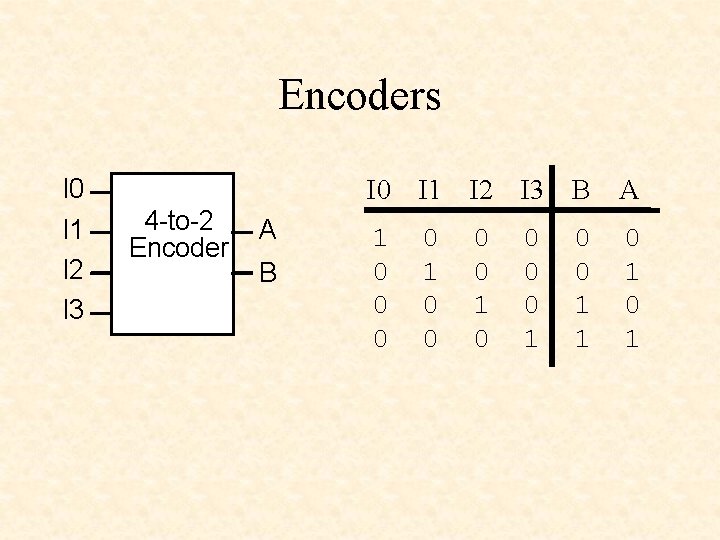

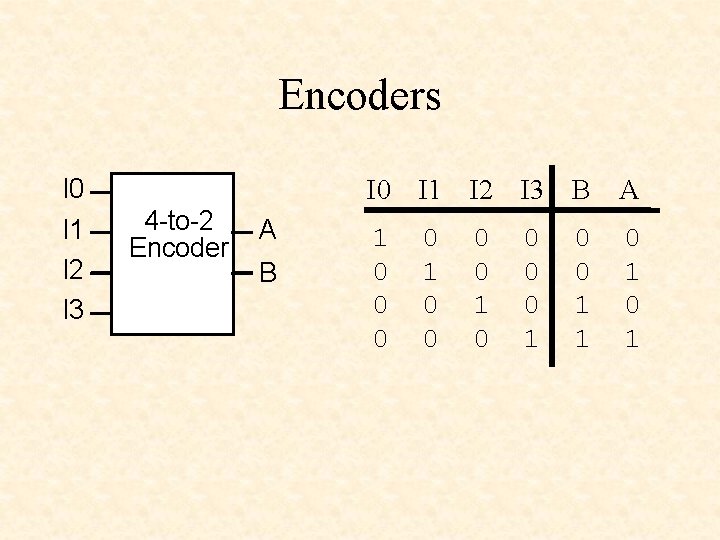

Encoders I 0 I 1 I 2 I 3 4 -to-2 Encoder A B I 0 I 1 I 2 I 3 B A 1 0 0 0 0 1 0 0 1 1 0 1

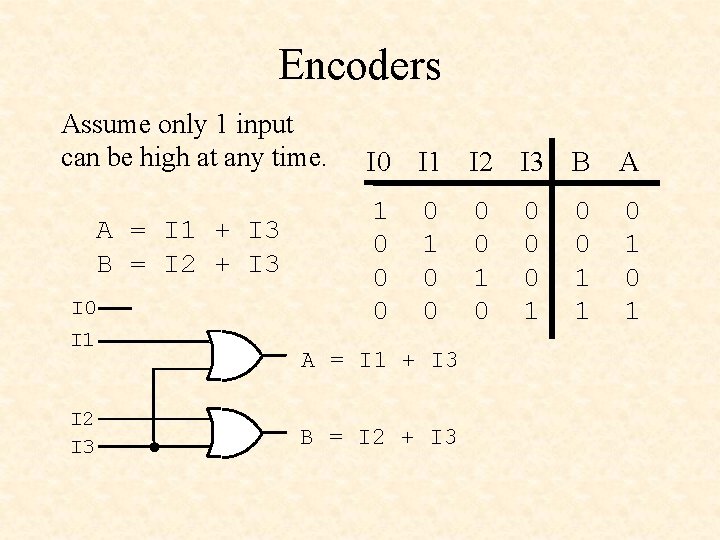

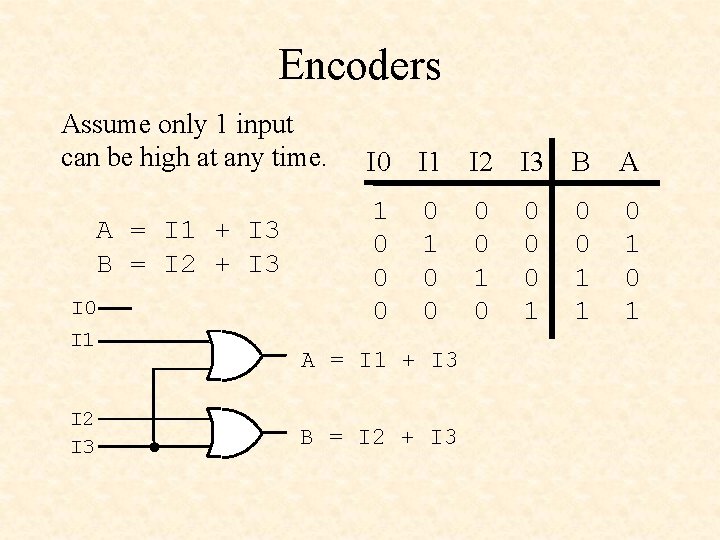

Encoders Assume only 1 input can be high at any time. A = I 1 + I 3 B = I 2 + I 3 I 0 I 1 I 2 I 3 B A 1 0 0 0 0 1 0 0 1 1 0 1 A = I 1 + I 3 B = I 2 + I 3

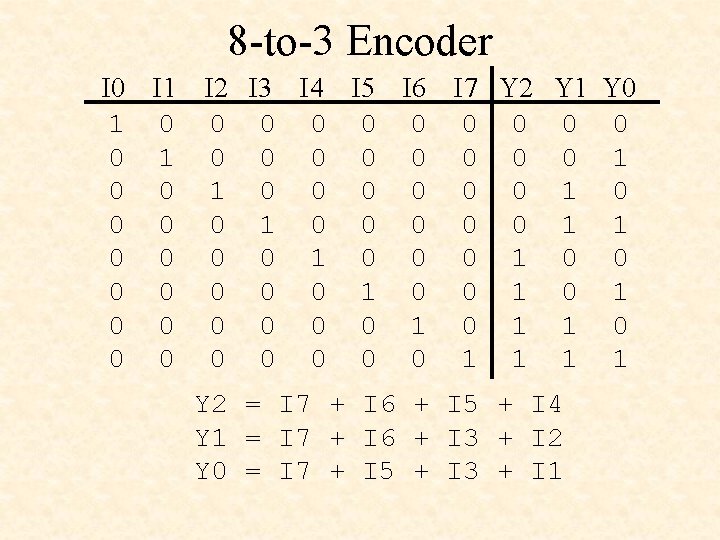

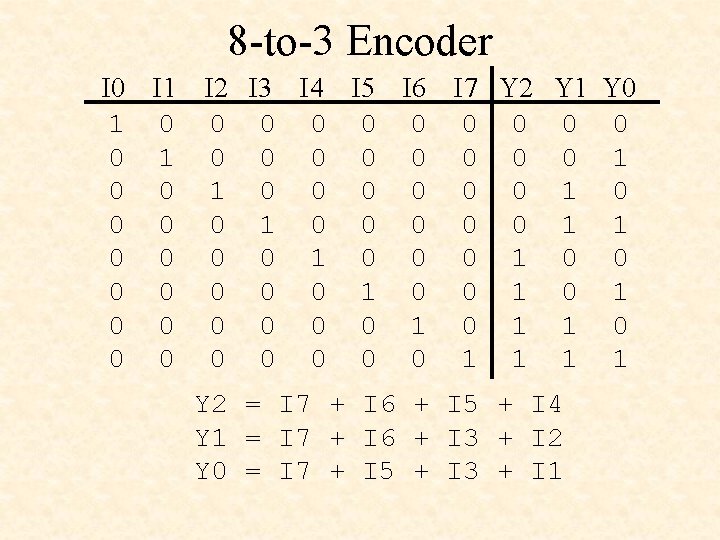

8 -to-3 Encoder I 0 1 0 0 0 0 I 2 I 3 I 4 I 5 I 6 I 7 Y 2 Y 1 Y 0 0 0 0 0 1 1 0 0 0 0 0 1 1 0 0 0 1 0 1 0 1 1 0 0 0 1 1 Y 2 = I 7 + I 6 + I 5 + I 4 Y 1 = I 7 + I 6 + I 3 + I 2 Y 0 = I 7 + I 5 + I 3 + I 1

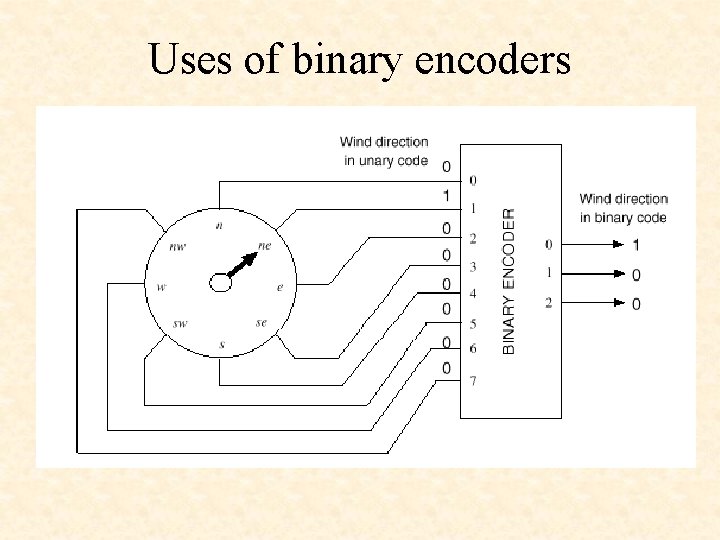

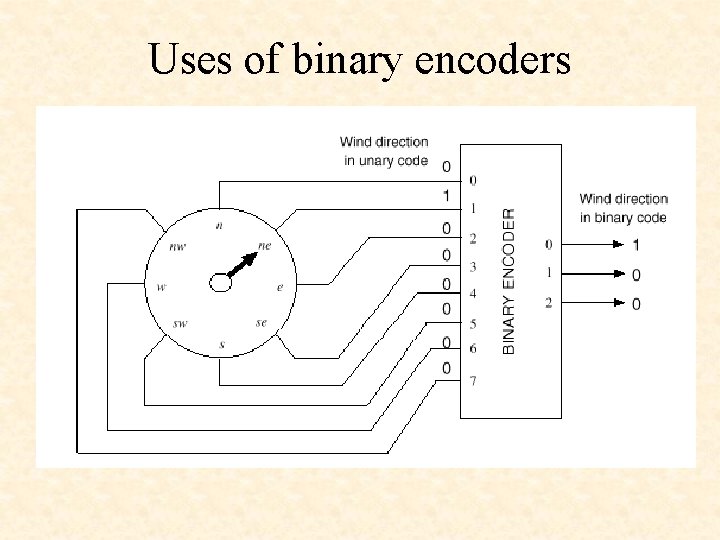

Uses of binary encoders

Decoders and Encoders • Binary Decoders • Binary Encoders • Priority Encoders

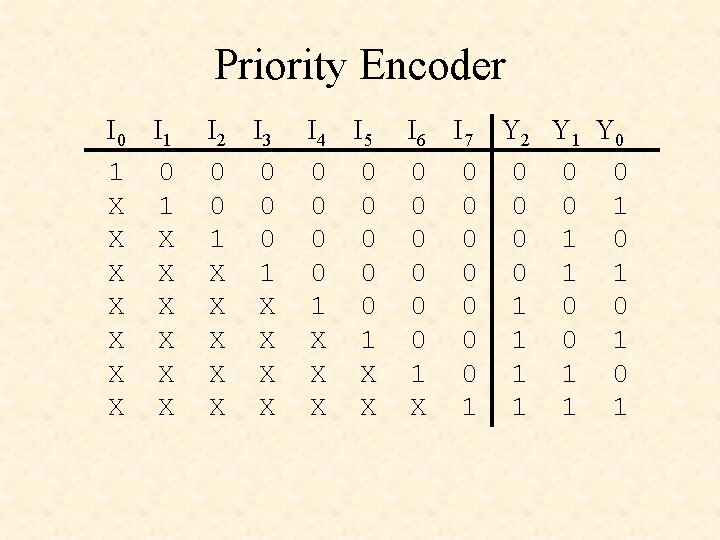

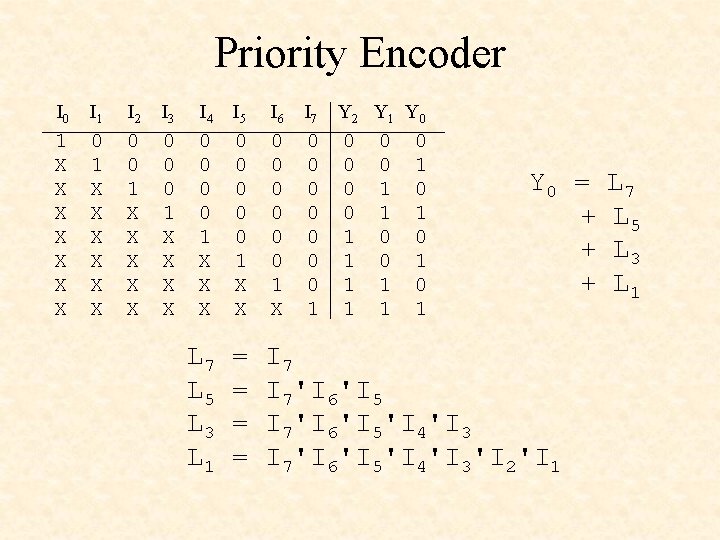

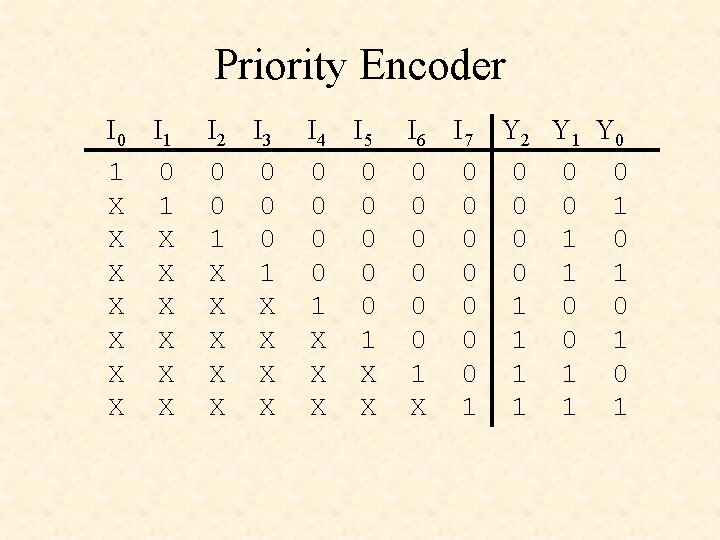

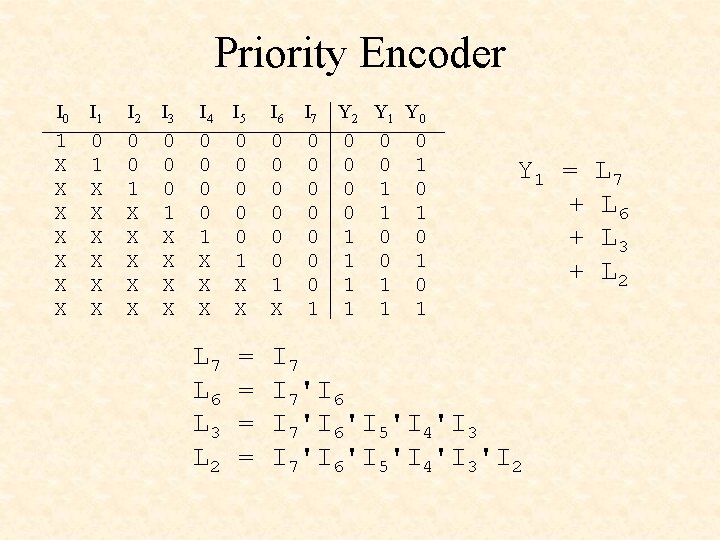

Priority Encoder I 0 I 1 1 0 X 1 X X X I 2 I 3 0 0 1 0 X 1 X X X X I 4 I 5 0 0 0 0 1 0 X 1 X X I 6 I 7 Y 2 Y 1 Y 0 0 0 0 0 1 1 0 0 0 0 1 1 0 X 1 1

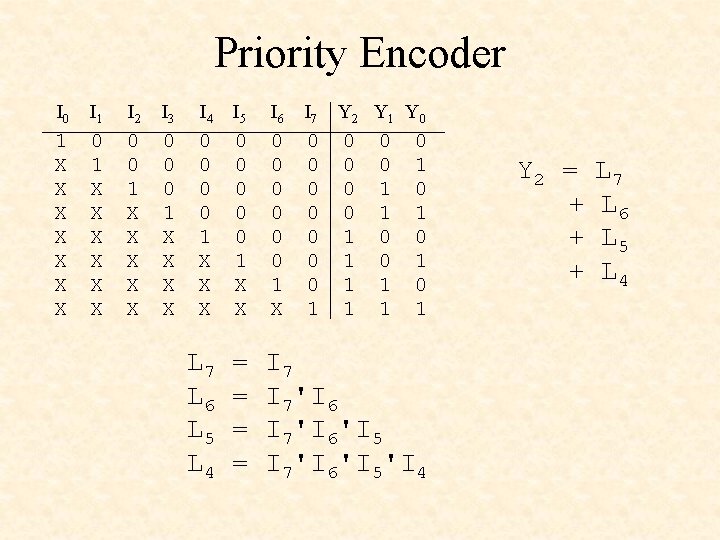

Priority Encoder I 0 1 X X X X I 1 0 1 X X X I 2 0 0 1 X X X I 3 0 0 0 1 X X I 4 0 0 1 X X X I 5 0 0 0 1 X X I 6 0 0 0 1 X I 7 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 0 1 0 1 1 1 1 L 7 L 6 L 5 L 4 = = I 7'I 6'I 5'I 4 Y 2 = + + + L 7 L 6 L 5 L 4

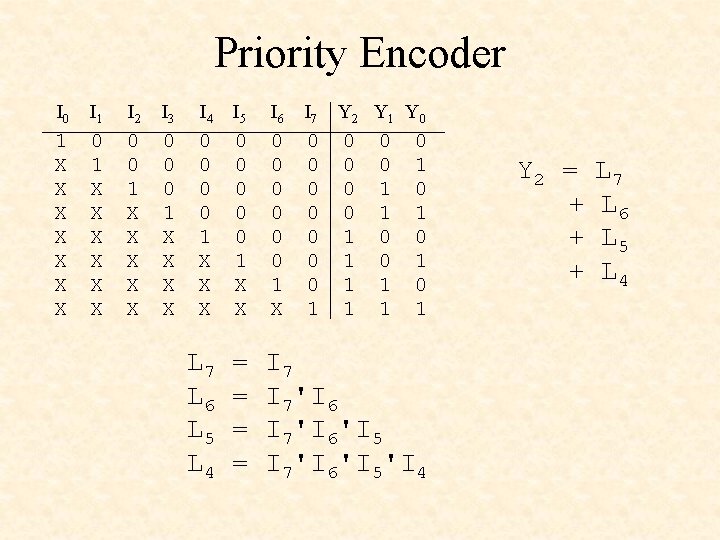

Priority Encoder I 0 1 X X X X I 1 0 1 X X X I 2 0 0 1 X X X I 3 0 0 0 1 X X I 4 0 0 1 X X X I 5 0 0 0 1 X X I 6 0 0 0 1 X I 7 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 0 1 0 1 1 1 1 L 7 L 6 L 3 L 2 = = I 7'I 6'I 5'I 4'I 3'I 2 Y 1 = + + + L 7 L 6 L 3 L 2

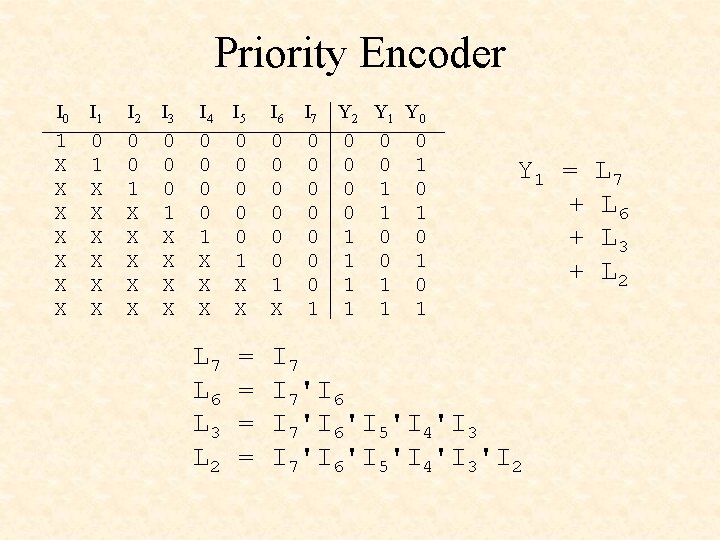

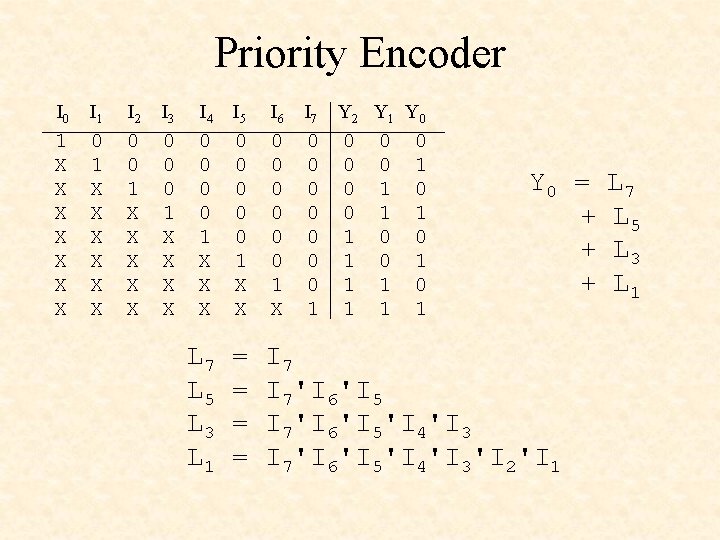

Priority Encoder I 0 1 X X X X I 1 0 1 X X X I 2 0 0 1 X X X I 3 0 0 0 1 X X I 4 0 0 1 X X X I 5 0 0 0 1 X X I 6 0 0 0 1 X I 7 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 0 1 0 1 1 1 1 L 7 L 5 L 3 L 1 = = I 7'I 6'I 5'I 4'I 3'I 2'I 1 Y 0 = + + + L 7 L 5 L 3 L 1

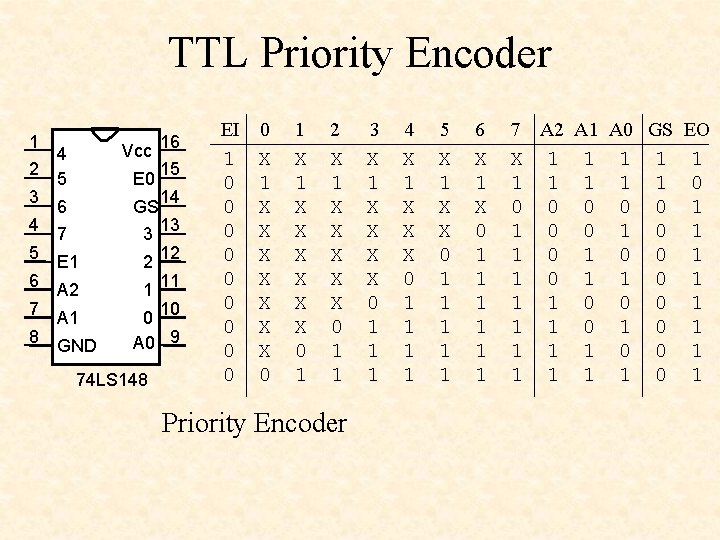

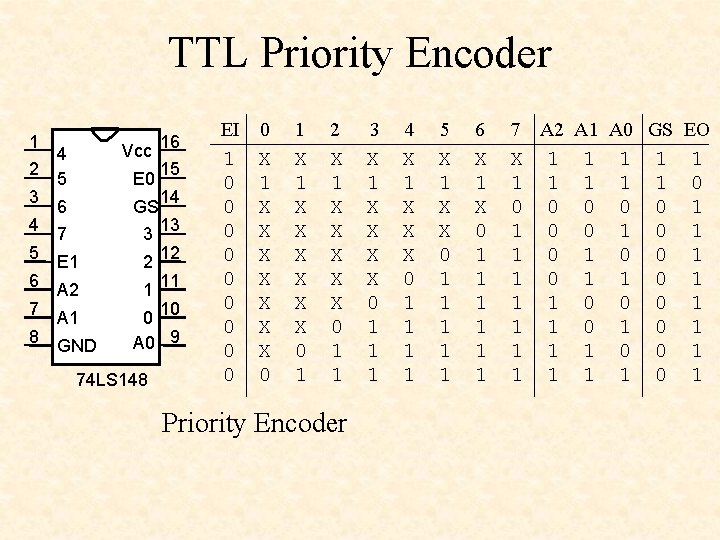

TTL Priority Encoder 1 4 2 5 3 6 4 7 5 E 1 6 A 2 7 A 1 8 GND Vcc E 0 GS 3 2 1 16 15 14 13 12 11 10 0 A 0 9 74 LS 148 EI 1 0 0 0 0 0 X 1 X X X X 0 1 2 X 1 X X X 0 1 1 Priority Encoder 3 X 1 X X 0 1 1 1 4 X 1 X X X 0 1 1 5 X 1 X X 0 1 1 1 6 X 1 X 0 1 1 1 7 A 2 A 1 A 0 GS EO X 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 0 0 1 1 1 0 1

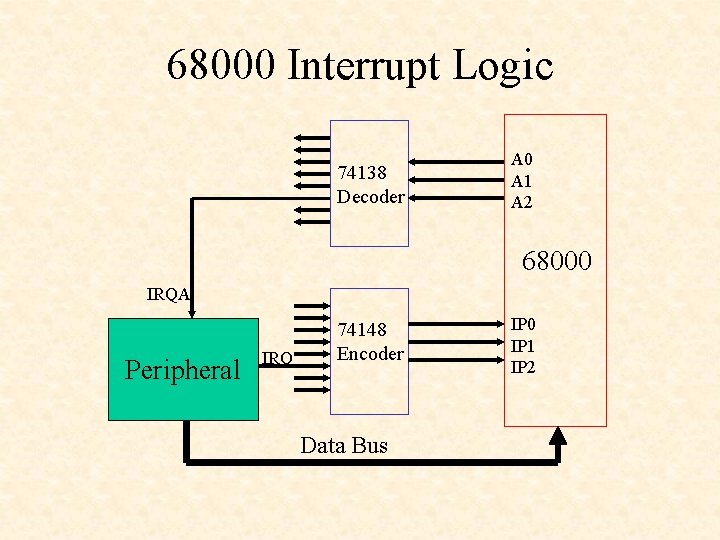

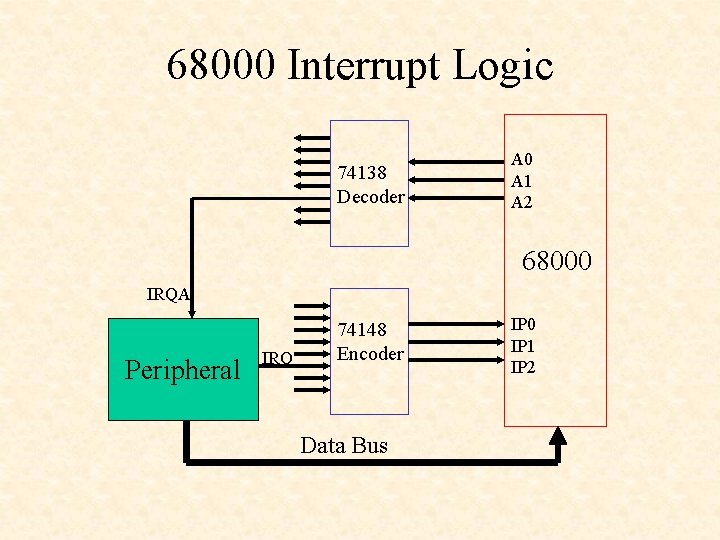

68000 Interrupt Logic 74138 Decoder A 0 A 1 A 2 68000 IRQA Peripheral IRQ 74148 Encoder Data Bus IP 0 IP 1 IP 2

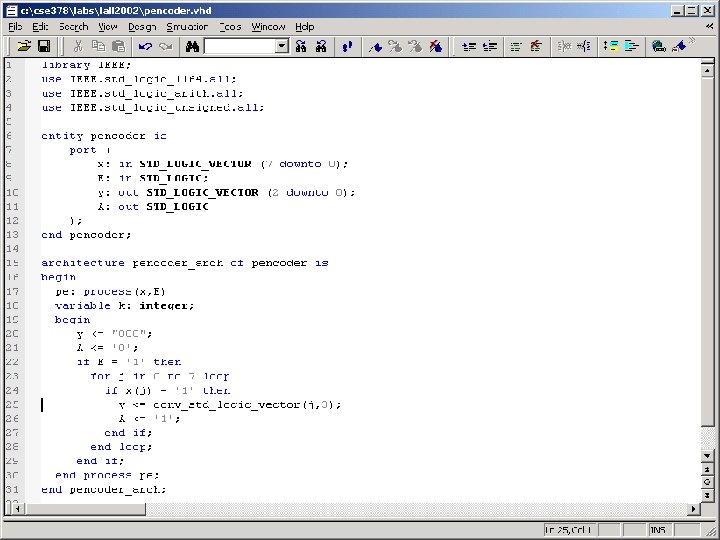

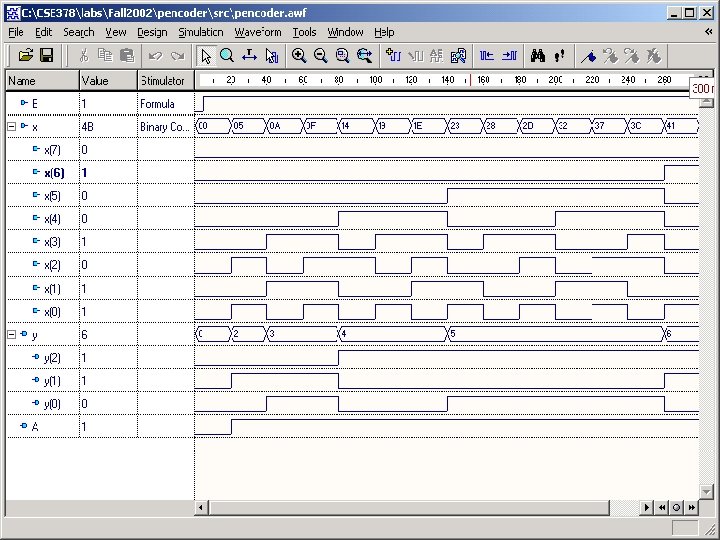

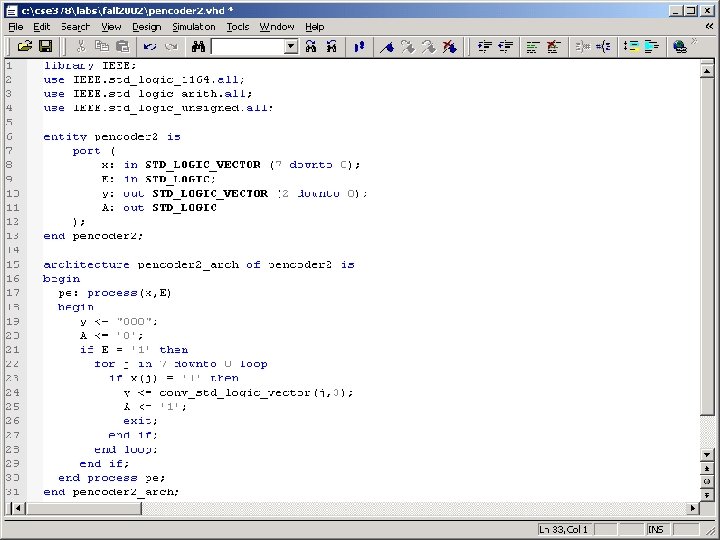

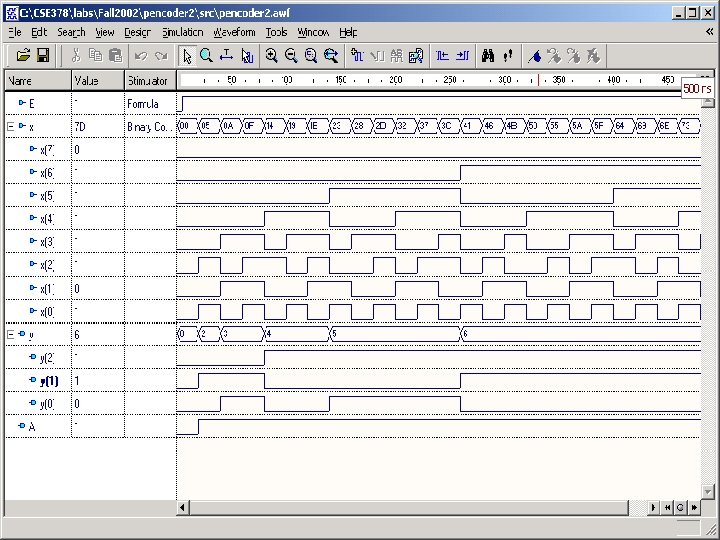

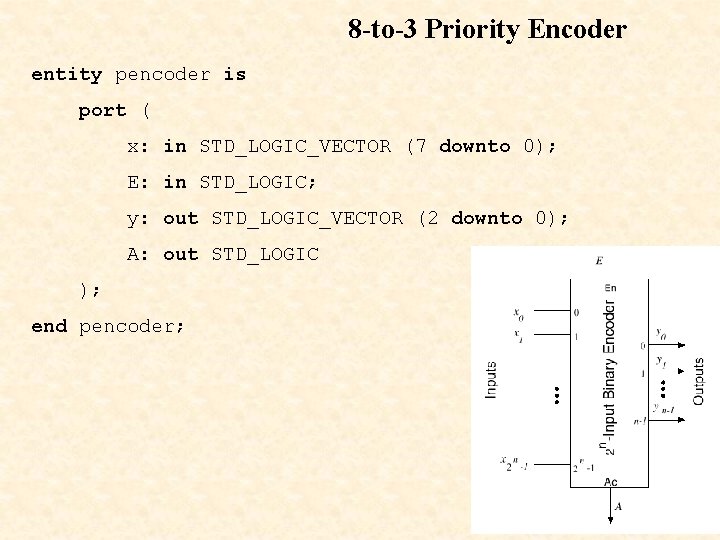

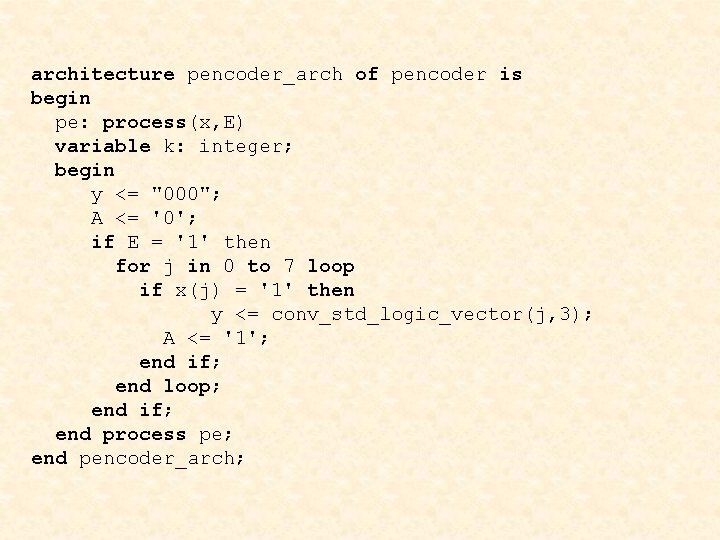

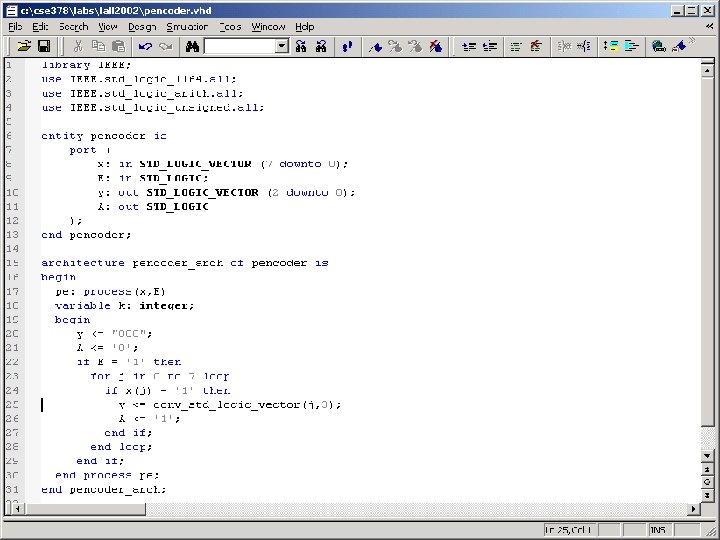

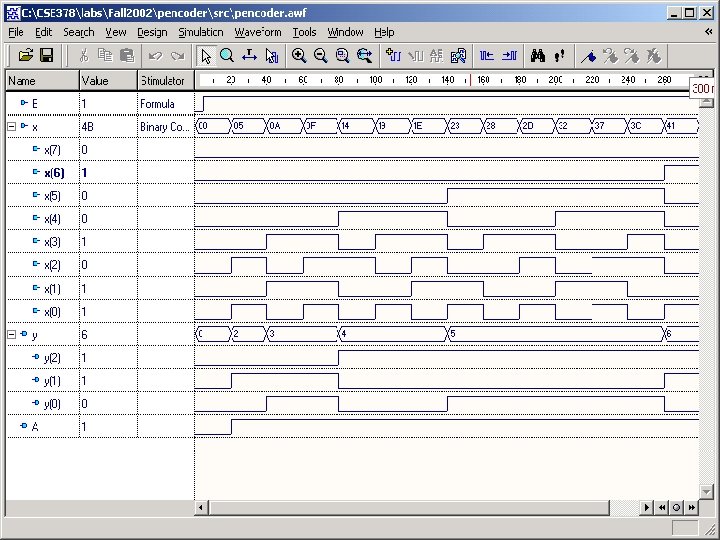

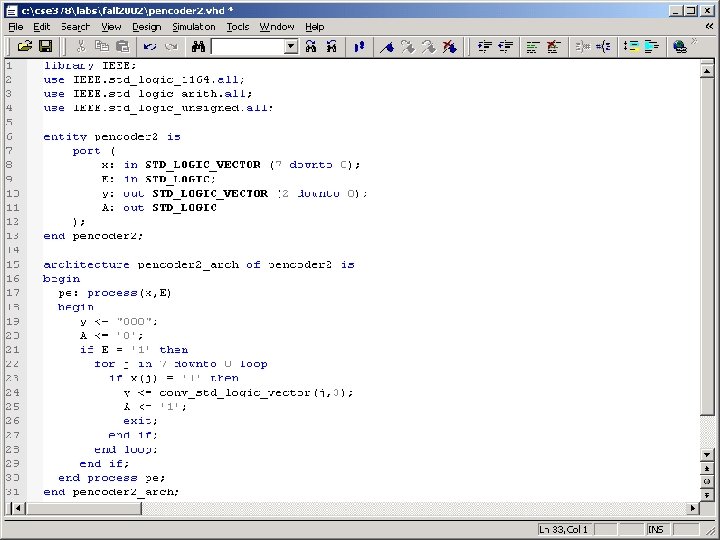

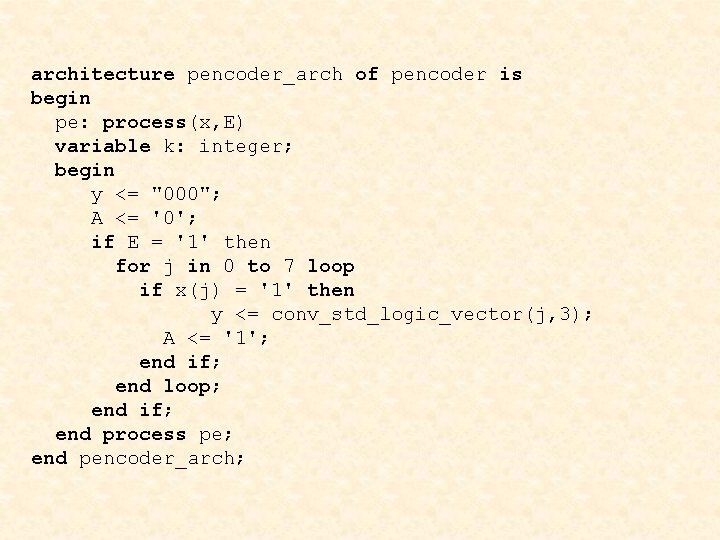

8 -to-3 Priority Encoder entity pencoder is port ( x: in STD_LOGIC_VECTOR (7 downto 0); E: in STD_LOGIC; y: out STD_LOGIC_VECTOR (2 downto 0); A: out STD_LOGIC ); end pencoder;

architecture pencoder_arch of pencoder is begin pe: process(x, E) variable k: integer; begin y <= "000"; A <= '0'; if E = '1' then for j in 0 to 7 loop if x(j) = '1' then y <= conv_std_logic_vector(j, 3); A <= '1'; end if; end loop; end if; end process pe; end pencoder_arch;