Priority Encoders Discussion D 9 4 Example 24

- Slides: 10

Priority Encoders Discussion D 9. 4 Example 24

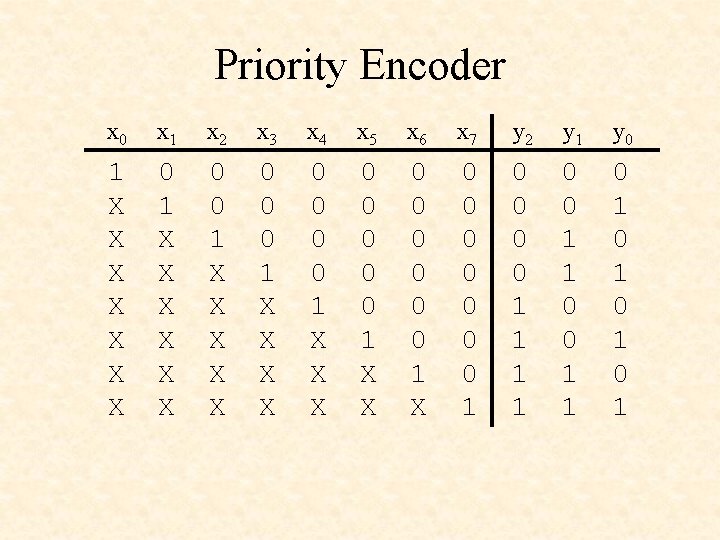

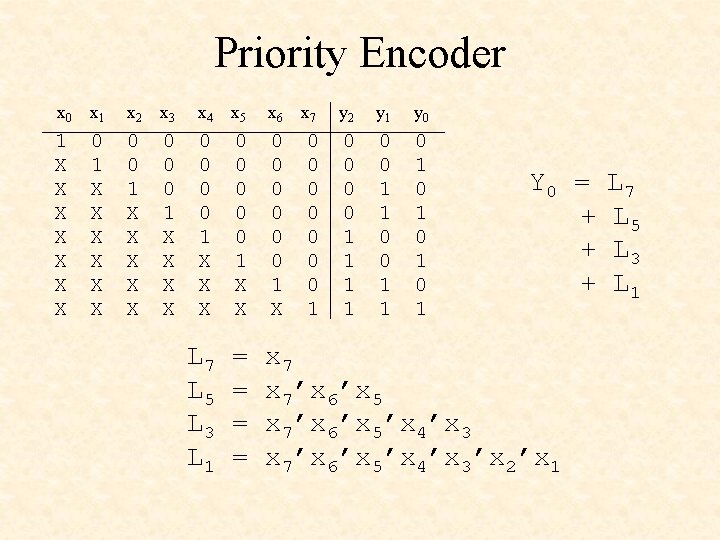

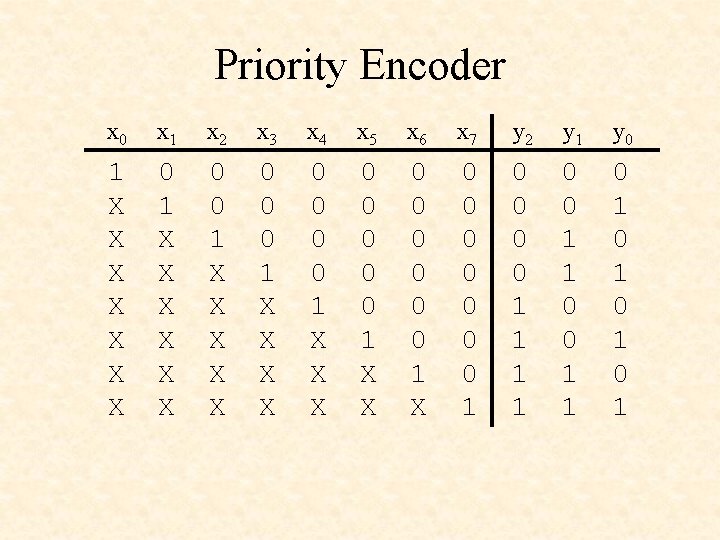

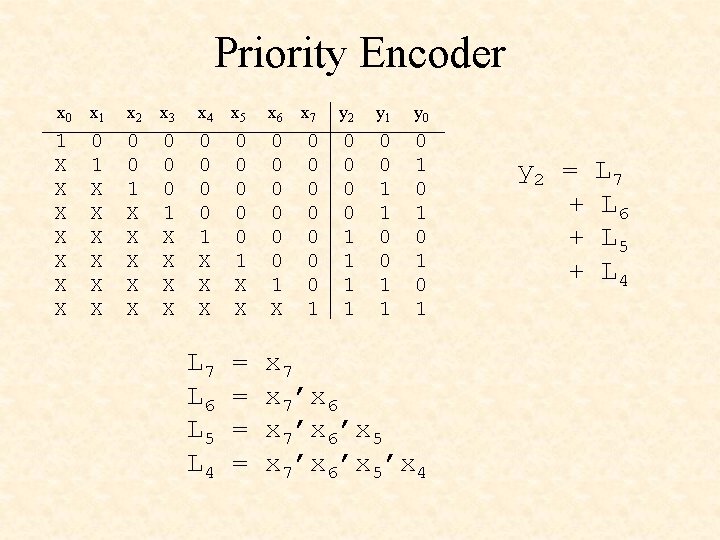

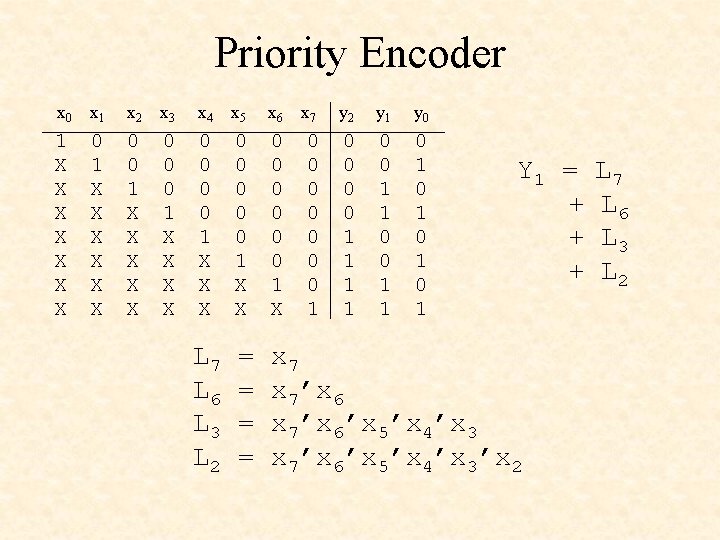

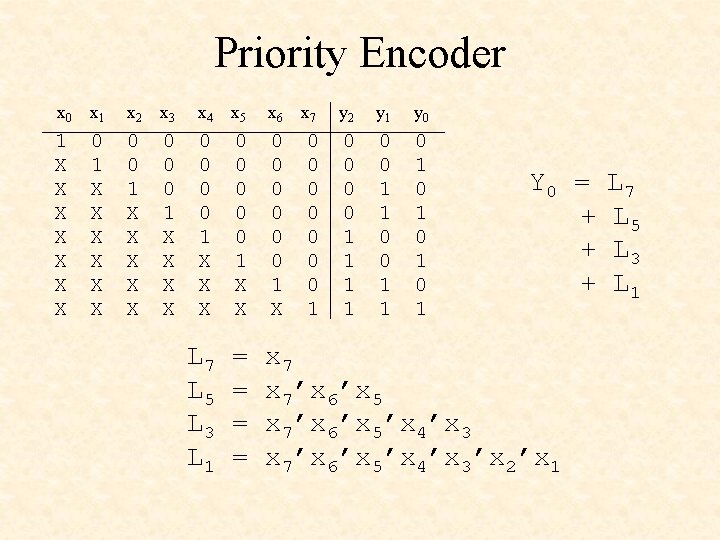

Priority Encoder x 0 x 1 x 2 x 3 x 4 x 5 x 6 x 7 y 2 y 1 y 0 1 X X X X 0 1 X X X 0 0 0 1 X X X 0 0 0 1 X 0 0 0 0 1 1 0 0 1 1 0 1 0 1

Priority Encoder x 0 x 1 x 2 x 3 x 4 x 5 x 6 x 7 y 2 y 1 y 0 1 X X X X 0 1 X X X 0 0 0 1 X X X 0 0 0 1 X 0 0 0 0 1 1 0 0 1 1 0 1 0 1 L 7 L 6 L 5 L 4 = = x 7’x 6’x 5’x 4 y 2 = + + + L 7 L 6 L 5 L 4

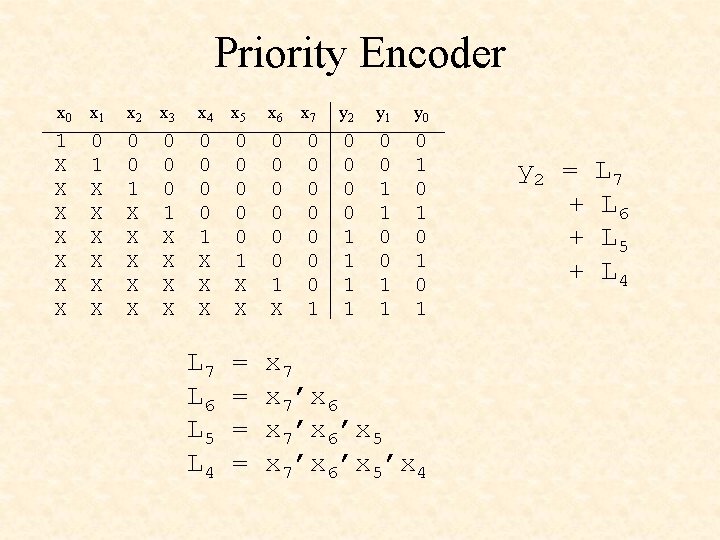

Priority Encoder x 0 x 1 x 2 x 3 x 4 x 5 x 6 x 7 y 2 y 1 y 0 1 X X X X 0 1 X X X 0 0 0 1 X X X 0 0 0 1 X 0 0 0 0 1 1 0 0 1 1 0 1 0 1 L 7 L 6 L 3 L 2 = = x 7’x 6’x 5’x 4’x 3’x 2 Y 1 = + + + L 7 L 6 L 3 L 2

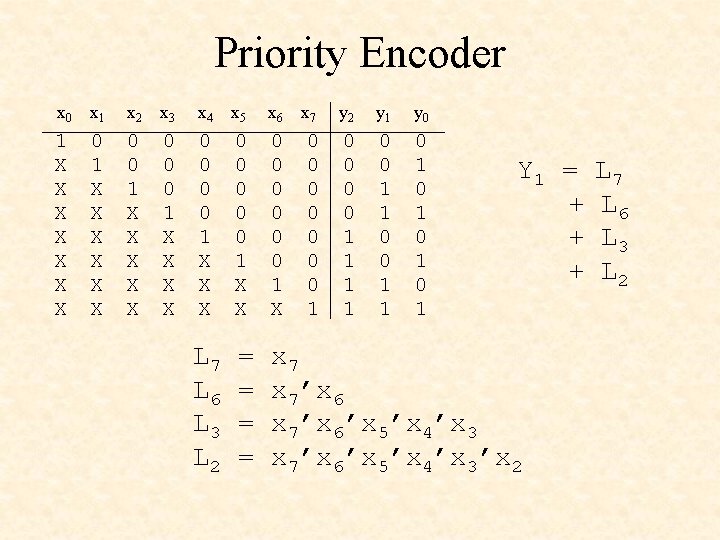

Priority Encoder x 0 x 1 x 2 x 3 x 4 x 5 x 6 x 7 y 2 y 1 y 0 1 X X X X 0 1 X X X 0 0 0 1 X X X 0 0 0 1 X 0 0 0 0 1 1 0 0 1 1 0 1 0 1 L 7 L 5 L 3 L 1 = = x 7’x 6’x 5’x 4’x 3’x 2’x 1 Y 0 = + + + L 7 L 5 L 3 L 1

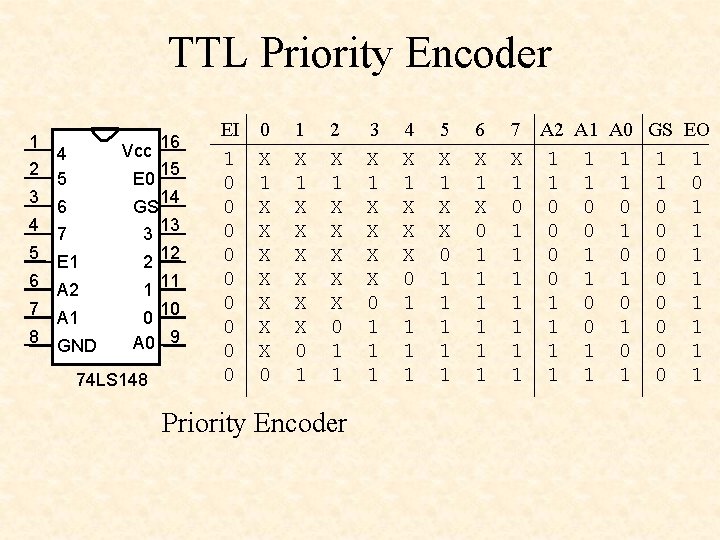

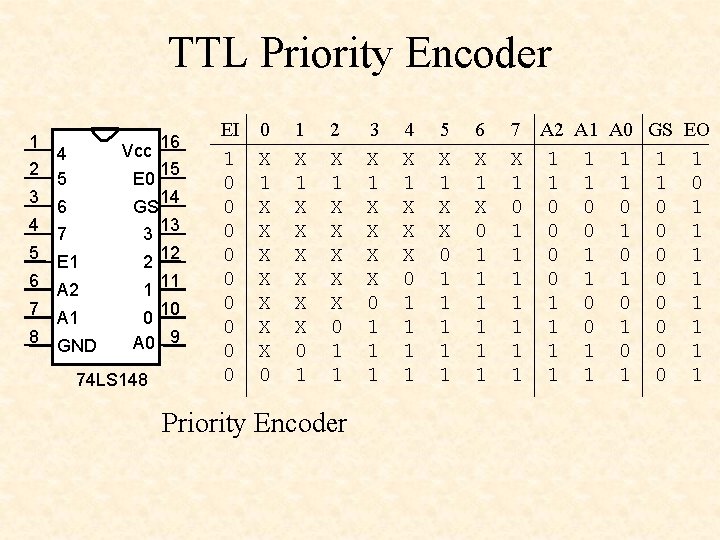

TTL Priority Encoder 1 4 2 5 3 6 4 7 5 E 1 6 A 2 7 A 1 8 GND Vcc E 0 GS 3 2 1 16 15 14 13 12 11 10 0 A 0 9 74 LS 148 EI 1 0 0 0 0 0 X 1 X X X X 0 1 2 X 1 X X X 0 1 1 Priority Encoder 3 X 1 X X 0 1 1 1 4 X 1 X X X 0 1 1 5 X 1 X X 0 1 1 1 6 X 1 X 0 1 1 1 7 A 2 A 1 A 0 GS EO X 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 0 0 1 1 1 0 1

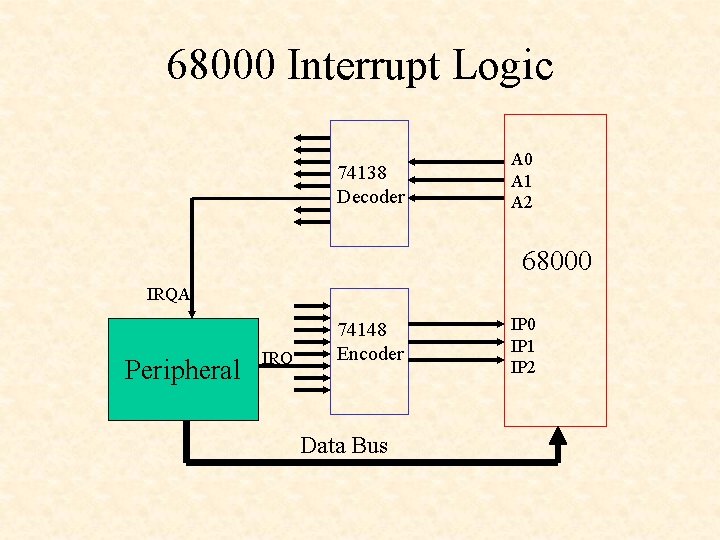

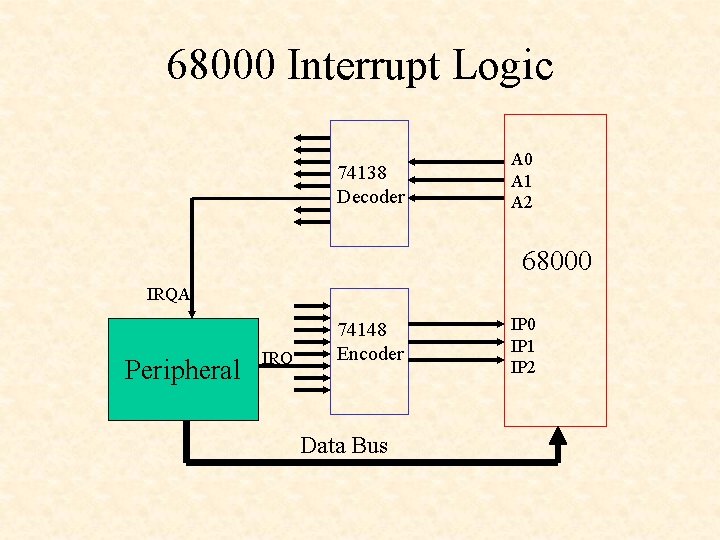

68000 Interrupt Logic 74138 Decoder A 0 A 1 A 2 68000 IRQA Peripheral IRQ 74148 Encoder Data Bus IP 0 IP 1 IP 2

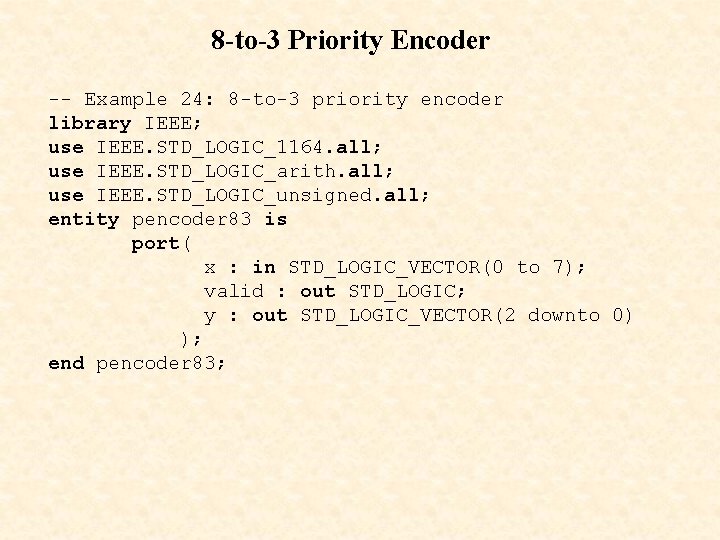

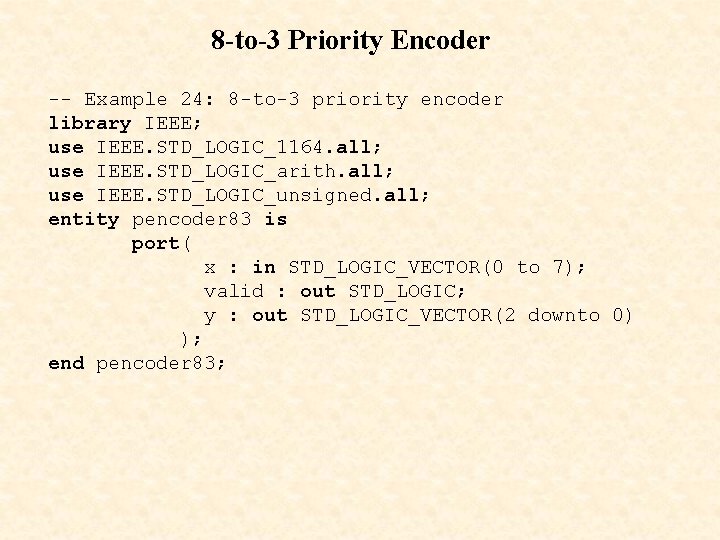

8 -to-3 Priority Encoder -- Example 24: 8 -to-3 priority encoder library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_arith. all; use IEEE. STD_LOGIC_unsigned. all; entity pencoder 83 is port( x : in STD_LOGIC_VECTOR(0 to 7); valid : out STD_LOGIC; y : out STD_LOGIC_VECTOR(2 downto 0) ); end pencoder 83;

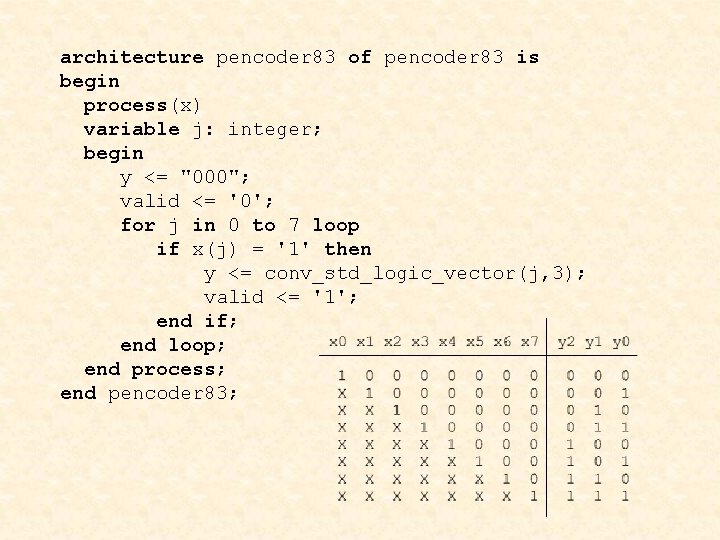

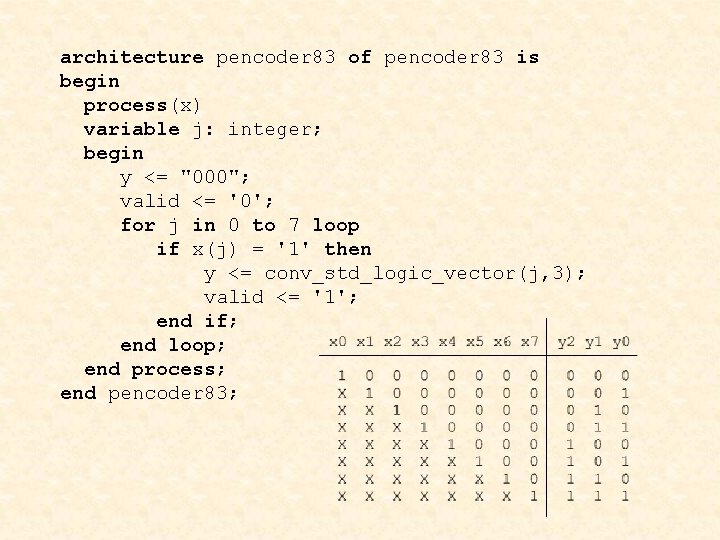

architecture pencoder 83 of pencoder 83 is begin process(x) variable j: integer; begin y <= "000"; valid <= '0'; for j in 0 to 7 loop if x(j) = '1' then y <= conv_std_logic_vector(j, 3); valid <= '1'; end if; end loop; end process; end pencoder 83;

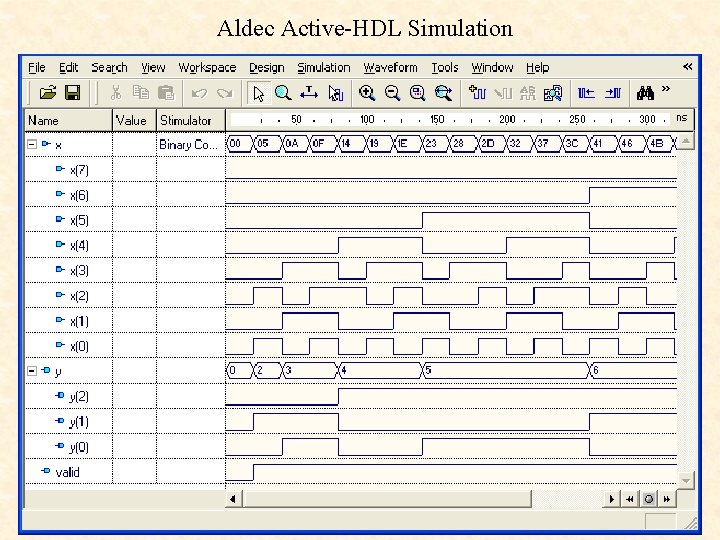

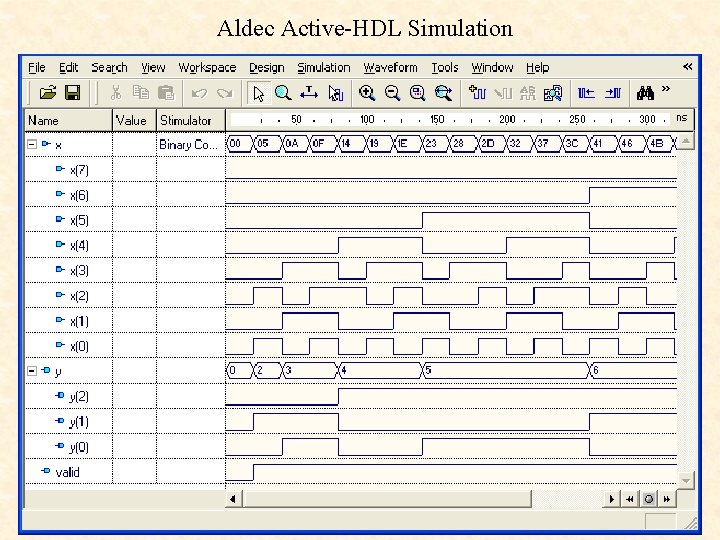

Aldec Active-HDL Simulation