Decoders and Multiplexer Circuits 91509 L 15 Decoders

- Slides: 10

Decoders and Multiplexer Circuits 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 1

Class 16 – Decoders, Multiplexers o Decoder Circuits Multiplexer Circuits o Material from section 3 -7 and 3 -10 of text o 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 2

Uses for the circuits o Distribution – information received from a single line is transmitted to one of 2 n possible output lines. Called de-multiplexing. o Consider some other specific uses. 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 3

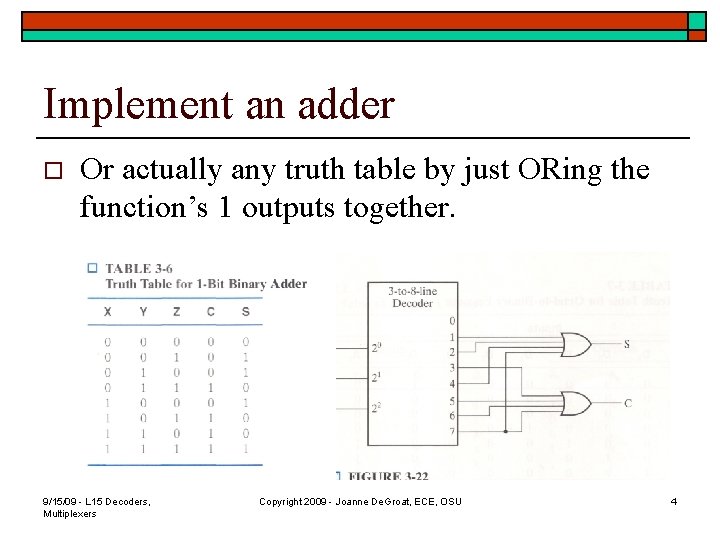

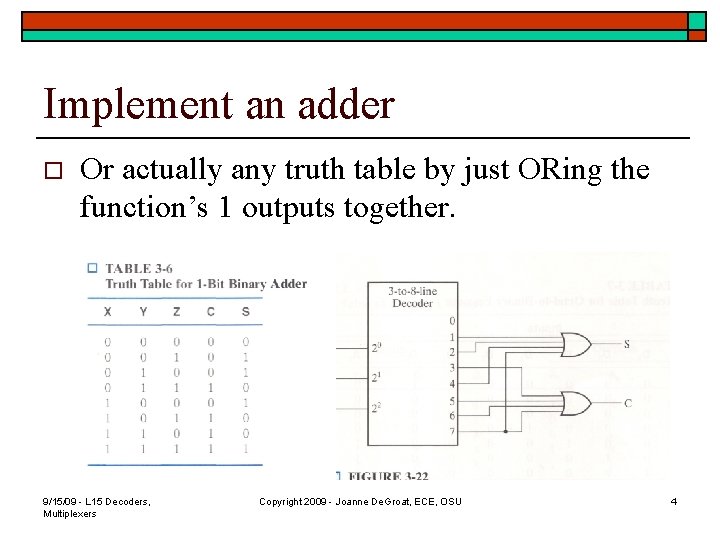

Implement an adder o Or actually any truth table by just ORing the function’s 1 outputs together. 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 4

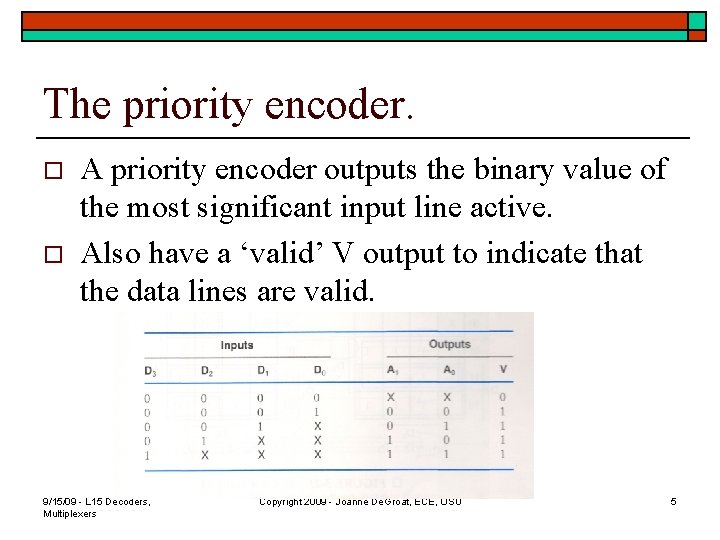

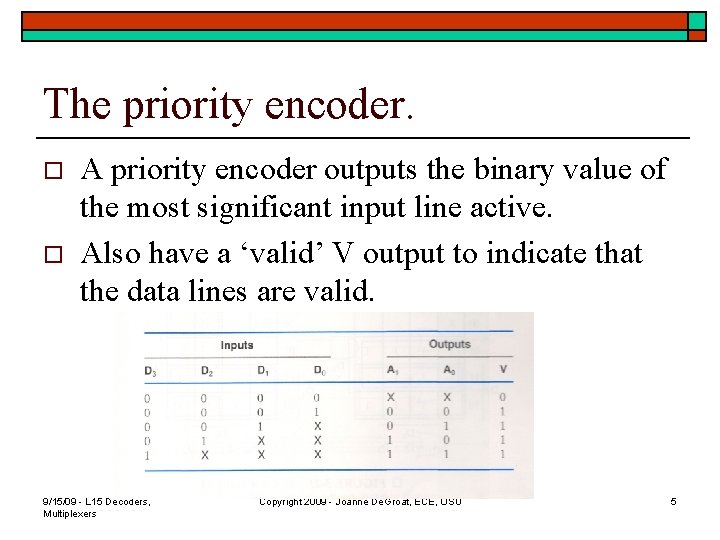

The priority encoder. o o A priority encoder outputs the binary value of the most significant input line active. Also have a ‘valid’ V output to indicate that the data lines are valid. 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 5

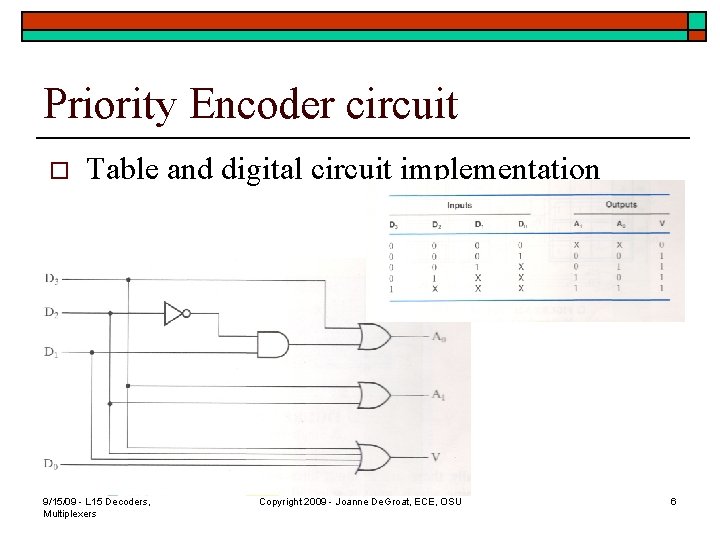

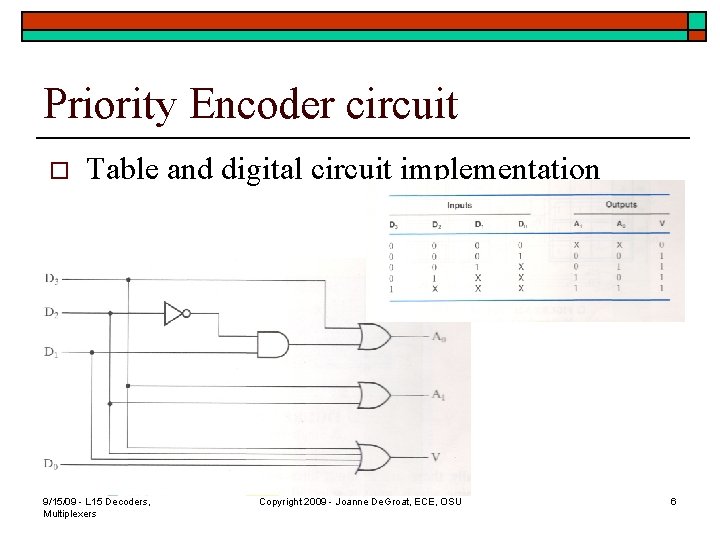

Priority Encoder circuit o Table and digital circuit implementation 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 6

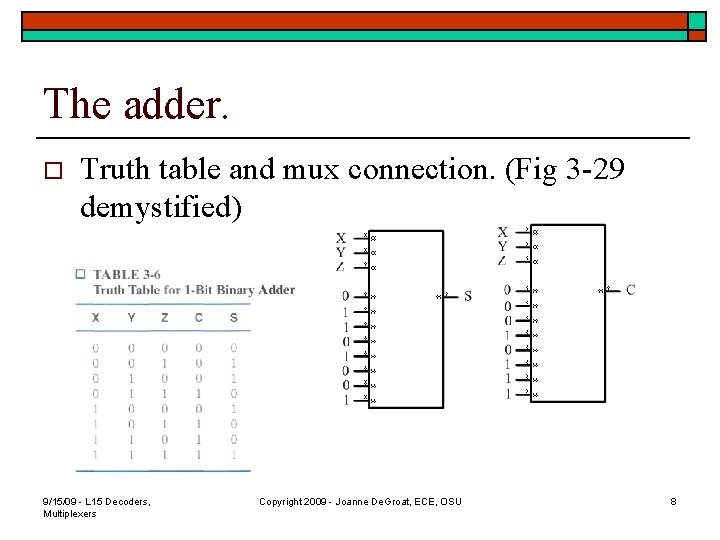

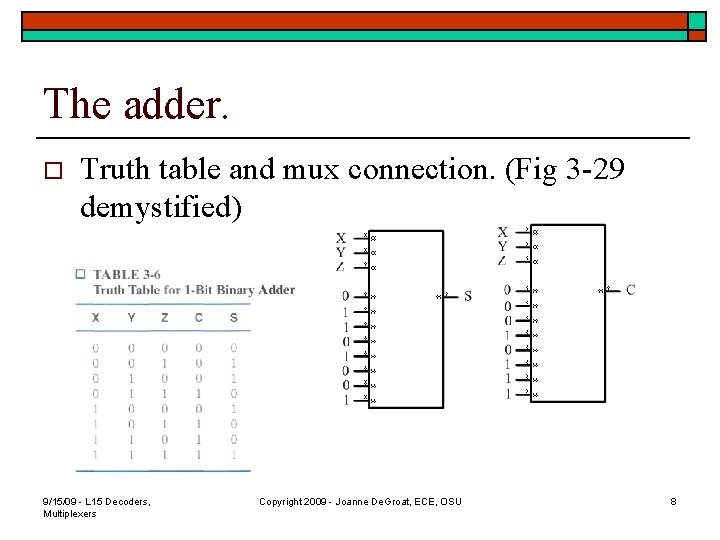

Mux and logic functions o o A m input multiplexer can implement any of the logic functions n-bits where 2 n ≤ m. Example for n=3 is the 1 -bit binary adder implemented by using two 8 -to-1 multiplexers. 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 7

The adder. o Truth table and mux connection. (Fig 3 -29 demystified) 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 8

Mux implementation in general o o o Have the truth table for n variables Have a multiplexer with n select inputs Simply map the 0’s and 1’s from the truth table to the appropriate inputs. Don’t cares could be connected either to power or ground. “From the previous, a 4 -to-1 multiplexer can implement any of the logic functions of 2 inputs. ” 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 9

Class 16 assignment o o Covered sections 3 -7 through 3 -10 Problems for hand in n o Problems for practice n o none 3 -28, 33, 37, 44, 46, 48 (same as Class 15) Reading for next class: sections 4 -1, 4 -2 9/15/09 - L 15 Decoders, Multiplexers Copyright 2009 - Joanne De. Groat, ECE, OSU 10