CS 444544 Operating Systems II Paging and Virtual

![In kern/entrypgdir. c 0 xf 0001000 will consult entry_pgtable[1] -> 0 x 001000 | In kern/entrypgdir. c 0 xf 0001000 will consult entry_pgtable[1] -> 0 x 001000 |](https://slidetodoc.com/presentation_image_h/080f2f6a0ba1602ba600a520e580382f/image-21.jpg)

![Pros/Cons of Segmentation • Pros • Easy implementation (in hardware) • Select [Base address] Pros/Cons of Segmentation • Pros • Easy implementation (in hardware) • Select [Base address]](https://slidetodoc.com/presentation_image_h/080f2f6a0ba1602ba600a520e580382f/image-54.jpg)

- Slides: 58

CS 444/544 Operating Systems II Paging and Virtual Memory Translation Yeongjin Jang 1

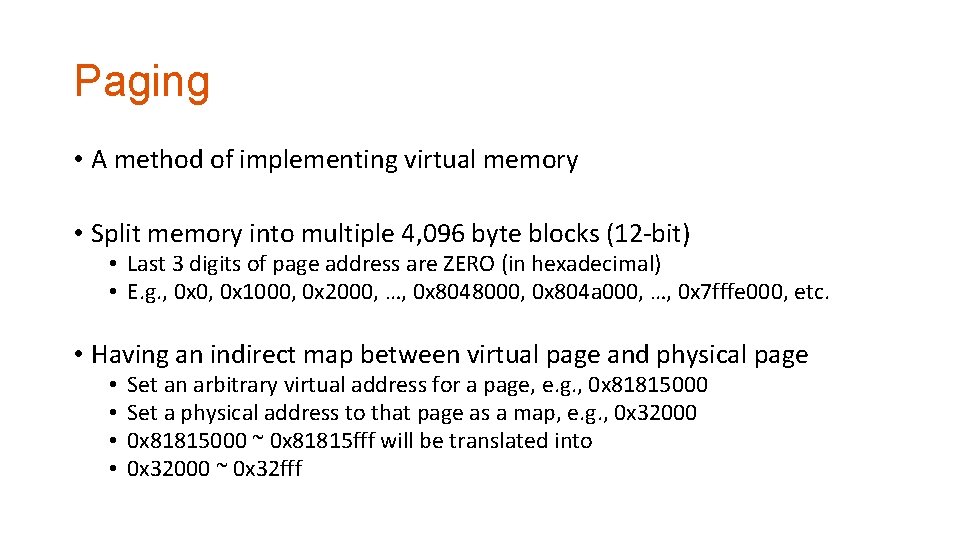

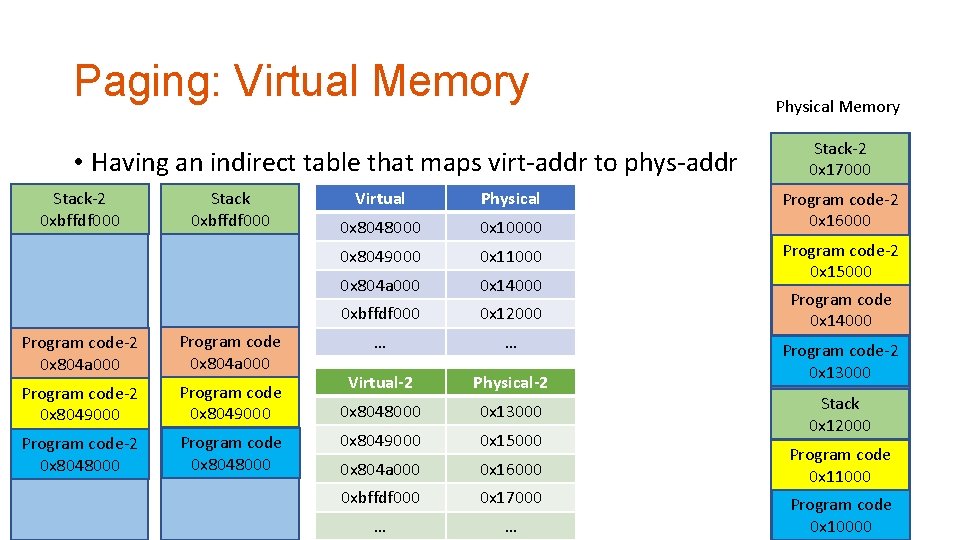

Protected Mode Summary • Segment access via GDT • Base + Offset, if Offset < Limit * 4096 (if G == 1) • Base + Offset, if Offset < Limit (if G == 0) • Last two bits in %cs - CPL • Memory Privilege - Ring level • 0 for OS kernel • 3 for user application • Changing CR 0 to enable protected mode • CR 0_PE_ON == 1, set via eax • Changing CPL? • ljmp %cs: xxxxx, set the last 2 bits of %cs as 0 for kernel, 3 for user 2

Virtual Memory • Three goals • Transparency: does not need to know system’s internal state • Program A is loaded at 0 x 8048000. Can Program B be loaded at 0 x 8048000? • Efficiency: do not waste memory; manage memory fragmentation • Can Program B (288 KB) be loaded if 288 KB of memory is free, regardless of its allocation? • Protection: isolate program’s execution environment • Can we prevent an overflow from Program A from overwriting Program B’s data? 3

Paging • A method of implementing virtual memory • Split memory into multiple 4, 096 byte blocks (12 -bit) • Last 3 digits of page address are ZERO (in hexadecimal) • E. g. , 0 x 0, 0 x 1000, 0 x 2000, …, 0 x 8048000, 0 x 804 a 000, …, 0 x 7 fffe 000, etc. • Having an indirect map between virtual page and physical page • • Set an arbitrary virtual address for a page, e. g. , 0 x 81815000 Set a physical address to that page as a map, e. g. , 0 x 32000 0 x 81815000 ~ 0 x 81815 fff will be translated into 0 x 32000 ~ 0 x 32 fff

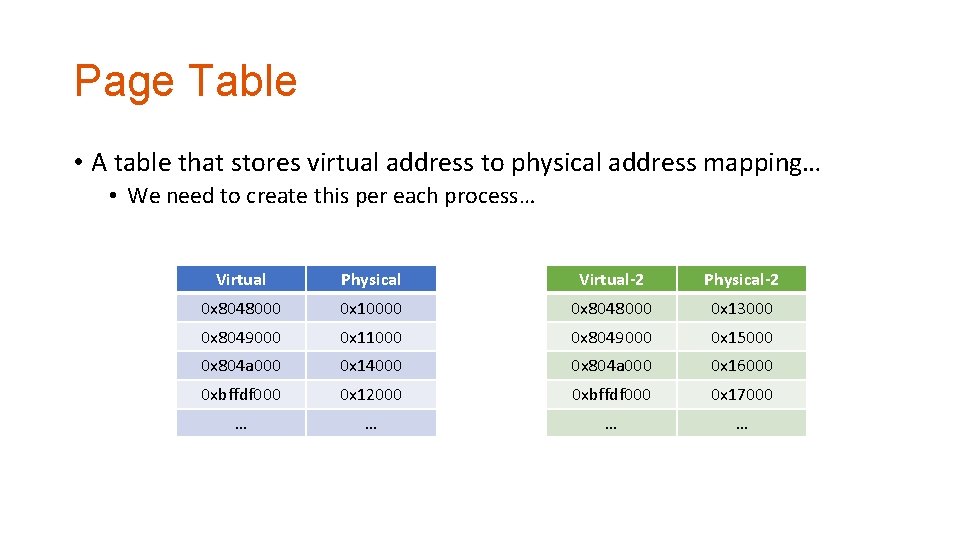

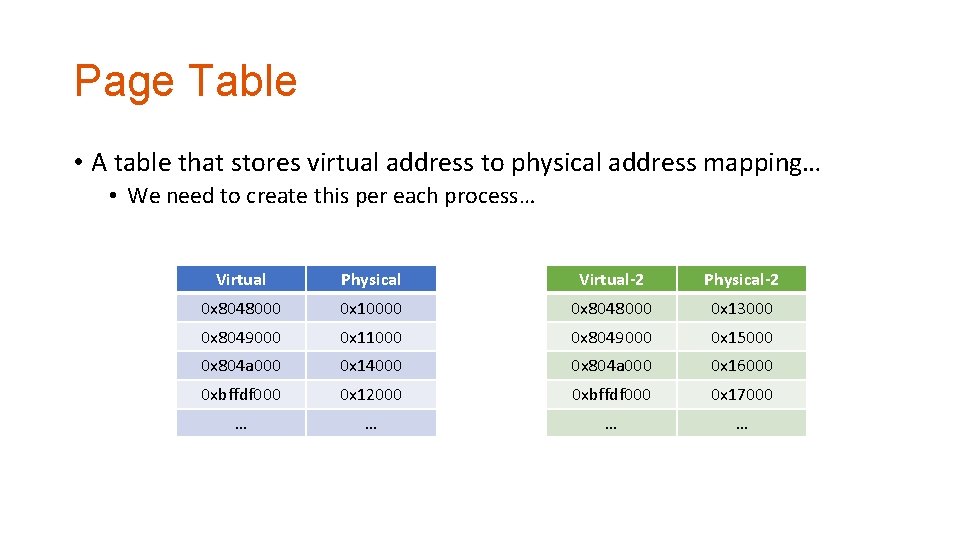

Page Table • A table that stores virtual address to physical address mapping… • We need to create this per each process… Virtual Physical Virtual-2 Physical-2 0 x 8048000 0 x 10000 0 x 8048000 0 x 13000 0 x 8049000 0 x 11000 0 x 8049000 0 x 15000 0 x 804 a 000 0 x 14000 0 x 804 a 000 0 x 16000 0 xbffdf 000 0 x 12000 0 xbffdf 000 0 x 17000 … …

Paging: Virtual Memory • Having an indirect table that maps virt-addr to phys-addr Stack-2 0 xbffdf 000 Stack 0 xbffdf 000 Program code-2 0 x 804 a 000 Program code-2 0 x 8049000 Program code-2 0 x 8048000 Program code 0 x 8048000 Virtual Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 14000 0 xbffdf 000 0 x 12000 … … Virtual-2 Physical-2 0 x 8048000 0 x 13000 0 x 8049000 0 x 15000 0 x 804 a 000 0 x 16000 0 xbffdf 000 0 x 17000 … … Physical Memory Stack-2 0 x 17000 Program code-2 0 x 16000 Program code-2 0 x 15000 Program code 0 x 14000 Program code-2 0 x 13000 Stack 0 x 12000 Program code 0 x 11000 Program code 0 x 10000

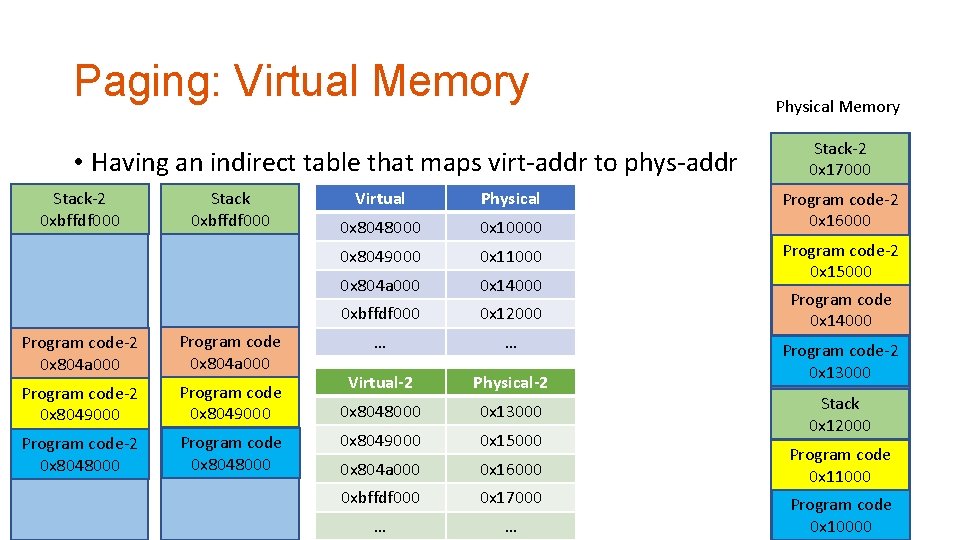

x 86 Memory Access

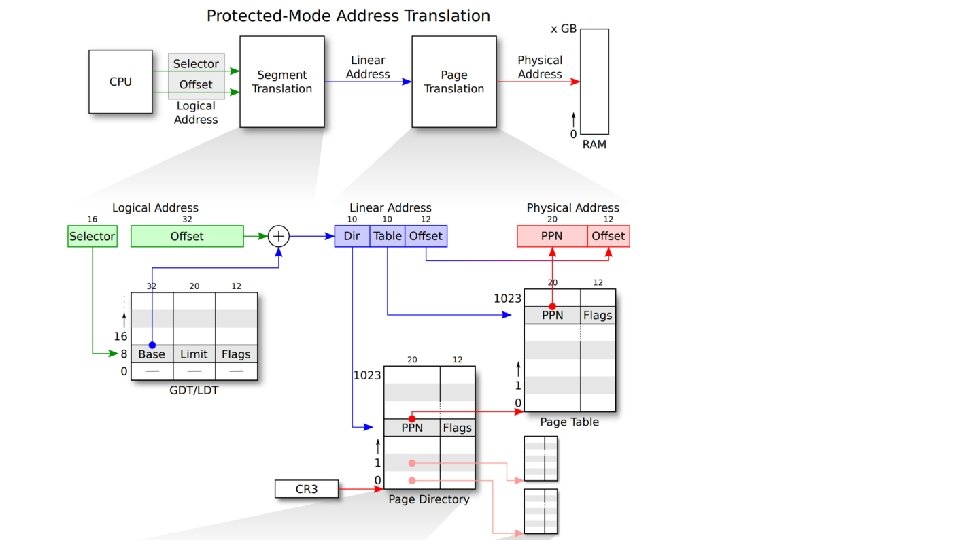

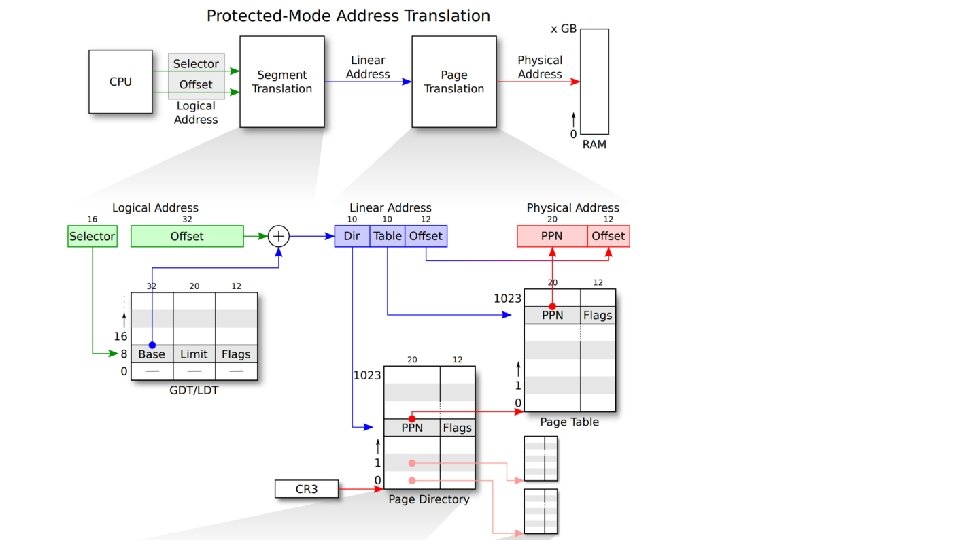

Page Directory / Table • We access page table by virtual address • Page size: 4 KB (12 bits) 31 12 Page number • Page number: 20 bits • What is the page number and offset of • 0 x 8048000 • 0 xb 7 ff 3100 8 0 Offset

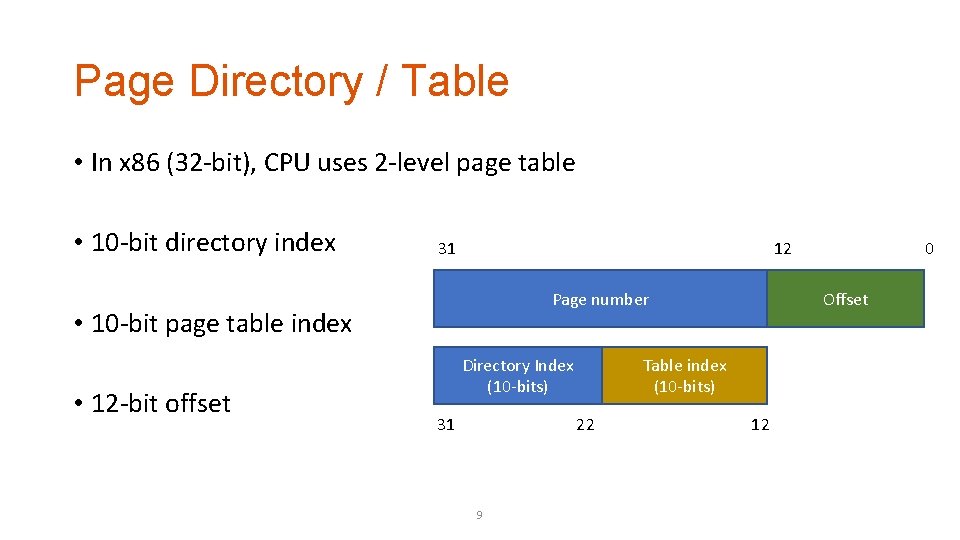

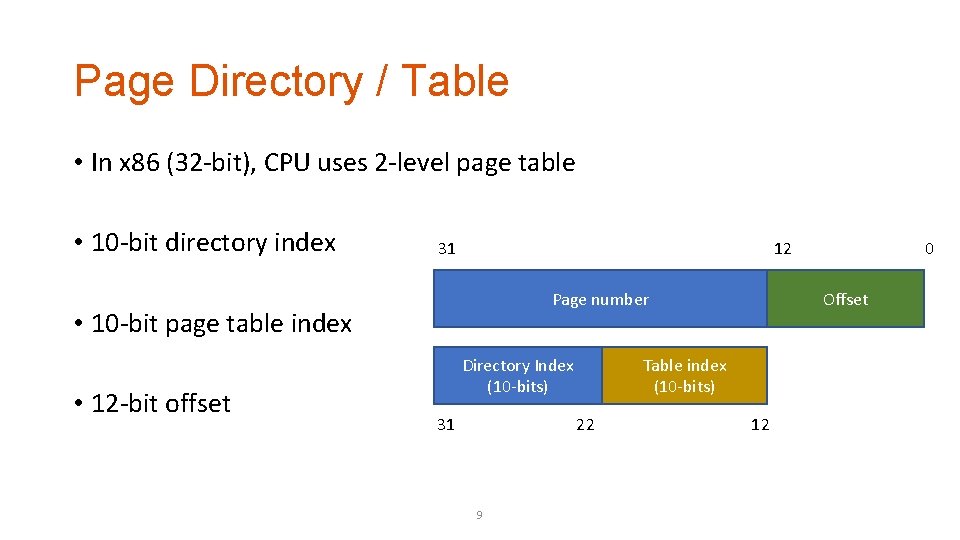

Page Directory / Table • In x 86 (32 -bit), CPU uses 2 -level page table • 10 -bit directory index 31 12 • 12 -bit offset Offset Page number • 10 -bit page table index Directory Index (10 -bits) Table index (10 -bits) 22 31 9 0 12

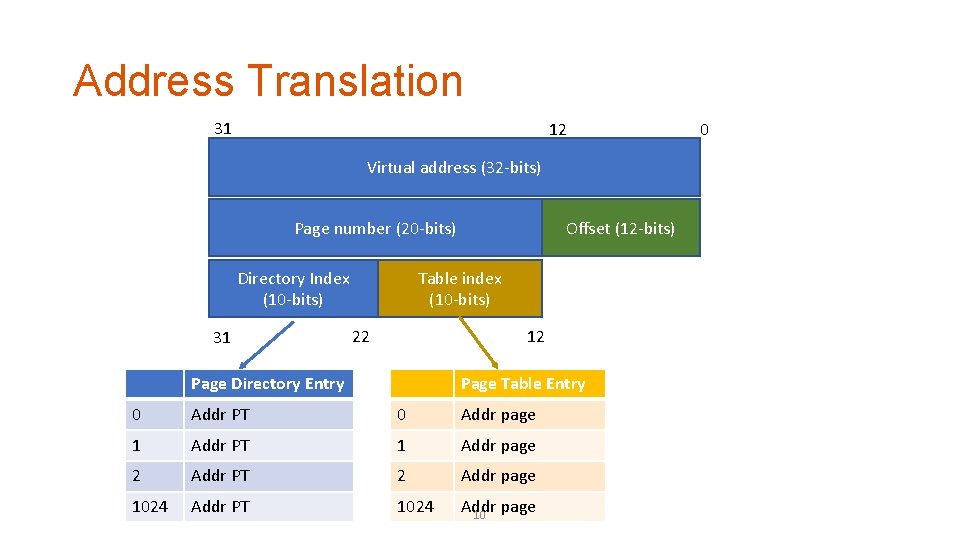

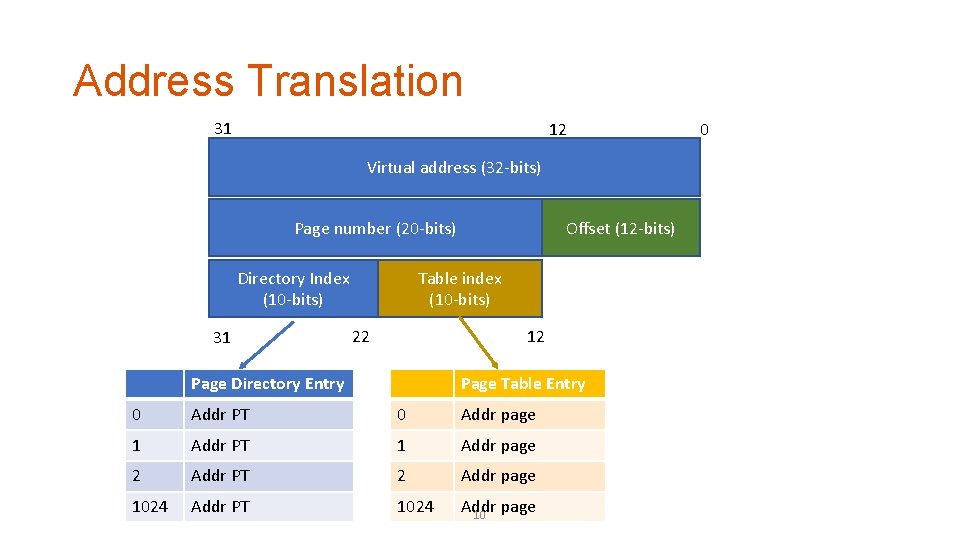

Address Translation 31 12 Virtual address (32 -bits) Offset (12 -bits) Page number (20 -bits) Directory Index (10 -bits) 31 Table index (10 -bits) 22 12 Page Directory Entry Page Table Entry 0 Addr PT 0 Addr page 1 Addr PT 1 Addr page 2 Addr PT 2 Addr page 1024 Addr PT 1024 Addr page 10 0

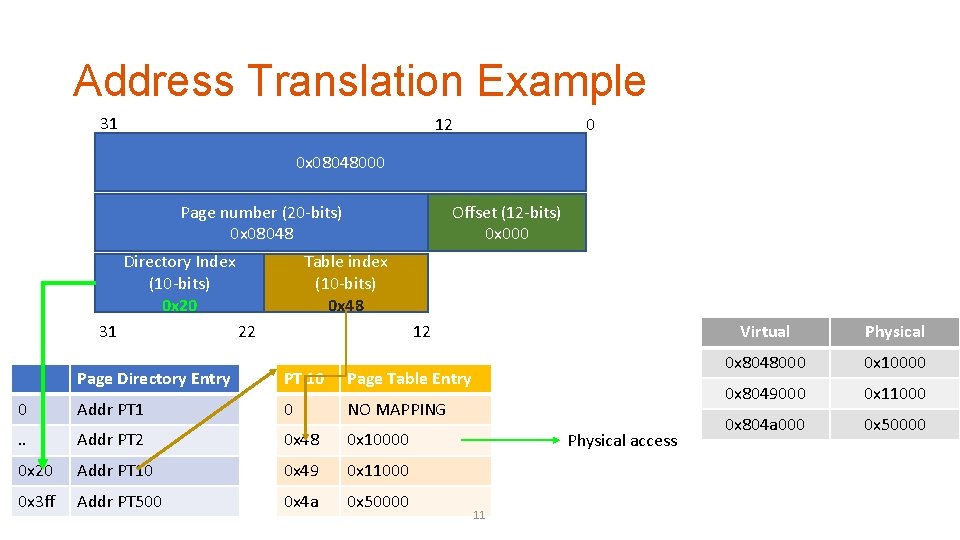

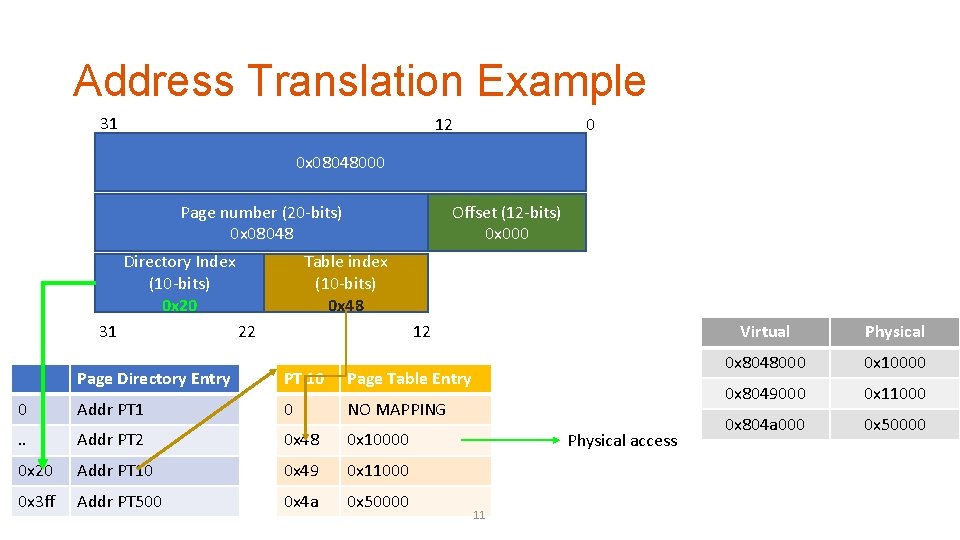

Address Translation Example 31 12 0 0 x 08048000 Offset (12 -bits) 0 x 000 Page number (20 -bits) 0 x 08048 Directory Index (10 -bits) 0 x 20 31 Table index (10 -bits) 0 x 48 22 12 Page Directory Entry PT 10 Page Table Entry 0 Addr PT 1 0 NO MAPPING . . Addr PT 2 0 x 48 0 x 10000 0 x 20 Addr PT 10 0 x 49 0 x 11000 0 x 3 ff Addr PT 500 0 x 4 a 0 x 50000 Physical access 11 Virtual Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 50000

Page Table Entry • Address translation is from virtual page to physical page • E. g. , 0 x 8048000 -> 0 x 11000 • We do not need to translate lower 12 bits • E. g. , 0 x 8048001 -> 0 x 8048000 + 0 x 001 -> 0 x 11000 + 0 x 001 • So page table entry only uses higher 20 bits to store physical page address • Lower 12 bits remaining as the same • We do not translate the lower 12 bits! 12

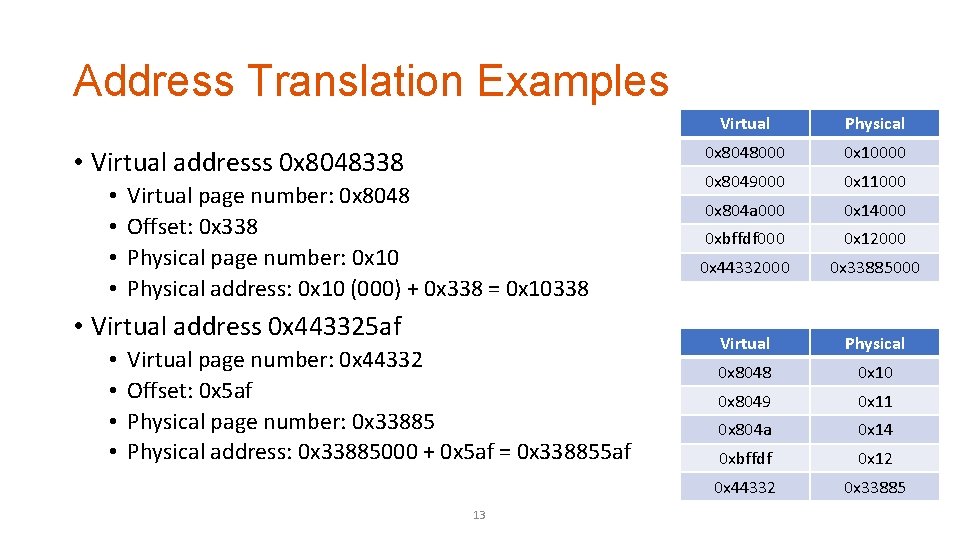

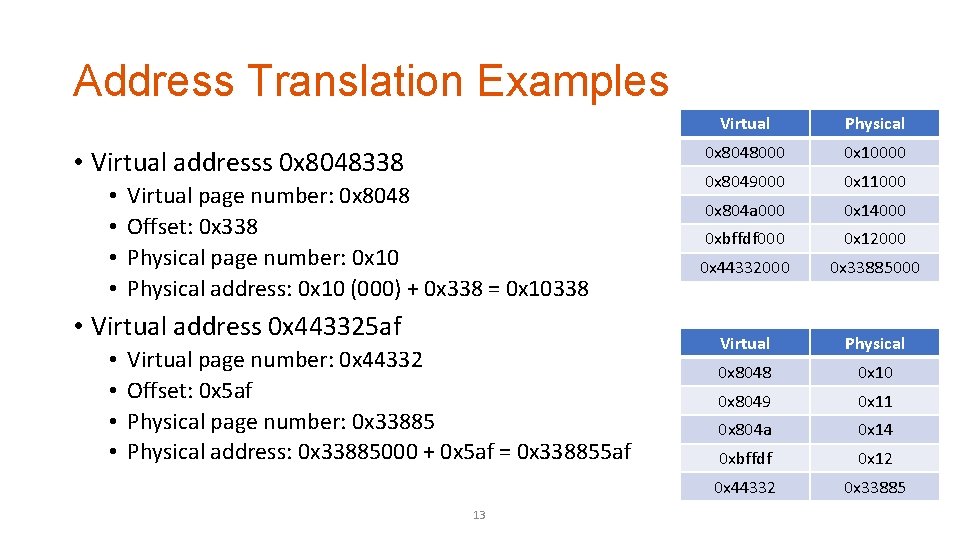

Address Translation Examples • Virtual addresss 0 x 8048338 • • Virtual page number: 0 x 8048 Offset: 0 x 338 Physical page number: 0 x 10 Physical address: 0 x 10 (000) + 0 x 338 = 0 x 10338 • Virtual address 0 x 443325 af • • Virtual page number: 0 x 44332 Offset: 0 x 5 af Physical page number: 0 x 33885 Physical address: 0 x 33885000 + 0 x 5 af = 0 x 338855 af 13 Virtual Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 14000 0 xbffdf 000 0 x 12000 0 x 44332000 0 x 33885000 Virtual Physical 0 x 8048 0 x 10 0 x 8049 0 x 11 0 x 804 a 0 x 14 0 xbffdf 0 x 12 0 x 44332 0 x 33885

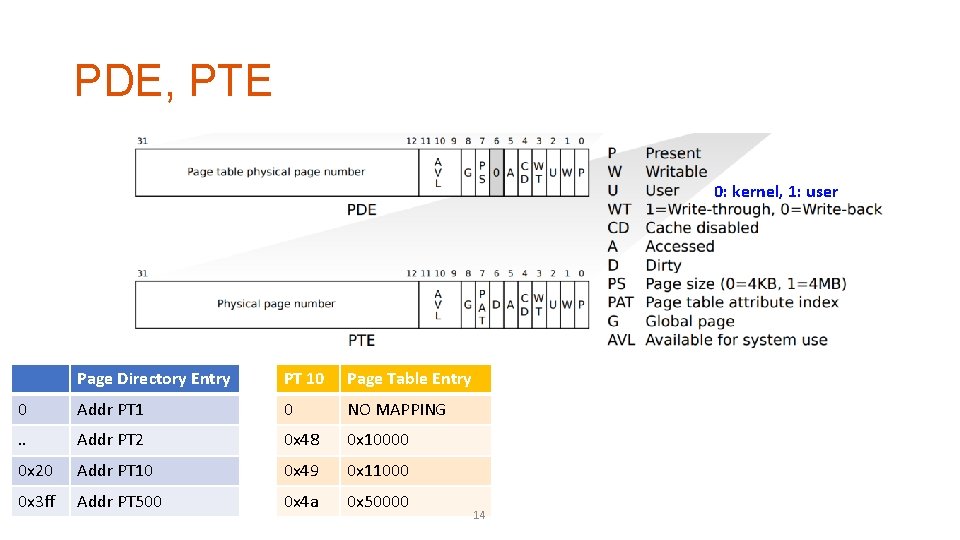

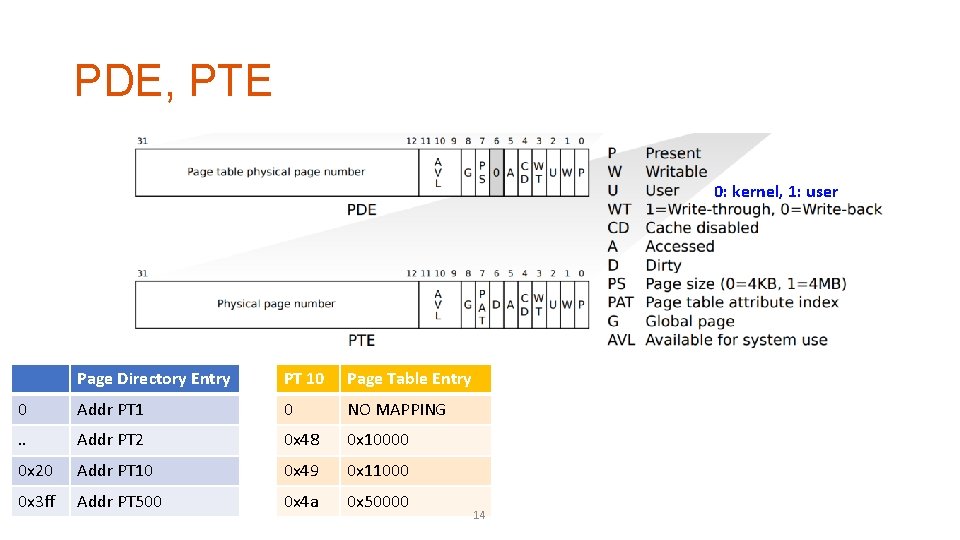

PDE, PTE 0: kernel, 1: user Page Directory Entry PT 10 Page Table Entry 0 Addr PT 1 0 NO MAPPING . . Addr PT 2 0 x 48 0 x 10000 0 x 20 Addr PT 10 0 x 49 0 x 11000 0 x 3 ff Addr PT 500 0 x 4 a 0 x 50000 14

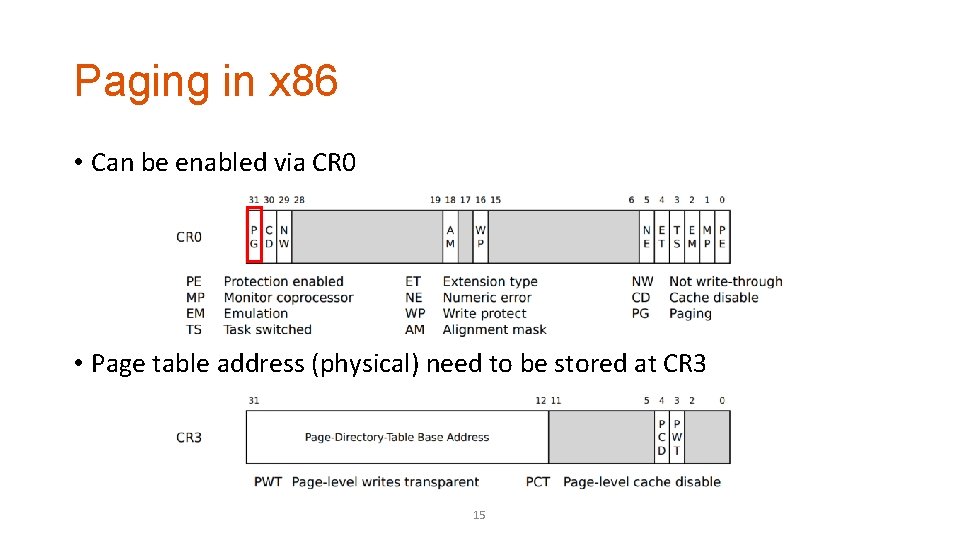

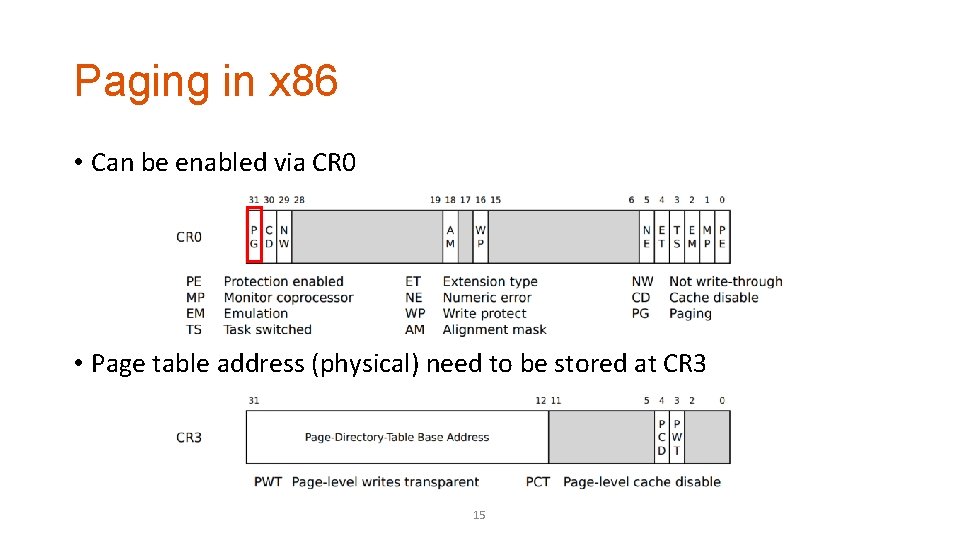

Paging in x 86 • Can be enabled via CR 0 • Page table address (physical) need to be stored at CR 3 15

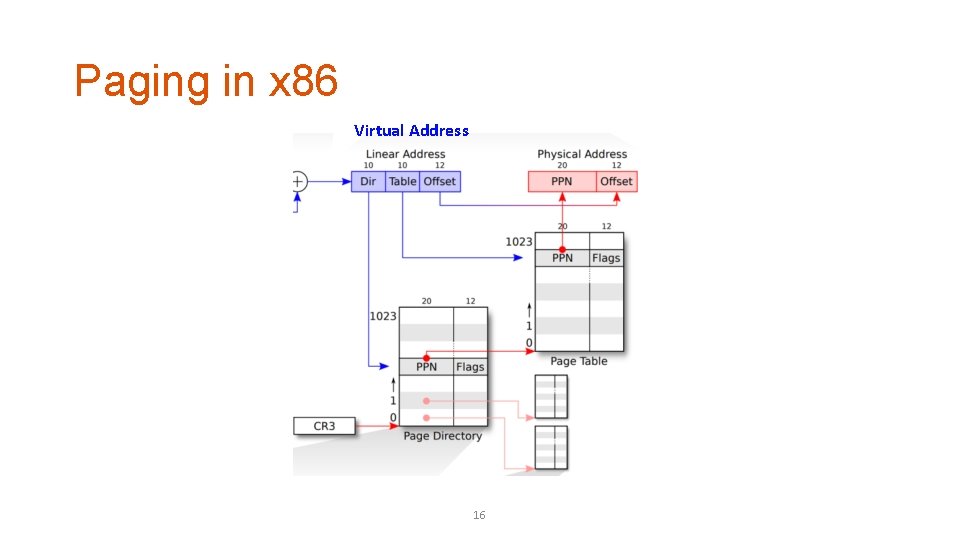

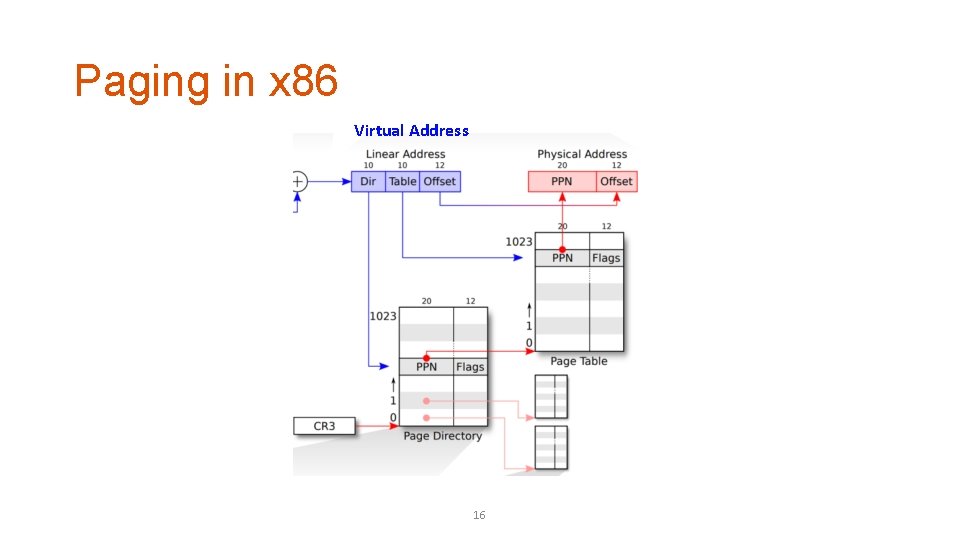

Paging in x 86 Virtual Address 16

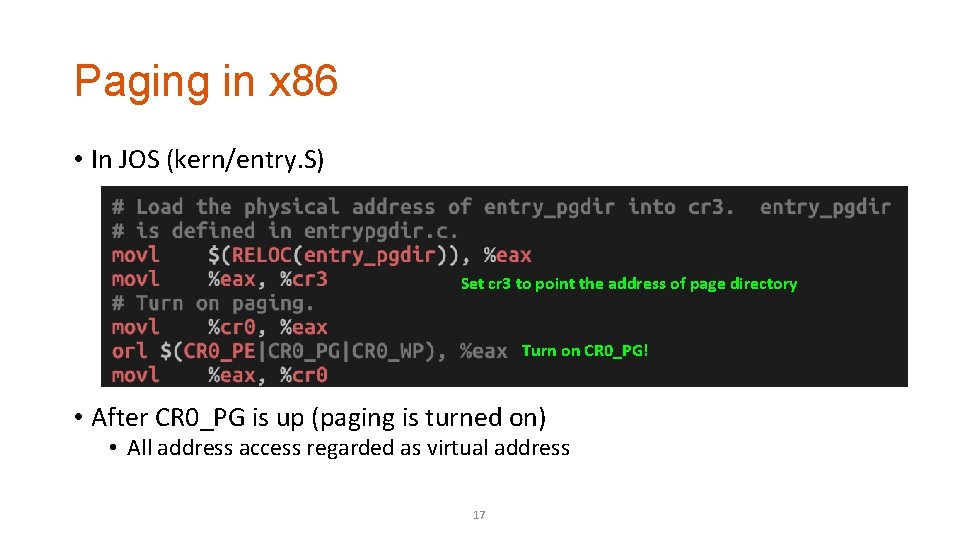

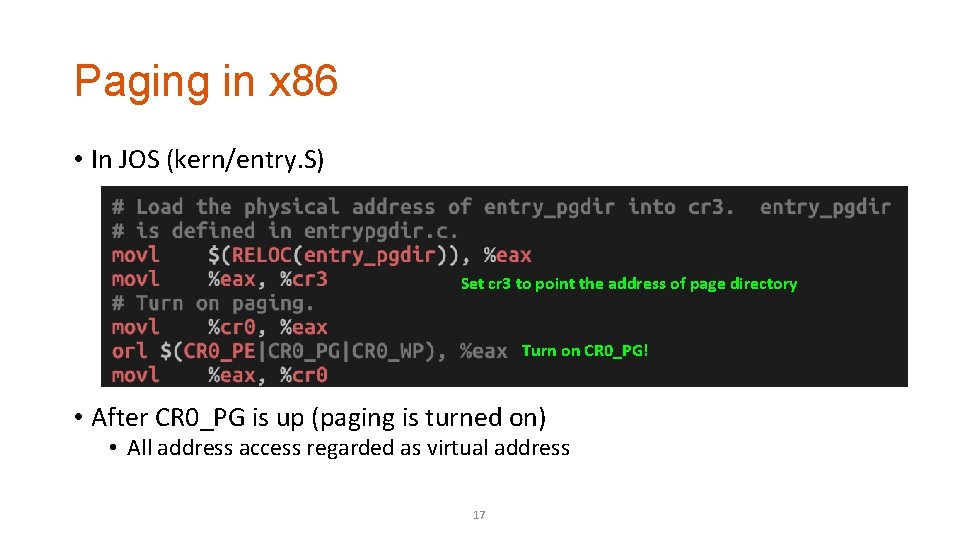

Paging in x 86 • In JOS (kern/entry. S) Set cr 3 to point the address of page directory Turn on CR 0_PG! • After CR 0_PG is up (paging is turned on) • All address access regarded as virtual address 17

How can we access physical address • After CR 0_PG is up (paging is turned on) • All address access regarded as virtual address • What if we would like to access the physical address 0 x 100010? • Our kernel is at physical address 0 x 100000 ~ 0 x 110000 • What’s the virtual addresses of those area? 18

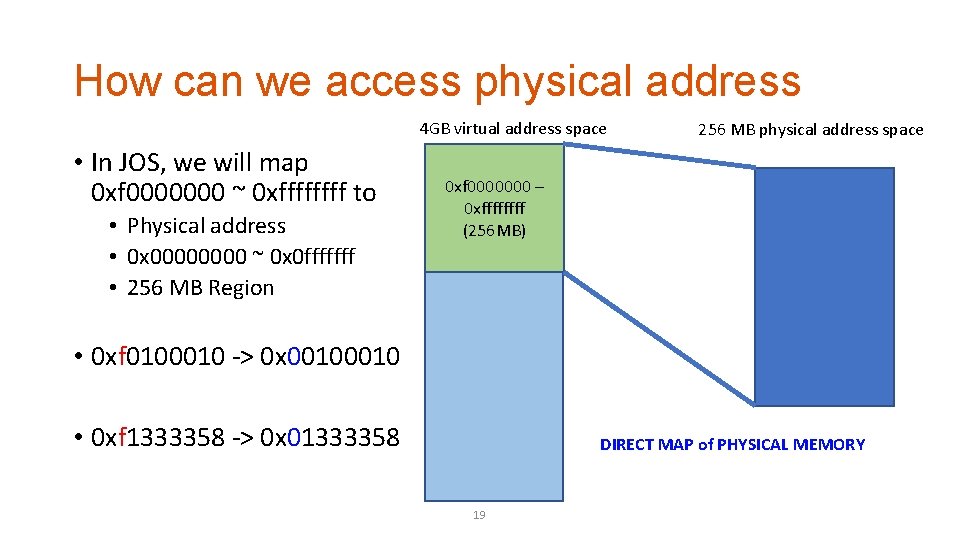

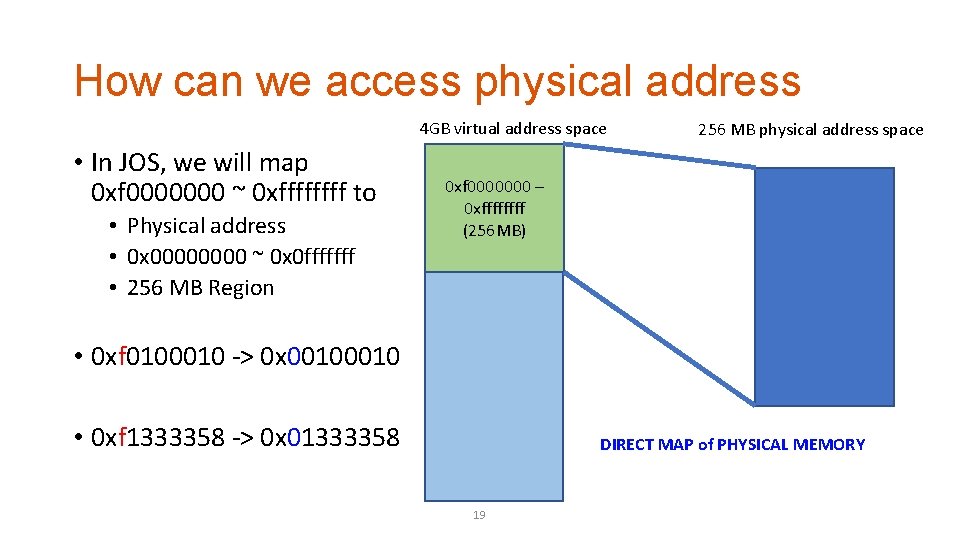

How can we access physical address 4 GB virtual address space • In JOS, we will map 0 xf 0000000 ~ 0 xffff to • Physical address • 0 x 0000 ~ 0 x 0 fffffff • 256 MB Region 256 MB physical address space 0 xf 0000000 – 0 xffff (256 MB) • 0 xf 0100010 -> 0 x 0010 • 0 xf 1333358 -> 0 x 01333358 DIRECT MAP of PHYSICAL MEMORY 19

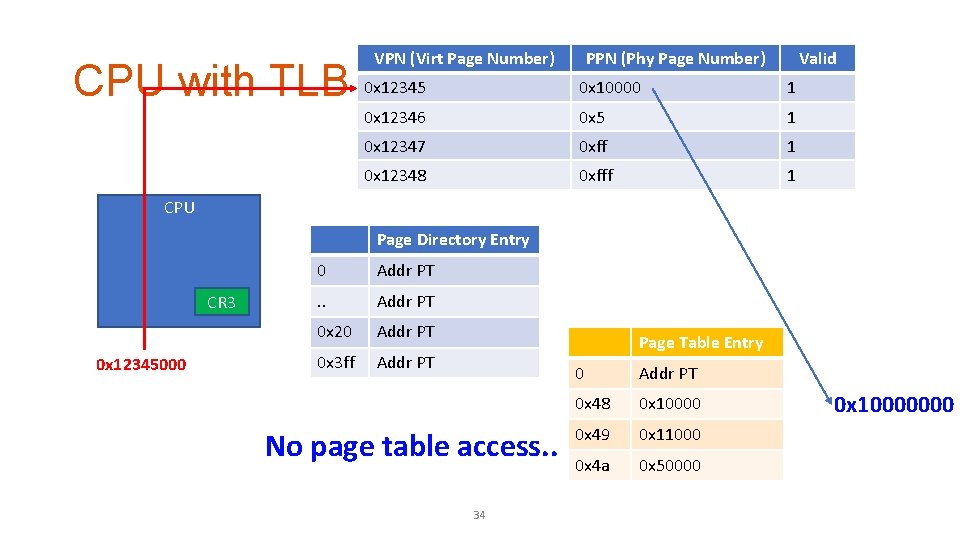

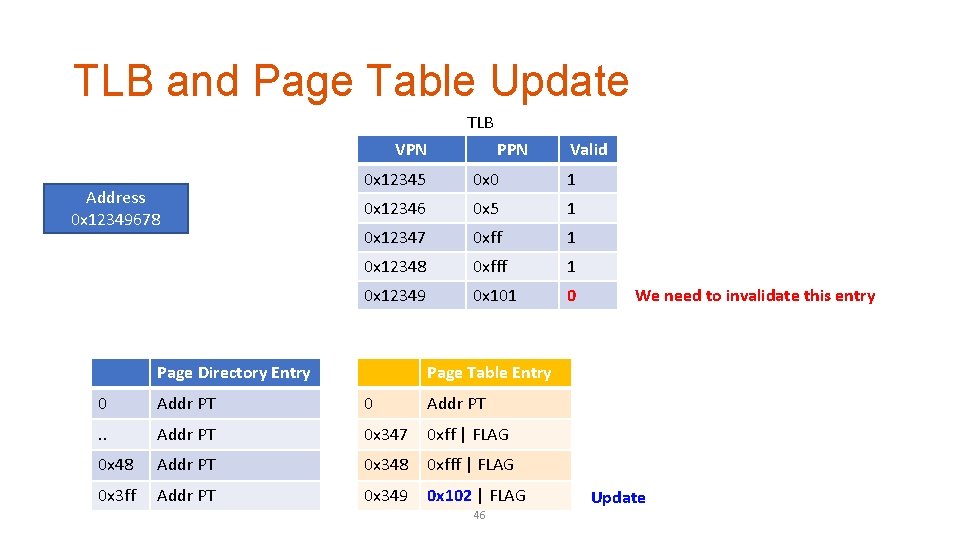

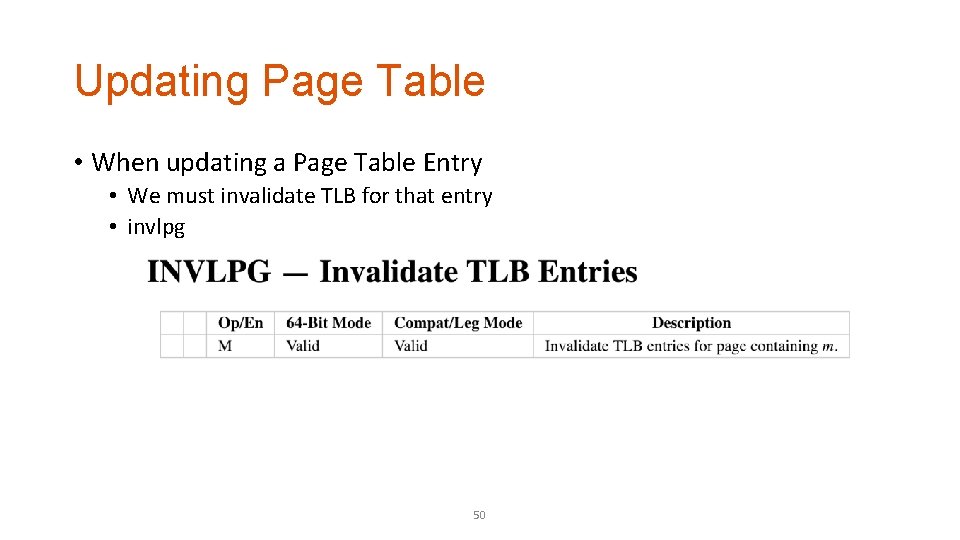

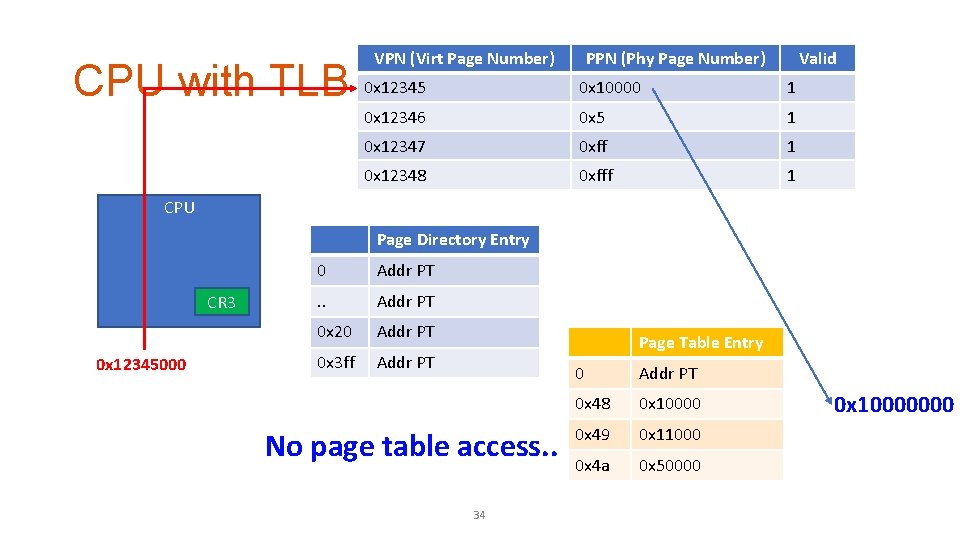

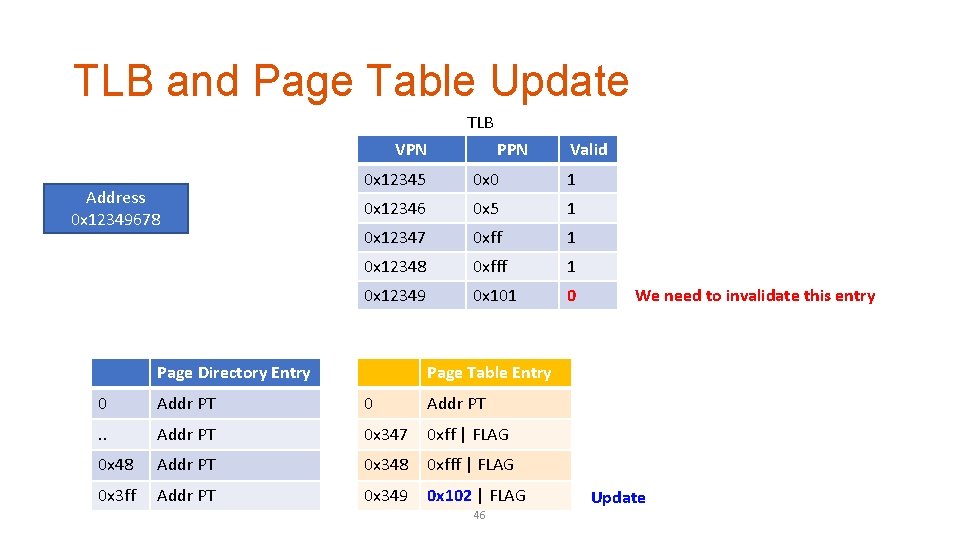

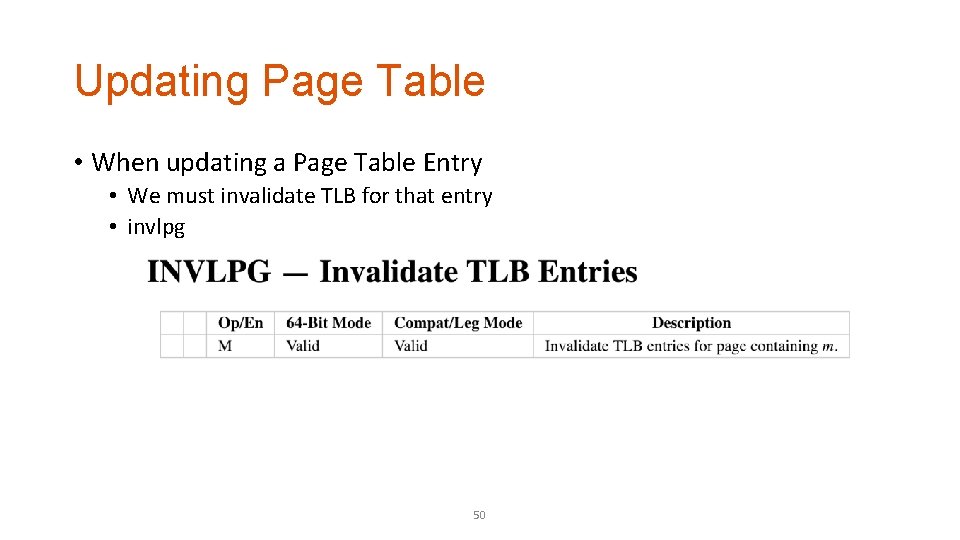

In kern/entrypgdir. c Entry_pgdir only contains two entries; 0 ~ 0 x 400000 to 0 ~ 0 x 400000 (not writable) 0 xf 0000000 ~ 0 xf 0400000 to 0 ~ 0 x 400000 (writable) 20

![In kernentrypgdir c 0 xf 0001000 will consult entrypgtable1 0 x 001000 In kern/entrypgdir. c 0 xf 0001000 will consult entry_pgtable[1] -> 0 x 001000 |](https://slidetodoc.com/presentation_image_h/080f2f6a0ba1602ba600a520e580382f/image-21.jpg)

In kern/entrypgdir. c 0 xf 0001000 will consult entry_pgtable[1] -> 0 x 001000 | PTE_P | PTE_W Phyaddr: 0 x 1000 21

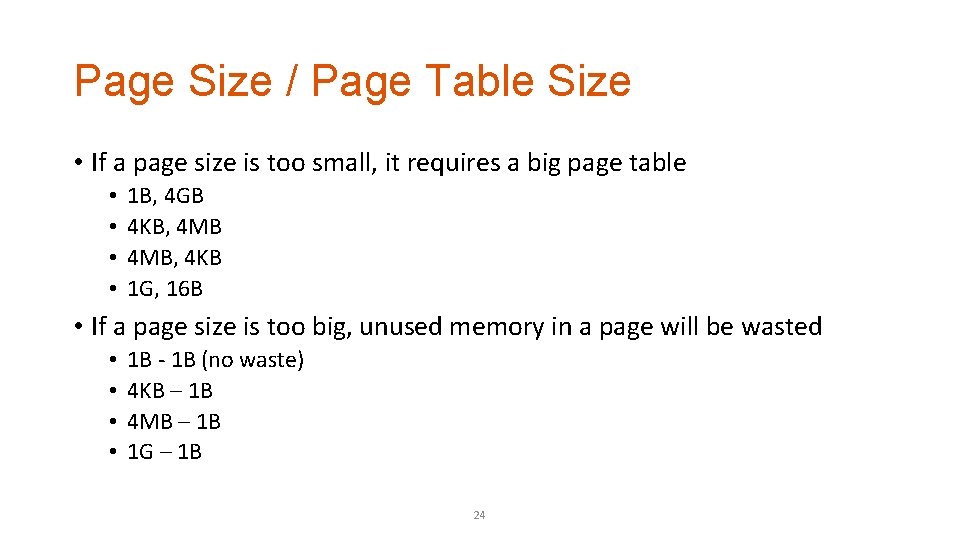

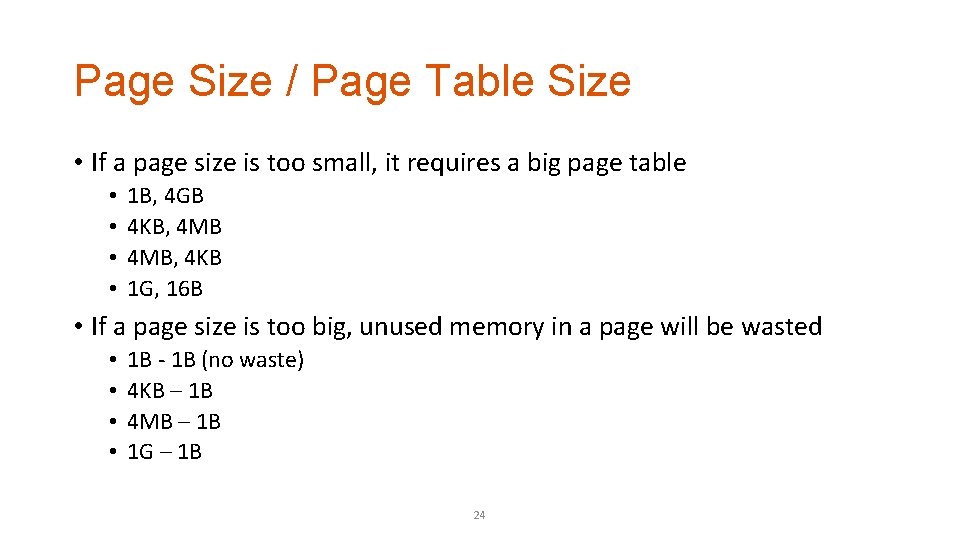

Page • A page • A 4, 096 (4 KB) block of memory • Why having a block? • How large does the page table should be to map 4 GB (32 -bit space)? • • If a block is 1 GB – 4 entries * pointer (32 -bit, 4 byte) = 16 byte long If a block is 4 MB – 1024 entries * pointer = 4, 096 bytes, 4 KB long If a block is 4 KB – 1048576 entries * pointer = 4 MB long If a block is 1 byte – 4294967296 entries = 4 GB… NONO… Design consideration: Size of page table matters! 22 Virtual Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 50000

Page (cont’d) • A page • A 4, 096 (4 KB) block of memory • Why 4 KB in Intel x 86? • How much memory do you need to allocate 1 byte? • • 1 GB page – 1 GB 4 MB page – 4 MB 4 KB page – 4 KB 1 B page – 1 B Design consideration: Memory fragmentation matters! 23 Virtual Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 50000

Page Size / Page Table Size • If a page size is too small, it requires a big page table • • 1 B, 4 GB 4 KB, 4 MB, 4 KB 1 G, 16 B • If a page size is too big, unused memory in a page will be wasted • • 1 B - 1 B (no waste) 4 KB – 1 B 4 MB – 1 B 1 G – 1 B 24

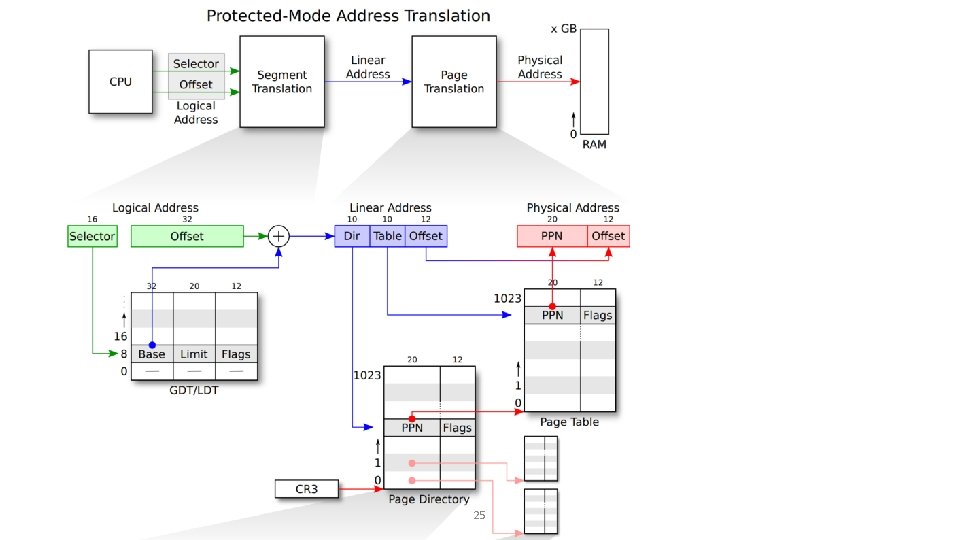

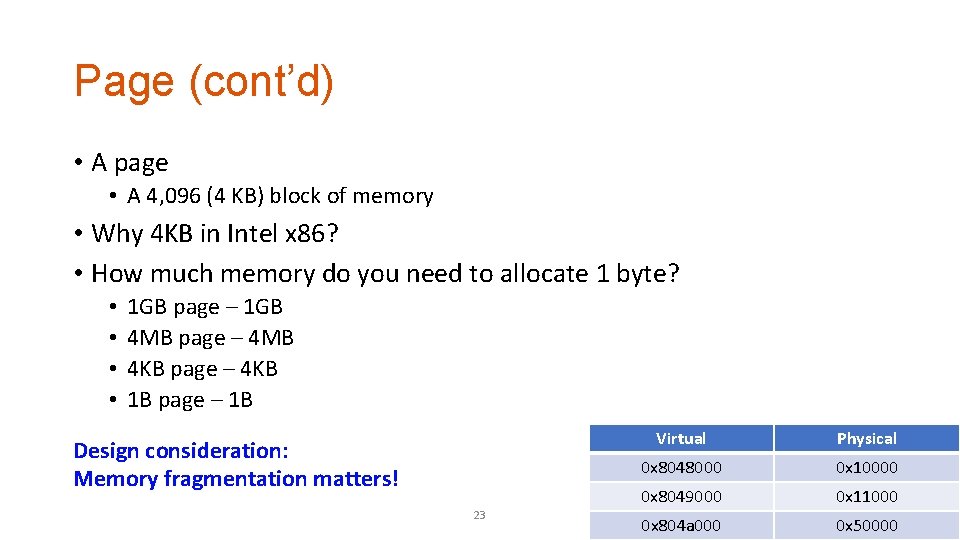

x 86 Memory Access 25

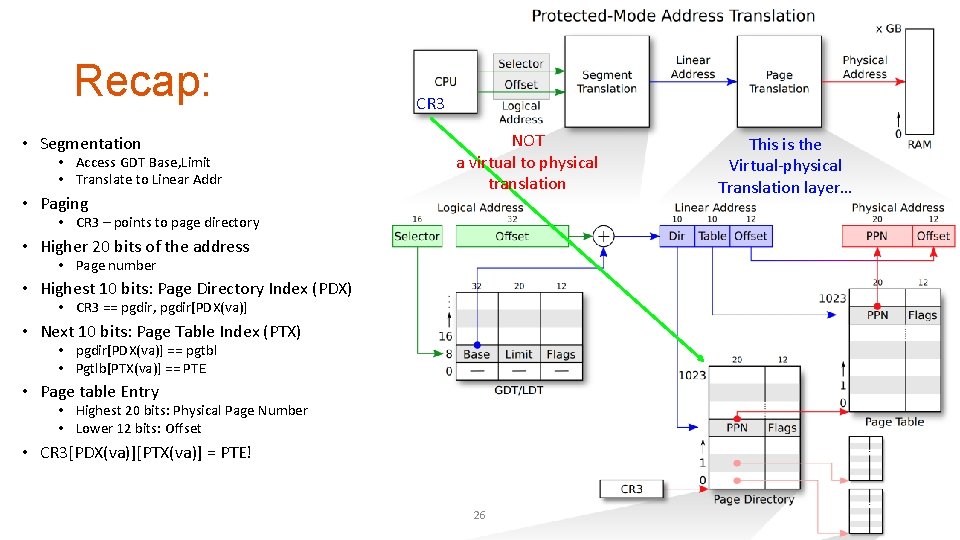

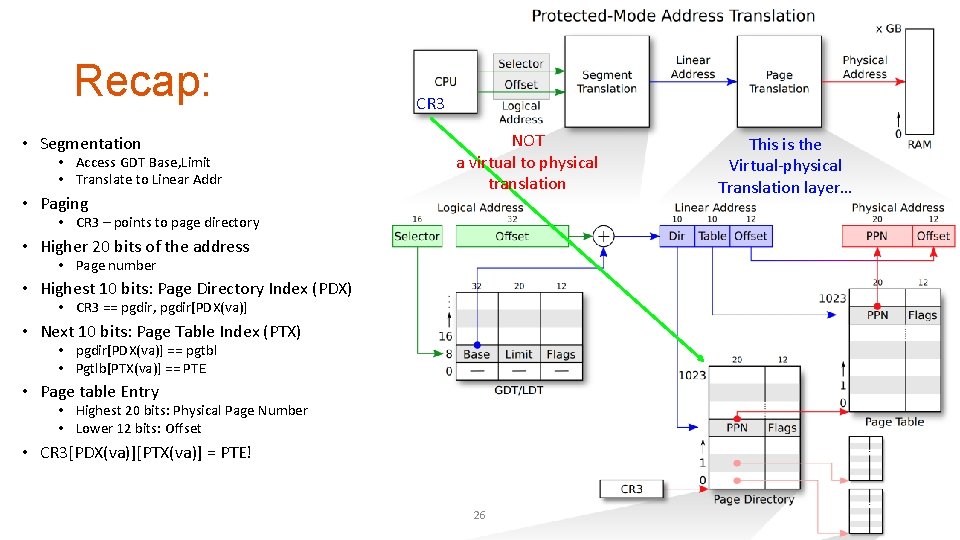

Recap: • Segmentation • Access GDT Base, Limit • Translate to Linear Addr • Paging CR 3 NOT a virtual to physical translation • CR 3 – points to page directory • Higher 20 bits of the address • Page number • Highest 10 bits: Page Directory Index (PDX) • CR 3 == pgdir, pgdir[PDX(va)] • Next 10 bits: Page Table Index (PTX) • pgdir[PDX(va)] == pgtbl • Pgtlb[PTX(va)] == PTE • Page table Entry • Highest 20 bits: Physical Page Number • Lower 12 bits: Offset • CR 3[PDX(va)][PTX(va)] = PTE! 26 This is the Virtual-physical Translation layer…

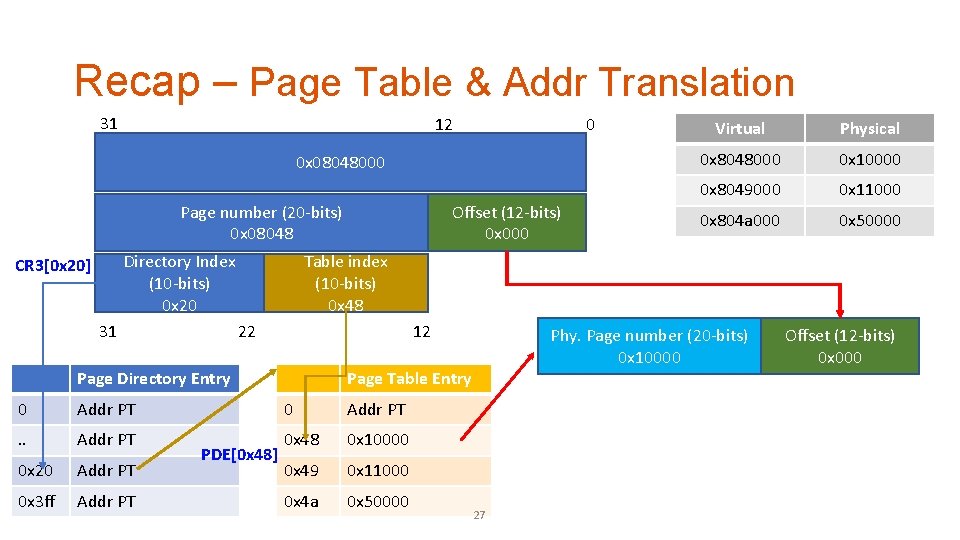

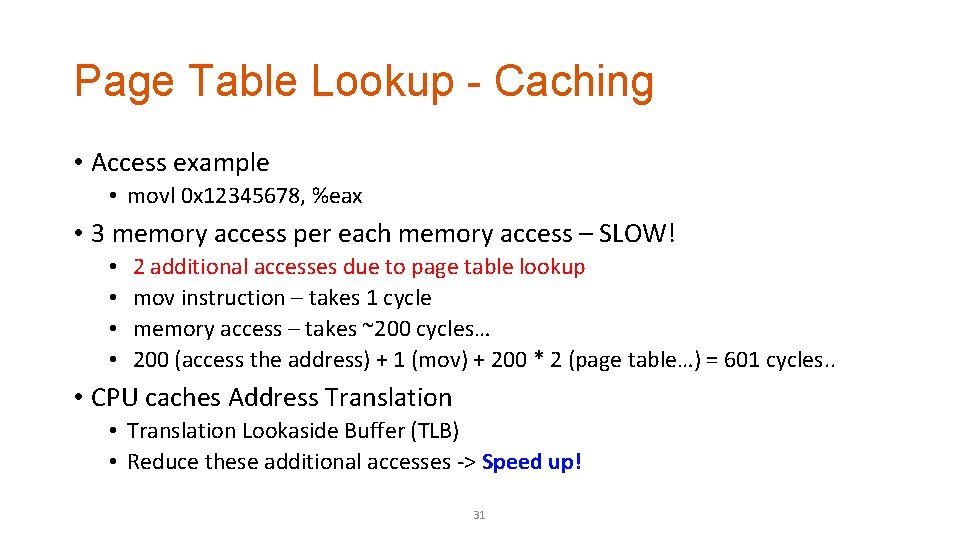

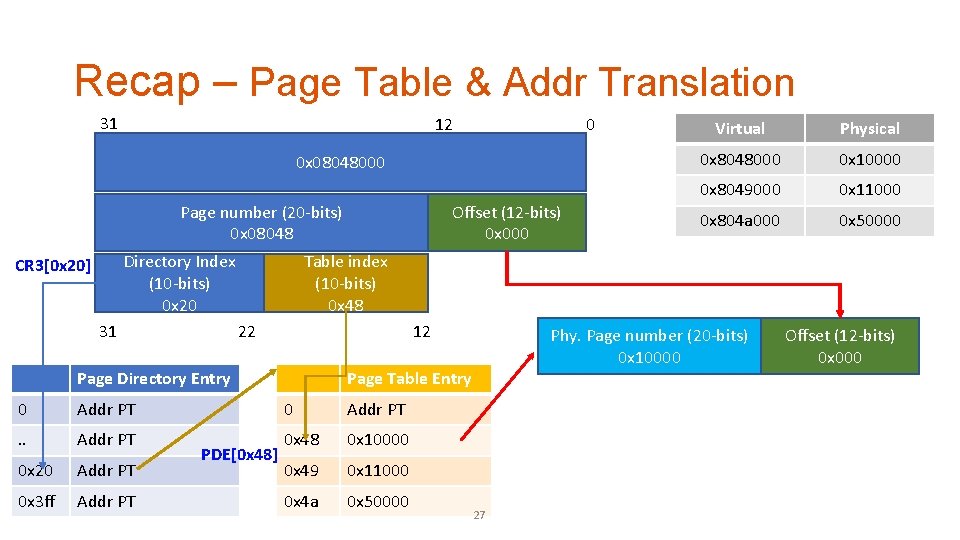

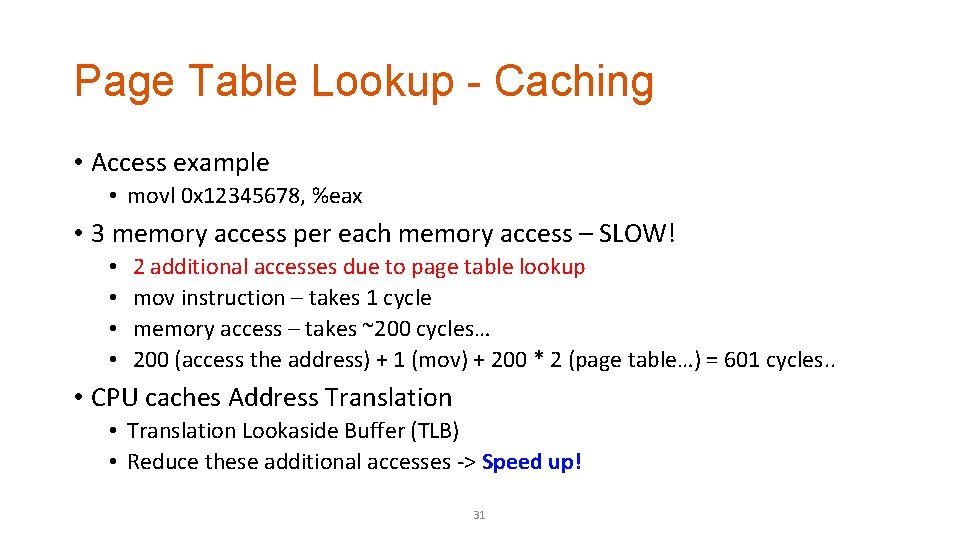

Recap – Page Table & Addr Translation 31 12 0 0 x 08048000 Offset (12 -bits) 0 x 000 Page number (20 -bits) 0 x 08048 Directory Index (10 -bits) 0 x 20 CR 3[0 x 20] Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 50000 Table index (10 -bits) 0 x 48 22 31 Virtual 12 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 48 0 x 10000 0 x 20 Addr PT 0 x 49 0 x 11000 0 x 3 ff Addr PT 0 x 4 a 0 x 50000 PDE[0 x 48] Phy. Page number (20 -bits) 0 x 10000 27 Offset (12 -bits) 0 x 000

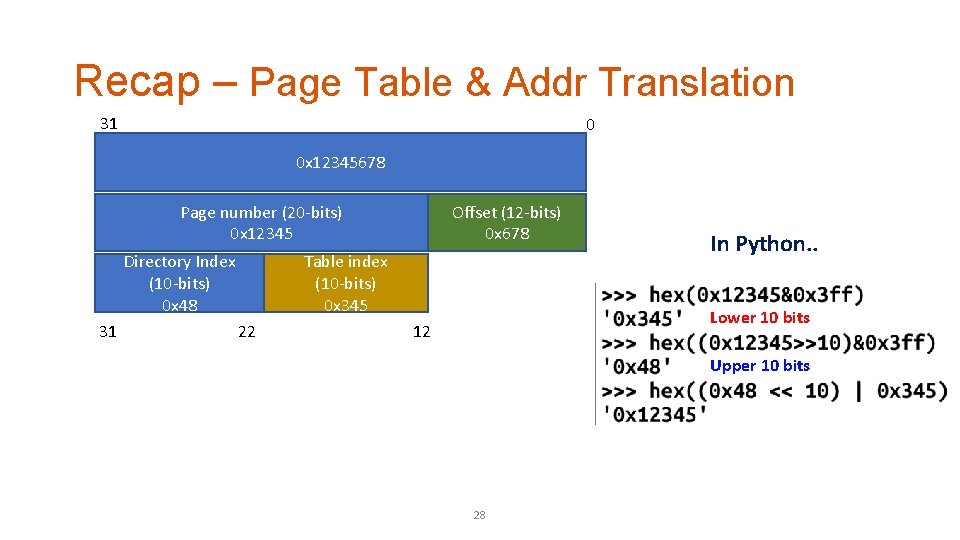

Recap – Page Table & Addr Translation 31 0 0 x 12345678 Offset (12 -bits) 0 x 678 Page number (20 -bits) 0 x 12345 Directory Index (10 -bits) 0 x 48 31 Table index (10 -bits) 0 x 345 22 In Python. . Lower 10 bits 12 Upper 10 bits 28

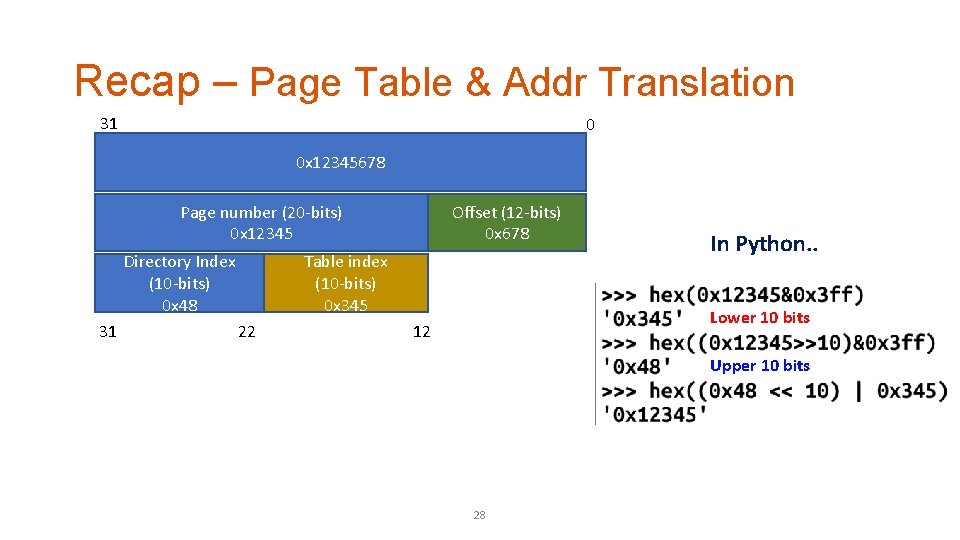

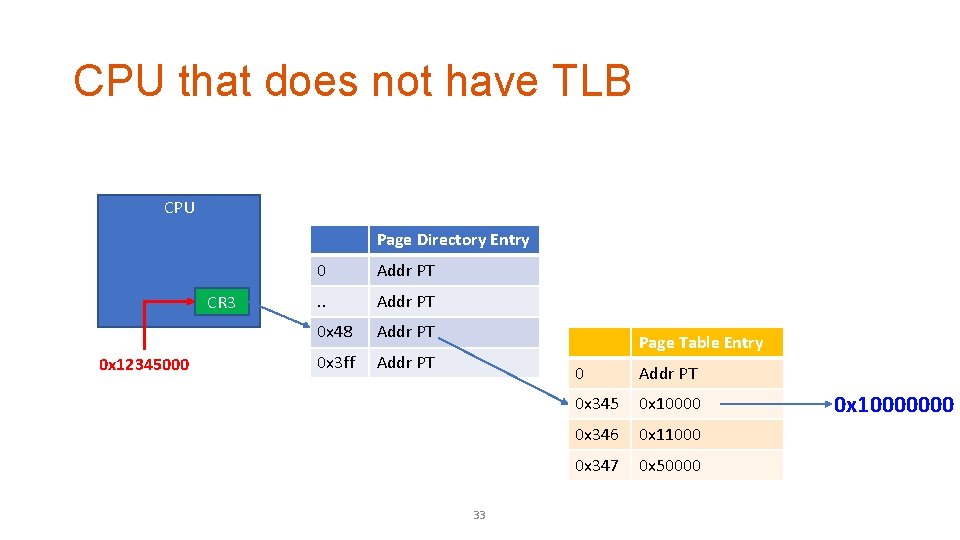

Vritual Page number (20 -bits) 0 x 12345 Page Table Lookup Offset (12 -bits) 0 x 678 • Access example • movl 0 x 12345678, %eax • (load 4 -byte data from the address 0 x 12345678 to %eax) Physical Page number (20 -bits) 0 x 10000 • Memory access sequence Offset (12 -bits) 0 x 678 Virtual page number: top 20 bits, PGNUM = (0 x 12345678 >> 12) = 0 x 12345 Page Directory Index: top 10 bits, PDX = ( PGNUM >> 10 )& 0 x 3 ff = 0 x 48 Page Table Index: next 10 bits, PTX = PGNUM & 0 x 3 ff = 0 x 345 Page Table Entry: PTE = CR 3[PDX][PTX] – 2 memory dereferences Physical address = Physical Page Number + OFFSET = (PTE & 0 xfffff 000) + (0 x 12345678 & 0 xfff) • eax = PHY_ADDR[0] – 1 memory dereferences (required) • • • 29

Recap – Page Table & Addr Translation 31 12 0 0 x 08048000 Offset (12 -bits) 0 x 000 Page number (20 -bits) 0 x 08048 Mem access #1 CR 3[0 x 20] Directory Index (10 -bits) 0 x 20 Physical 0 x 8048000 0 x 10000 0 x 8049000 0 x 11000 0 x 804 a 000 0 x 50000 Table index (10 -bits) 0 x 48 22 31 Virtual 12 Page Directory Entry Phy. Page number (20 -bits) 0 x 10000 Page Table Entry 0 Addr PT . . Addr PT 0 x 48 0 x 10000 0 x 20 Addr PT 0 x 3 ff Addr PT PDE[0 x 48] Mem access 0 x 49 #2 0 x 4 a Mem access #3 (required) 0 x 11000 0 x 50000 30 Offset (12 -bits) 0 x 000

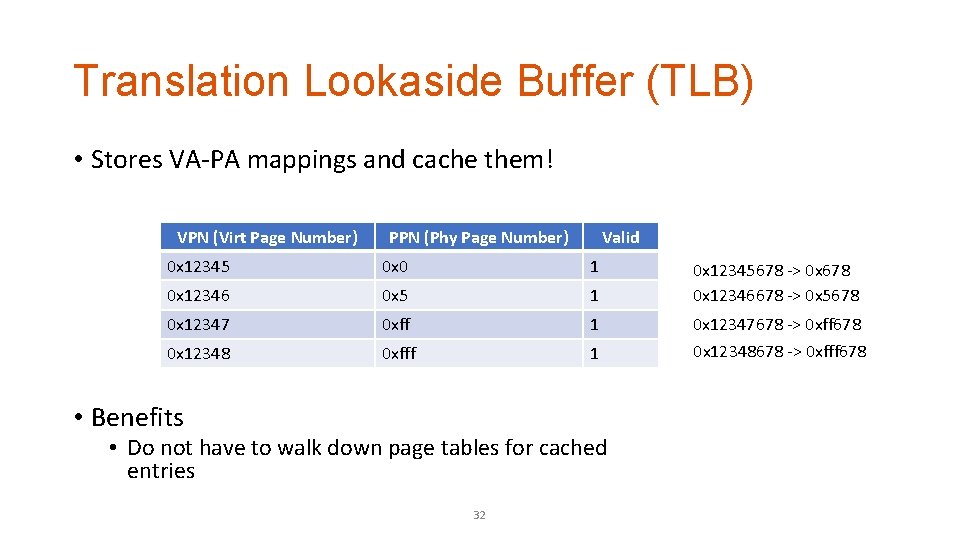

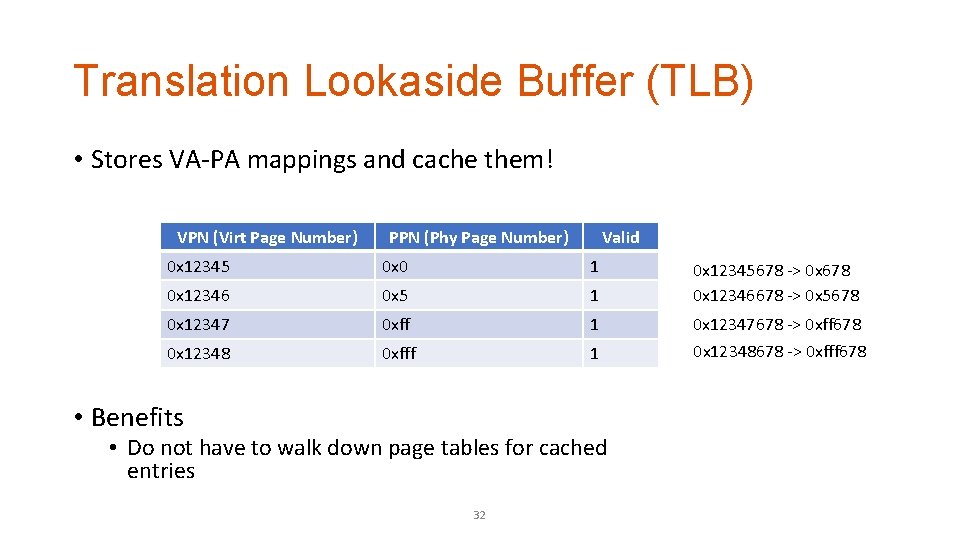

Page Table Lookup - Caching • Access example • movl 0 x 12345678, %eax • 3 memory access per each memory access – SLOW! • • 2 additional accesses due to page table lookup mov instruction – takes 1 cycle memory access – takes ~200 cycles… 200 (access the address) + 1 (mov) + 200 * 2 (page table…) = 601 cycles. . • CPU caches Address Translation • Translation Lookaside Buffer (TLB) • Reduce these additional accesses -> Speed up! 31

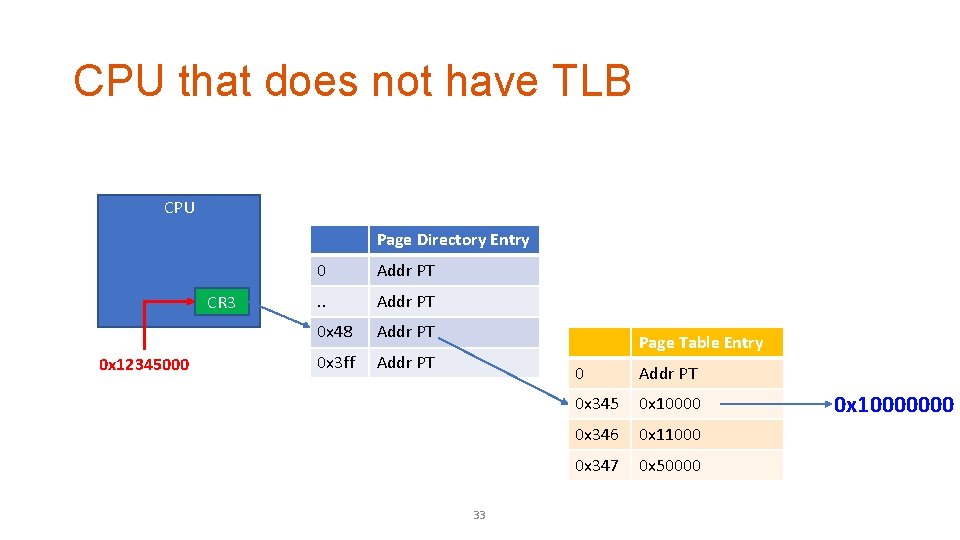

Translation Lookaside Buffer (TLB) • Stores VA-PA mappings and cache them! VPN (Virt Page Number) PPN (Phy Page Number) Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 • Benefits • Do not have to walk down page tables for cached entries 32 0 x 12345678 -> 0 x 678 0 x 12346678 -> 0 x 5678 0 x 12347678 -> 0 xff 678 0 x 12348678 -> 0 xfff 678

CPU that does not have TLB CPU Page Directory Entry CR 3 0 x 12345000 0 Addr PT . . Addr PT 0 x 48 Addr PT 0 x 3 ff Addr PT Page Table Entry 33 0 Addr PT 0 x 345 0 x 10000 0 x 346 0 x 11000 0 x 347 0 x 50000 0 x 10000000

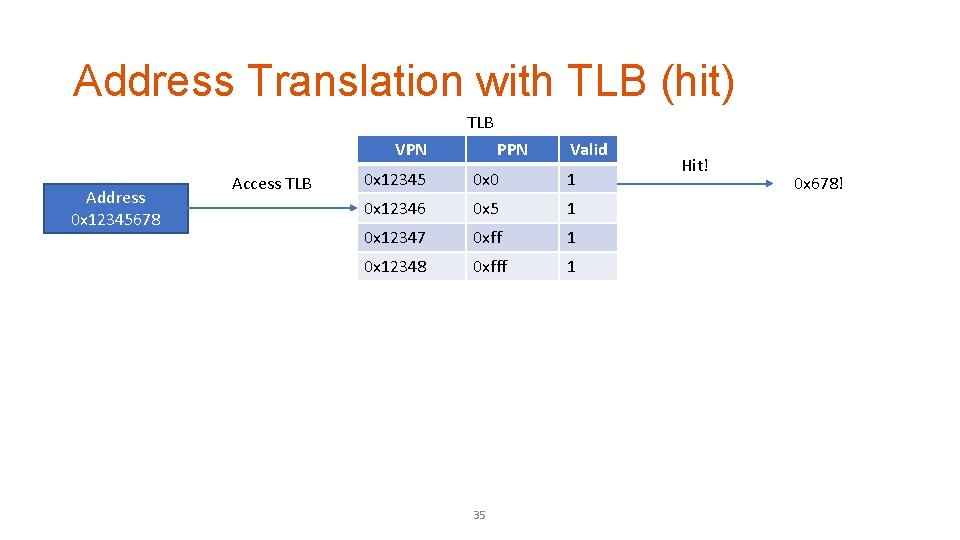

CPU with TLB VPN (Virt Page Number) PPN (Phy Page Number) Valid 0 x 12345 0 x 10000 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 CPU Page Directory Entry CR 3 0 x 12345000 0 Addr PT . . Addr PT 0 x 20 Addr PT 0 x 3 ff Addr PT Page Table Entry No page table access. . 34 0 Addr PT 0 x 48 0 x 10000 0 x 49 0 x 11000 0 x 4 a 0 x 50000 0 x 10000000

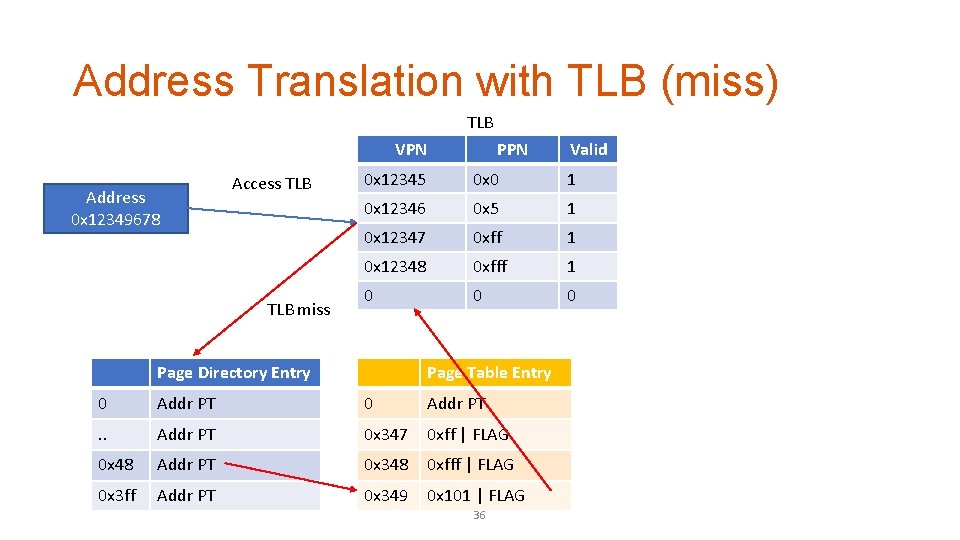

Address Translation with TLB (hit) TLB VPN Address 0 x 12345678 Access TLB PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 35 Hit! 0 x 678!

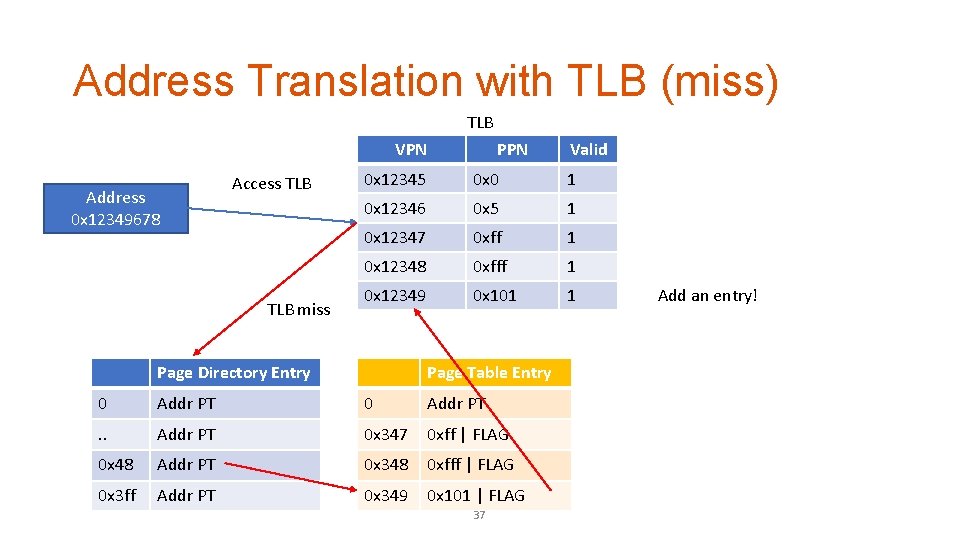

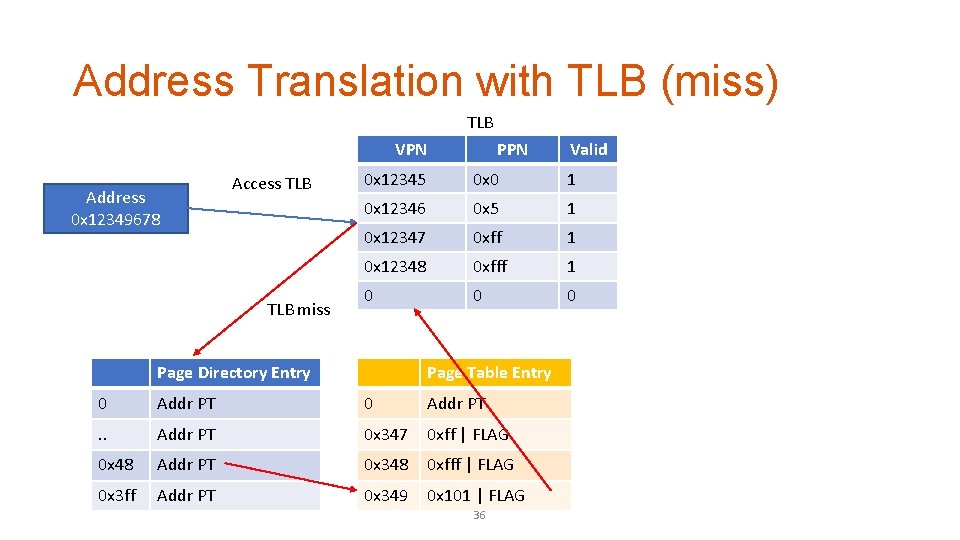

Address Translation with TLB (miss) TLB VPN Address 0 x 12349678 Access TLB miss PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 0 0 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 36

Address Translation with TLB (miss) TLB VPN Address 0 x 12349678 Access TLB miss PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 37 Add an entry!

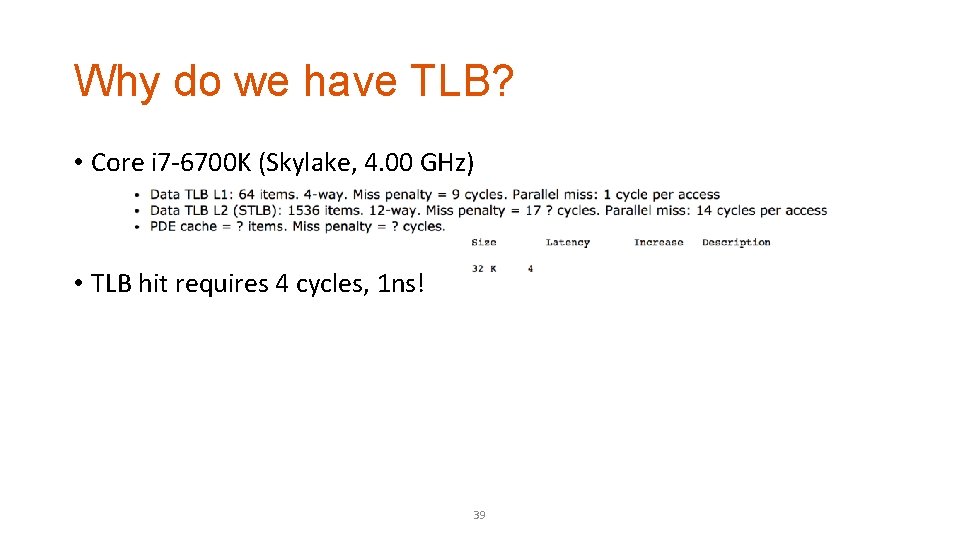

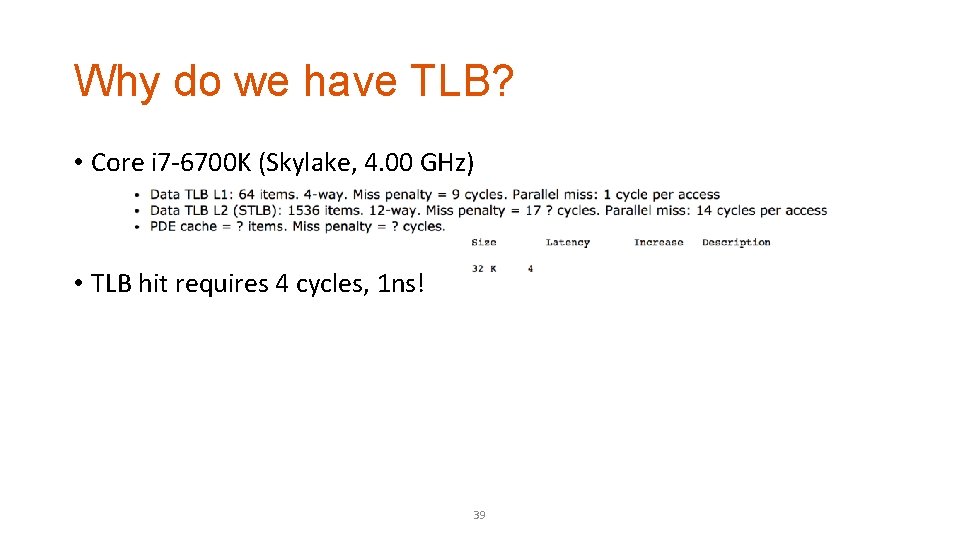

Address Translation with TLB (hit) TLB VPN Address 0 x 12349678 Access TLB PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 38 Hit! 0 x 0 x 101678!

Why do we have TLB? • Core i 7 -6700 K (Skylake, 4. 00 GHz) • TLB hit requires 4 cycles, 1 ns! 39

Why do we have TLB? • TLB hit requires 4 cycles, 1 ns! • Page table walk requires 2 memory access for translation • Uncached: 9 cycles + (42 cycles + 51 ns) * 2 • [TLB miss] [RAM latency] 2 ns + (10 ns + 51 ns) * 2 = 124 ns (124 times slower…) • Cached: 9 + 4 * 2 = 17 cycles if all blocks cached in L 1 (4 ns, 4 times slower!) 40

We have limited entries in TLB • Core i 7 -6700 K (Skylake, 4. 00 GHz) • 64 items for L 1 d-TLB, 1536 items for L 2 d-TLB • CPU need to schedule this cache • Based on Temporal/Spatial locality… 41

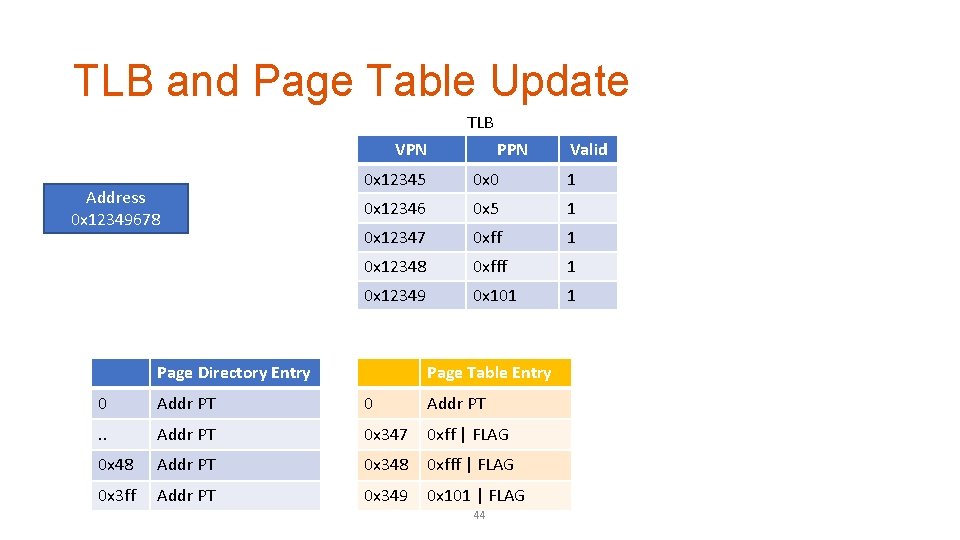

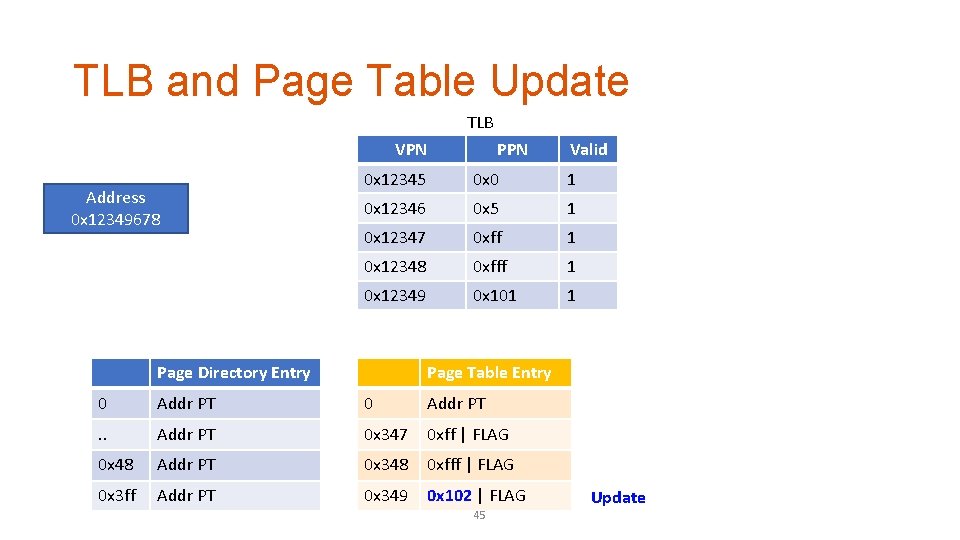

TLB Replacement Policy • Smart: LRU (Least Recently Used) • Mark when the block was accessed (update timestamp upon access) • When an eviction is required, evict the one with the oldest timestamp • Random • Do not do anything when accessed • When an eviction is required, evict an entry randomly… • Sometimes, this works better than LRU. . • We will learn more about such scheduling later • When we learn about process scheduling… 42

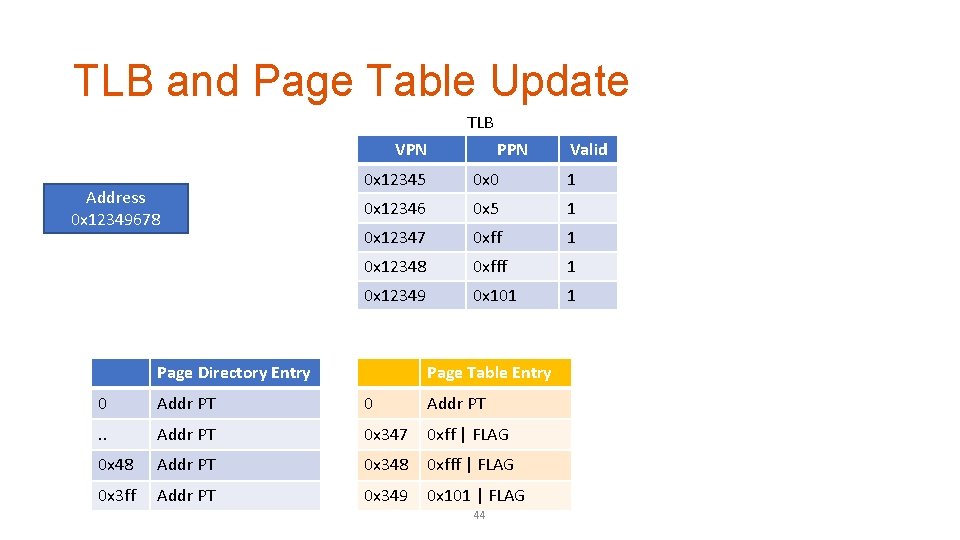

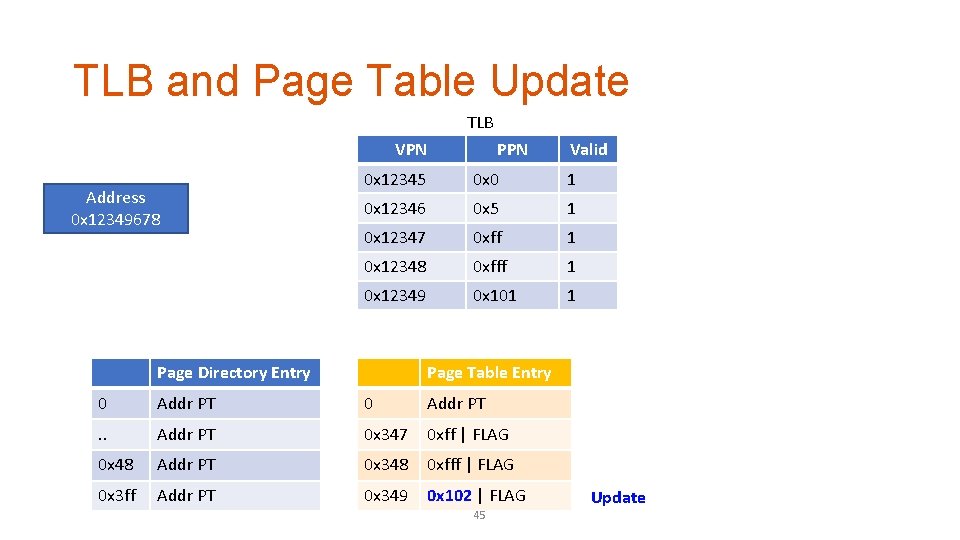

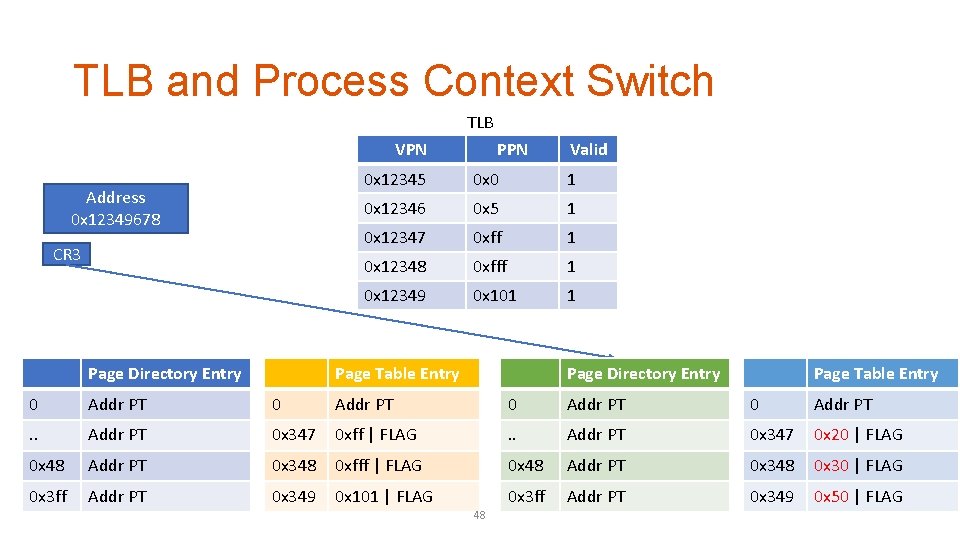

Synchronizing TLB with Page Table • CPU uses the TLB for caching Page Table Entries • What will happen if content in TLB mismatches to the PTE in the page table? • Access wrong physical memory… • Does not honor the correct privilege in PTE (if we updated PTE after caching) • Running a new process with new CR 3 • Use old process’s mapping, wrong access 43

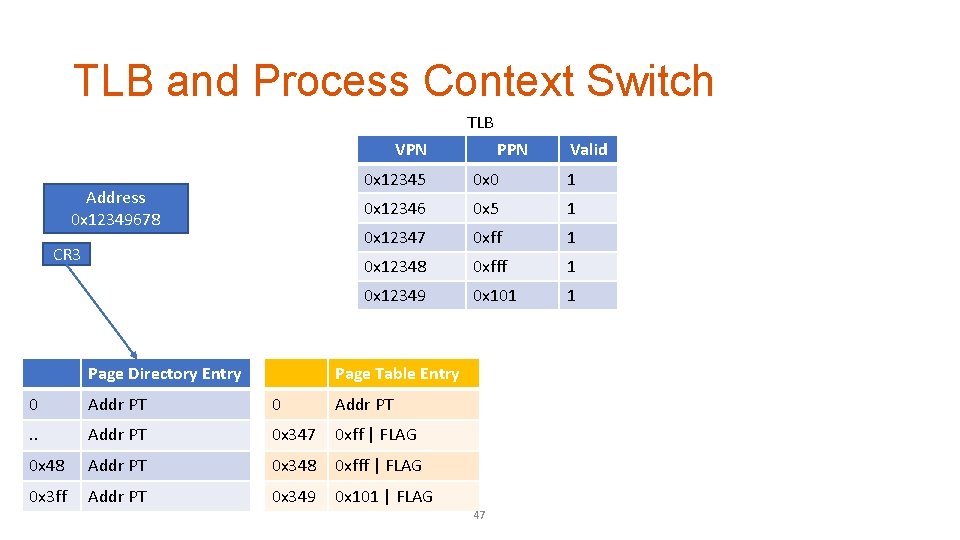

TLB and Page Table Update TLB VPN Address 0 x 12349678 PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 44

TLB and Page Table Update TLB VPN Address 0 x 12349678 PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 102 | FLAG 45 Update

TLB and Page Table Update TLB VPN Address 0 x 12349678 PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 0 Page Directory Entry We need to invalidate this entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 102 | FLAG 46 Update

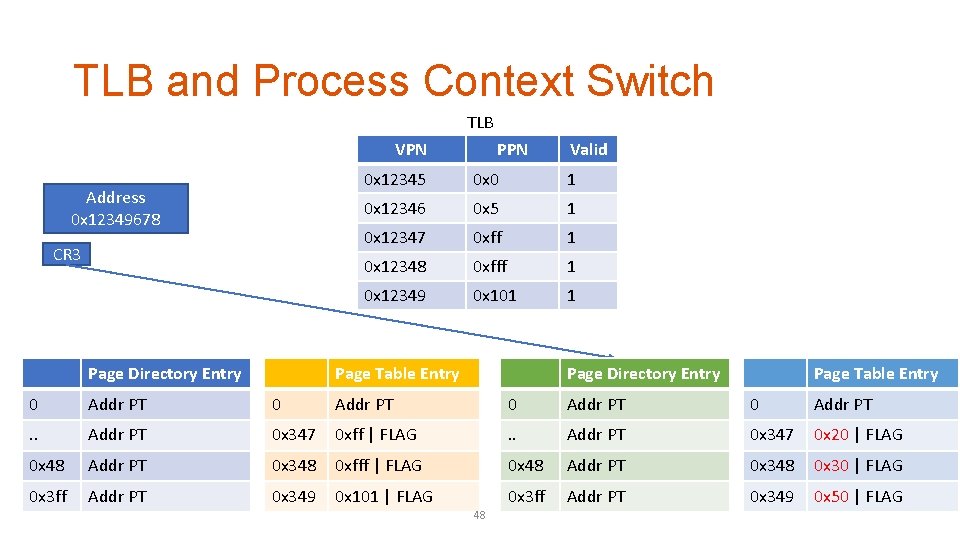

TLB and Process Context Switch TLB VPN Address 0 x 12349678 CR 3 Page Directory Entry PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 47

TLB and Process Context Switch TLB VPN Address 0 x 12349678 CR 3 Page Directory Entry PPN Valid 0 x 12345 0 x 0 1 0 x 12346 0 x 5 1 0 x 12347 0 xff 1 0 x 12348 0 xfff 1 0 x 12349 0 x 101 1 Page Table Entry Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG . . Addr PT 0 x 347 0 x 20 | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 48 Addr PT 0 x 348 0 x 30 | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 50 | FLAG 48

TLB and Process Context Switch TLB VPN Address 0 x 12349678 CR 3 Page Directory Entry PPN Valid 0 x 12345 0 x 0 0 0 x 12346 0 x 5 0 0 x 12347 0 xff 0 0 x 12348 0 xfff 0 0 x 12349 0 x 101 0 Page Table Entry We need to invalidate all previous entries. . Page Directory Entry Page Table Entry 0 Addr PT . . Addr PT 0 x 347 0 xff | FLAG . . Addr PT 0 x 347 0 x 20 | FLAG 0 x 48 Addr PT 0 x 348 0 xfff | FLAG 0 x 48 Addr PT 0 x 348 0 x 30 | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 101 | FLAG 0 x 3 ff Addr PT 0 x 349 0 x 50 | FLAG 49

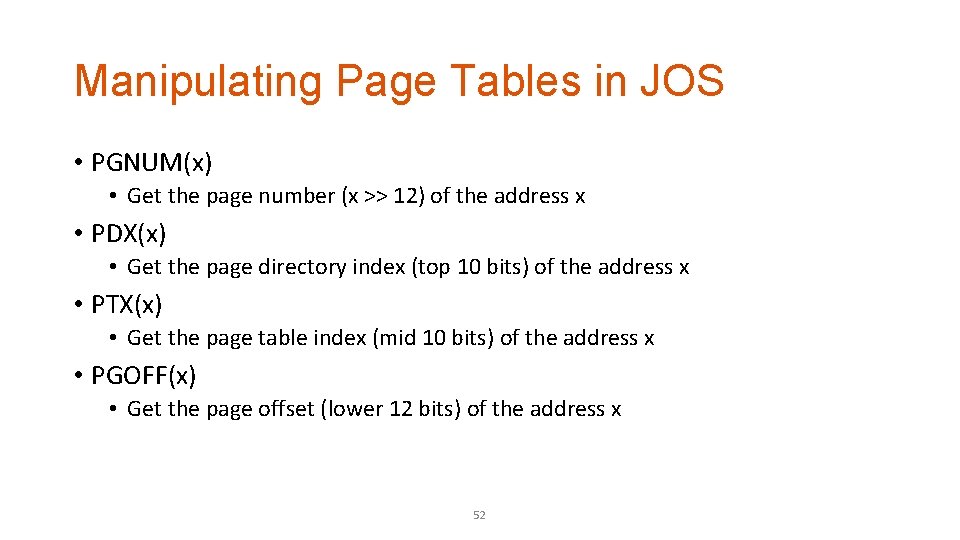

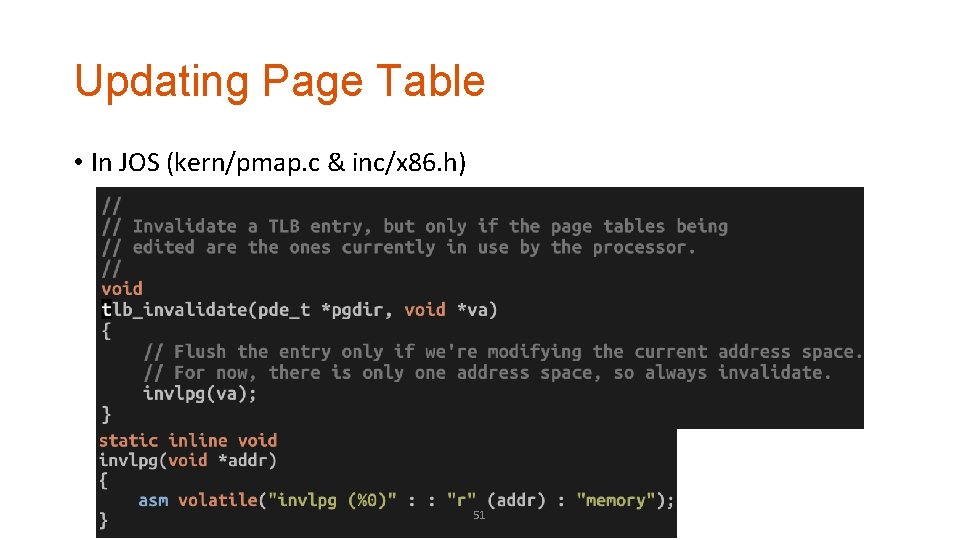

Updating Page Table • When updating a Page Table Entry • We must invalidate TLB for that entry • invlpg 50

Updating Page Table • In JOS (kern/pmap. c & inc/x 86. h) 51

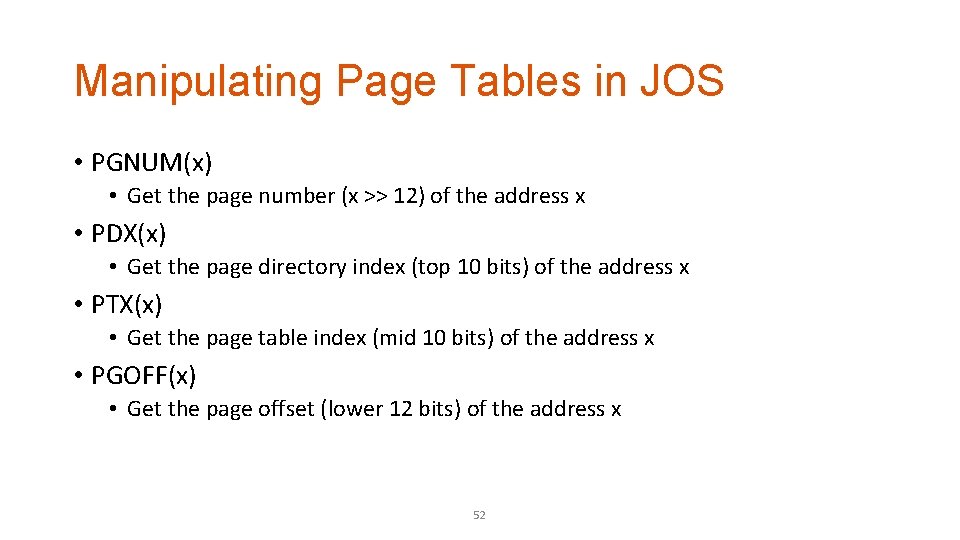

Manipulating Page Tables in JOS • PGNUM(x) • Get the page number (x >> 12) of the address x • PDX(x) • Get the page directory index (top 10 bits) of the address x • PTX(x) • Get the page table index (mid 10 bits) of the address x • PGOFF(x) • Get the page offset (lower 12 bits) of the address x 52

Manipulating Page Tables in JOS • PTE_ADDR(pte) • Get the physical address that a pte points • PTE_ADDR(pte) + PGOFF(x) • The physical address pointed by the PTE, translated by a virtual address x • Translate a virtual address va to physical address pa • pte = CR 3[PDX(va)][PTX(va)] • pte_t **cr 3 = lcr 3(); # or, kern_pgdir • pte_t *pt = cr 3[PDX(va)] • pte_t pte = pt[PTX(va)] • physaddr_t pa = PTE_ADDR(pte) + PGOFF(va); 53

![ProsCons of Segmentation Pros Easy implementation in hardware Select Base address Pros/Cons of Segmentation • Pros • Easy implementation (in hardware) • Select [Base address]](https://slidetodoc.com/presentation_image_h/080f2f6a0ba1602ba600a520e580382f/image-54.jpg)

Pros/Cons of Segmentation • Pros • Easy implementation (in hardware) • Select [Base address] and add offset • Small memory requirement • 8 byte for address translation in GDT (per each region) • Can allocate by the exact size (within 20 bits limit) • Base = 0 x 10000, limit = 0 x 10 • Memory protection (DPL) 54

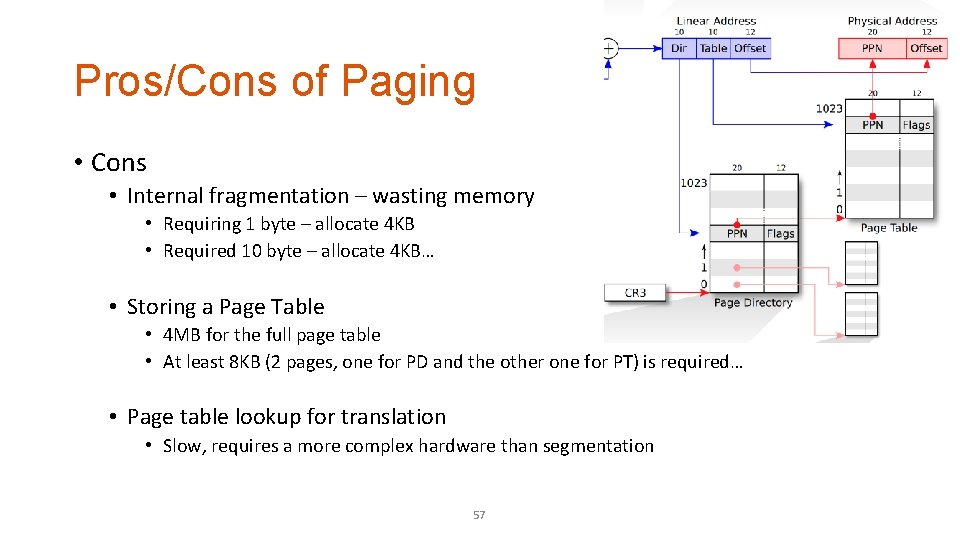

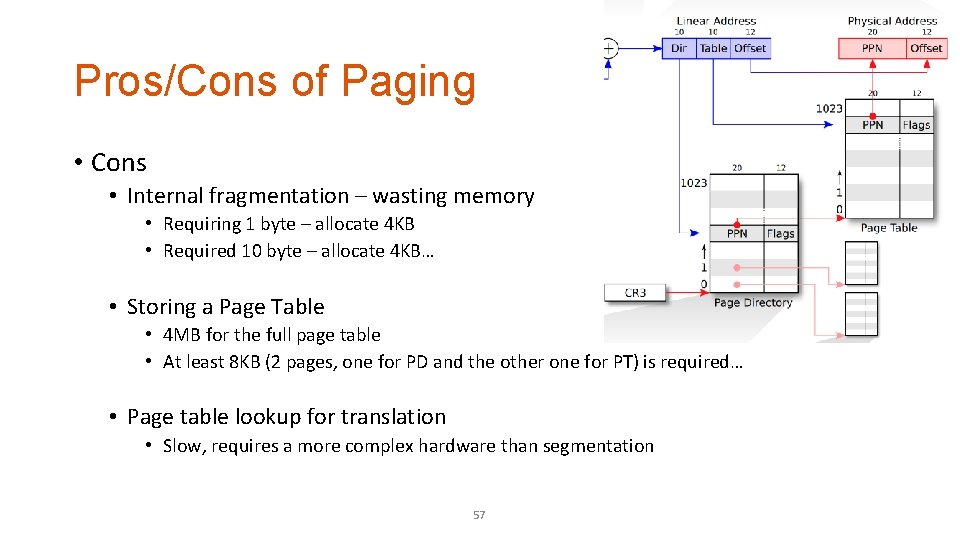

Pros/Cons of Segmentation • Cons • Fragmentation • Must allocate contiguous space for the region • Need to search for such region (regarding size) • Free: need to consolidate free memory chunks, etc. . • Memory protection placed for the entire region… Program Code - 2 (160 KB) 55 Program Data (64 KB) 0 x 58000 ~ 0 x 68000 (352 KB ~ 416 KB) Free (128 KB) 0 x 38000 ~ 0 x 58000 (224 KB ~ 352 KB) Program Code (160 KB) 0 x 10000 ~ 0 x 38000 (64 KB ~ 224 KB)

Pros/Cons of Paging Virtual Memory Physical Memory Stack 0 xbffdf 000 • Pros • No fragmentation (splitted by 4 KB each blocks) • Not requiring allocating contiguous space • 0 x 8048000 -> 0 x 10000 • 0 x 8049000 -> 0 xff 000 • 0 x 804 a 000 -> 0 xe 0000 Program code 0 x 804 a 000 Program code 0 x 8049000 • Fast allocation • No need to search available blocks (just checks how many pages are available) • Free: removing PTE! • Memory protection can be enforced in page granularity • Part of region could have a different protection bits 56 Program code 0 x 8048000 Program code 0 x 14000 Stack 0 x 12000 Program code 0 x 11000 Program code 0 x 10000

Pros/Cons of Paging • Cons • Internal fragmentation – wasting memory • Requiring 1 byte – allocate 4 KB • Required 10 byte – allocate 4 KB… • Storing a Page Table • 4 MB for the full page table • At least 8 KB (2 pages, one for PD and the other one for PT) is required… • Page table lookup for translation • Slow, requires a more complex hardware than segmentation 57

Summary • Address translation • Segmentation: base+offset -> linear address • Paging: virtual -> physical • Segmentation – Pros/Cons • Paging – Pros/Cons • TLB • Benefits? • Scheduling? • Invalidating? 58