Computer Architecture A Constructive Approach Introduction to SMIPS

![Multiple Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; Multiple Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h2/1136ce74eb30cc28a48ee2923edfad87/image-3.jpg)

- Slides: 18

Computer Architecture: A Constructive Approach Introduction to SMIPS Jihong Kim Intro to SMIPS. 1 Jihong Kim

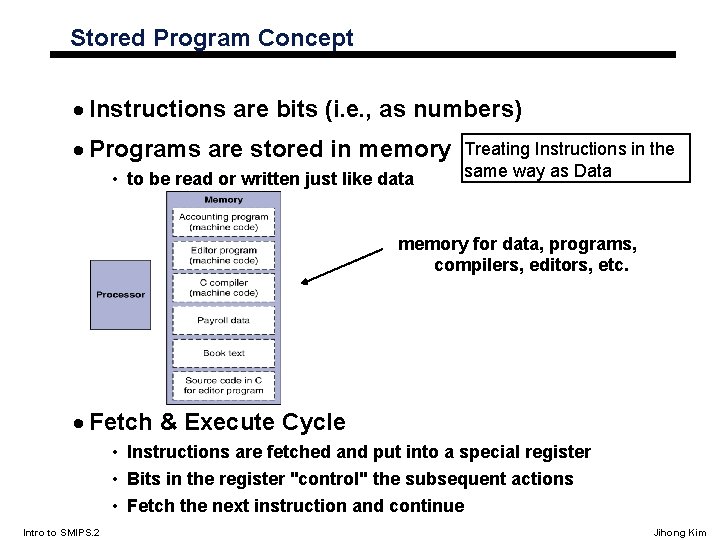

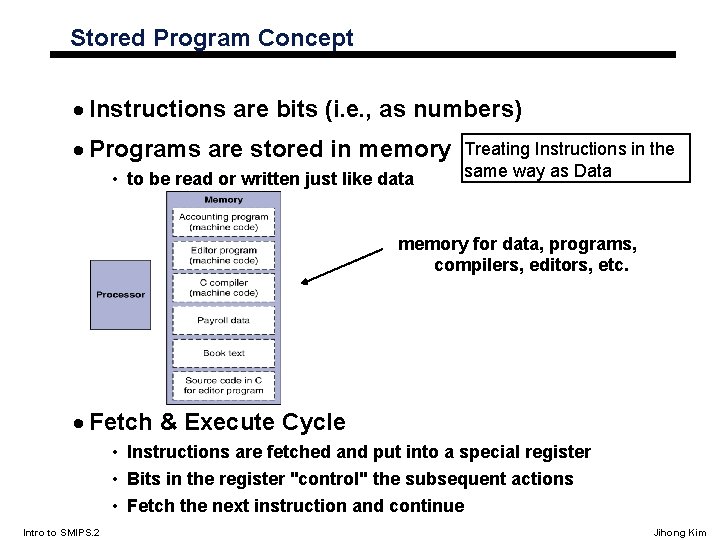

Stored Program Concept · Instructions are bits (i. e. , as numbers) · Programs are stored in memory • to be read or written just like data Treating Instructions in the same way as Data memory for data, programs, compilers, editors, etc. · Fetch & Execute Cycle • Instructions are fetched and put into a special register • Bits in the register "control" the subsequent actions • Fetch the next instruction and continue Intro to SMIPS. 2 Jihong Kim

![Multiple Levels of Representation temp vk High Level Language Program vk vk1 Multiple Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h2/1136ce74eb30cc28a48ee2923edfad87/image-3.jpg)

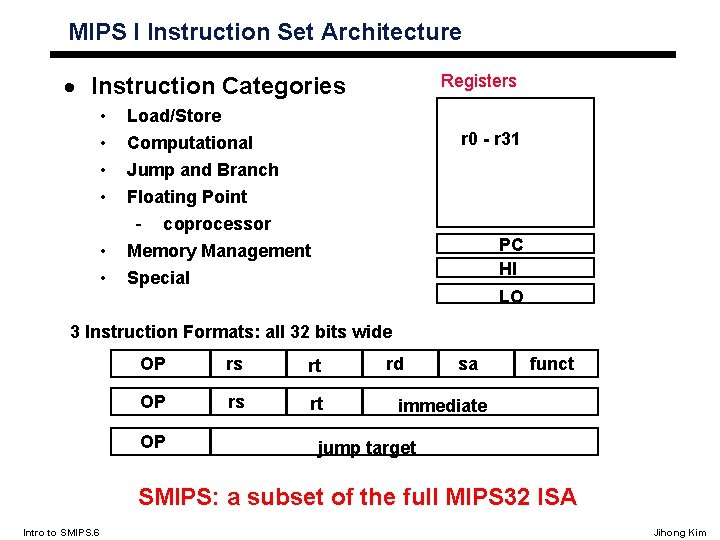

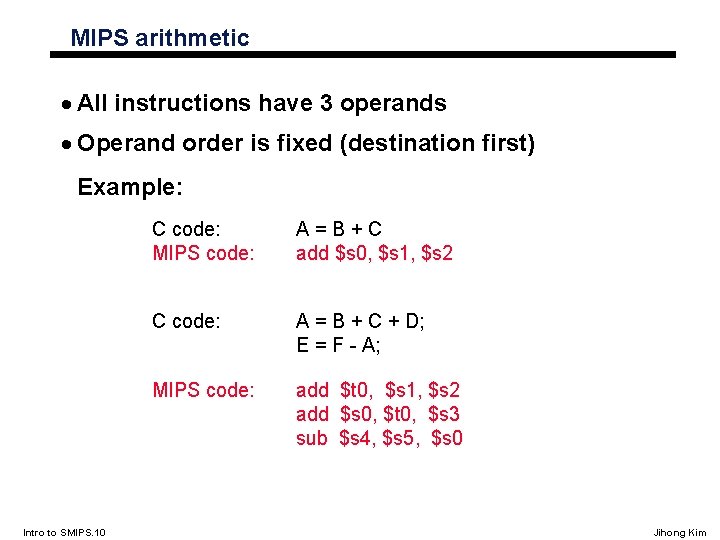

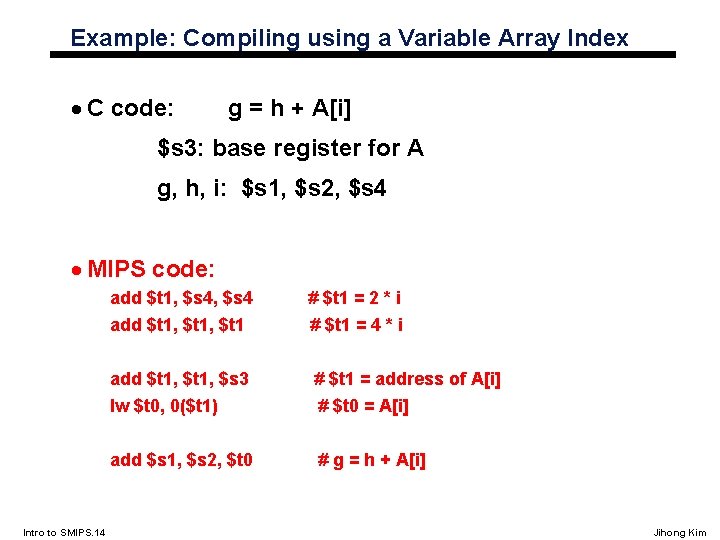

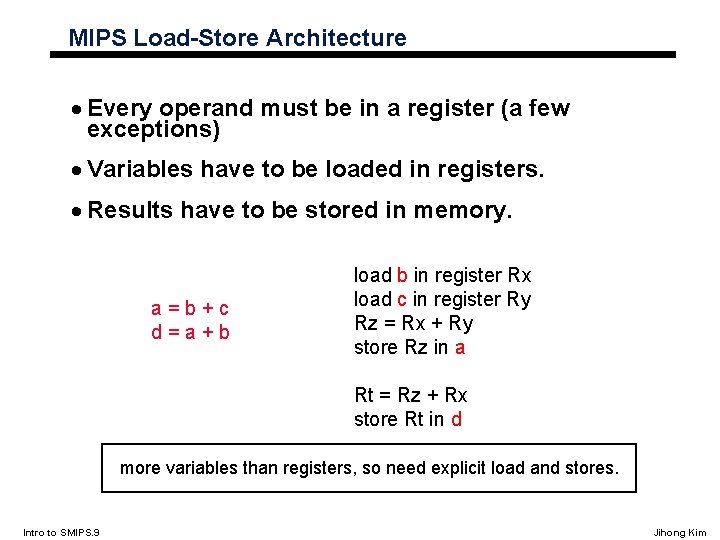

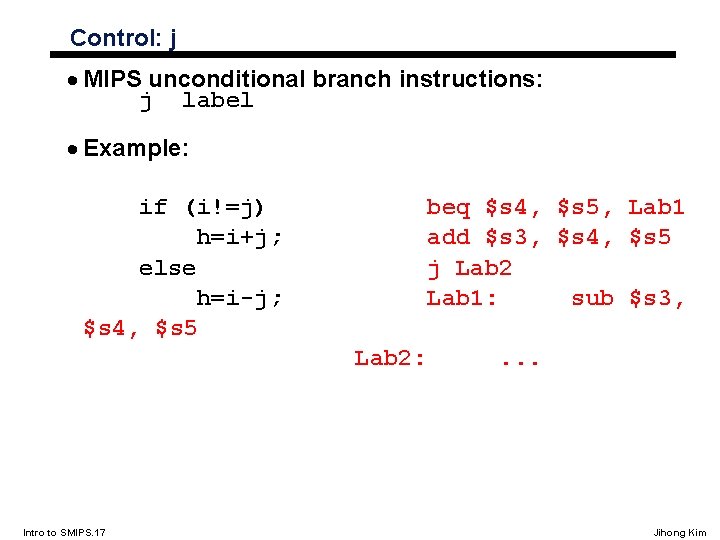

Multiple Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1] = temp; Compiler lw lw sw sw Assembly Language Program Assembler Machine Language Program 0000 1010 1100 0101 1001 1111 0110 1000 1100 0101 1010 0000 $15, $16, $15, 0110 1000 1111 1001 1010 0000 0101 1100 0($2) 4($2) 1111 1000 0110 0101 1100 0000 1010 1000 0110 1001 1111 Machine Interpretation Control Signal Specification Intro to SMIPS. 3 ALUOP[0: 3] <= Inst. Reg[9: 11] & MASK High and low signals on control lines Jihong Kim

Instruction Set Architecture (subset of Computer Arch. ) “. . . the attributes of a [computing] system as seen by the programmer, i. e. the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls, the logical design, and the physical implementation. “ Amdahl, Blaaw, and Brooks, 1964 SOFTWARE Intro to SMIPS. 4 Jihong Kim

Example ISAs · Intel 80 x 86 · ARM · HP PA-RISC · Sun Sparc · SGI MIPS · IBM/Motorola Power. PC Intro to SMIPS. 5 Jihong Kim

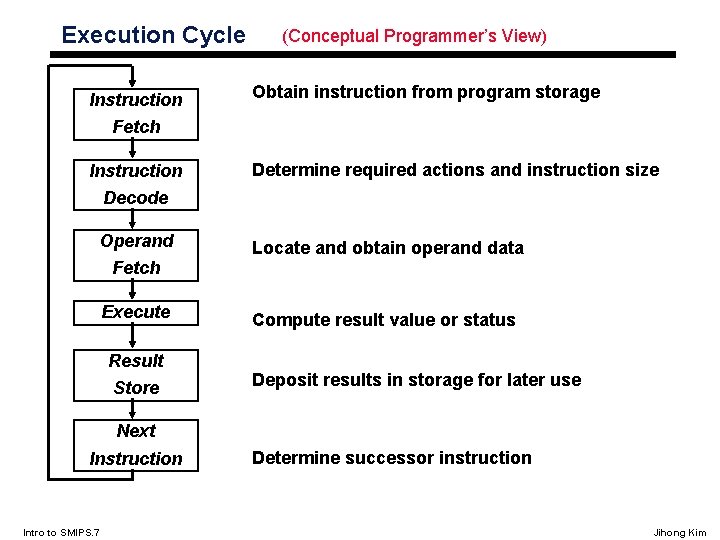

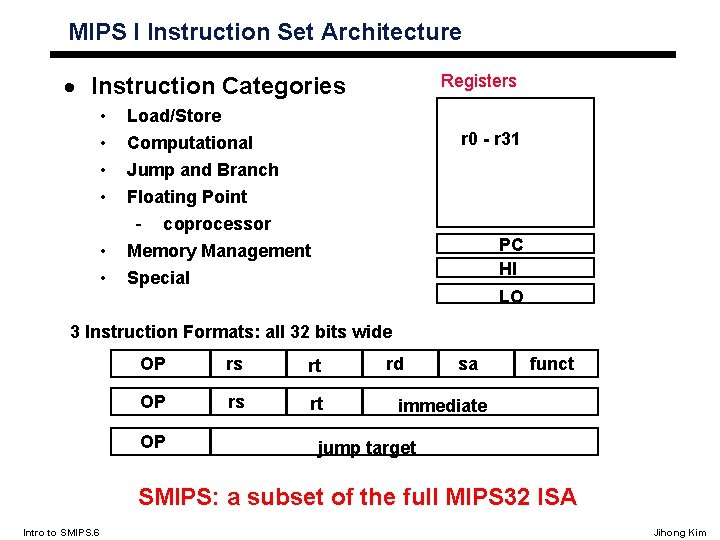

MIPS I Instruction Set Architecture · Instruction Categories • • • Registers Load/Store Computational Jump and Branch r 0 - r 31 Floating Point - coprocessor Memory Management Special PC HI LO 3 Instruction Formats: all 32 bits wide OP rs rt OP rd sa funct immediate jump target SMIPS: a subset of the full MIPS 32 ISA Intro to SMIPS. 6 Jihong Kim

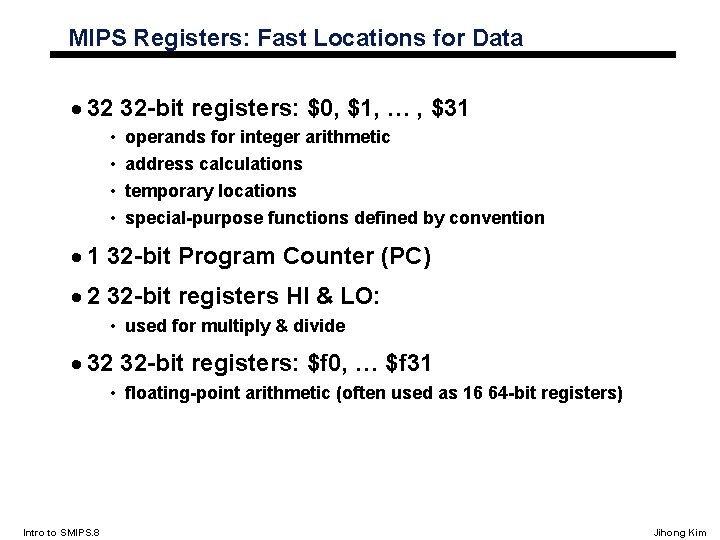

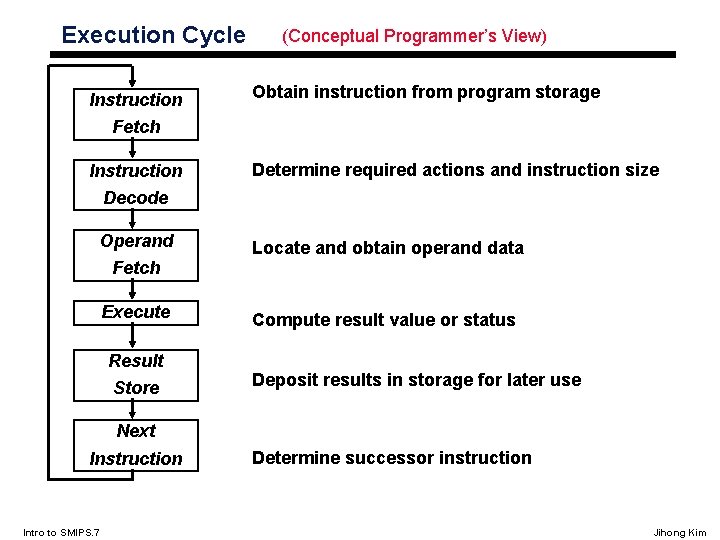

Execution Cycle Instruction (Conceptual Programmer’s View) Obtain instruction from program storage Fetch Instruction Determine required actions and instruction size Decode Operand Locate and obtain operand data Fetch Execute Result Store Compute result value or status Deposit results in storage for later use Next Instruction Intro to SMIPS. 7 Determine successor instruction Jihong Kim

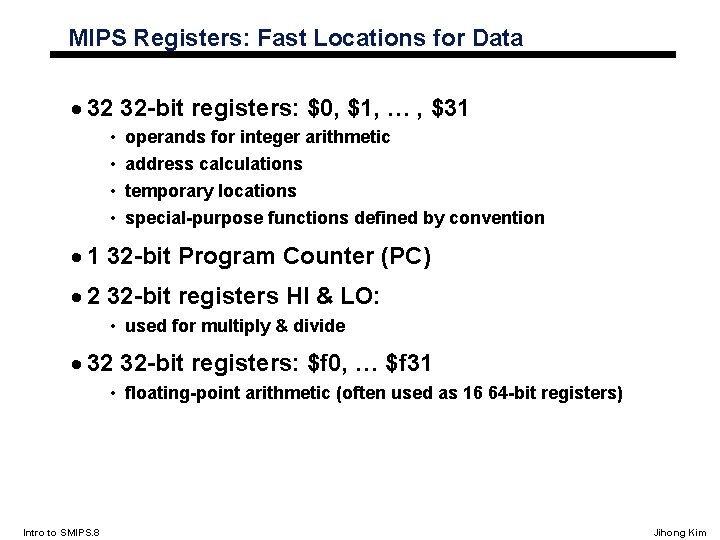

MIPS Registers: Fast Locations for Data · 32 32 -bit registers: $0, $1, … , $31 • • operands for integer arithmetic address calculations temporary locations special-purpose functions defined by convention · 1 32 -bit Program Counter (PC) · 2 32 -bit registers HI & LO: • used for multiply & divide · 32 32 -bit registers: $f 0, … $f 31 • floating-point arithmetic (often used as 16 64 -bit registers) Intro to SMIPS. 8 Jihong Kim

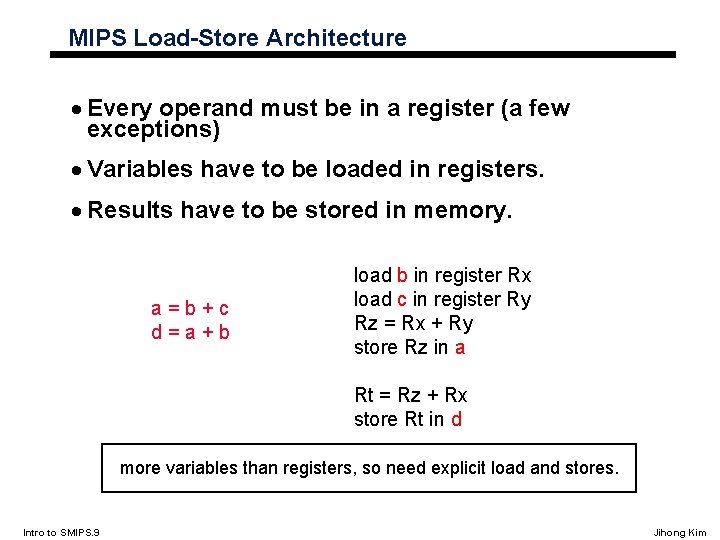

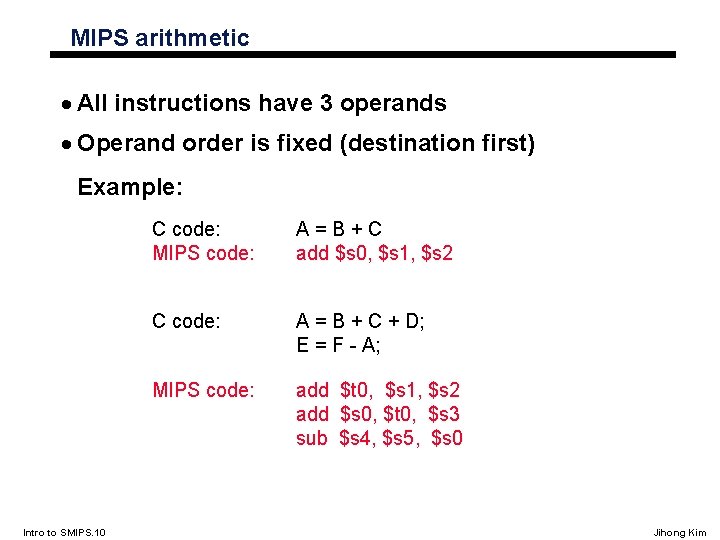

MIPS Load-Store Architecture · Every operand must be in a register (a few exceptions) · Variables have to be loaded in registers. · Results have to be stored in memory. a=b+c d=a+b load b in register Rx load c in register Ry Rz = Rx + Ry store Rz in a Rt = Rz + Rx store Rt in d more variables than registers, so need explicit load and stores. Intro to SMIPS. 9 Jihong Kim

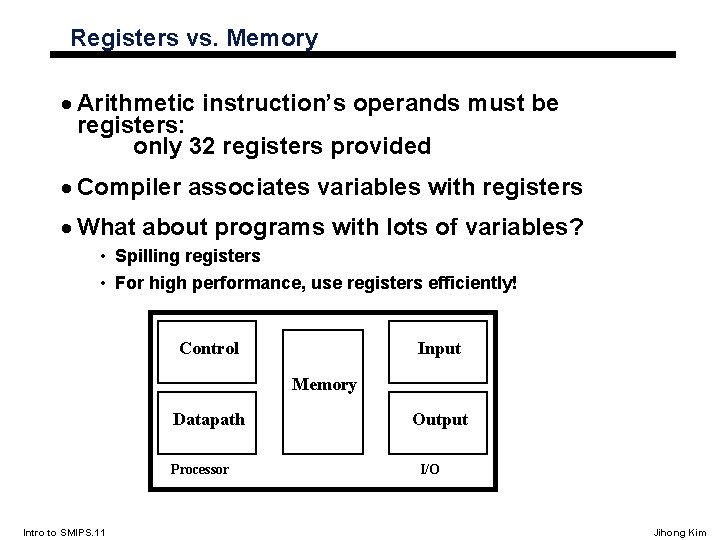

MIPS arithmetic · All instructions have 3 operands · Operand order is fixed (destination first) Example: Intro to SMIPS. 10 C code: MIPS code: A=B+C add $s 0, $s 1, $s 2 C code: A = B + C + D; E = F - A; MIPS code: add $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3 sub $s 4, $s 5, $s 0 Jihong Kim

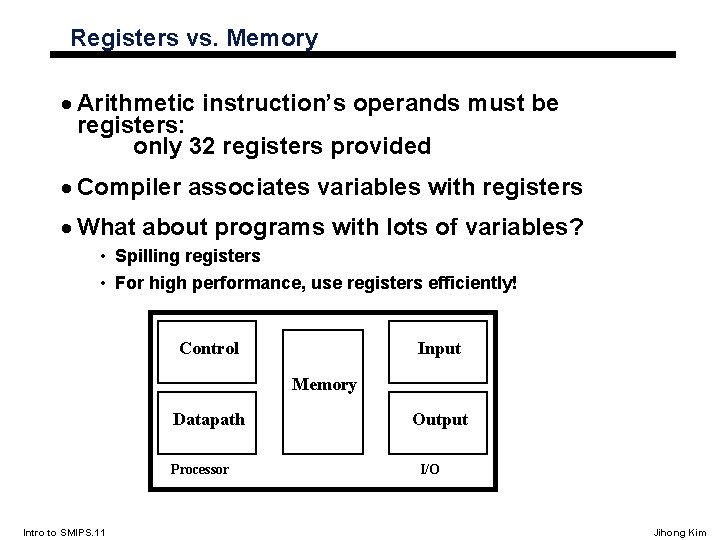

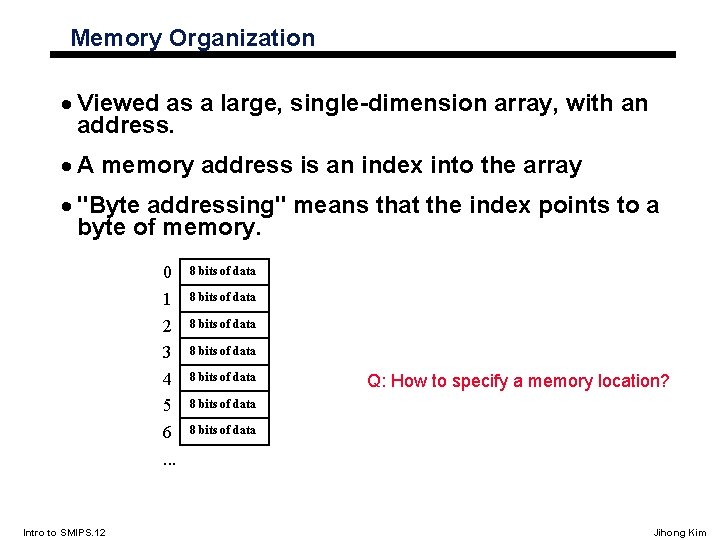

Registers vs. Memory · Arithmetic instruction’s operands must be registers: only 32 registers provided · Compiler associates variables with registers · What about programs with lots of variables? • Spilling registers • For high performance, use registers efficiently! Control Input Memory Datapath Processor Intro to SMIPS. 11 Output I/O Jihong Kim

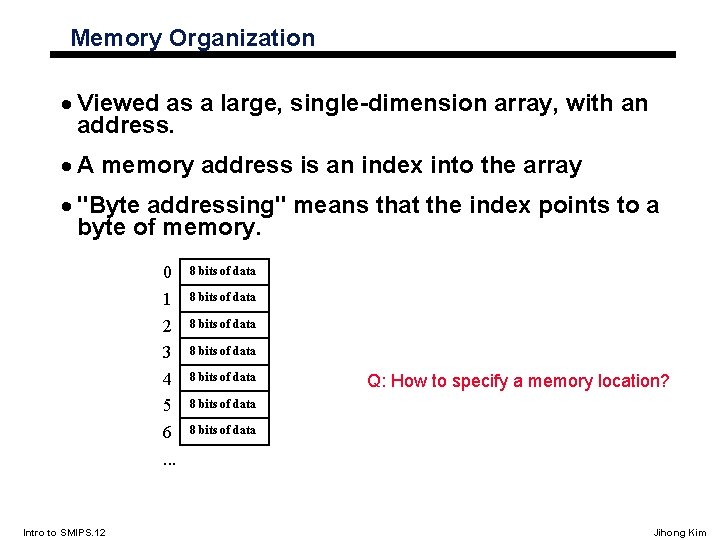

Memory Organization · Viewed as a large, single-dimension array, with an address. · A memory address is an index into the array · "Byte addressing" means that the index points to a byte of memory. 0 1 2 3 4 5 6. . . Intro to SMIPS. 12 8 bits of data 8 bits of data Q: How to specify a memory location? 8 bits of data Jihong Kim

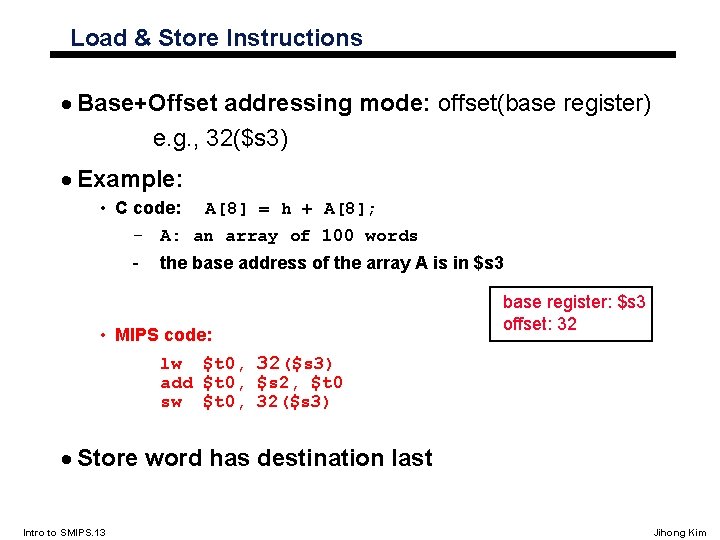

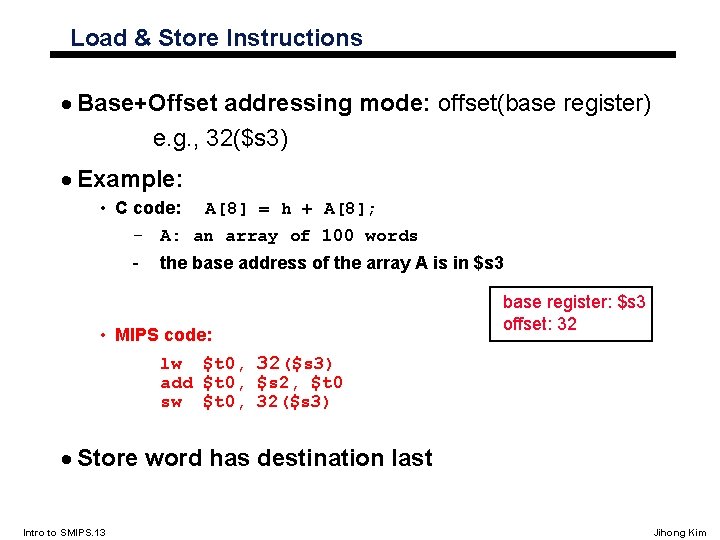

Load & Store Instructions · Base+Offset addressing mode: offset(base register) e. g. , 32($s 3) · Example: • C code: A[8] = h + A[8]; - A: an array of 100 words - the base address of the array A is in $s 3 • MIPS code: base register: $s 3 offset: 32 lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 32($s 3) · Store word has destination last Intro to SMIPS. 13 Jihong Kim

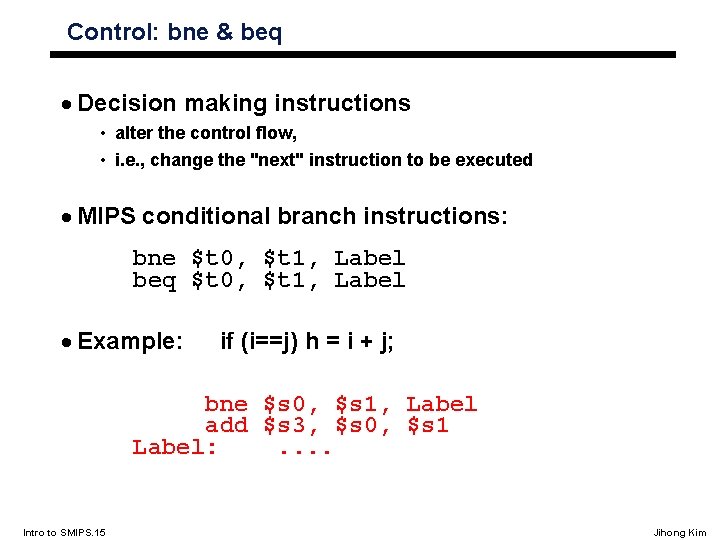

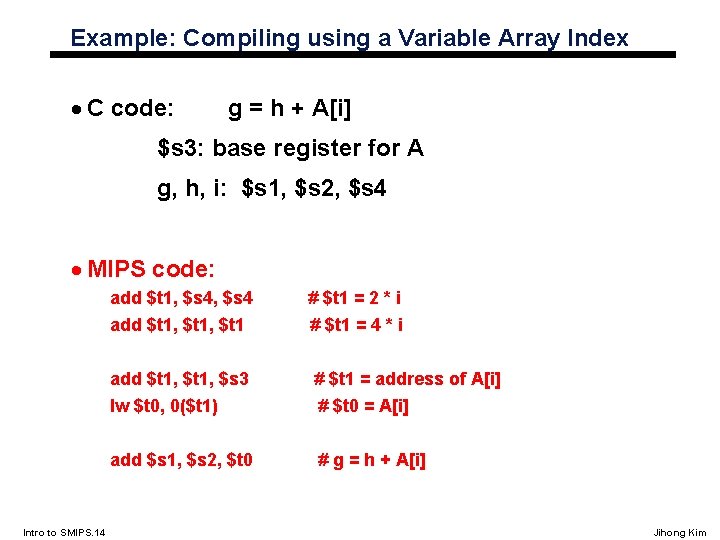

Example: Compiling using a Variable Array Index · C code: g = h + A[i] $s 3: base register for A g, h, i: $s 1, $s 2, $s 4 · MIPS code: add $t 1, $s 4 add $t 1, $t 1 Intro to SMIPS. 14 # $t 1 = 2 * i # $t 1 = 4 * i add $t 1, $s 3 # $t 1 = address of A[i] lw $t 0, 0($t 1) # $t 0 = A[i] add $s 1, $s 2, $t 0 # g = h + A[i] Jihong Kim

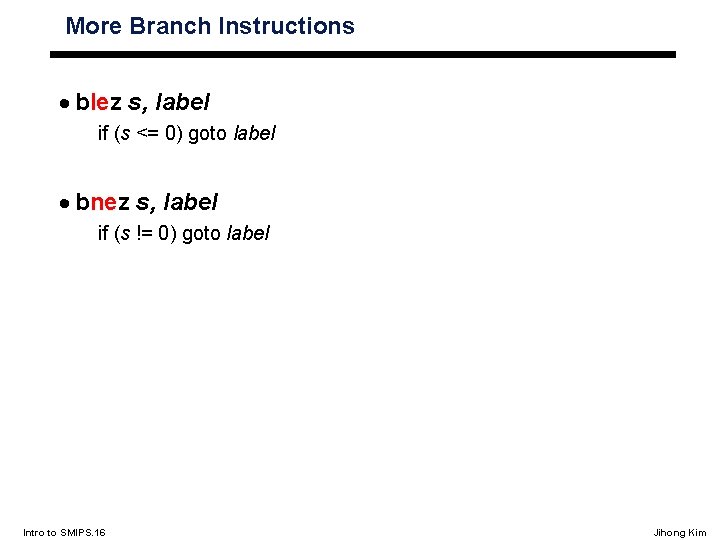

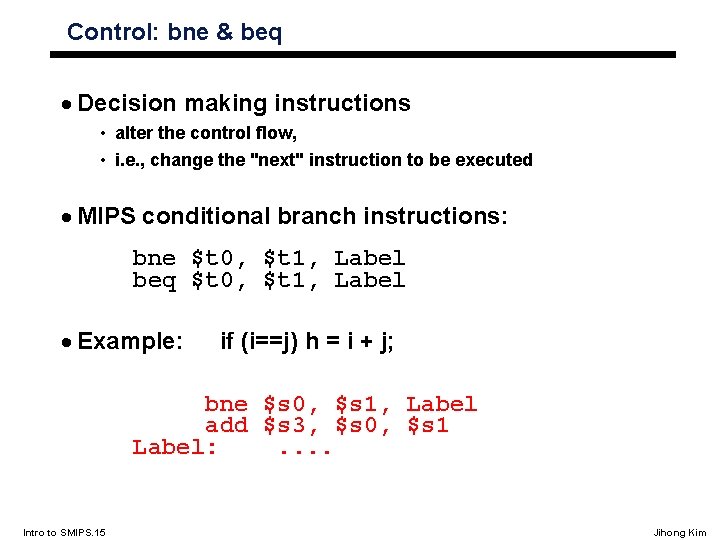

Control: bne & beq · Decision making instructions • alter the control flow, • i. e. , change the "next" instruction to be executed · MIPS conditional branch instructions: bne $t 0, $t 1, Label beq $t 0, $t 1, Label · Example: if (i==j) h = i + j; bne $s 0, $s 1, Label add $s 3, $s 0, $s 1 Label: . . Intro to SMIPS. 15 Jihong Kim

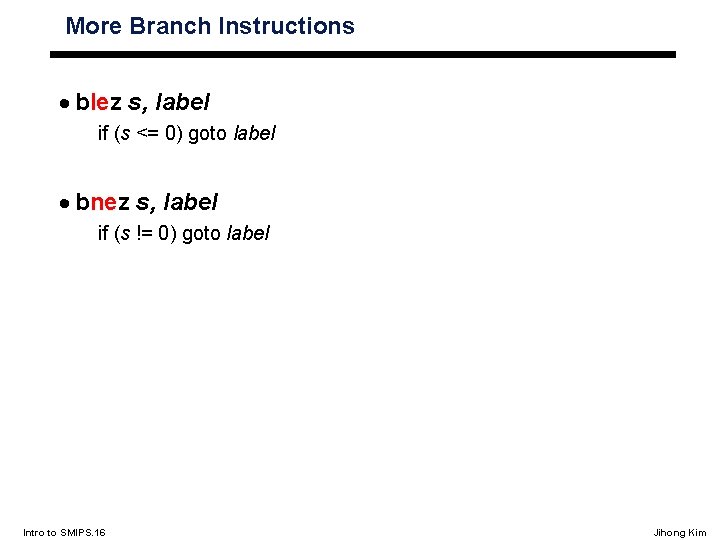

More Branch Instructions · blez s, label if (s <= 0) goto label · bnez s, label if (s != 0) goto label Intro to SMIPS. 16 Jihong Kim

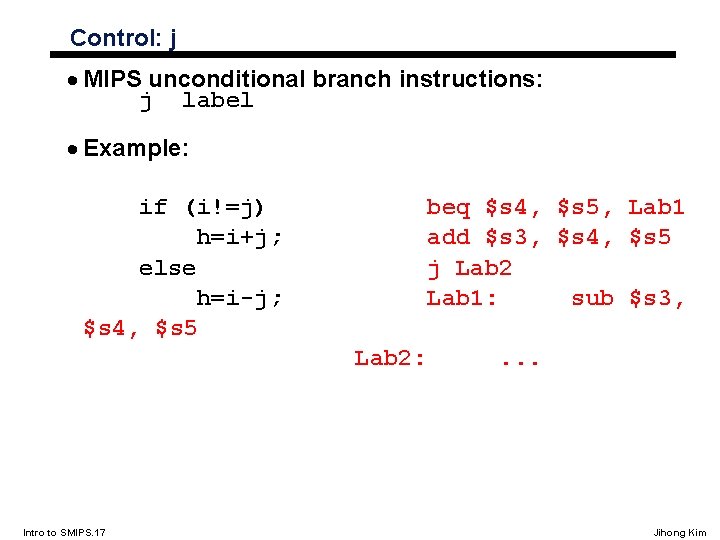

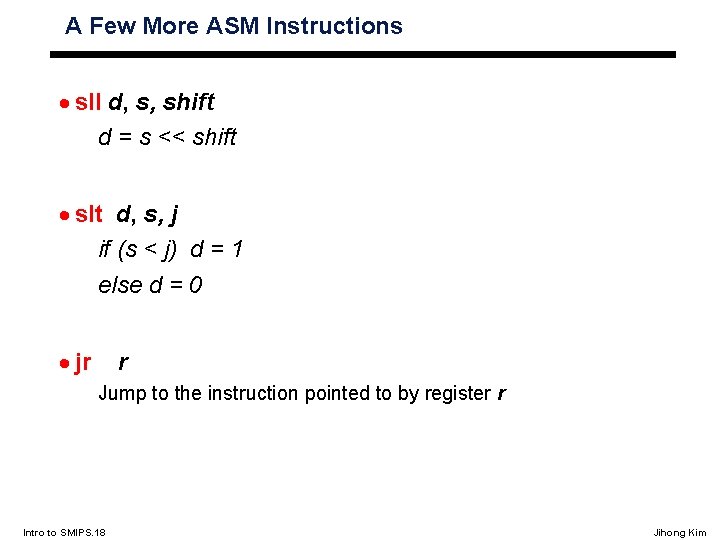

Control: j · MIPS unconditional branch instructions: j label · Example: if (i!=j) h=i+j; else h=i-j; $s 4, $s 5 beq $s 4, $s 5, Lab 1 add $s 3, $s 4, $s 5 j Lab 2 Lab 1: sub $s 3, Lab 2: Intro to SMIPS. 17 . . . Jihong Kim

A Few More ASM Instructions · sll d, s, shift d = s << shift · slt d, s, j if (s < j) d = 1 else d = 0 · jr r Jump to the instruction pointed to by register r Intro to SMIPS. 18 Jihong Kim