Constructive Computer Architecture Tutorial 7 SMIPS Epochs Andy

![Implementing Global Epoch States with EHRs Register File d. Epoch[i] e. Epoch[i] 6 IFetch Implementing Global Epoch States with EHRs Register File d. Epoch[i] e. Epoch[i] 6 IFetch](https://slidetodoc.com/presentation_image_h/0378a2bcf6329996c4f169636e5734a6/image-82.jpg)

- Slides: 86

Constructive Computer Architecture Tutorial 7: SMIPS Epochs Andy Wright 6. 175 TA October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -1

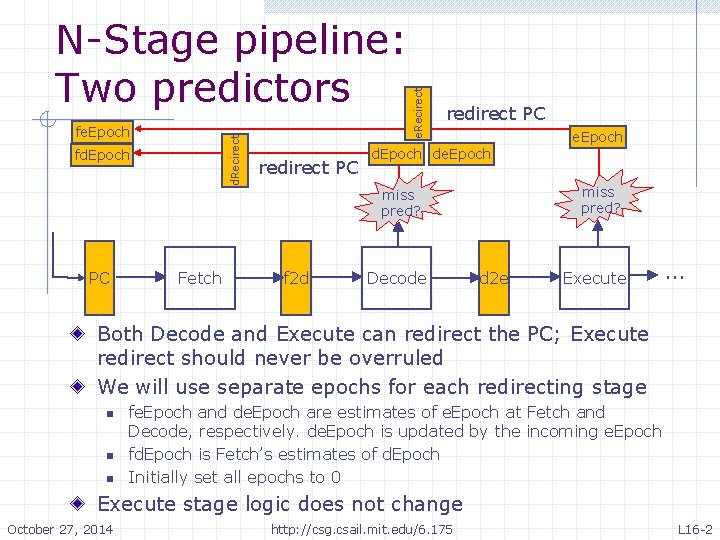

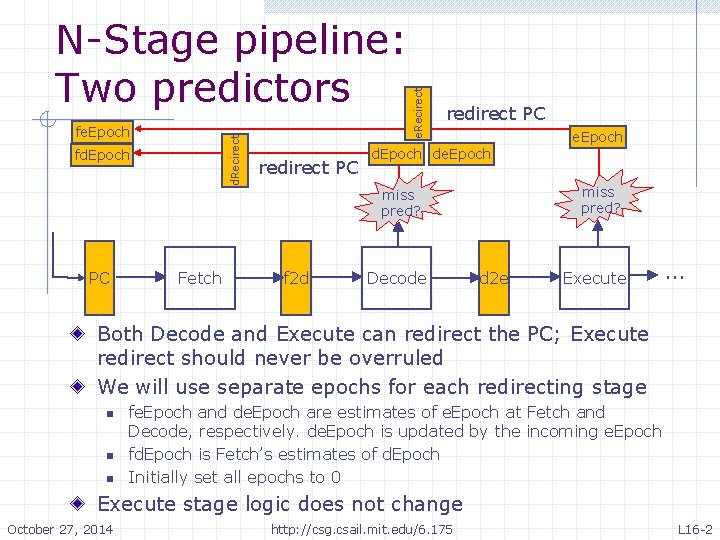

d. Recirect fe. Epoch fd. Epoch PC Fetch redirect PC e. Recirect N-Stage pipeline: Two predictors redirect PC d. Epoch de. Epoch miss pred? f 2 d Decode e. Epoch d 2 e Execute . . . Both Decode and Execute can redirect the PC; Execute redirect should never be overruled We will use separate epochs for each redirecting stage n n n fe. Epoch and de. Epoch are estimates of e. Epoch at Fetch and Decode, respectively. de. Epoch is updated by the incoming e. Epoch fd. Epoch is Fetch’s estimates of d. Epoch Initially set all epochs to 0 Execute stage logic does not change October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -2

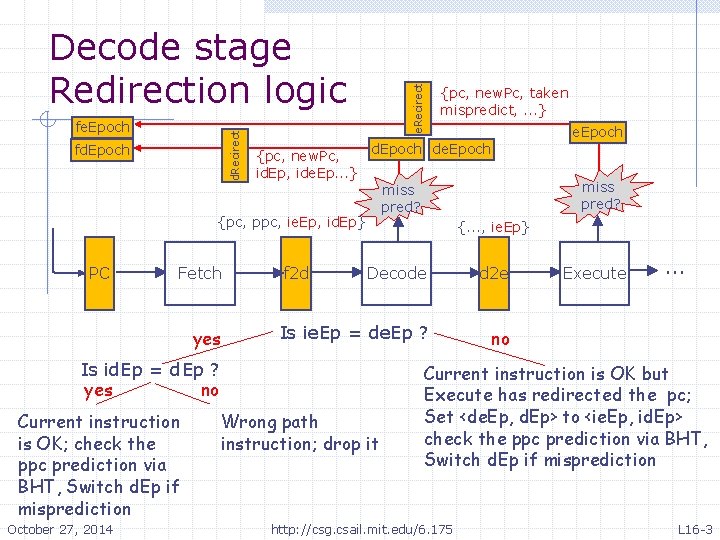

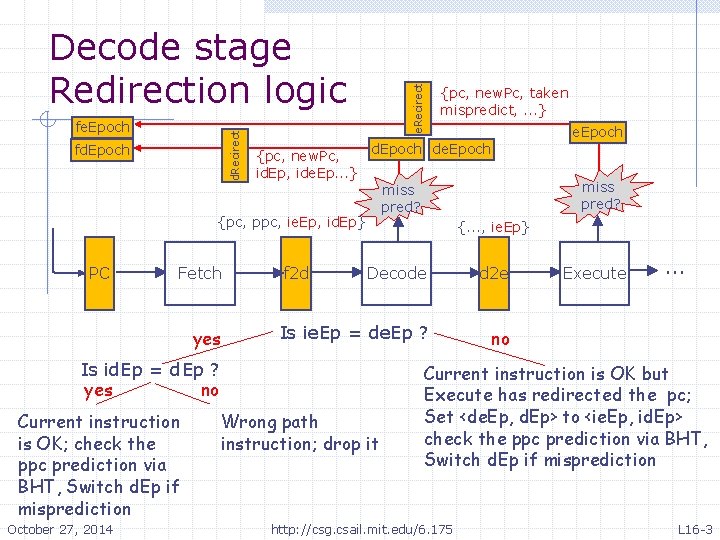

d. Recirect fe. Epoch fd. Epoch {pc, new. Pc, id. Ep, ide. Ep. . . } e. Recirect Decode stage Redirection logic Fetch yes October 27, 2014 miss pred? {. . . , ie. Ep} Decode d 2 e Is ie. Ep = de. Ep ? no f 2 d Is id. Ep = d. Ep ? no yes Current instruction is OK; check the ppc prediction via BHT, Switch d. Ep if misprediction e. Epoch de. Epoch {pc, ppc, ie. Ep, id. Ep} PC {pc, new. Pc, taken mispredict, . . . } Wrong path instruction; drop it Execute . . . Current instruction is OK but Execute has redirected the pc; Set <de. Ep, d. Ep> to <ie. Ep, id. Ep> check the ppc prediction via BHT, Switch d. Ep if misprediction http: //csg. csail. mit. edu/6. 175 L 16 -3

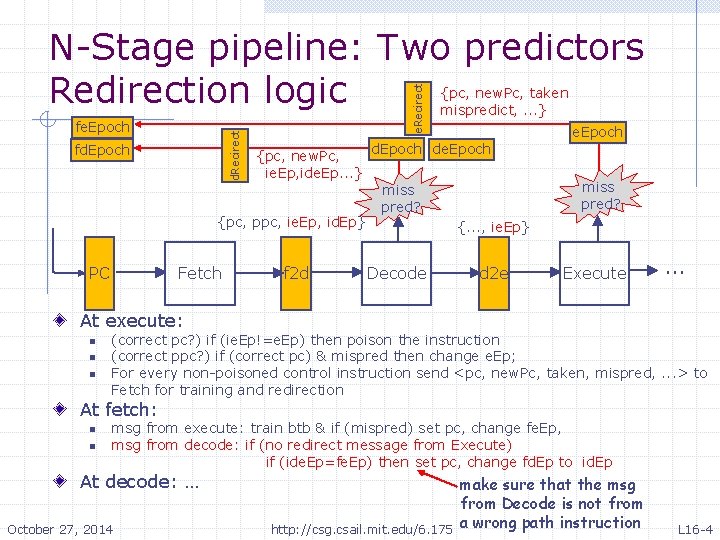

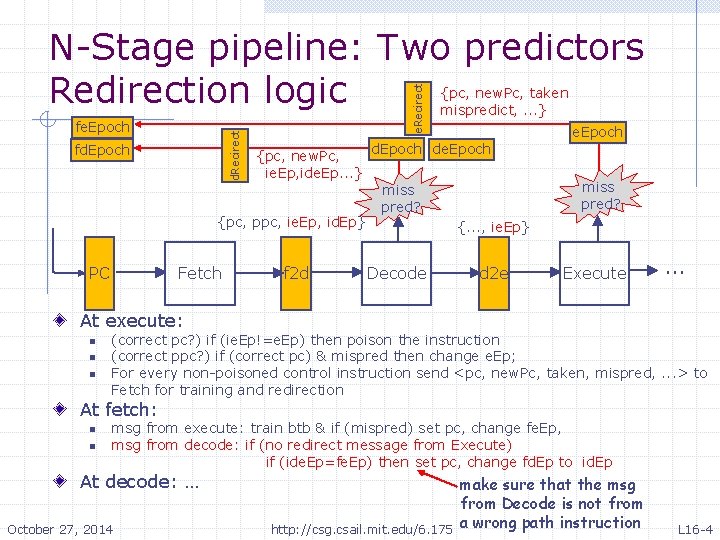

d. Recirect fe. Epoch fd. Epoch e. Recirect N-Stage pipeline: Two predictors Redirection logic {pc, new. Pc, ie. Ep, ide. Ep. . . } {pc, ppc, ie. Ep, id. Ep} Fetch PC f 2 d {pc, new. Pc, taken mispredict, . . . } d. Epoch de. Epoch miss pred? {. . . , ie. Ep} Decode d 2 e Execute . . . At execute: n n n (correct pc? ) if (ie. Ep!=e. Ep) then poison the instruction (correct ppc? ) if (correct pc) & mispred then change e. Ep; For every non-poisoned control instruction send <pc, new. Pc, taken, mispred, . . . > to Fetch for training and redirection At fetch: n n msg from execute: train btb & if (mispred) set pc, change fe. Ep, msg from decode: if (no redirect message from Execute) if (ide. Ep=fe. Ep) then set pc, change fd. Ep to id. Ep At decode: … October 27, 2014 http: //csg. csail. mit. edu/6. 175 make sure that the msg from Decode is not from a wrong path instruction L 16 -4

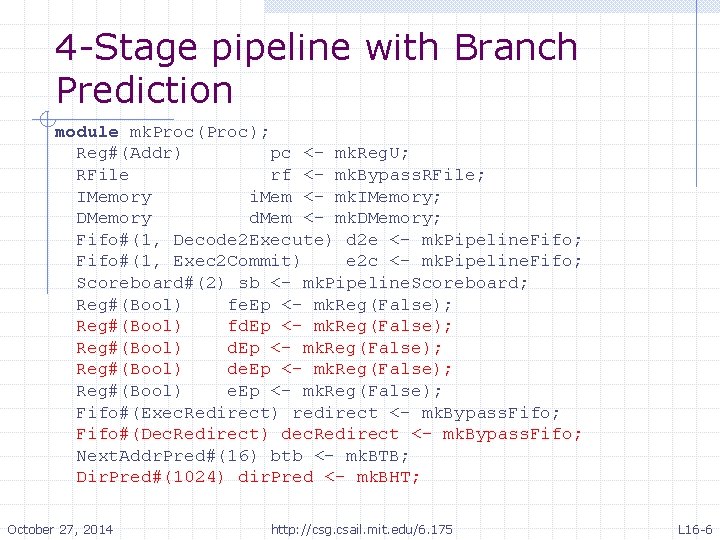

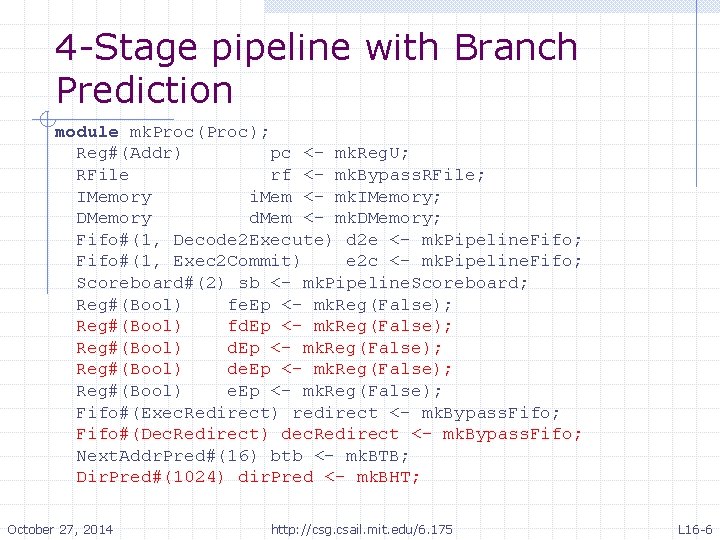

now some coding. . . 4 -stage pipeline (F, D&R, E&M, W) Direction predictor training is incompletely specified You will explore the effect of predictor training in the lab October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -5

4 -Stage pipeline with Branch Prediction module mk. Proc(Proc); Reg#(Addr) pc <- mk. Reg. U; RFile rf <- mk. Bypass. RFile; IMemory i. Mem <- mk. IMemory; DMemory d. Mem <- mk. DMemory; Fifo#(1, Decode 2 Execute) d 2 e <- mk. Pipeline. Fifo; Fifo#(1, Exec 2 Commit) e 2 c <- mk. Pipeline. Fifo; Scoreboard#(2) sb <- mk. Pipeline. Scoreboard; Reg#(Bool) fe. Ep <- mk. Reg(False); Reg#(Bool) fd. Ep <- mk. Reg(False); Reg#(Bool) de. Ep <- mk. Reg(False); Reg#(Bool) e. Ep <- mk. Reg(False); Fifo#(Exec. Redirect) redirect <- mk. Bypass. Fifo; Fifo#(Dec. Redirect) dec. Redirect <- mk. Bypass. Fifo; Next. Addr. Pred#(16) btb <- mk. BTB; Dir. Pred#(1024) dir. Pred <- mk. BHT; October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -6

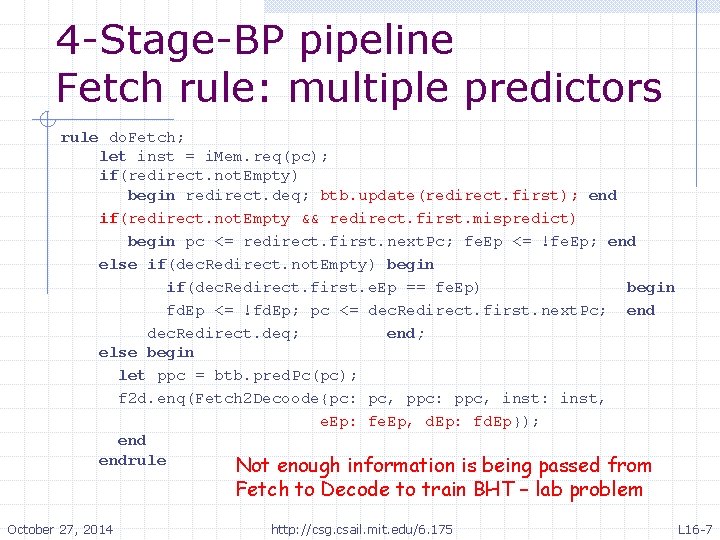

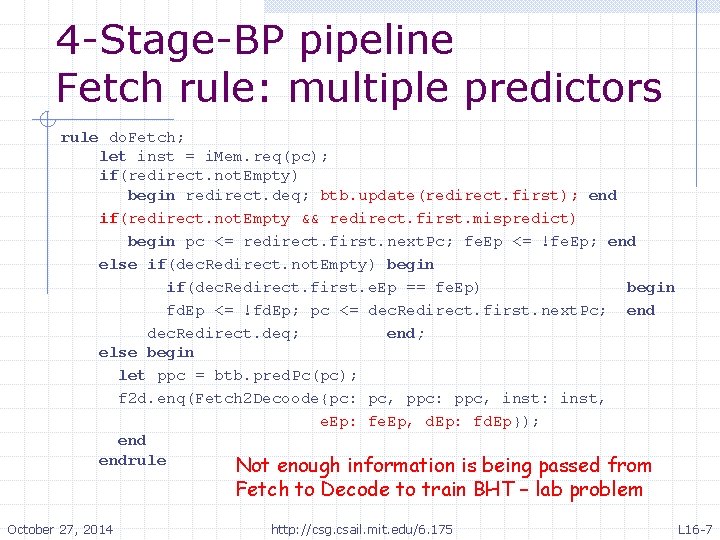

4 -Stage-BP pipeline Fetch rule: multiple predictors rule do. Fetch; let inst = i. Mem. req(pc); if(redirect. not. Empty) begin redirect. deq; btb. update(redirect. first); end if(redirect. not. Empty && redirect. first. mispredict) begin pc <= redirect. first. next. Pc; fe. Ep <= !fe. Ep; end else if(dec. Redirect. not. Empty) begin if(dec. Redirect. first. e. Ep == fe. Ep) begin fd. Ep <= !fd. Ep; pc <= dec. Redirect. first. next. Pc; end dec. Redirect. deq; end; else begin let ppc = btb. pred. Pc(pc); f 2 d. enq(Fetch 2 Decoode{pc: pc, ppc: ppc, inst: inst, e. Ep: fe. Ep, d. Ep: fd. Ep}); endrule Not enough information is being passed from Fetch to Decode to train BHT – lab problem October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -7

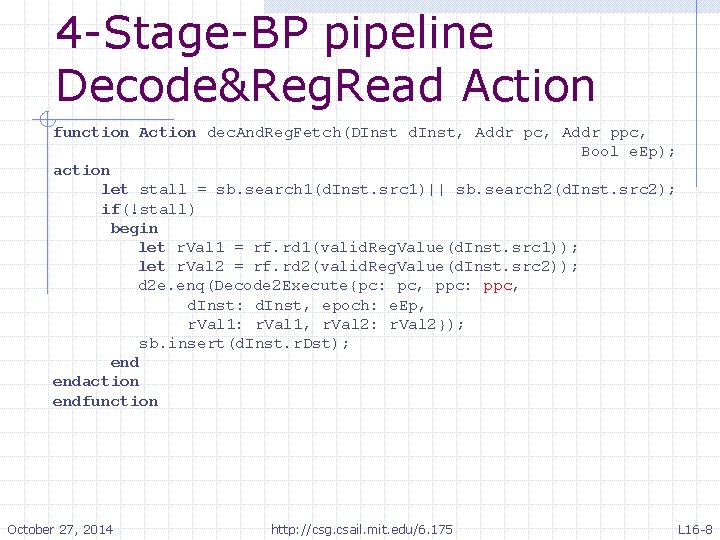

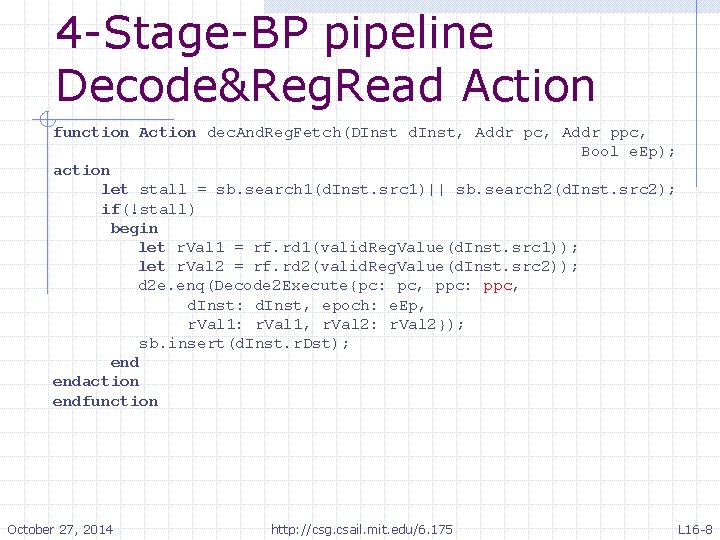

4 -Stage-BP pipeline Decode&Reg. Read Action function Action dec. And. Reg. Fetch(DInst d. Inst, Addr pc, Addr ppc, Bool e. Ep); action let stall = sb. search 1(d. Inst. src 1)|| sb. search 2(d. Inst. src 2); if(!stall) begin let r. Val 1 = rf. rd 1(valid. Reg. Value(d. Inst. src 1)); let r. Val 2 = rf. rd 2(valid. Reg. Value(d. Inst. src 2)); d 2 e. enq(Decode 2 Execute{pc: pc, ppc: ppc, d. Inst: d. Inst, epoch: e. Ep, r. Val 1: r. Val 1, r. Val 2: r. Val 2}); sb. insert(d. Inst. r. Dst); endaction endfunction October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -8

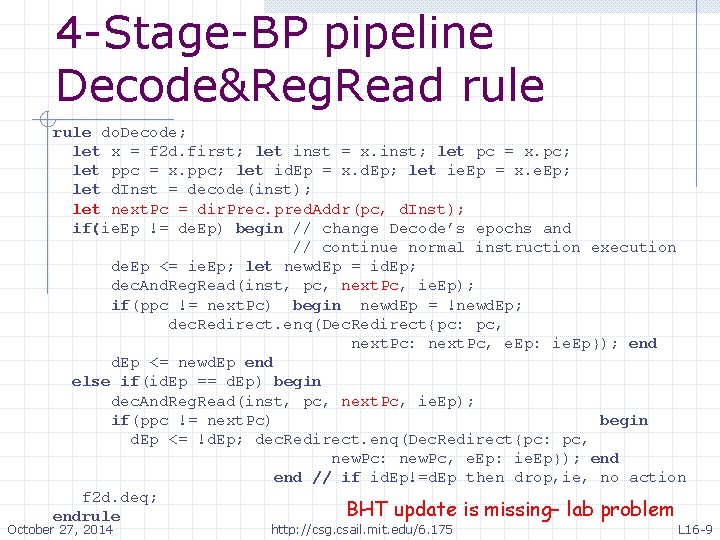

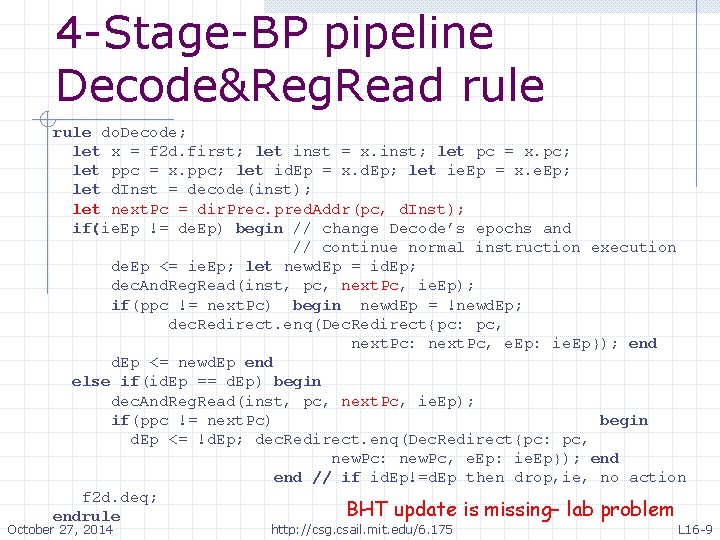

4 -Stage-BP pipeline Decode&Reg. Read rule do. Decode; let x = f 2 d. first; let inst = x. inst; let pc = x. pc; let ppc = x. ppc; let id. Ep = x. d. Ep; let ie. Ep = x. e. Ep; let d. Inst = decode(inst); let next. Pc = dir. Prec. pred. Addr(pc, d. Inst); if(ie. Ep != de. Ep) begin // change Decode’s epochs and // continue normal instruction execution de. Ep <= ie. Ep; let newd. Ep = id. Ep; dec. And. Reg. Read(inst, pc, next. Pc, ie. Ep); if(ppc != next. Pc) begin newd. Ep = !newd. Ep; dec. Redirect. enq(Dec. Redirect{pc: pc, next. Pc: next. Pc, e. Ep: ie. Ep}); end d. Ep <= newd. Ep end else if(id. Ep == d. Ep) begin dec. And. Reg. Read(inst, pc, next. Pc, ie. Ep); if(ppc != next. Pc) begin d. Ep <= !d. Ep; dec. Redirect. enq(Dec. Redirect{pc: pc, new. Pc: new. Pc, e. Ep: ie. Ep}); end // if id. Ep!=d. Ep then drop, ie, no action f 2 d. deq; BHT update is missing– lab problem endrule October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -9

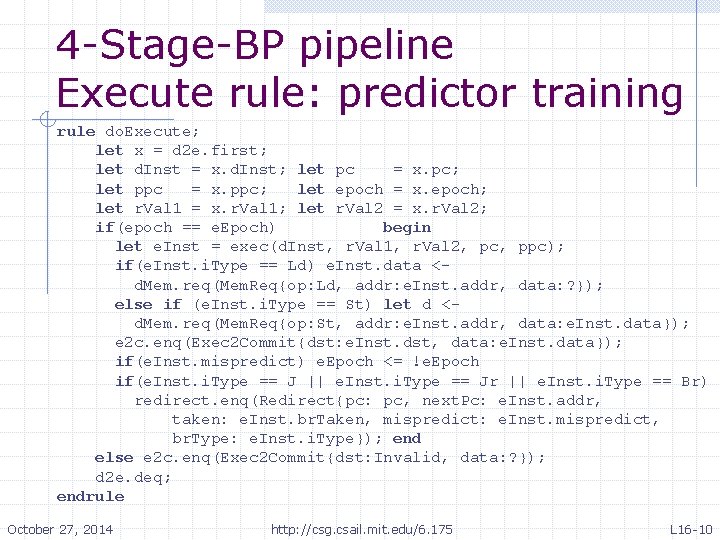

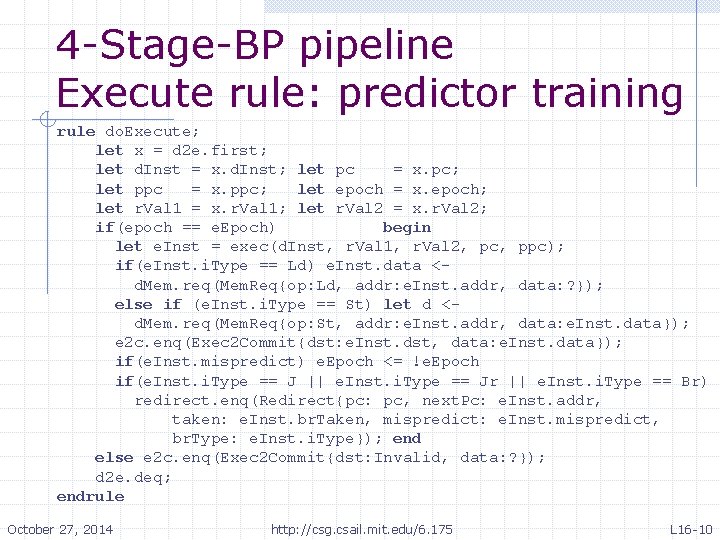

4 -Stage-BP pipeline Execute rule: predictor training rule do. Execute; let x = d 2 e. first; let d. Inst = x. d. Inst; let pc = x. pc; let ppc = x. ppc; let epoch = x. epoch; let r. Val 1 = x. r. Val 1; let r. Val 2 = x. r. Val 2; if(epoch == e. Epoch) begin let e. Inst = exec(d. Inst, r. Val 1, r. Val 2, pc, ppc); if(e. Inst. i. Type == Ld) e. Inst. data <d. Mem. req(Mem. Req{op: Ld, addr: e. Inst. addr, data: ? }); else if (e. Inst. i. Type == St) let d <d. Mem. req(Mem. Req{op: St, addr: e. Inst. addr, data: e. Inst. data}); e 2 c. enq(Exec 2 Commit{dst: e. Inst. dst, data: e. Inst. data}); if(e. Inst. mispredict) e. Epoch <= !e. Epoch if(e. Inst. i. Type == J || e. Inst. i. Type == Jr || e. Inst. i. Type == Br) redirect. enq(Redirect{pc: pc, next. Pc: e. Inst. addr, taken: e. Inst. br. Taken, mispredict: e. Inst. mispredict, br. Type: e. Inst. i. Type}); end else e 2 c. enq(Exec 2 Commit{dst: Invalid, data: ? }); d 2 e. deq; endrule October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -10

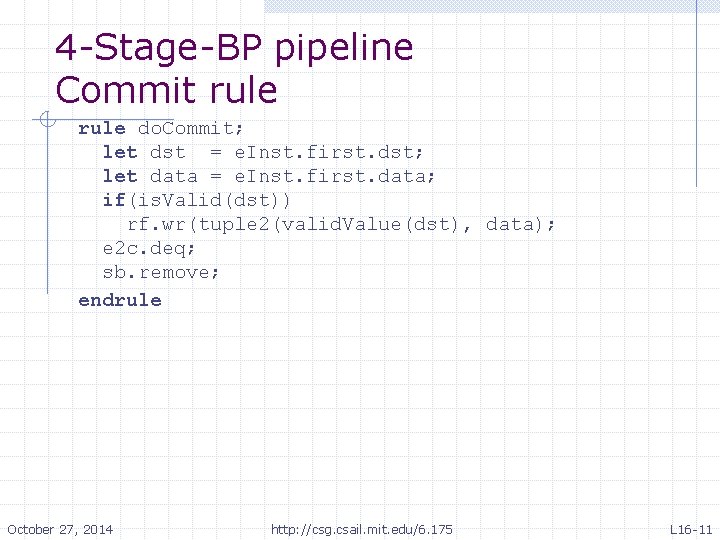

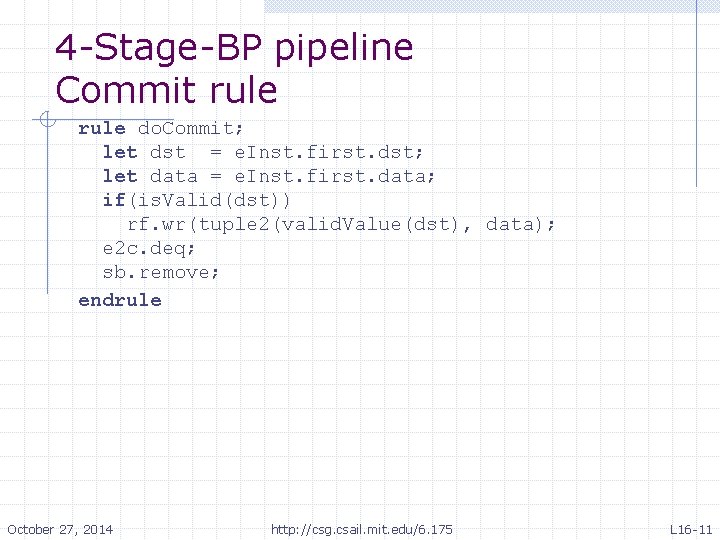

4 -Stage-BP pipeline Commit rule do. Commit; let dst = e. Inst. first. dst; let data = e. Inst. first. data; if(is. Valid(dst)) rf. wr(tuple 2(valid. Value(dst), data); e 2 c. deq; sb. remove; endrule October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -11

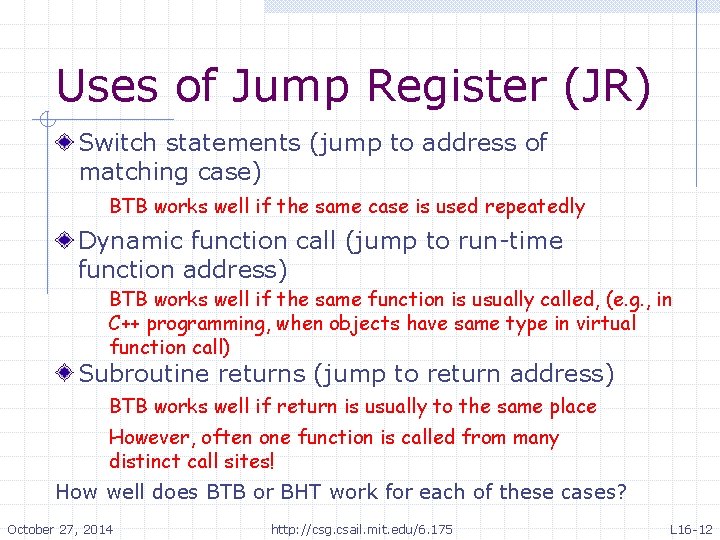

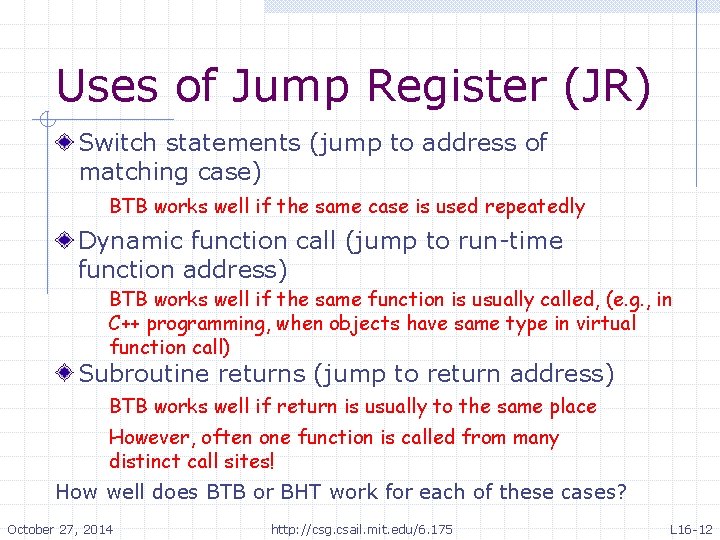

Uses of Jump Register (JR) Switch statements (jump to address of matching case) BTB works well if the same case is used repeatedly Dynamic function call (jump to run-time function address) BTB works well if the same function is usually called, (e. g. , in C++ programming, when objects have same type in virtual function call) Subroutine returns (jump to return address) BTB works well if return is usually to the same place However, often one function is called from many distinct call sites! How well does BTB or BHT work for each of these cases? October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -12

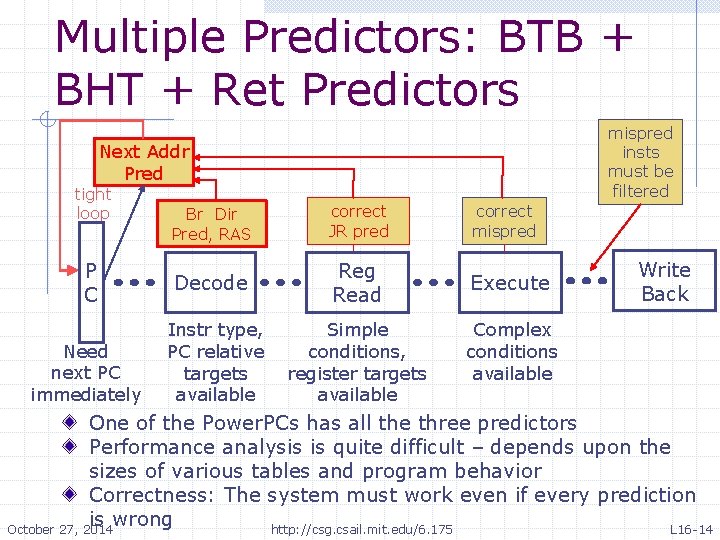

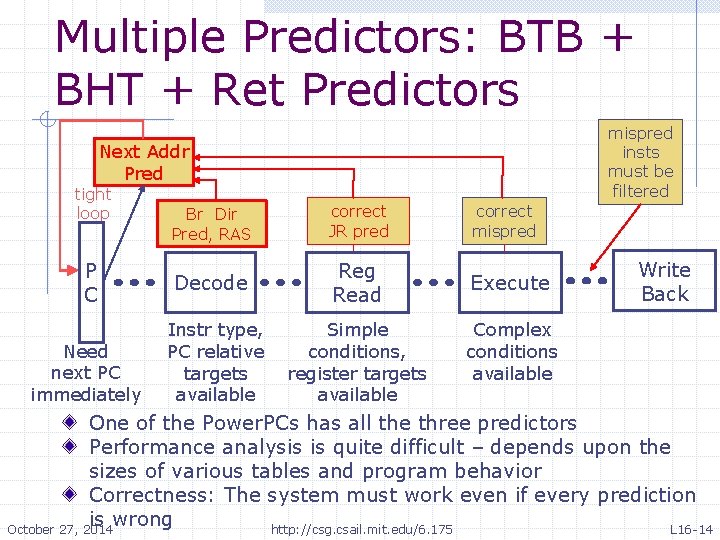

Subroutine Return Stack A small structure to accelerate JR for subroutine returns is typically much more accurate than BTBs Push call address when function call executed fa() { fb(); } fb() { fc(); } fc() { fd(); } Pop return address when subroutine return decoded pc of fd call pc of fc call k entries (typically k=8 -16) pc of fb call October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -13

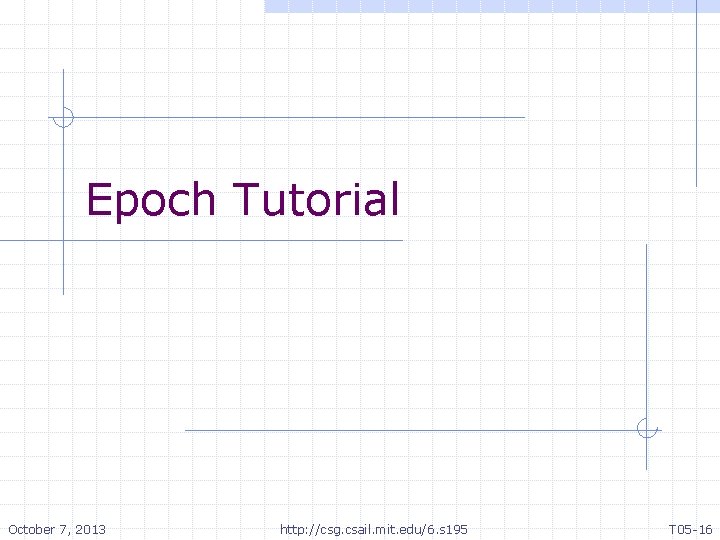

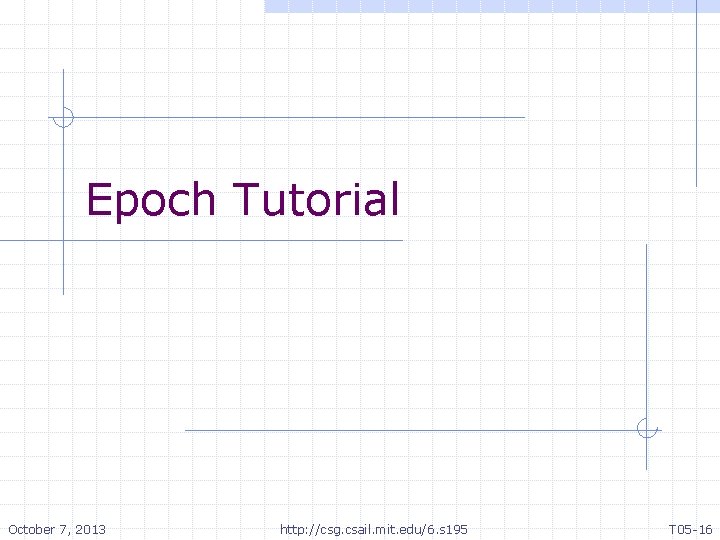

Multiple Predictors: BTB + BHT + Ret Predictors mispred insts must be filtered Next Addr Pred tight loop P C Need next PC immediately Br Dir Pred, RAS correct JR pred correct mispred Decode Reg Read Execute Instr type, PC relative targets available Simple conditions, register targets available Write Back Complex conditions available One of the Power. PCs has all the three predictors Performance analysis is quite difficult – depends upon the sizes of various tables and program behavior Correctness: The system must work even if every prediction is wrong October 27, 2014 http: //csg. csail. mit. edu/6. 175 L 16 -14

October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -15

Epoch Tutorial October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -16

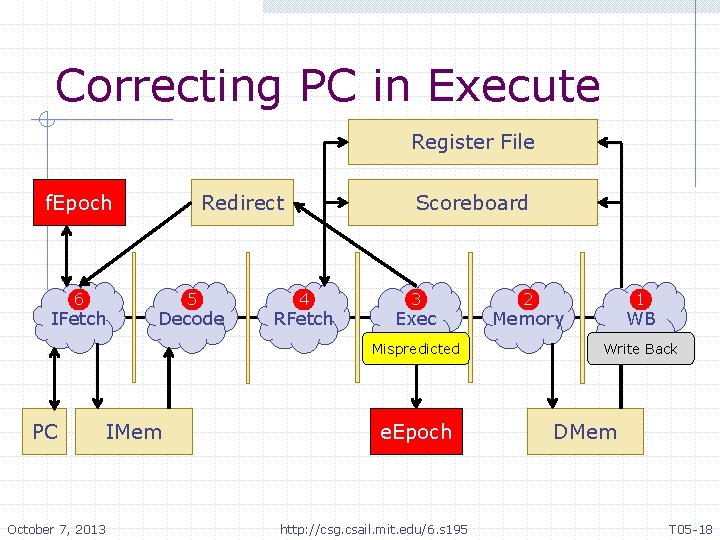

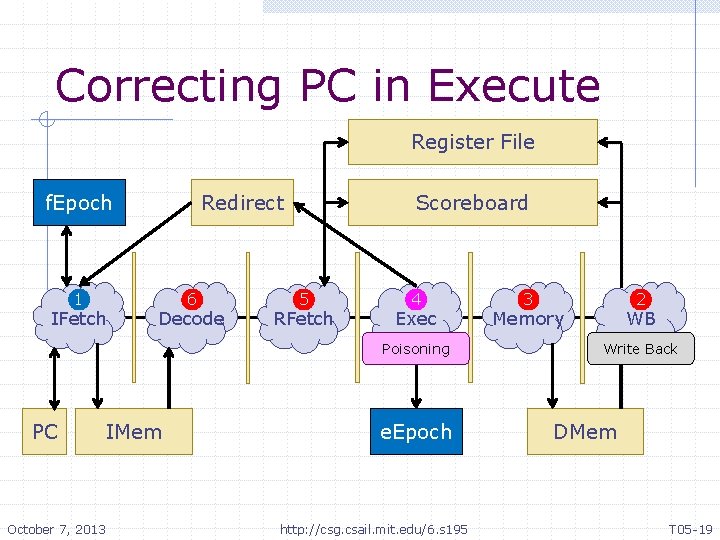

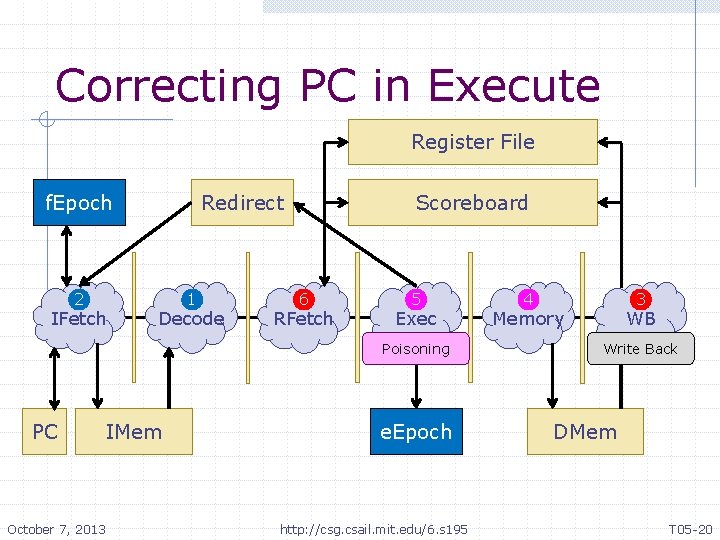

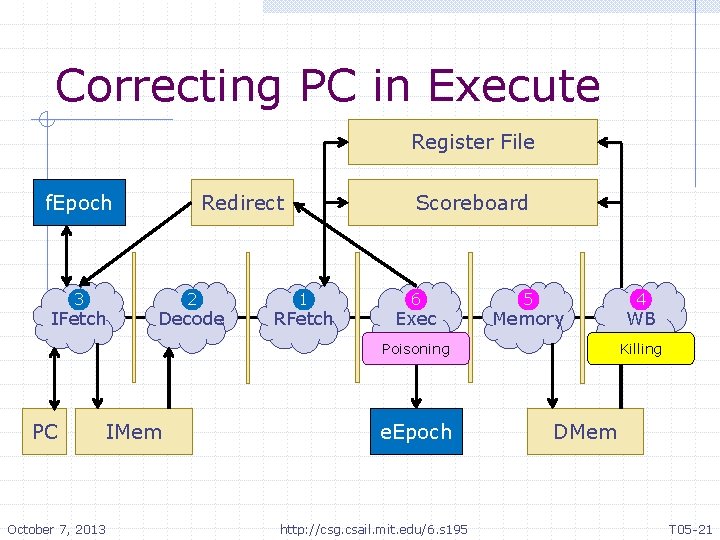

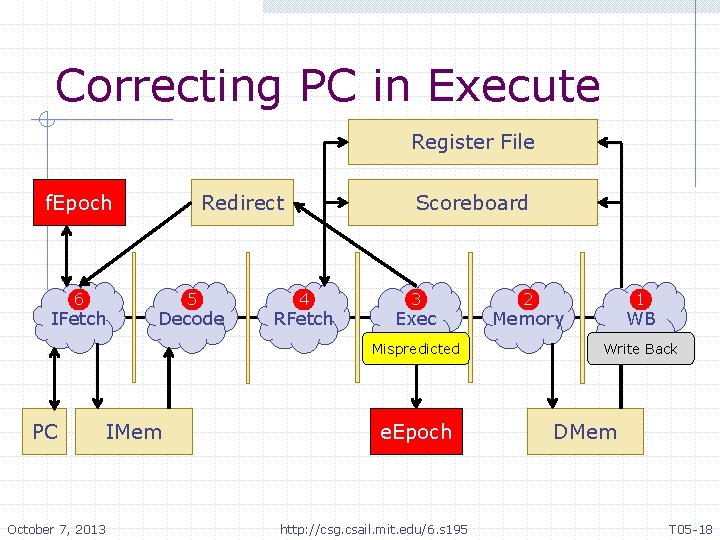

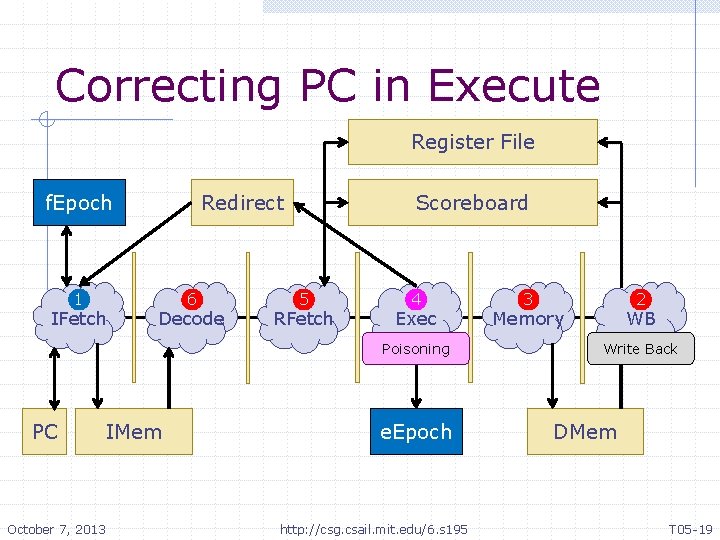

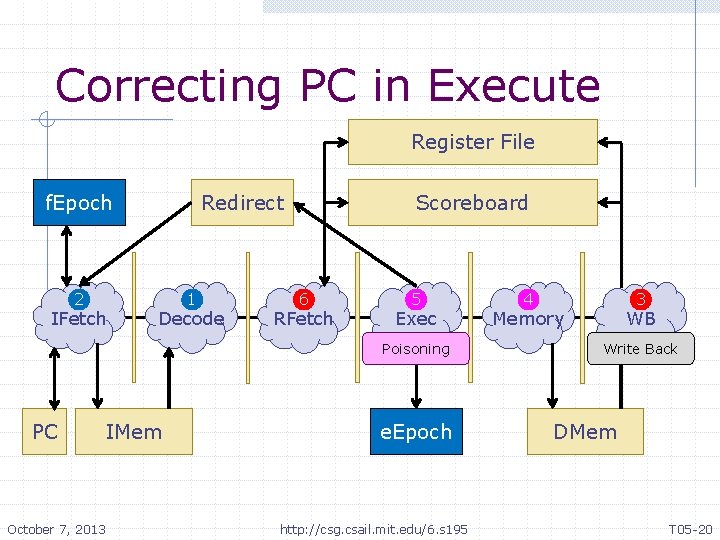

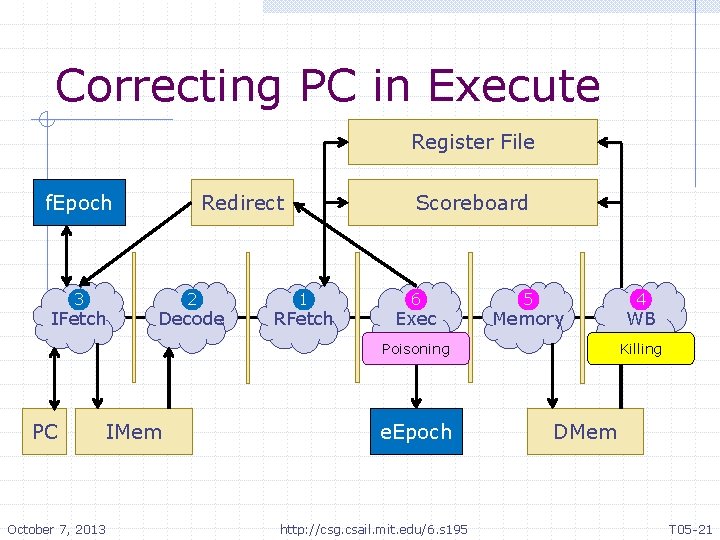

Handling Multiple Epochs If only one epoch changes, it acts just like the case where there is only one epoch. First we are going to look at the execute epoch and the decode epoch separately. October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -17

Correcting PC in Execute Register File f. Epoch 6 IFetch Redirect 5 Decode Scoreboard 4 RFetch 3 Exec Mispredicted PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -18

Correcting PC in Execute Register File f. Epoch 1 IFetch Redirect 6 Decode Scoreboard 5 RFetch 4 Exec Poisoning PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 3 2 Memory WB Write Back DMem T 05 -19

Correcting PC in Execute Register File f. Epoch 2 IFetch Redirect 1 Decode Scoreboard 6 RFetch 5 Exec Poisoning PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 4 3 Memory WB Write Back DMem T 05 -20

Correcting PC in Execute Register File f. Epoch 3 IFetch Redirect 2 Decode Scoreboard 1 RFetch 6 Exec 5 Memory Poisoning PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 4 WB Killing DMem T 05 -21

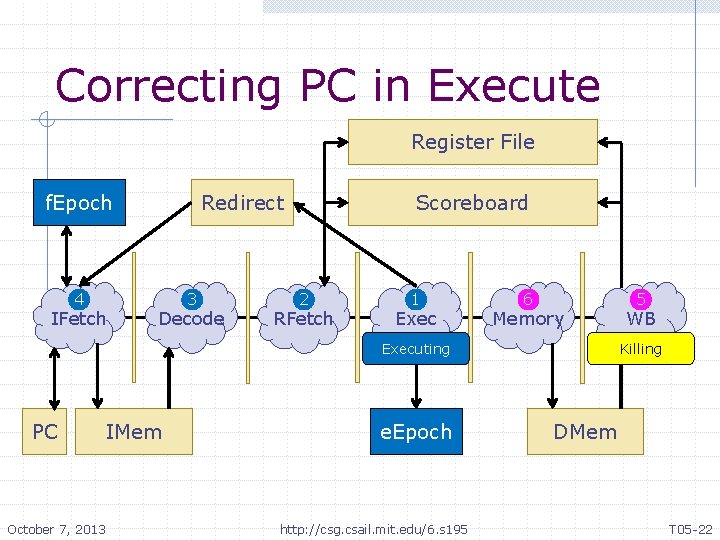

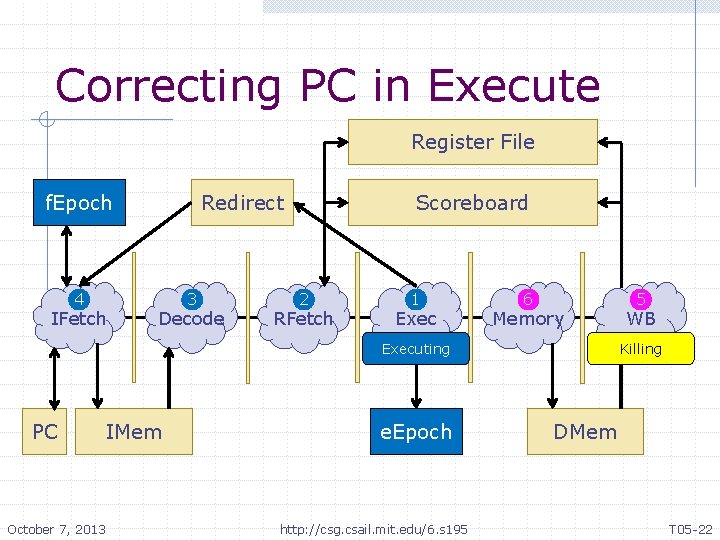

Correcting PC in Execute Register File f. Epoch 4 IFetch Redirect 3 Decode Scoreboard 2 RFetch 1 Exec 6 Memory Executing PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 5 WB Killing DMem T 05 -22

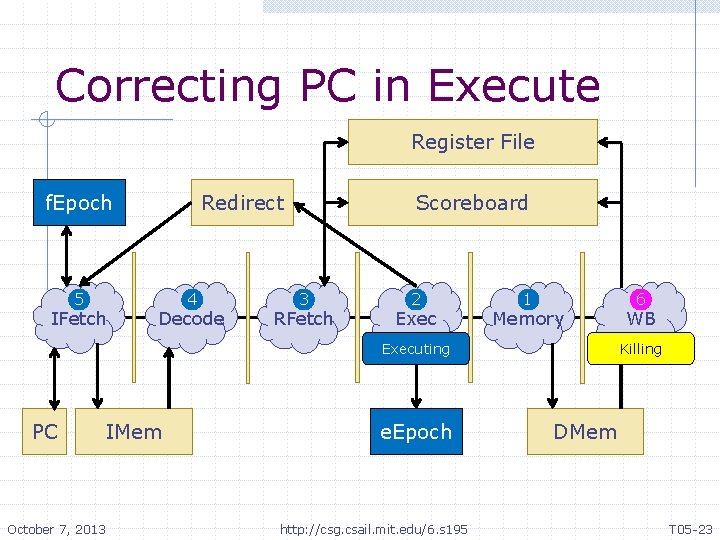

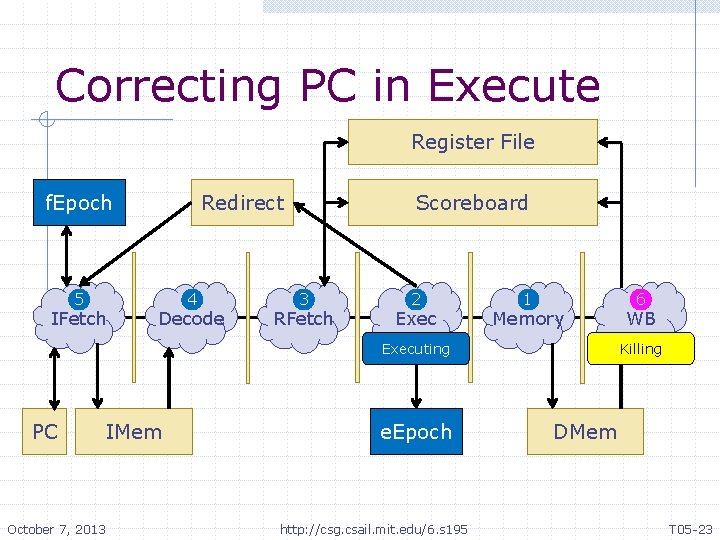

Correcting PC in Execute Register File f. Epoch 5 IFetch Redirect 4 Decode Scoreboard 3 RFetch 2 Exec 1 Memory Executing PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 6 WB Killing DMem T 05 -23

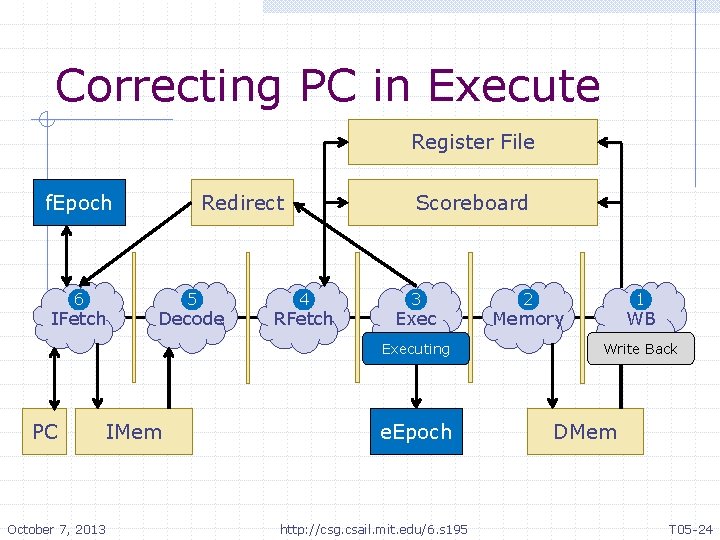

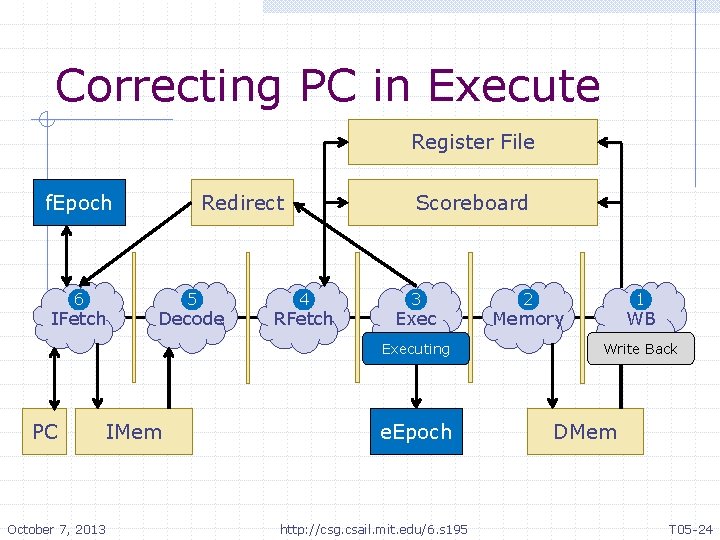

Correcting PC in Execute Register File f. Epoch 6 IFetch Redirect 5 Decode Scoreboard 4 RFetch 3 Executing PC October 7, 2013 IMem e. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -24

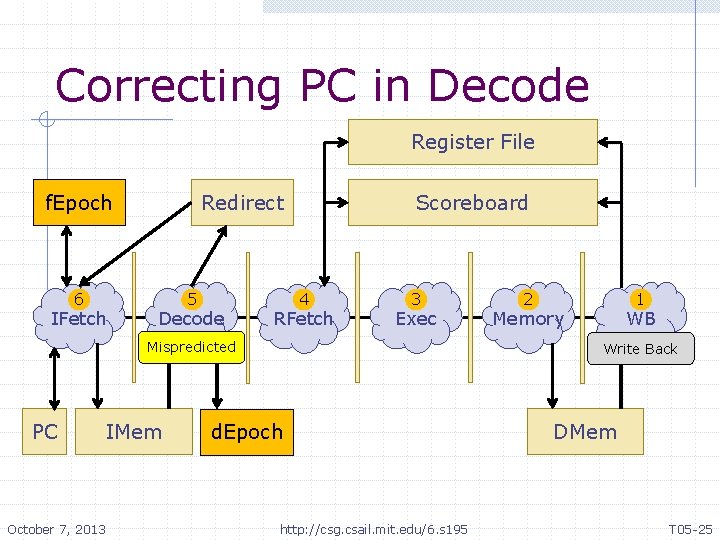

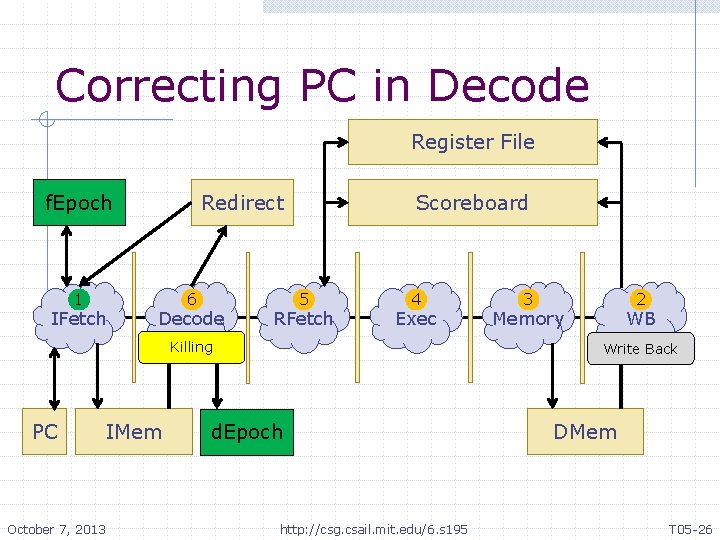

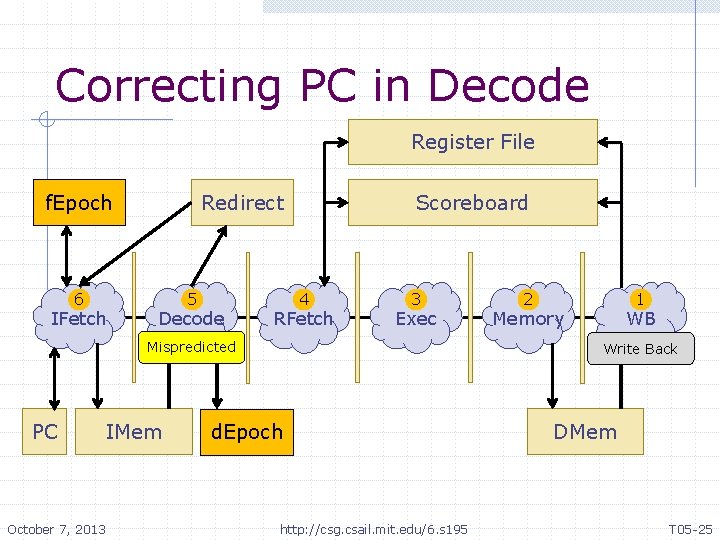

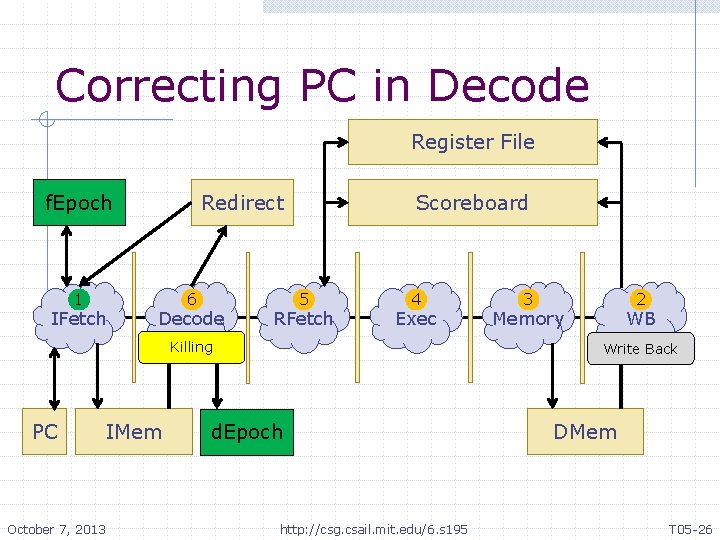

Correcting PC in Decode Register File f. Epoch 6 IFetch Redirect 5 Decode Scoreboard 4 RFetch 3 Exec Mispredicted PC October 7, 2013 IMem 2 1 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -25

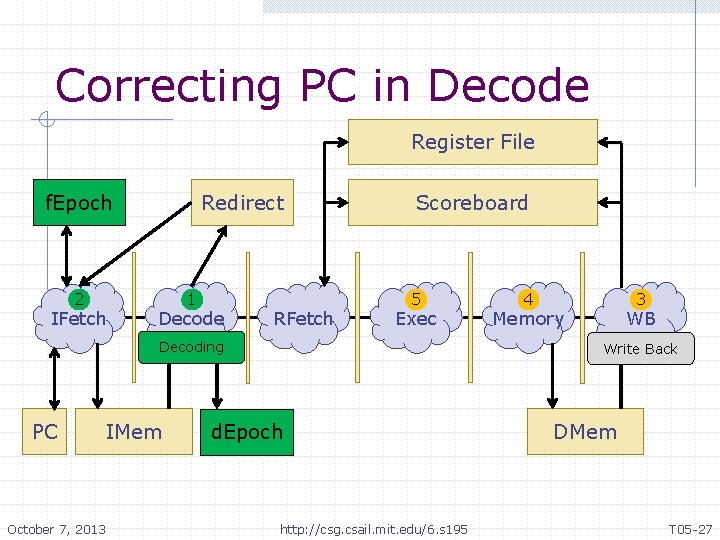

Correcting PC in Decode Register File f. Epoch 1 IFetch Redirect 6 Decode Scoreboard 5 RFetch 4 Exec Killing PC October 7, 2013 IMem 3 2 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -26

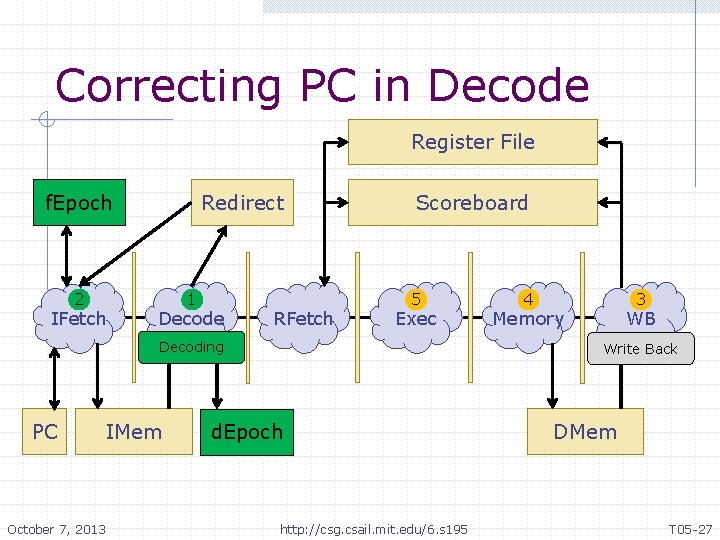

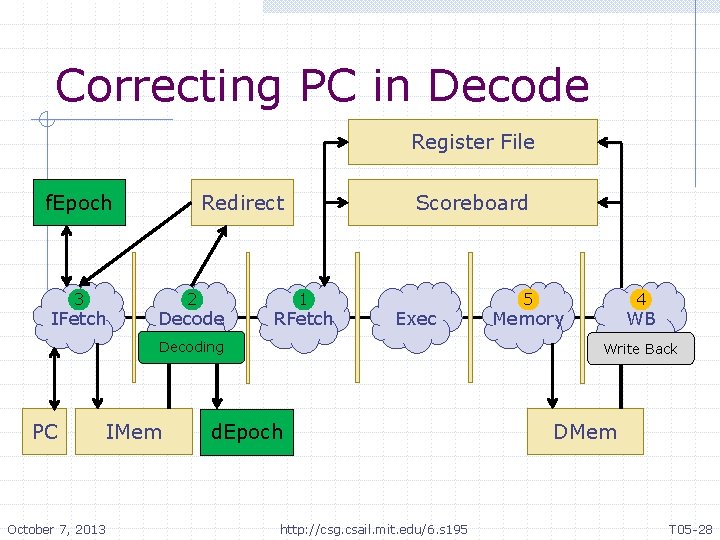

Correcting PC in Decode Register File f. Epoch 2 IFetch Redirect 1 Decode RFetch Scoreboard 5 Exec Decoding PC October 7, 2013 IMem 4 3 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -27

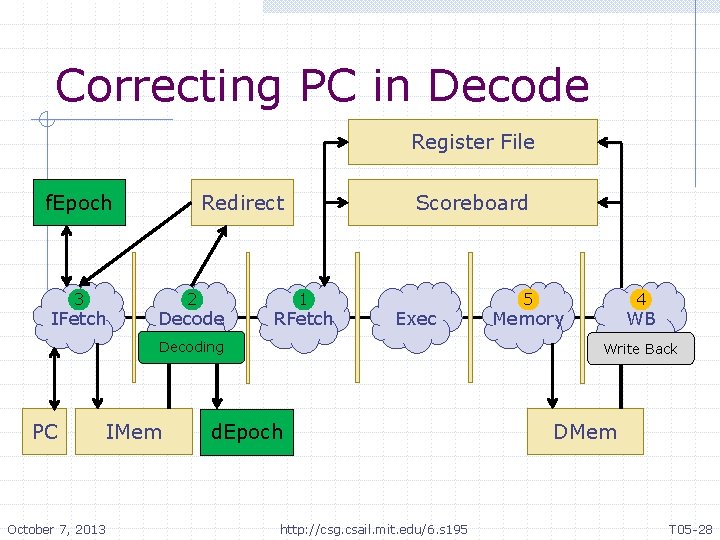

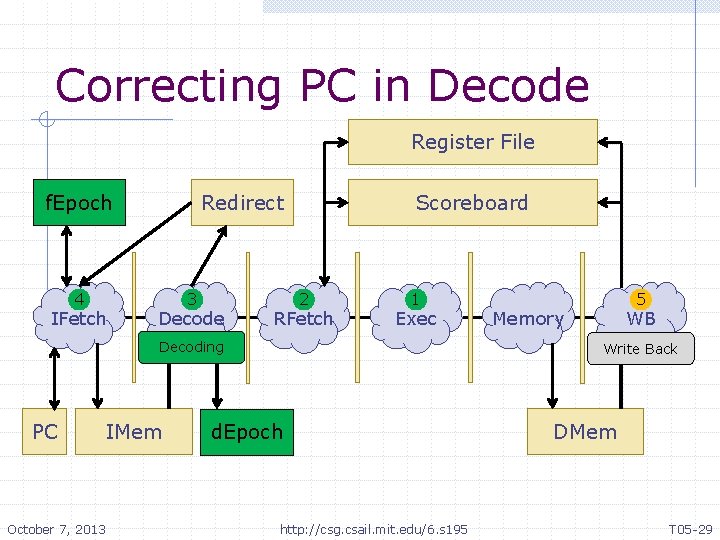

Correcting PC in Decode Register File f. Epoch 3 IFetch Redirect 2 Decode Scoreboard 1 RFetch Exec Decoding PC October 7, 2013 IMem 5 4 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -28

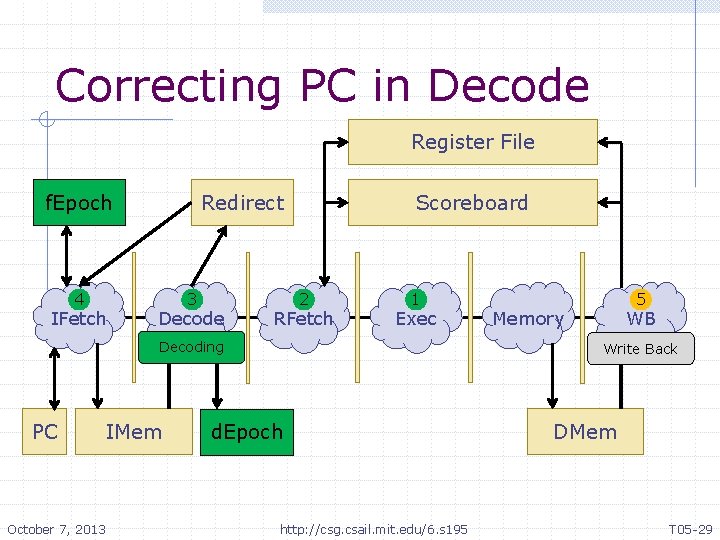

Correcting PC in Decode Register File f. Epoch 4 IFetch Redirect 3 Decode Scoreboard 2 RFetch 1 Exec Decoding PC October 7, 2013 IMem 5 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -29

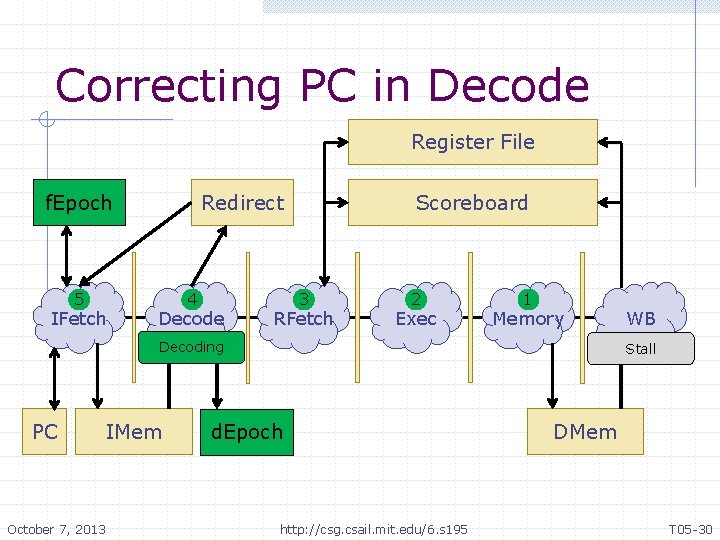

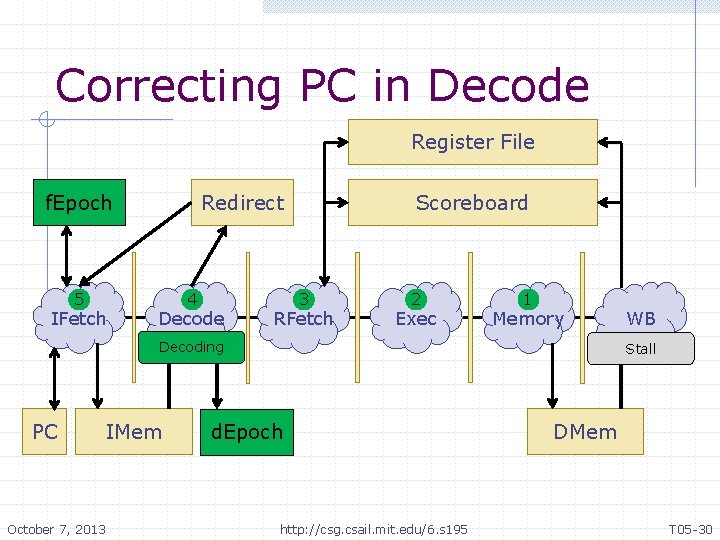

Correcting PC in Decode Register File f. Epoch 5 IFetch Redirect 4 Decode Scoreboard 3 RFetch 2 Exec 1 Memory Decoding PC October 7, 2013 IMem WB Stall d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -30

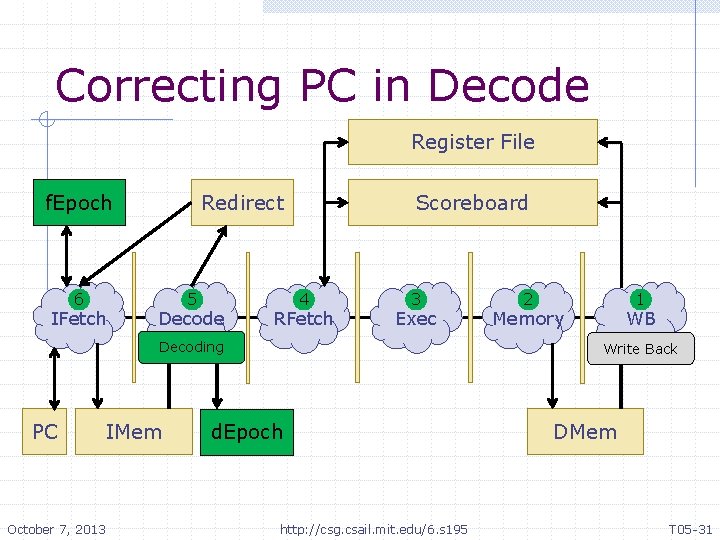

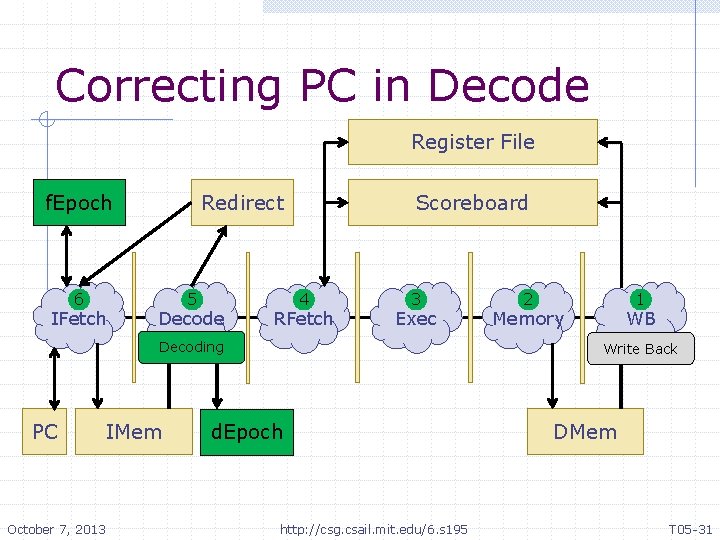

Correcting PC in Decode Register File f. Epoch 6 IFetch Redirect 5 Decode Scoreboard 4 RFetch 3 Exec Decoding PC October 7, 2013 IMem 2 1 Memory WB Write Back d. Epoch http: //csg. csail. mit. edu/6. s 195 DMem T 05 -31

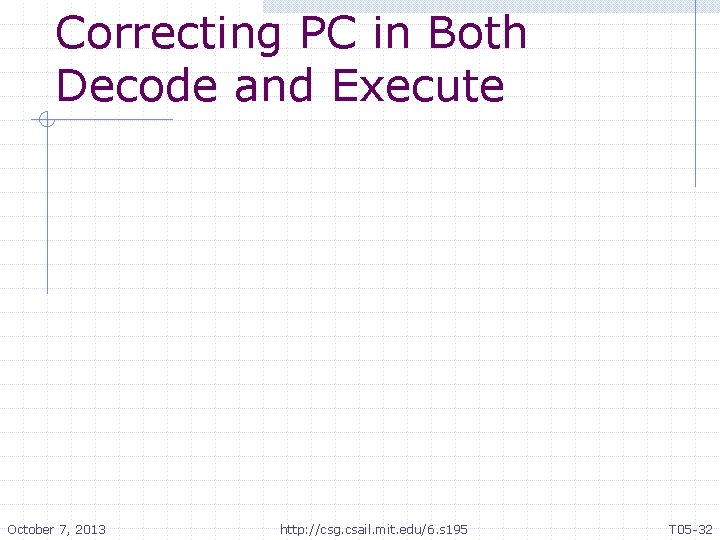

Correcting PC in Both Decode and Execute October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -32

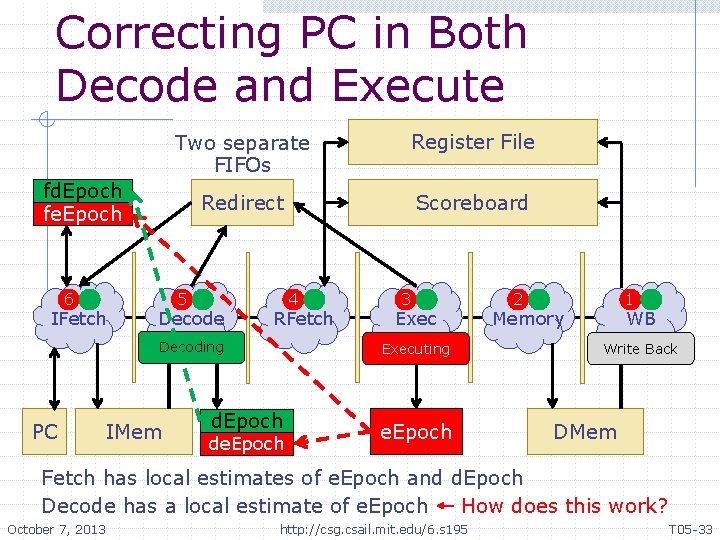

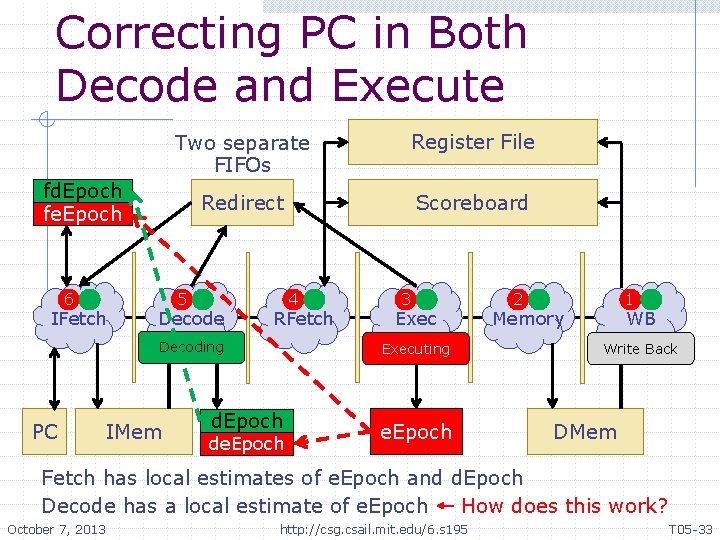

Correcting PC in Both Decode and Execute Two separate FIFOs Register File Redirect Scoreboard fd. Epoch fe. Epoch 6 IFetch 5 Decode 4 RFetch Decoding PC IMem 3 Executing d. Epoch de. Epoch 2 1 Memory WB Write Back DMem Fetch has local estimates of e. Epoch and d. Epoch Decode has a local estimate of e. Epoch How does this work? October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -33

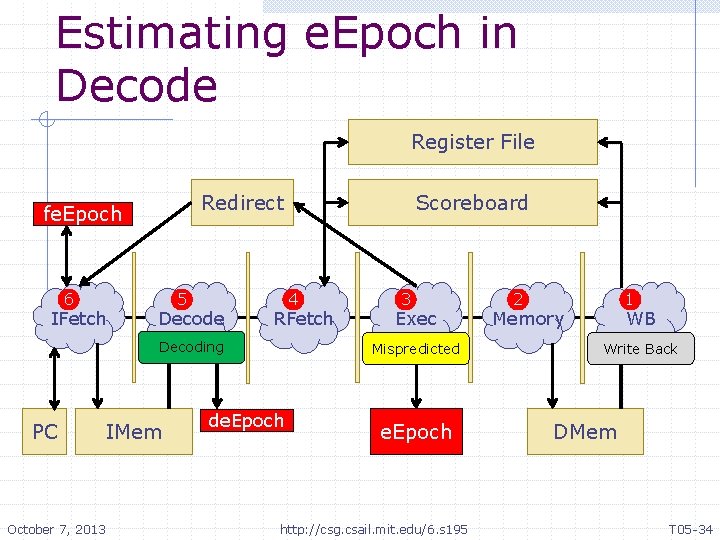

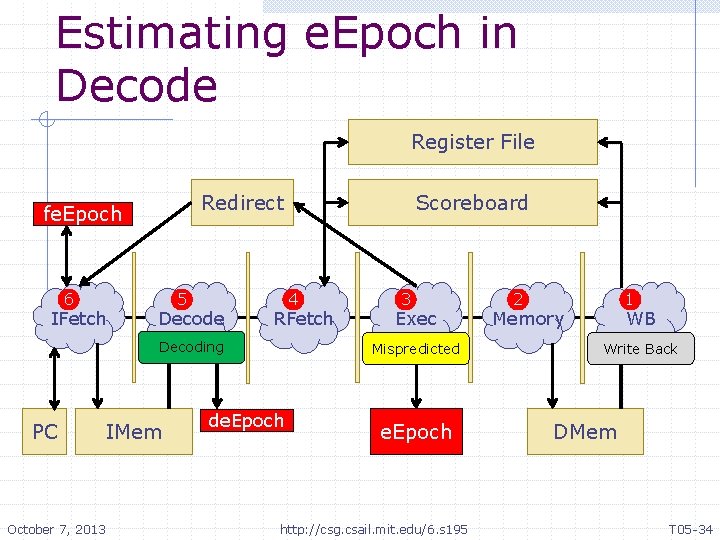

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 6 IFetch 5 Decode 4 RFetch Decoding PC October 7, 2013 IMem Scoreboard 3 Exec Mispredicted de. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -34

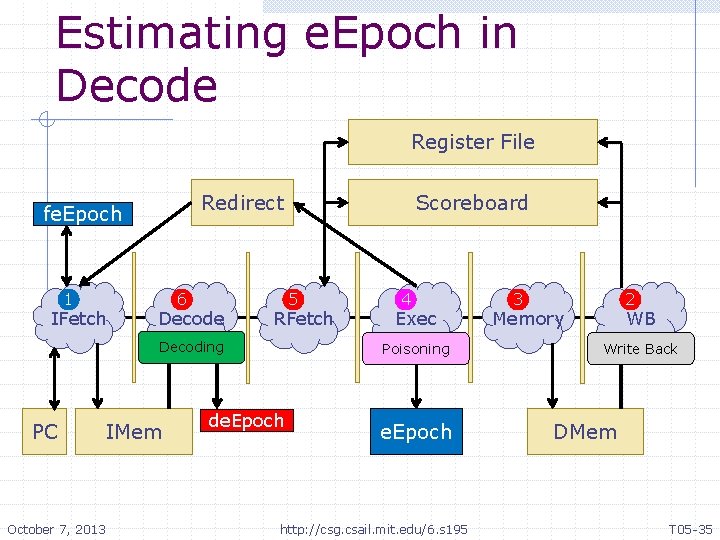

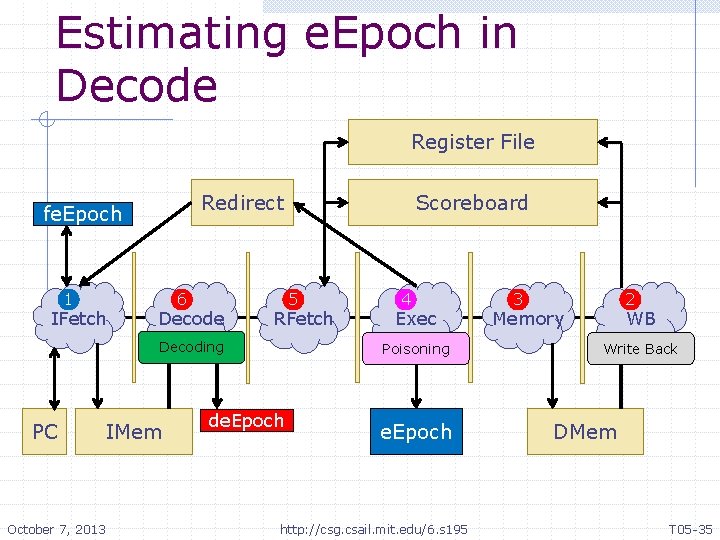

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 1 IFetch 6 Decode 5 RFetch Decoding PC October 7, 2013 IMem Scoreboard 4 Exec Poisoning de. Epoch http: //csg. csail. mit. edu/6. s 195 3 2 Memory WB Write Back DMem T 05 -35

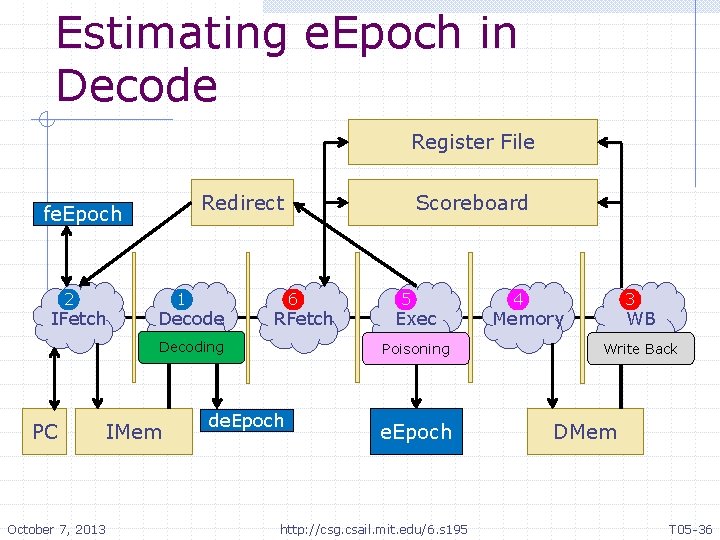

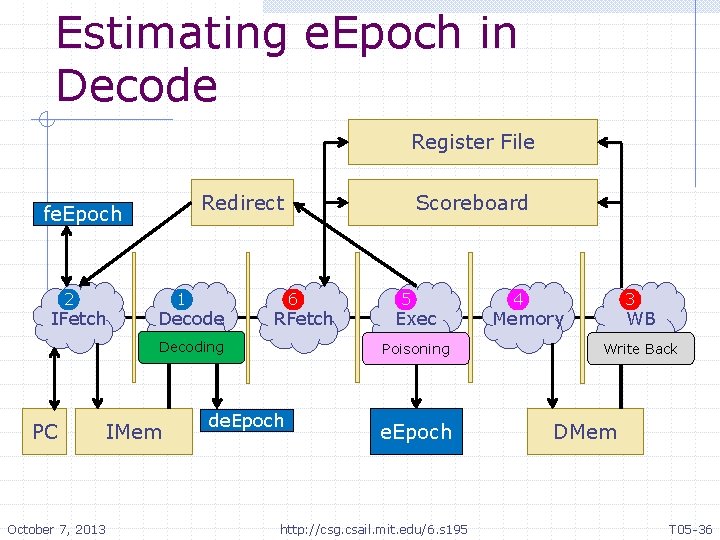

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 2 IFetch 1 Decode 6 RFetch Decoding PC October 7, 2013 IMem Scoreboard 5 Exec Poisoning de. Epoch http: //csg. csail. mit. edu/6. s 195 4 3 Memory WB Write Back DMem T 05 -36

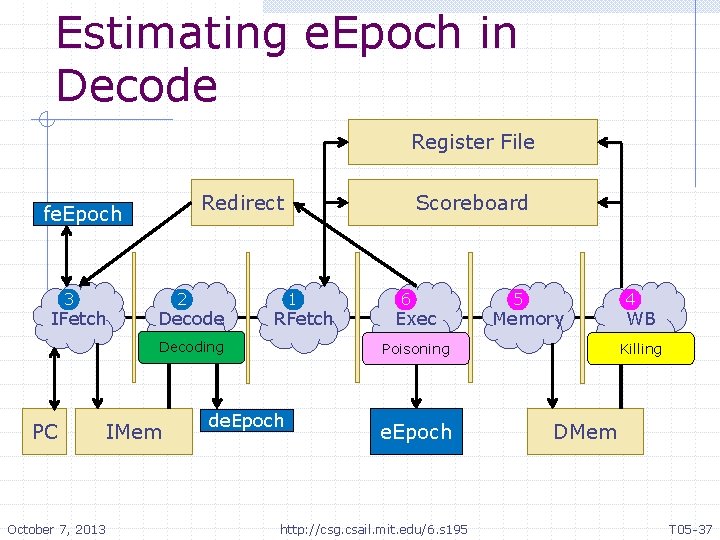

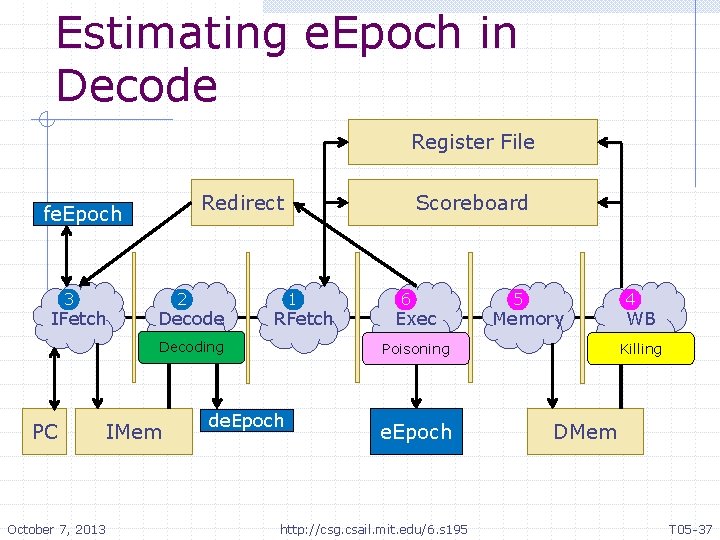

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 3 IFetch 2 Decode 1 RFetch Decoding PC October 7, 2013 IMem Scoreboard 6 Exec 5 Memory Poisoning de. Epoch http: //csg. csail. mit. edu/6. s 195 4 WB Killing DMem T 05 -37

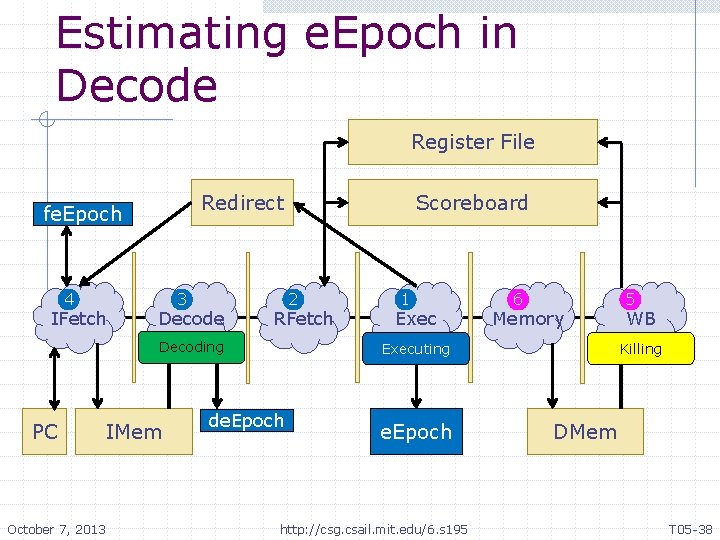

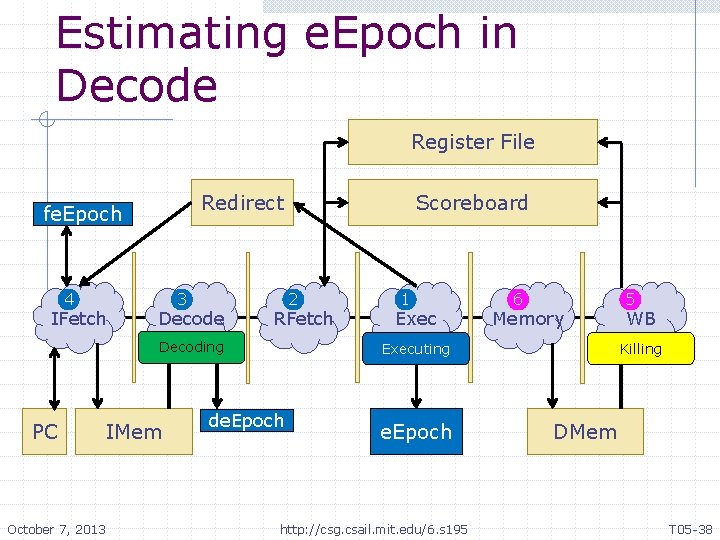

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 4 IFetch 3 Decode 2 RFetch Decoding PC October 7, 2013 IMem Scoreboard 1 Exec 6 Memory Executing de. Epoch http: //csg. csail. mit. edu/6. s 195 5 WB Killing DMem T 05 -38

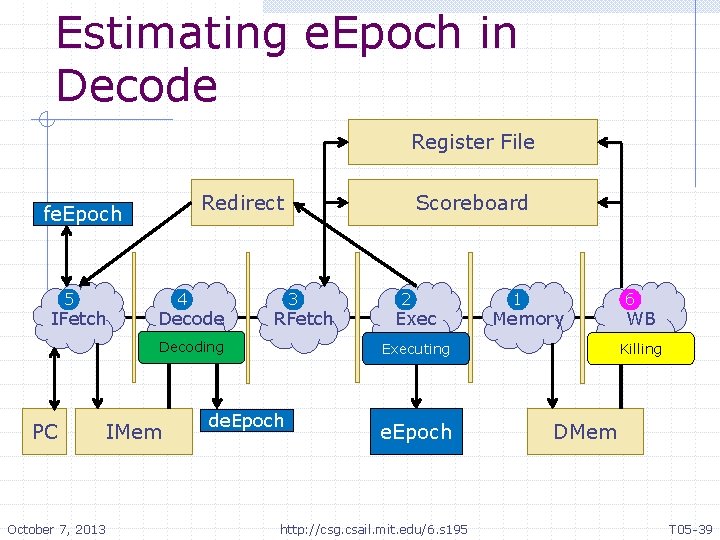

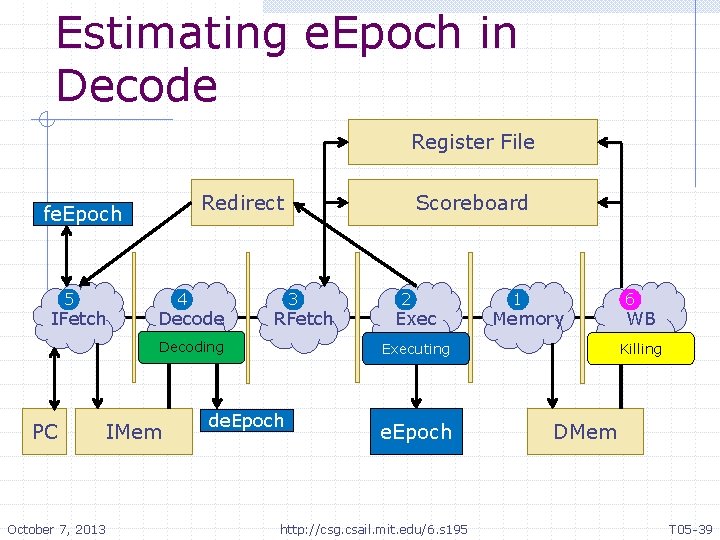

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 5 IFetch 4 Decode 3 RFetch Decoding PC October 7, 2013 IMem Scoreboard 2 Exec 1 Memory Executing de. Epoch http: //csg. csail. mit. edu/6. s 195 6 WB Killing DMem T 05 -39

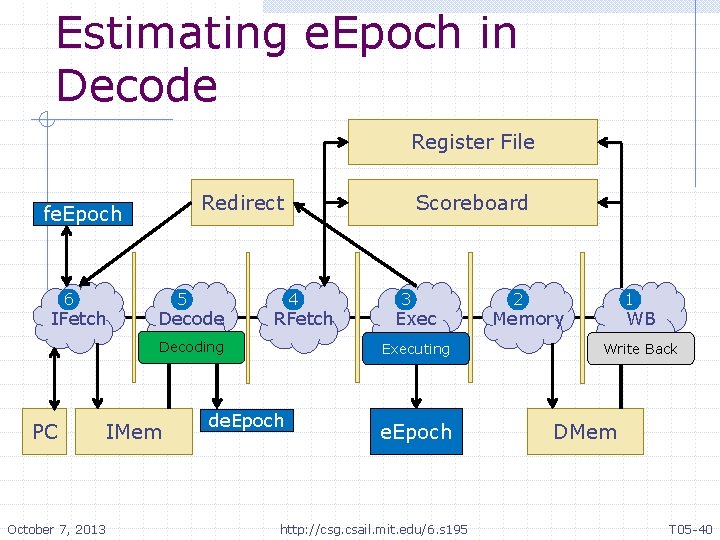

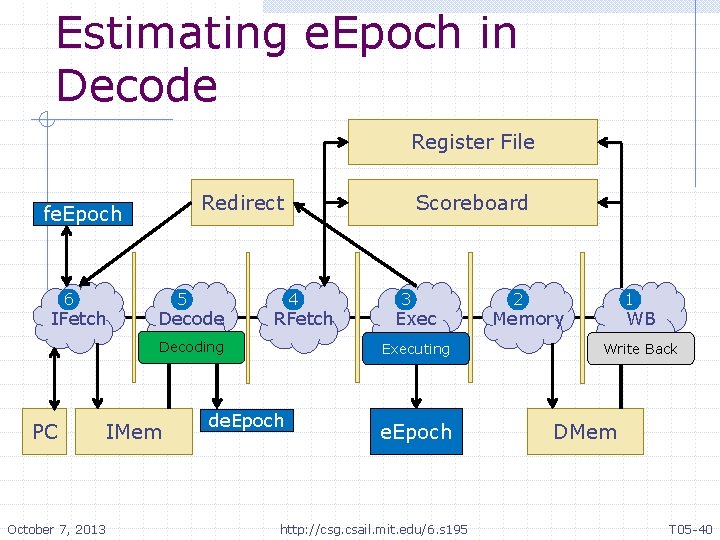

Estimating e. Epoch in Decode Register File Redirect fe. Epoch 6 IFetch 5 Decode 4 RFetch Decoding PC October 7, 2013 IMem Scoreboard 3 Executing de. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -40

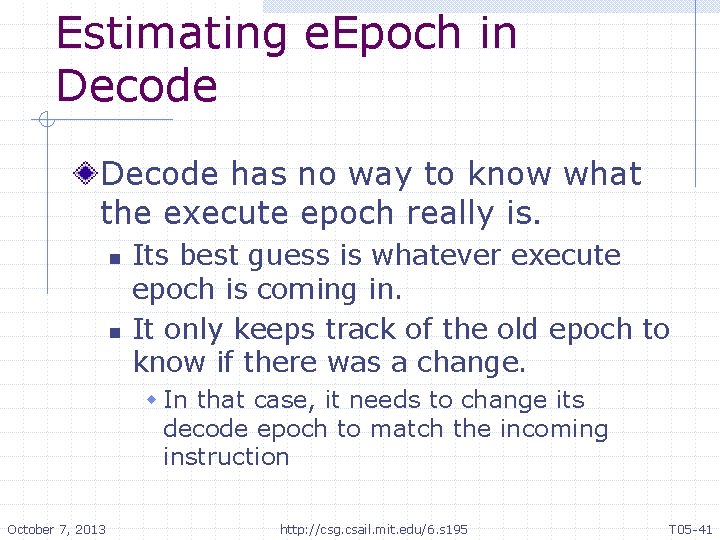

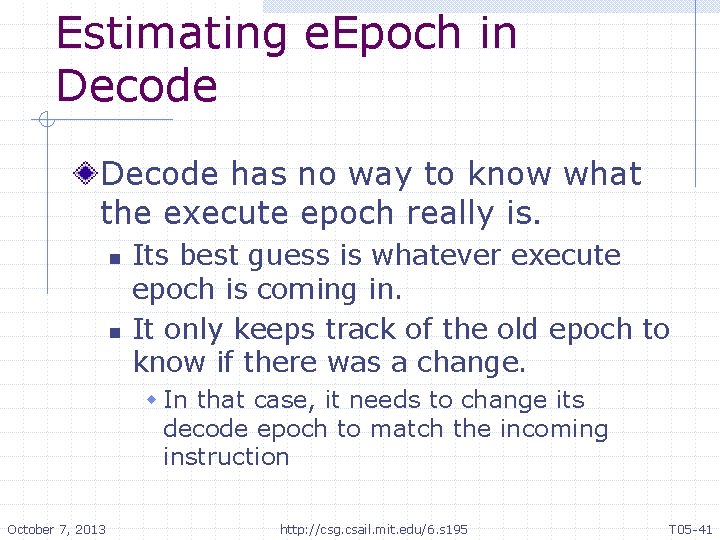

Estimating e. Epoch in Decode has no way to know what the execute epoch really is. n n Its best guess is whatever execute epoch is coming in. It only keeps track of the old epoch to know if there was a change. w In that case, it needs to change its decode epoch to match the incoming instruction October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -41

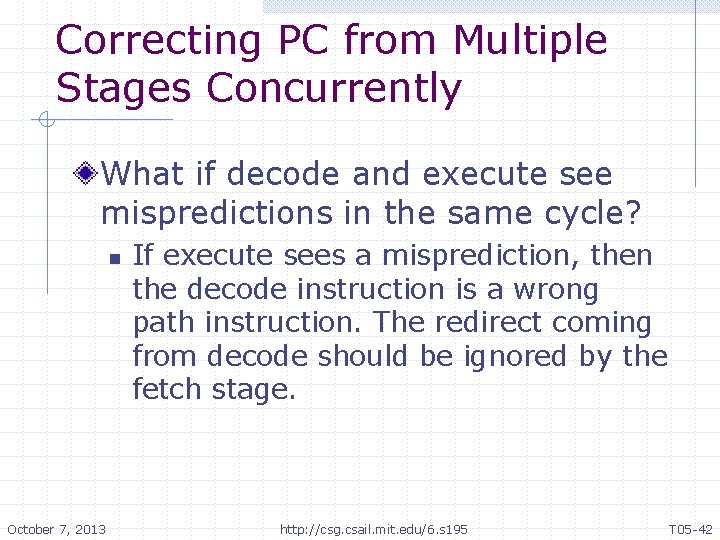

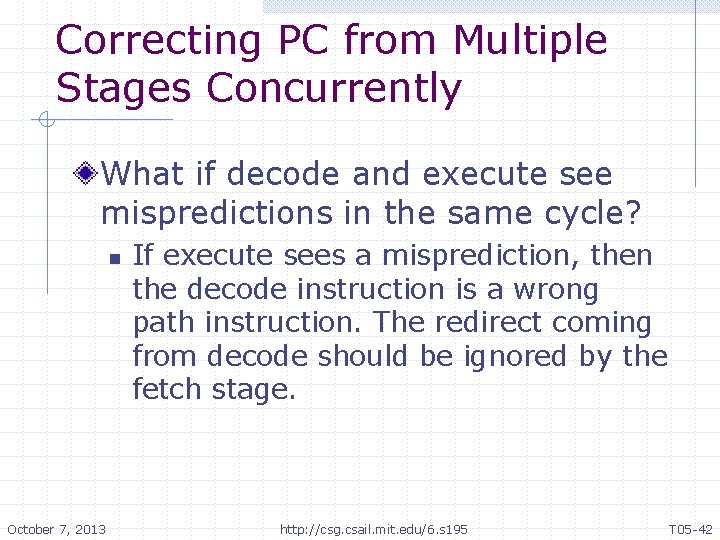

Correcting PC from Multiple Stages Concurrently What if decode and execute see mispredictions in the same cycle? n October 7, 2013 If execute sees a misprediction, then the decode instruction is a wrong path instruction. The redirect coming from decode should be ignored by the fetch stage. http: //csg. csail. mit. edu/6. s 195 T 05 -42

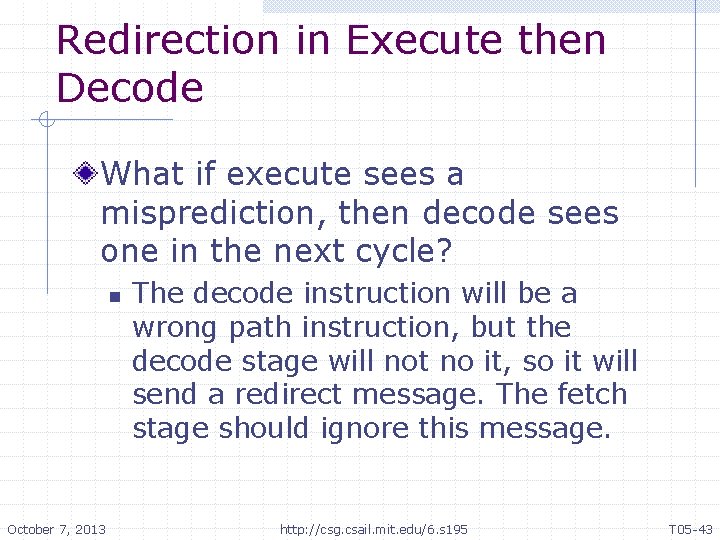

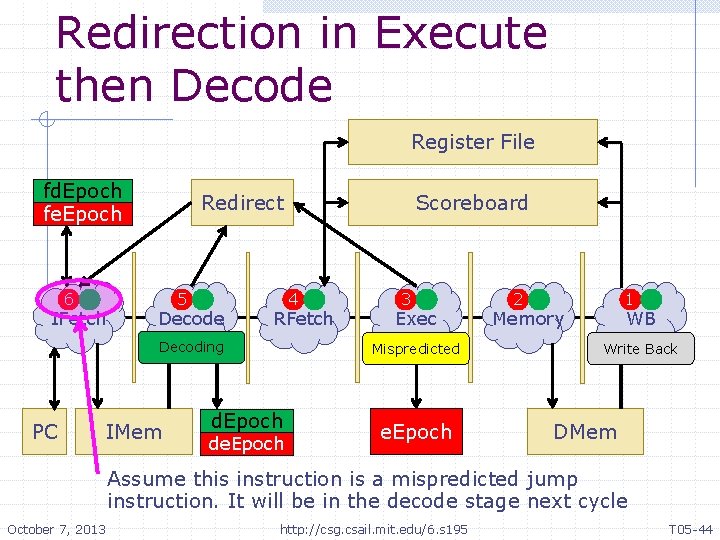

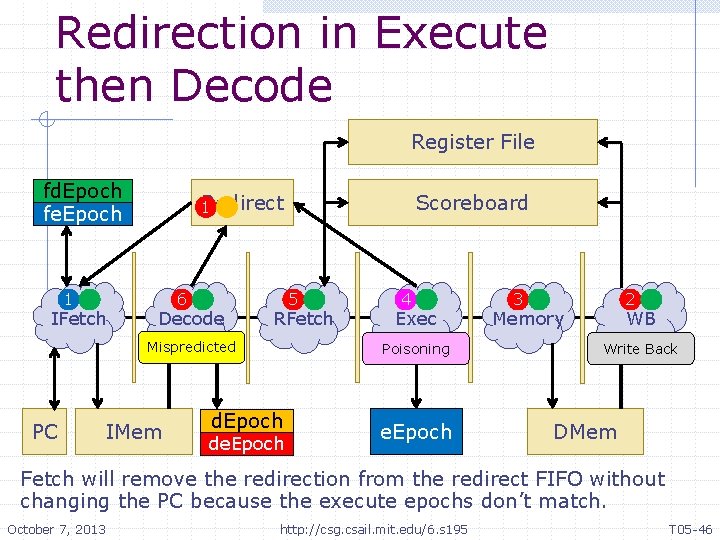

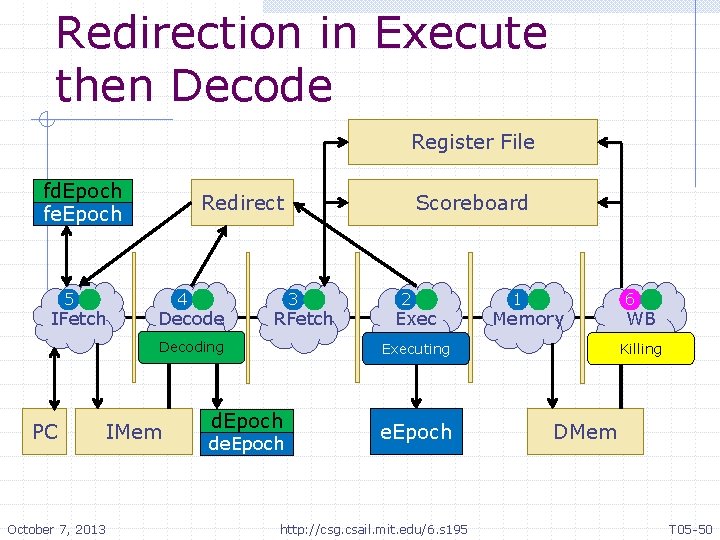

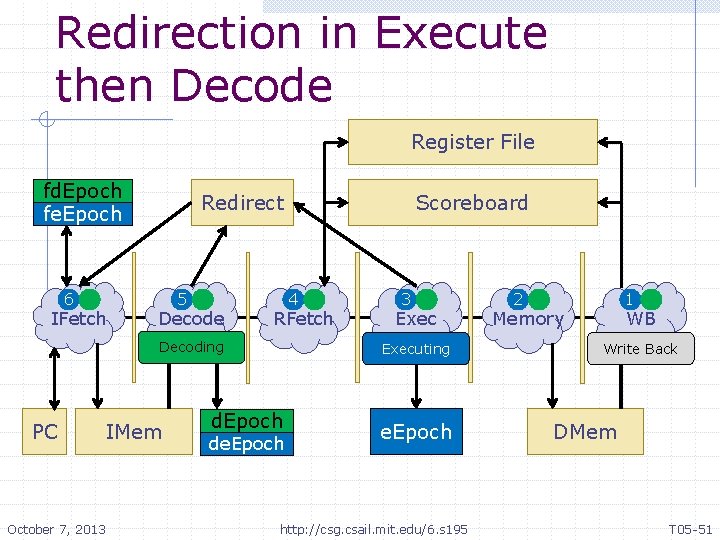

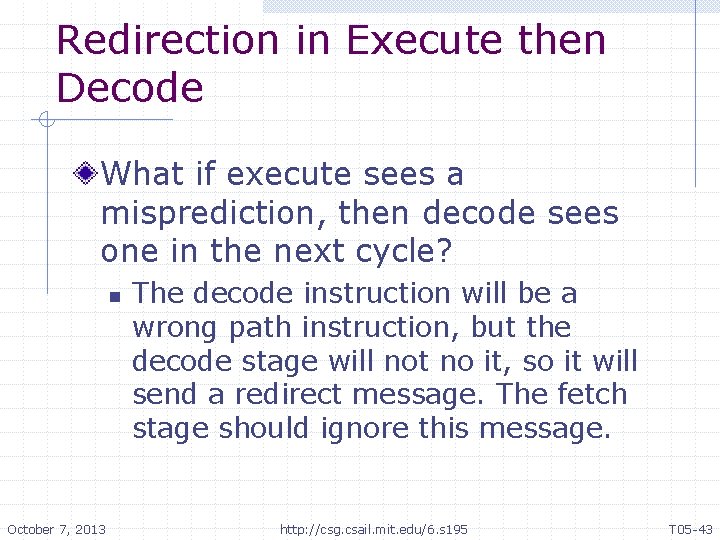

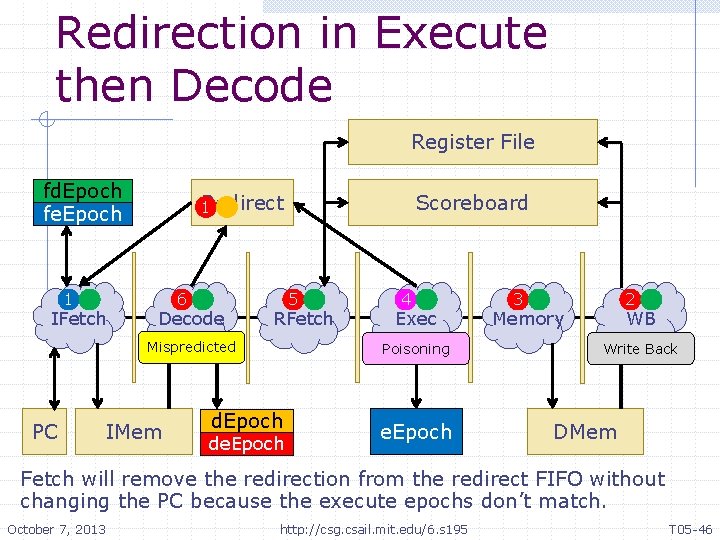

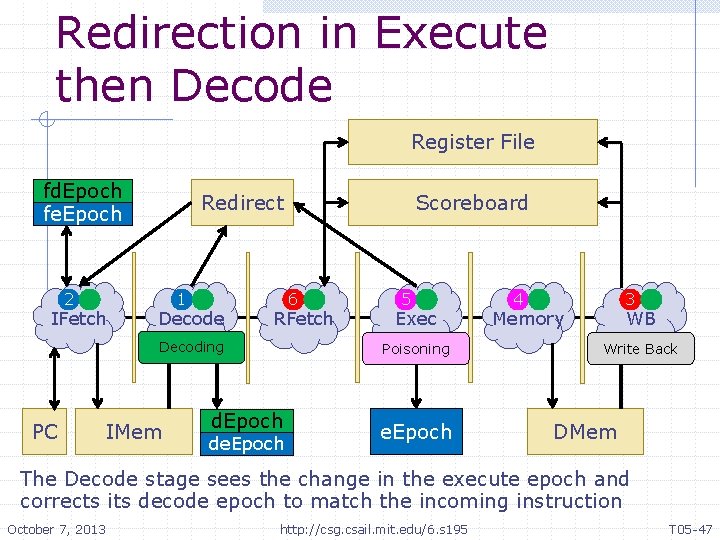

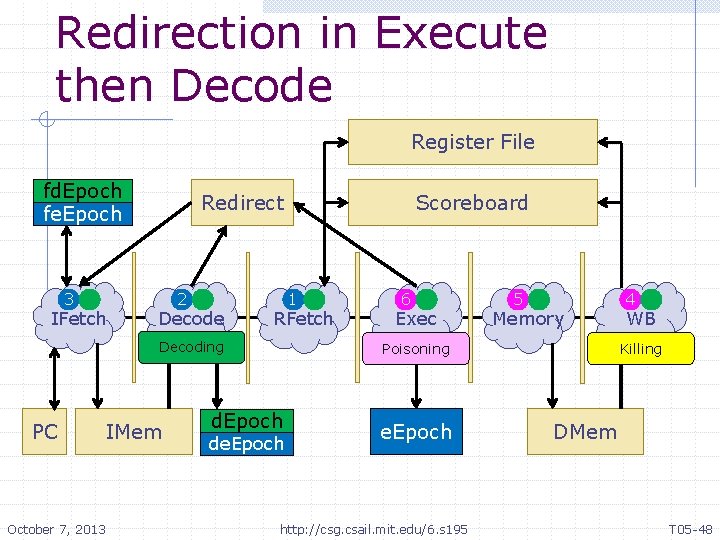

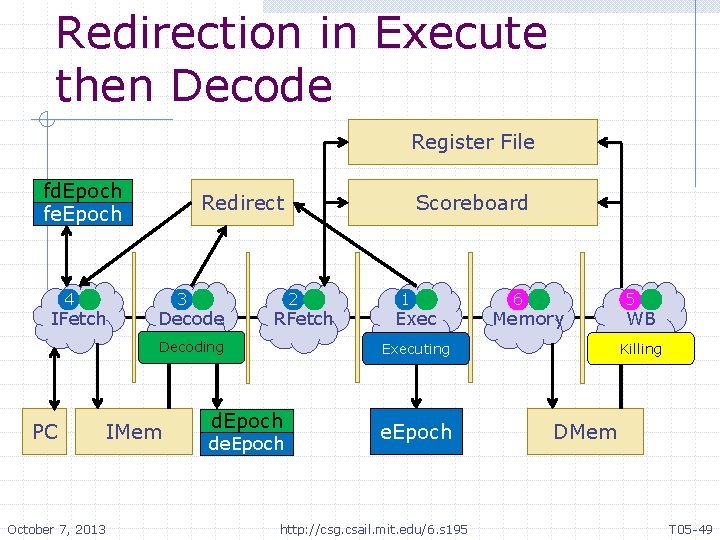

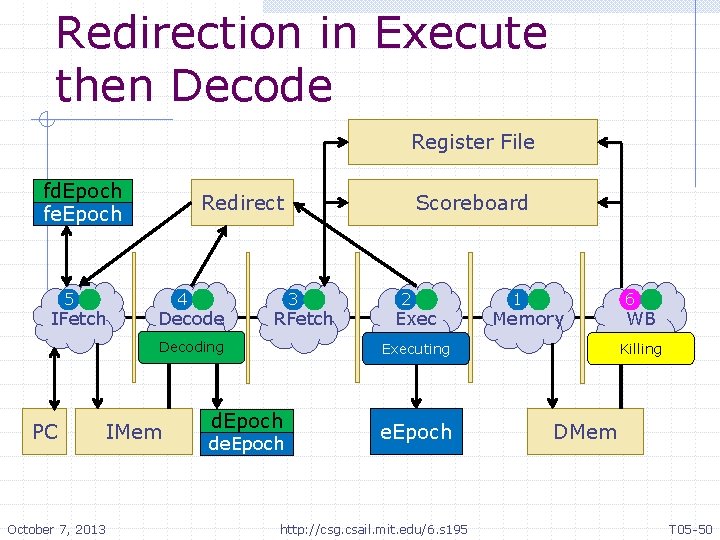

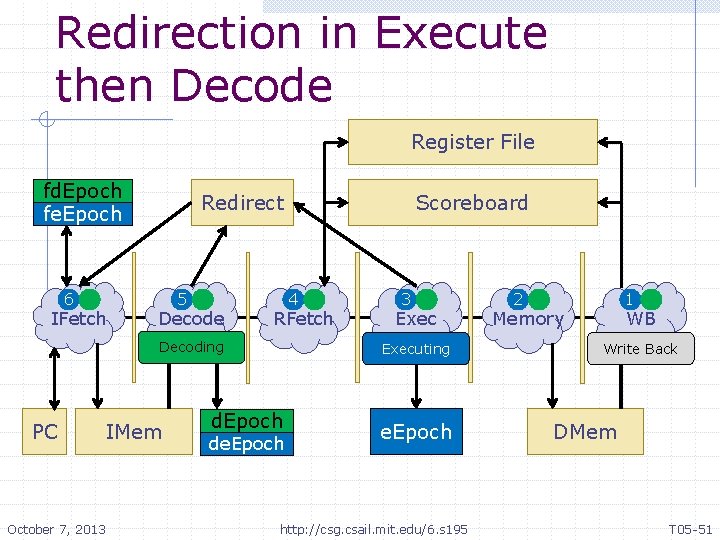

Redirection in Execute then Decode What if execute sees a misprediction, then decode sees one in the next cycle? n October 7, 2013 The decode instruction will be a wrong path instruction, but the decode stage will not no it, so it will send a redirect message. The fetch stage should ignore this message. http: //csg. csail. mit. edu/6. s 195 T 05 -43

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 6 IFetch Redirect 5 Decode 4 RFetch Decoding PC IMem Scoreboard 3 Exec Mispredicted d. Epoch de. Epoch 2 1 Memory WB Write Back DMem Assume this instruction is a mispredicted jump instruction. It will be in the decode stage next cycle October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -44

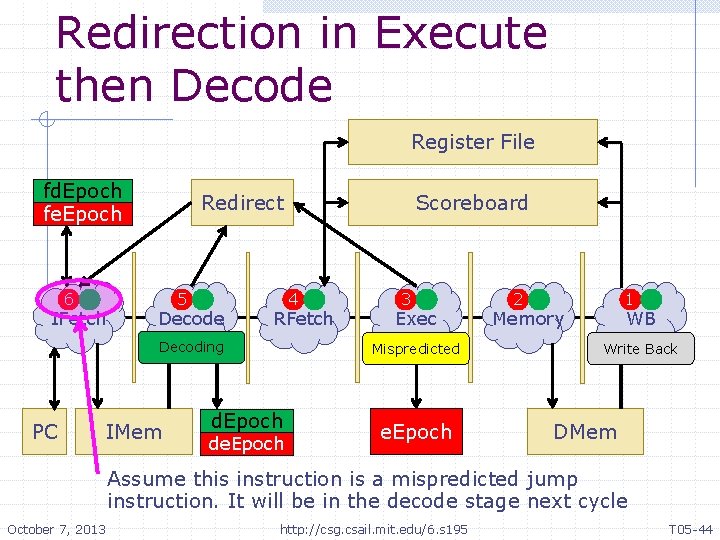

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 1 IFetch Redirect 6 Decode 5 RFetch Mispredicted PC IMem Scoreboard 4 Exec Poisoning d. Epoch de. Epoch 3 2 Memory WB Write Back DMem The decode stage’s estimate of e. Epoch is old, so it isn’t able to recognize it is decoding a wrong path instruction. October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -45

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 1 IFetch Redirect 1 6 Decode 5 RFetch Mispredicted PC IMem Scoreboard 4 Exec Poisoning d. Epoch de. Epoch 3 2 Memory WB Write Back DMem Fetch will remove the redirection from the redirect FIFO without changing the PC because the execute epochs don’t match. October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -46

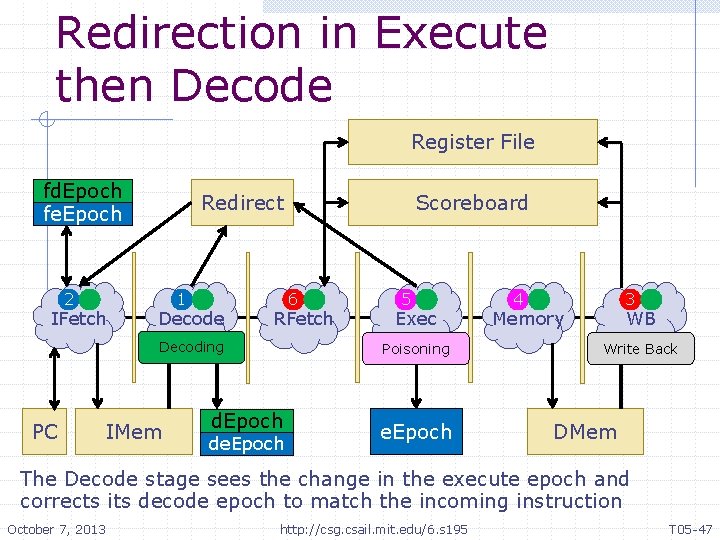

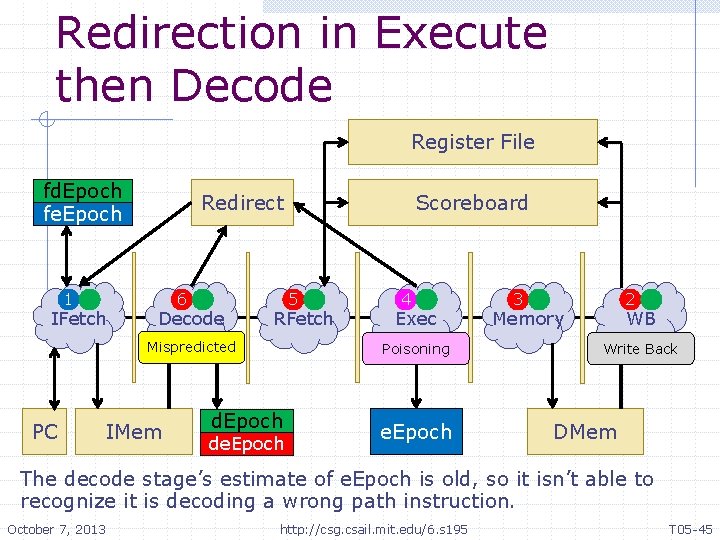

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 2 IFetch Redirect 1 Decode 6 RFetch Decoding PC IMem Scoreboard 5 Exec Poisoning d. Epoch de. Epoch 4 3 Memory WB Write Back DMem The Decode stage sees the change in the execute epoch and corrects its decode epoch to match the incoming instruction October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -47

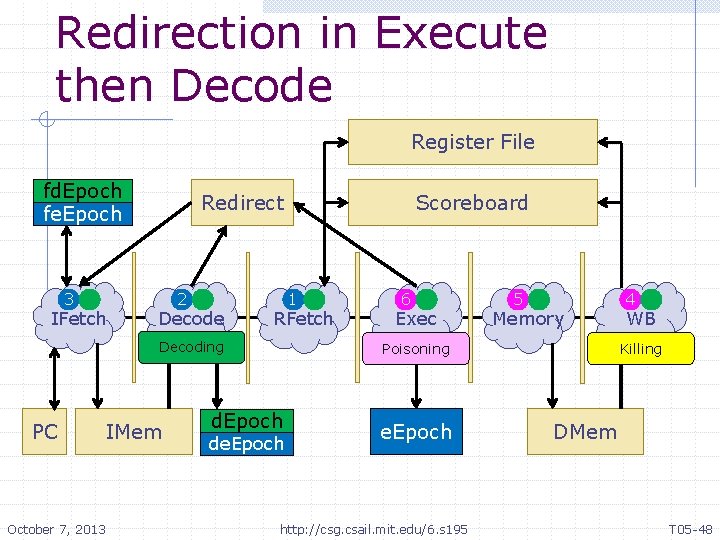

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 3 IFetch Redirect 2 Decode 1 RFetch Decoding PC October 7, 2013 IMem Scoreboard 6 Exec 5 Memory Poisoning d. Epoch de. Epoch http: //csg. csail. mit. edu/6. s 195 4 WB Killing DMem T 05 -48

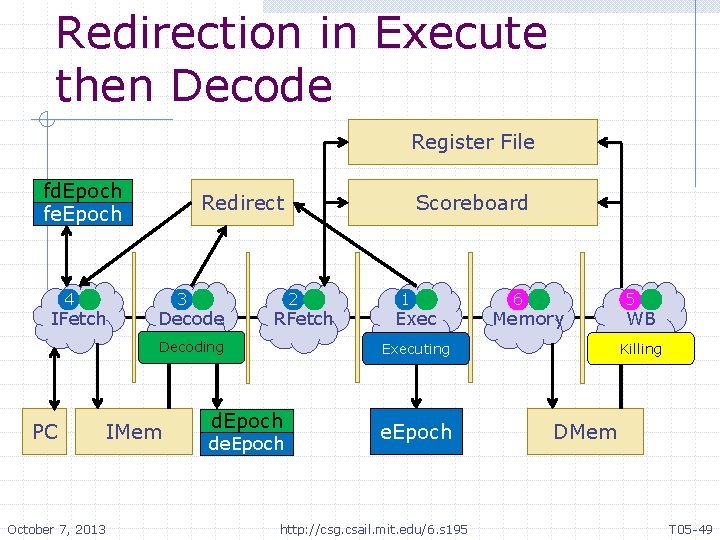

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 4 IFetch Redirect 3 Decode 2 RFetch Decoding PC October 7, 2013 IMem Scoreboard 1 Exec 6 Memory Executing d. Epoch de. Epoch http: //csg. csail. mit. edu/6. s 195 5 WB Killing DMem T 05 -49

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 5 IFetch Redirect 4 Decode 3 RFetch Decoding PC October 7, 2013 IMem Scoreboard 2 Exec 1 Memory Executing d. Epoch de. Epoch http: //csg. csail. mit. edu/6. s 195 6 WB Killing DMem T 05 -50

Redirection in Execute then Decode Register File fd. Epoch fe. Epoch 6 IFetch Redirect 5 Decode 4 RFetch Decoding PC October 7, 2013 IMem Scoreboard 3 Executing d. Epoch de. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -51

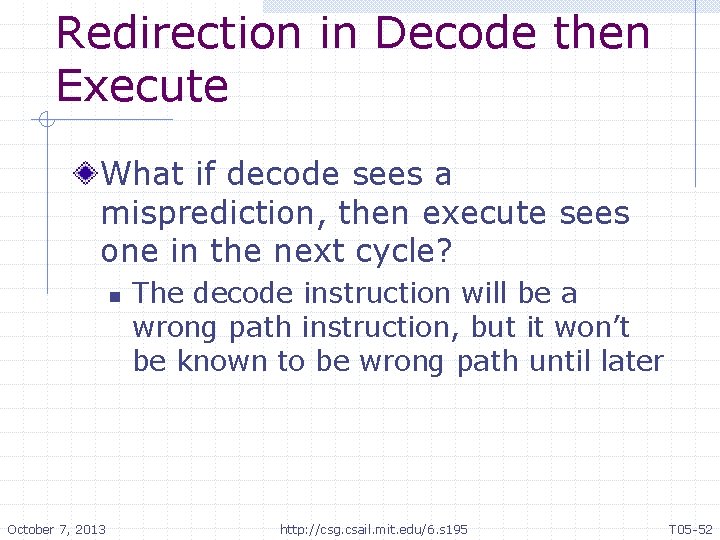

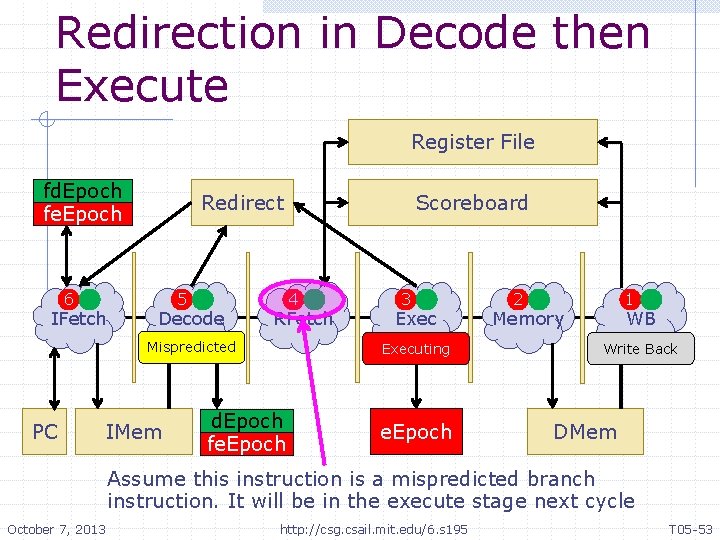

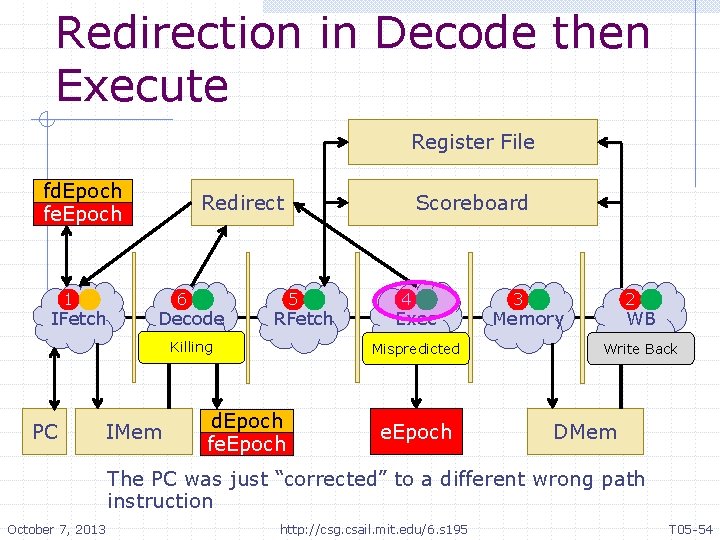

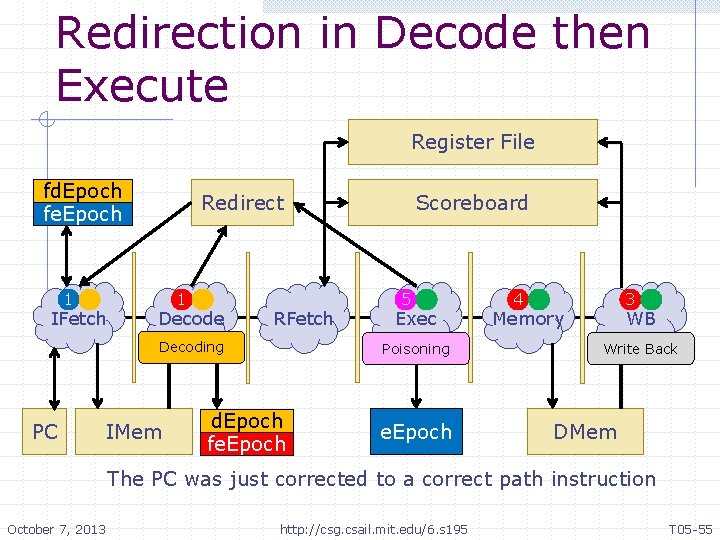

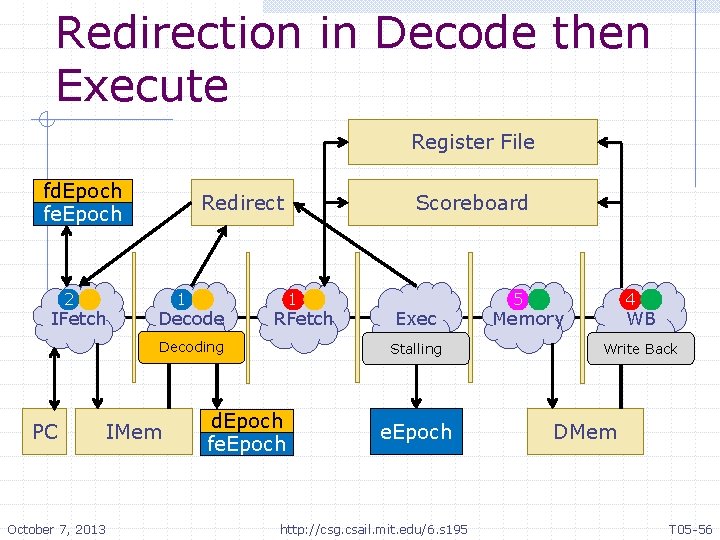

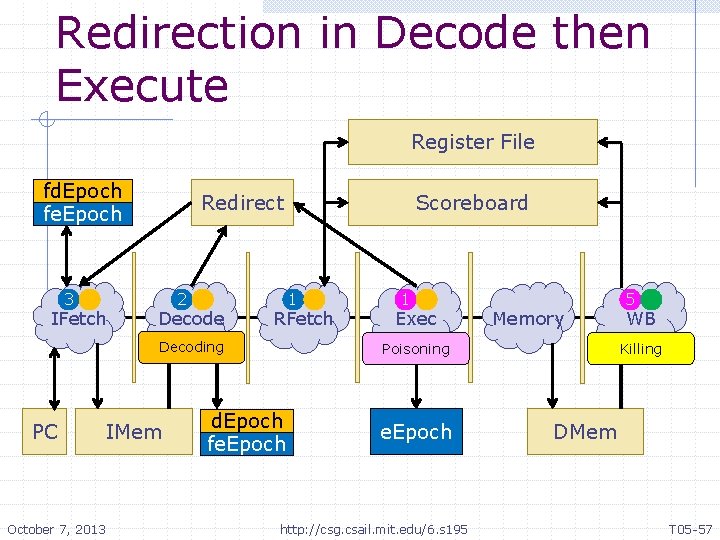

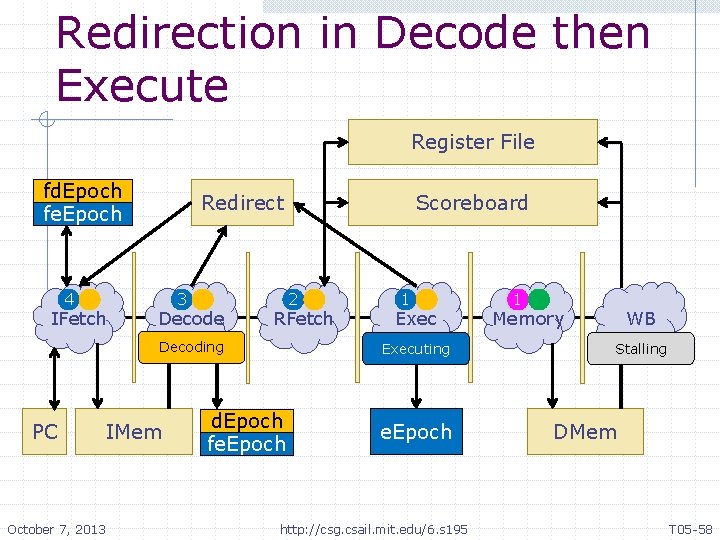

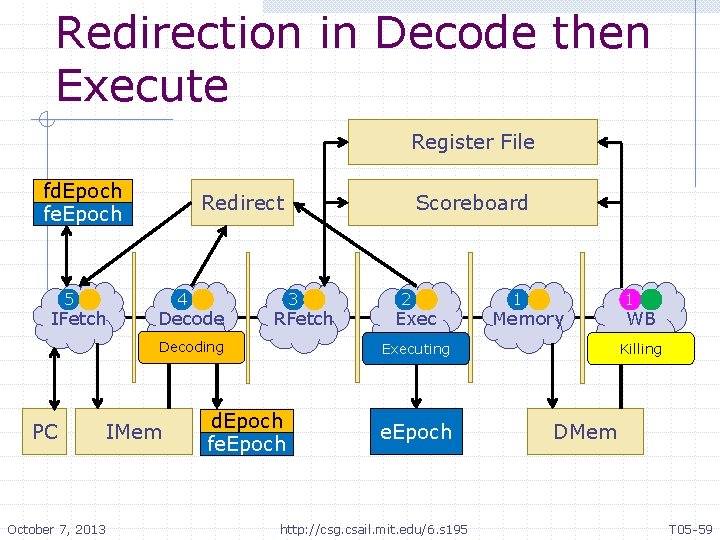

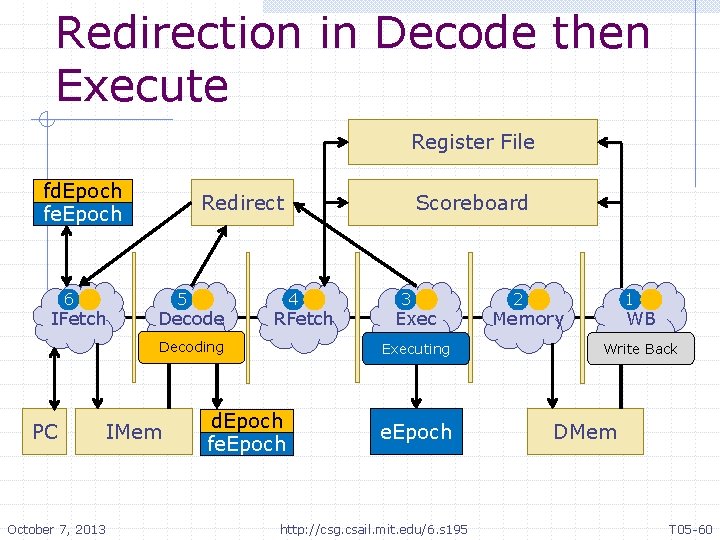

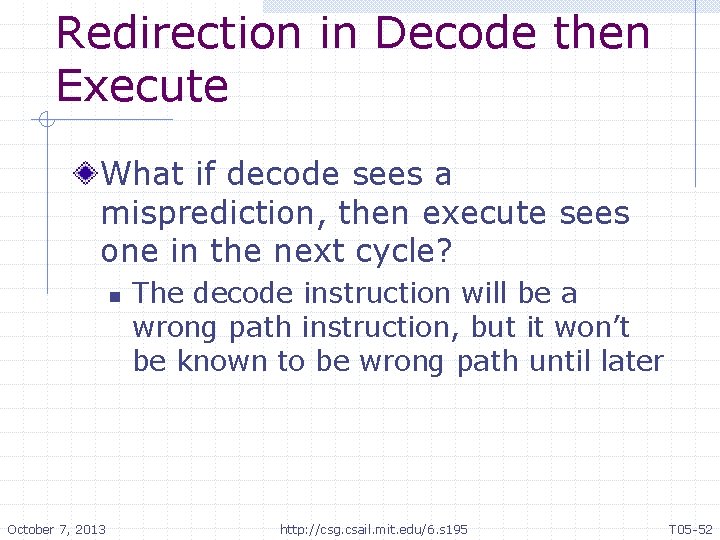

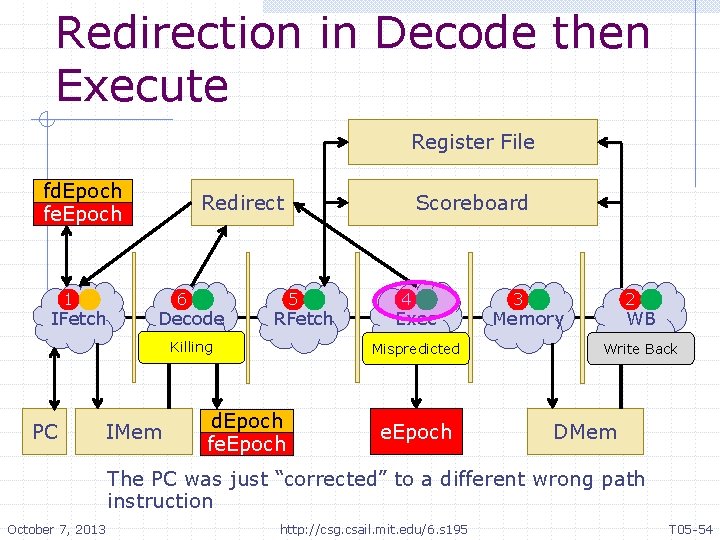

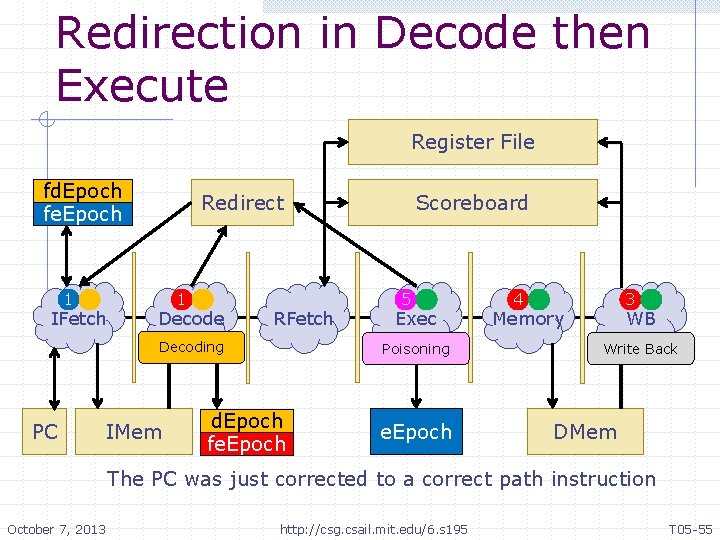

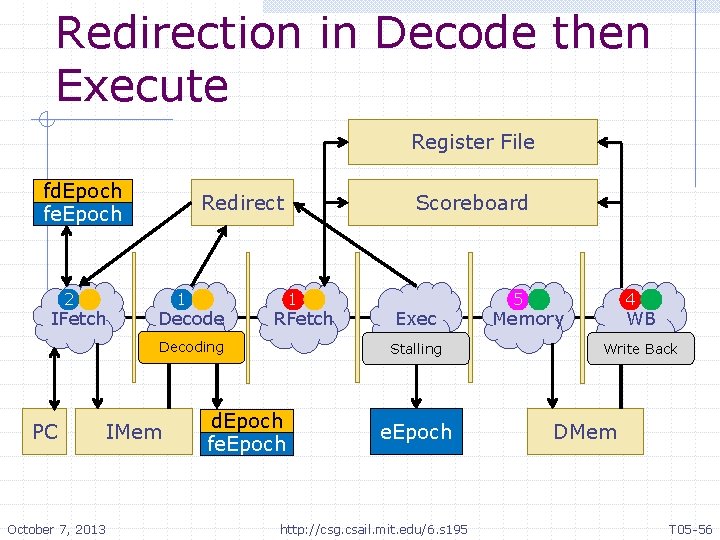

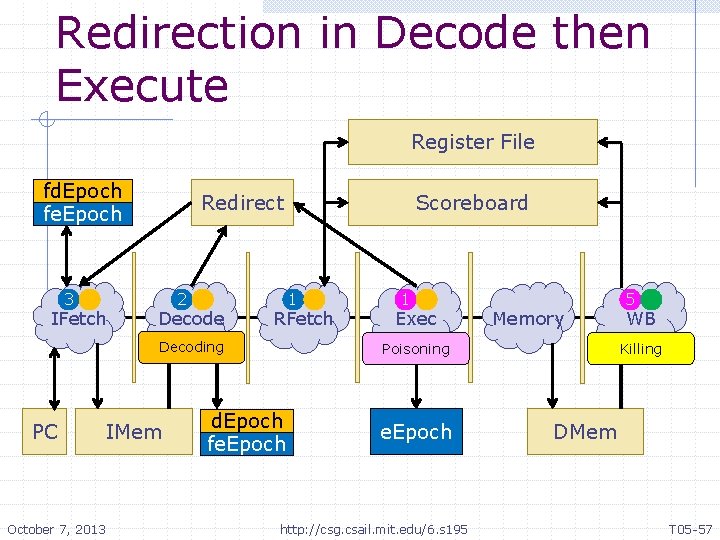

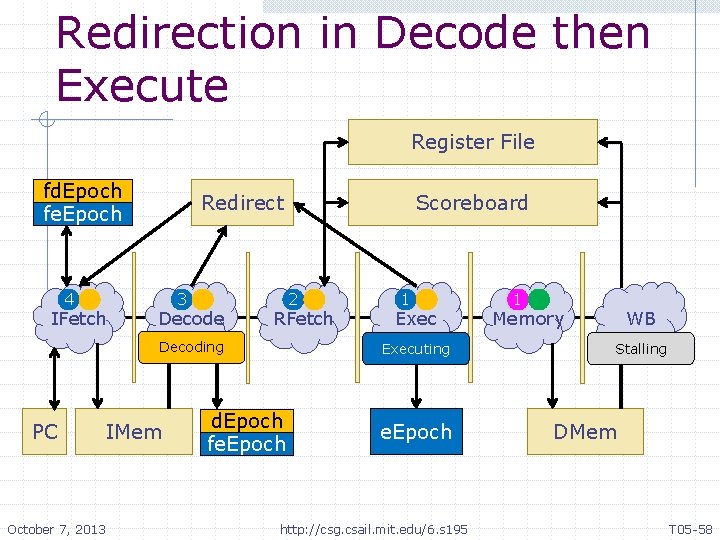

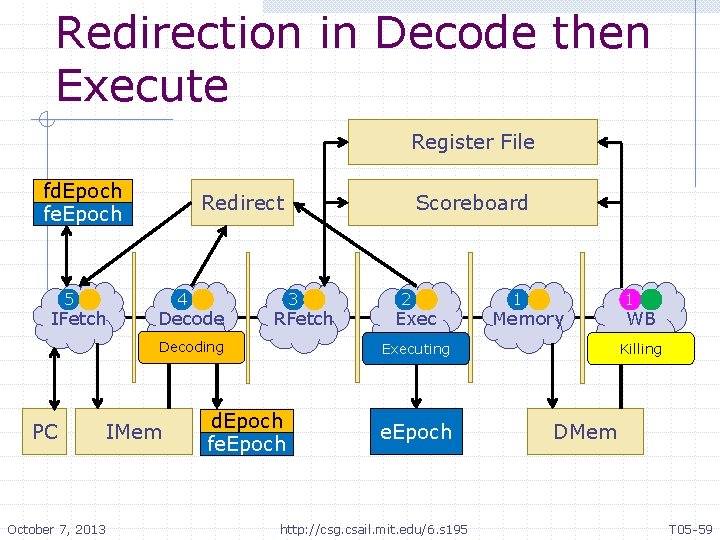

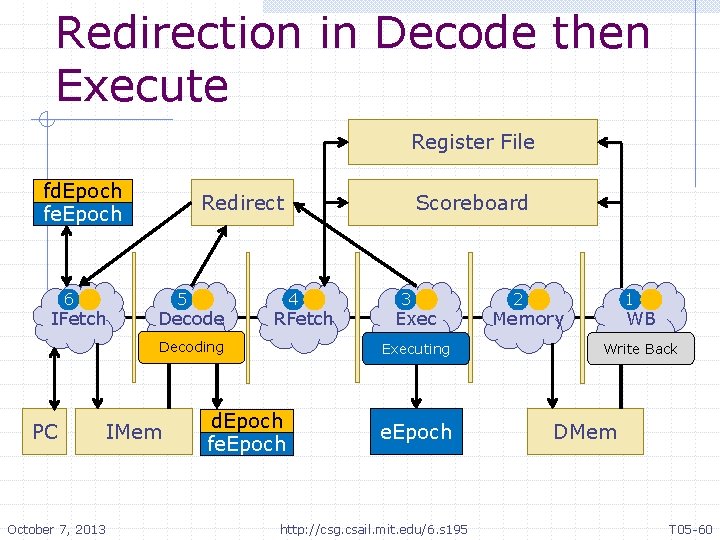

Redirection in Decode then Execute What if decode sees a misprediction, then execute sees one in the next cycle? n October 7, 2013 The decode instruction will be a wrong path instruction, but it won’t be known to be wrong path until later http: //csg. csail. mit. edu/6. s 195 T 05 -52

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 6 IFetch Redirect 5 Decode 4 RFetch Mispredicted PC IMem Scoreboard 3 Executing d. Epoch fe. Epoch 2 1 Memory WB Write Back DMem Assume this instruction is a mispredicted branch instruction. It will be in the execute stage next cycle October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -53

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 1 IFetch Redirect 6 Decode 5 RFetch Killing PC IMem Scoreboard 4 Exec Mispredicted d. Epoch fe. Epoch 3 2 Memory WB Write Back DMem The PC was just “corrected” to a different wrong path instruction October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -54

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 1 IFetch Redirect 1 Decode RFetch Decoding PC IMem Scoreboard 5 Exec Poisoning d. Epoch fe. Epoch 4 3 Memory WB Write Back DMem The PC was just corrected to a correct path instruction October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -55

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 2 IFetch Redirect 1 Decode 1 RFetch Decoding PC October 7, 2013 IMem Scoreboard Exec Stalling d. Epoch fe. Epoch http: //csg. csail. mit. edu/6. s 195 5 4 Memory WB Write Back DMem T 05 -56

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 3 IFetch Redirect 2 Decode 1 RFetch Decoding PC October 7, 2013 IMem Scoreboard 1 Exec Memory Poisoning d. Epoch fe. Epoch http: //csg. csail. mit. edu/6. s 195 5 WB Killing DMem T 05 -57

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 4 IFetch Redirect 3 Decode 2 RFetch Decoding PC October 7, 2013 IMem Scoreboard 1 Executing d. Epoch fe. Epoch http: //csg. csail. mit. edu/6. s 195 1 Memory WB Stalling DMem T 05 -58

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 5 IFetch Redirect 4 Decode 3 RFetch Decoding PC October 7, 2013 IMem Scoreboard 2 Exec 1 Memory Executing d. Epoch fe. Epoch http: //csg. csail. mit. edu/6. s 195 1 WB Killing DMem T 05 -59

Redirection in Decode then Execute Register File fd. Epoch fe. Epoch 6 IFetch Redirect 5 Decode 4 RFetch Decoding PC October 7, 2013 IMem Scoreboard 3 Executing d. Epoch fe. Epoch http: //csg. csail. mit. edu/6. s 195 2 1 Memory WB Write Back DMem T 05 -60

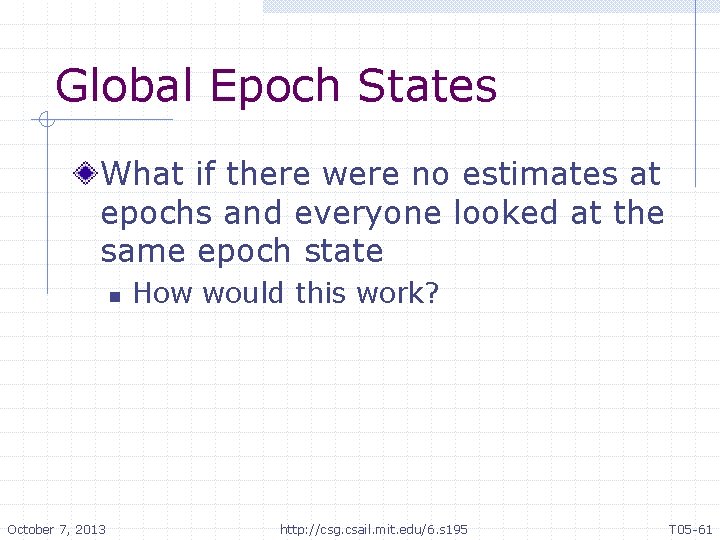

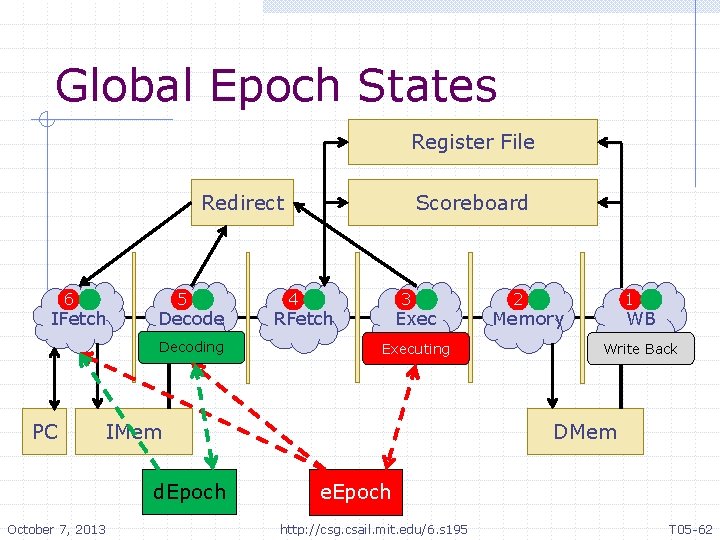

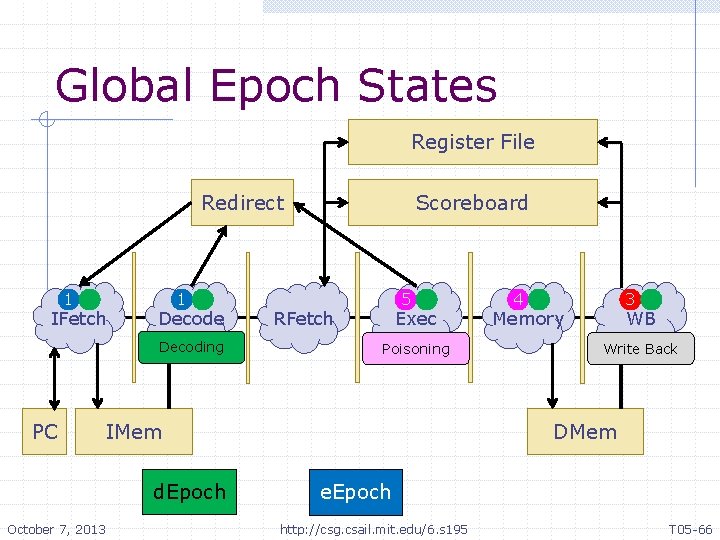

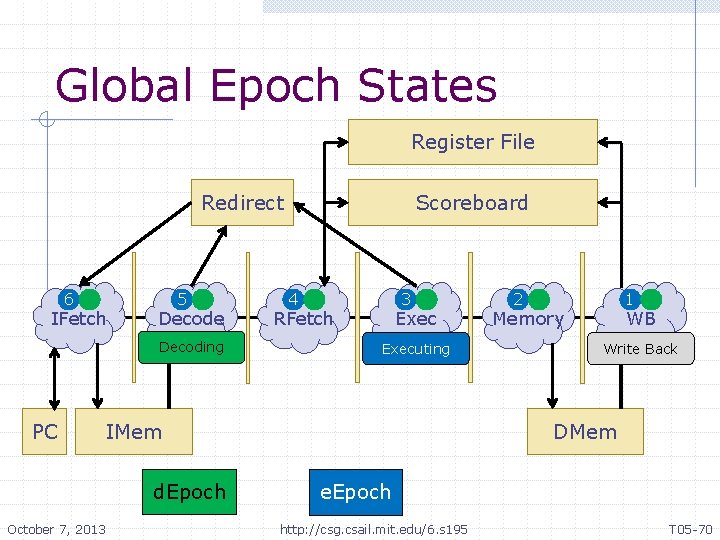

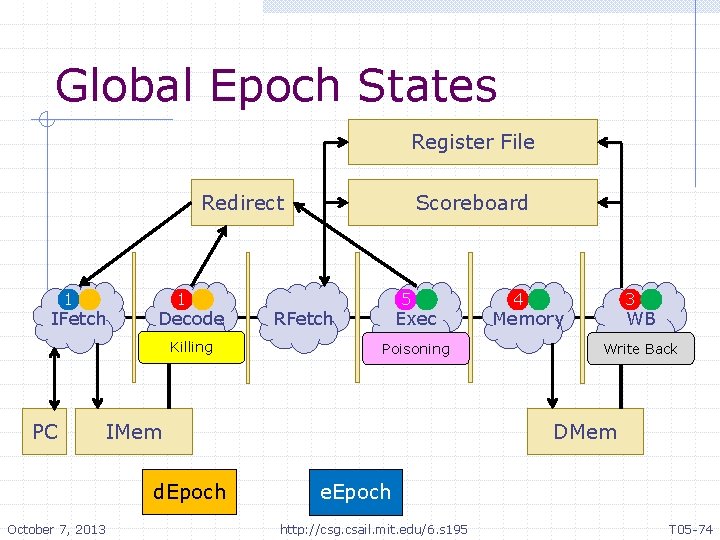

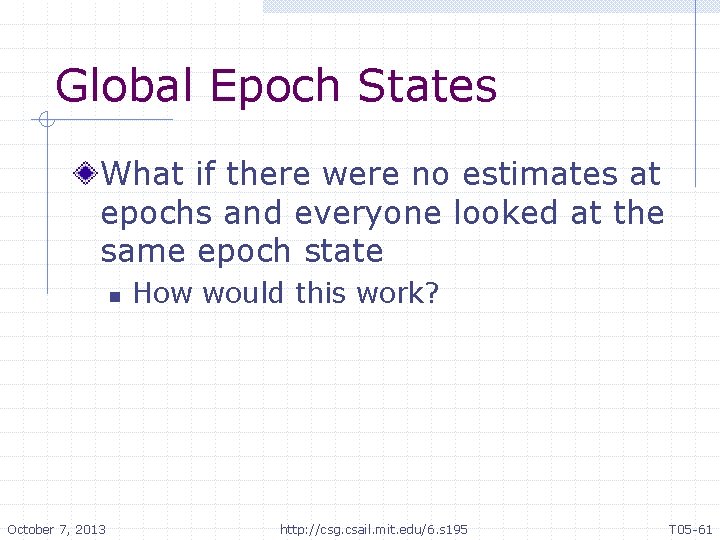

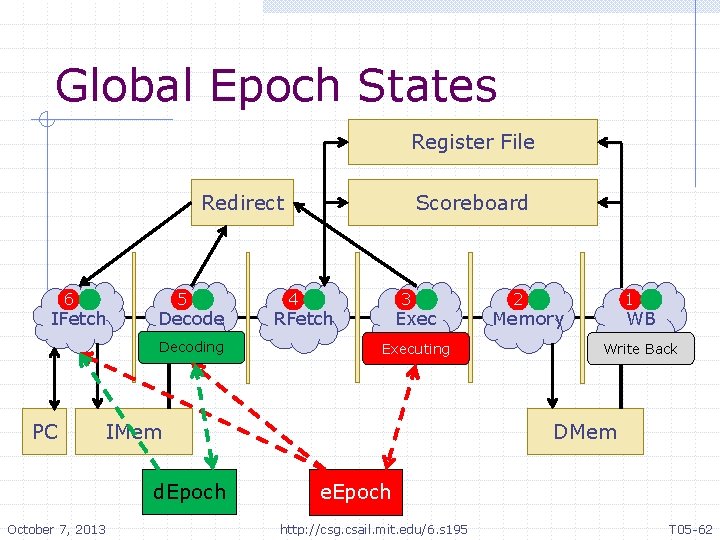

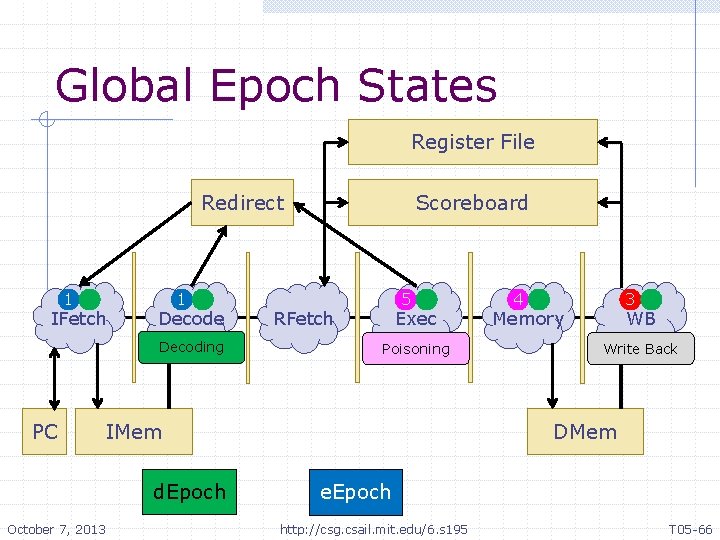

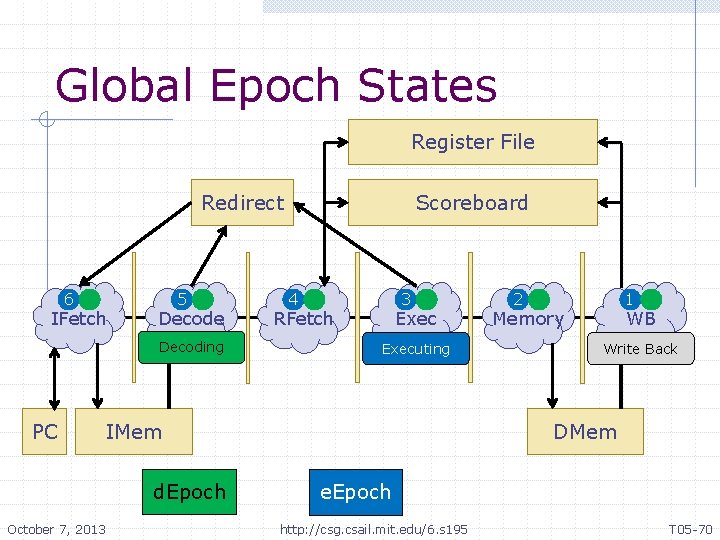

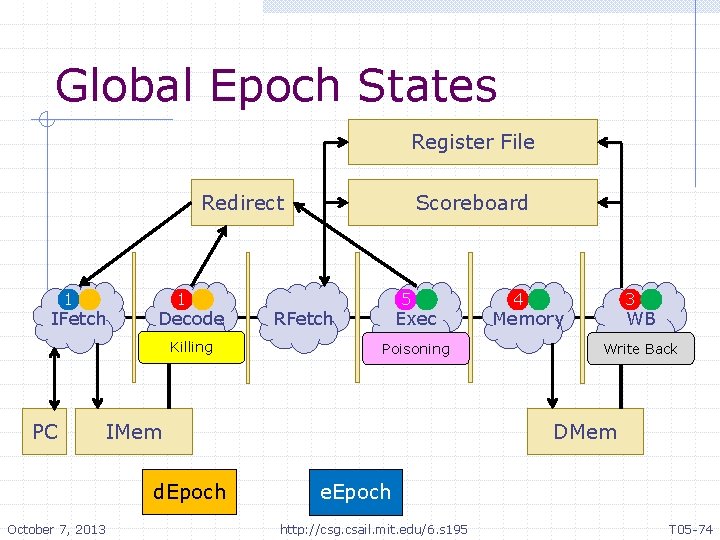

Global Epoch States What if there were no estimates at epochs and everyone looked at the same epoch state n October 7, 2013 How would this work? http: //csg. csail. mit. edu/6. s 195 T 05 -61

Global Epoch States Register File Redirect 6 IFetch 5 Decode Decoding PC 4 3 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 2 1 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -62

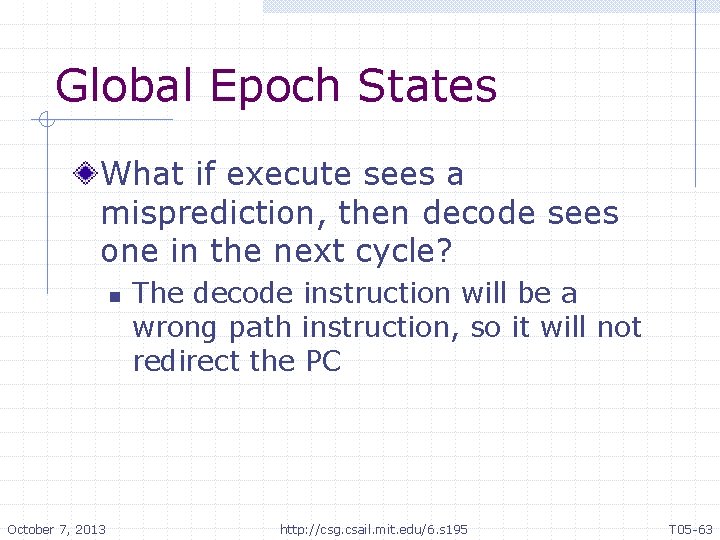

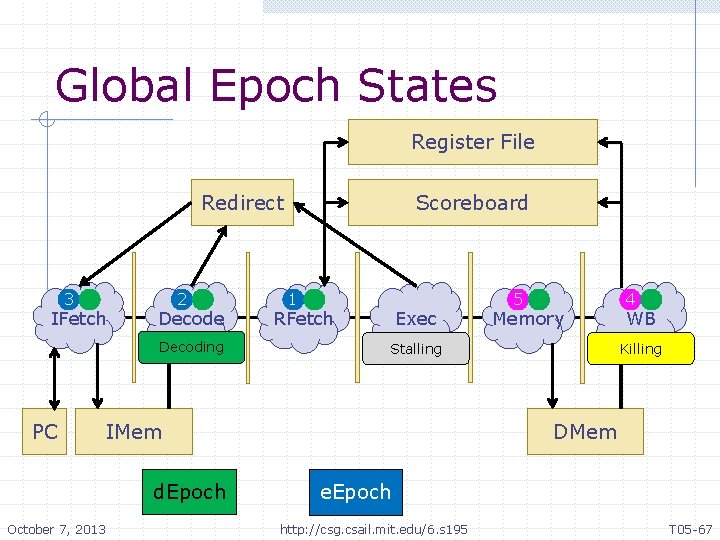

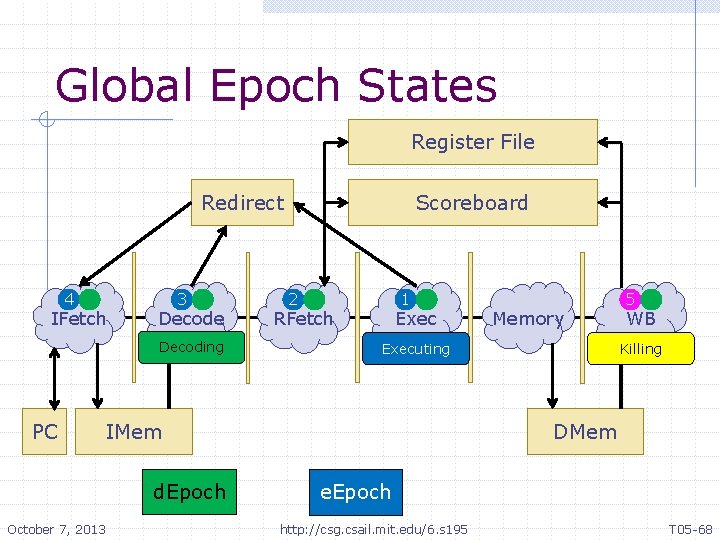

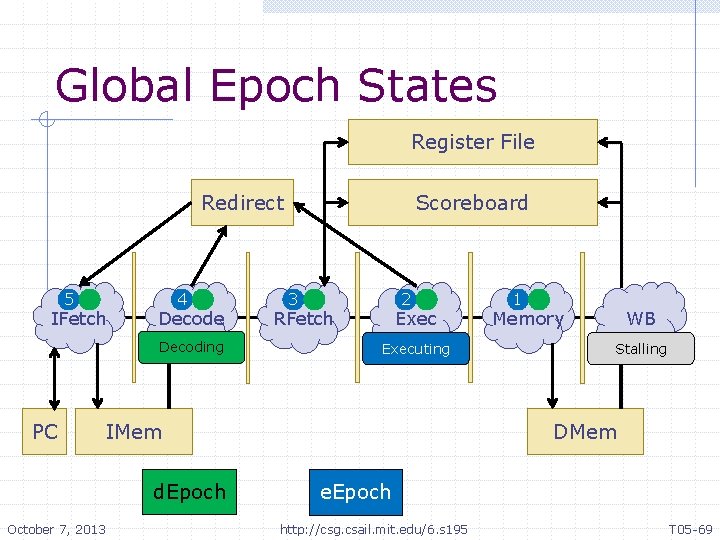

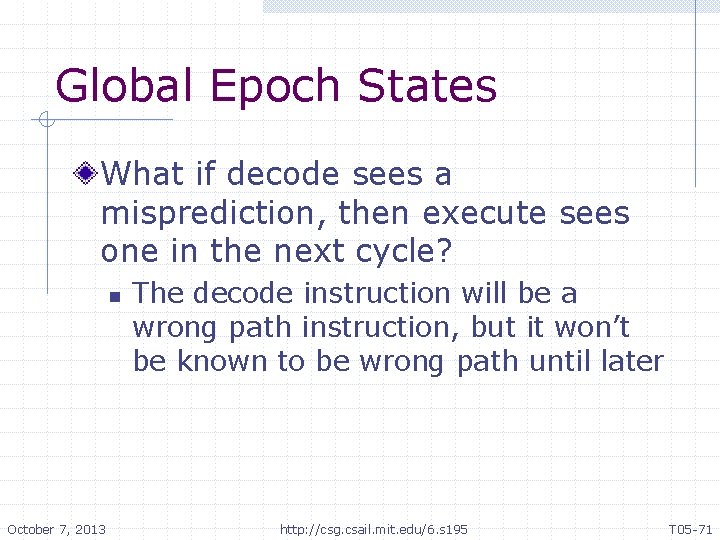

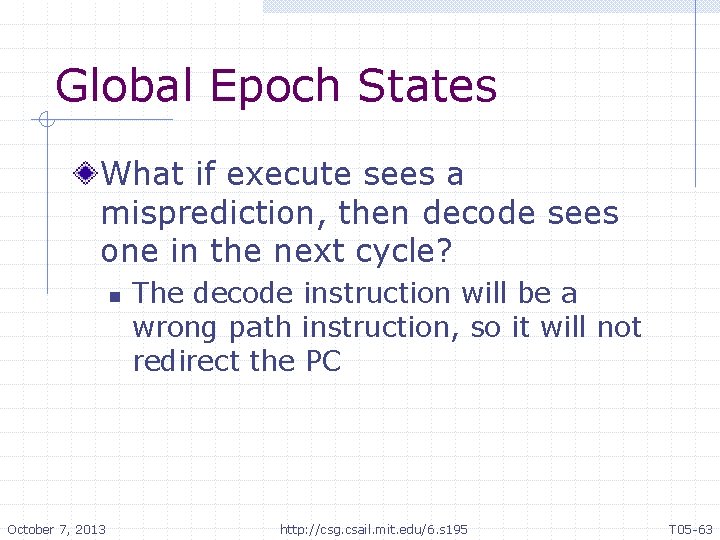

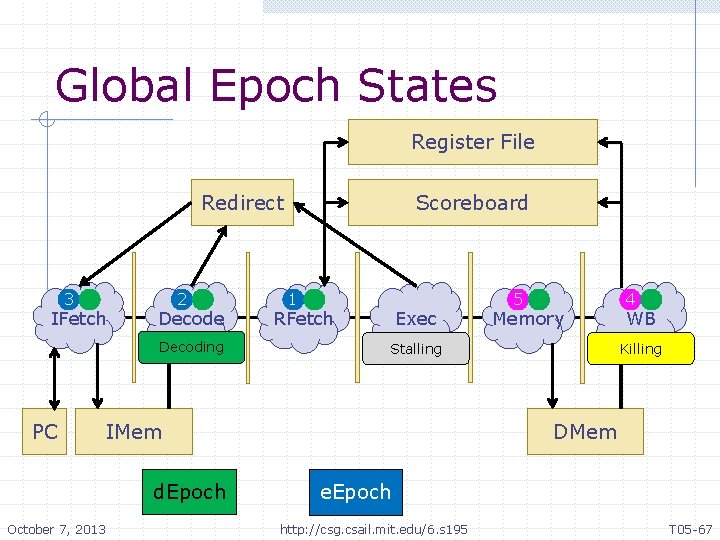

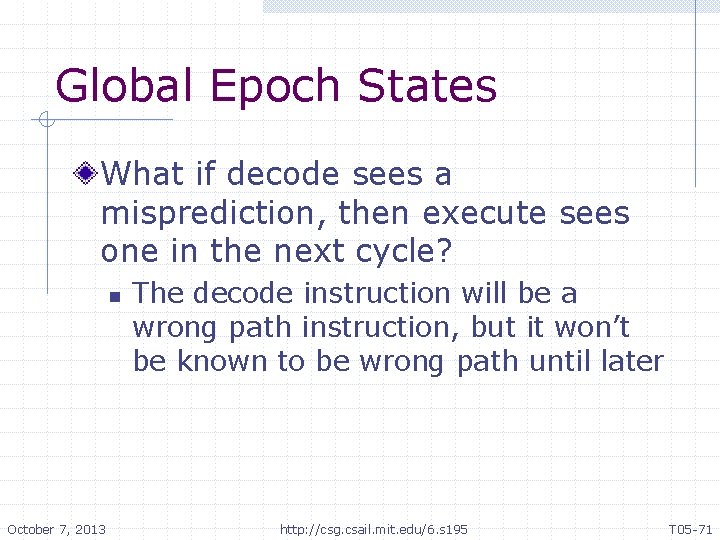

Global Epoch States What if execute sees a misprediction, then decode sees one in the next cycle? n October 7, 2013 The decode instruction will be a wrong path instruction, so it will not redirect the PC http: //csg. csail. mit. edu/6. s 195 T 05 -63

Global Epoch States Assume this instruction is a mispredicted jump instruction. Register File Redirect 6 IFetch 5 Decode Decoding PC 4 3 RFetch Exec Mispredicted IMem d. Epoch October 7, 2013 Scoreboard 2 1 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -64

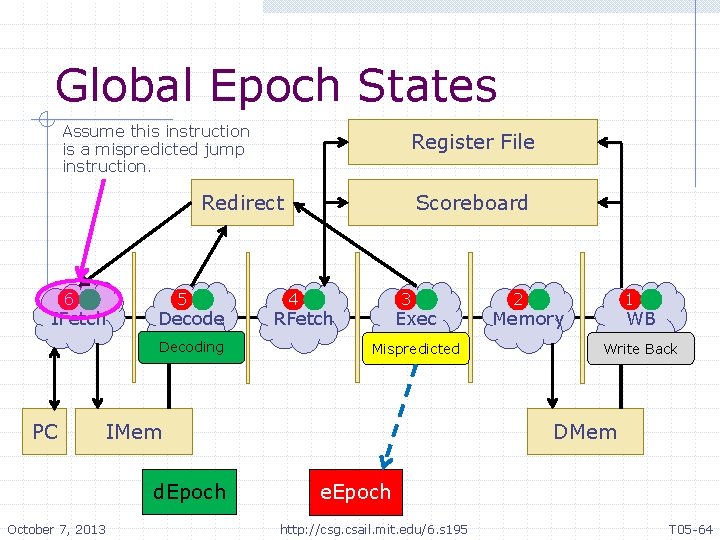

Global Epoch States Register File Redirect 1 IFetch 6 Decode Killing PC 5 4 RFetch Exec Poisoning IMem d. Epoch October 7, 2013 Scoreboard 3 2 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -65

Global Epoch States Register File Redirect 1 IFetch 1 Decode Decoding PC 5 RFetch Exec Poisoning IMem d. Epoch October 7, 2013 Scoreboard 4 3 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -66

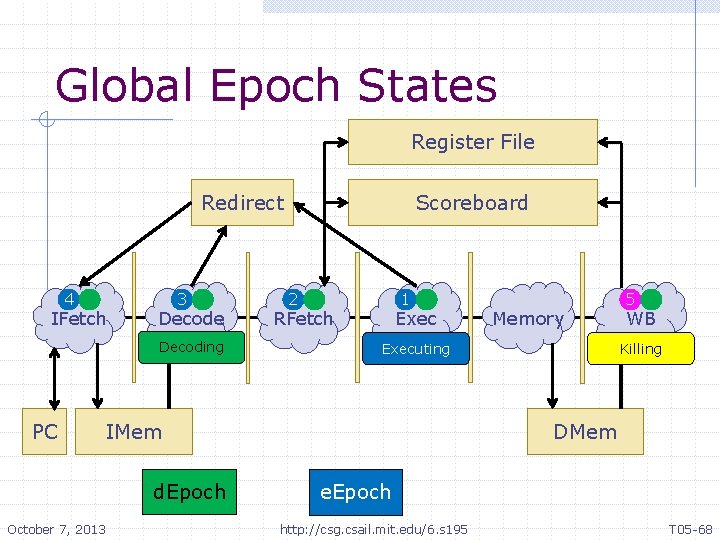

Global Epoch States Register File Redirect 3 IFetch 2 Decode Decoding PC 1 RFetch Exec 5 Memory Stalling IMem d. Epoch October 7, 2013 Scoreboard 4 WB Killing DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -67

Global Epoch States Register File Redirect 4 IFetch 3 Decode Decoding PC 2 1 RFetch Exec Memory Executing IMem d. Epoch October 7, 2013 Scoreboard 5 WB Killing DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -68

Global Epoch States Register File Redirect 5 IFetch 4 Decode Decoding PC 3 2 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 1 Memory WB Stalling DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -69

Global Epoch States Register File Redirect 6 IFetch 5 Decode Decoding PC 4 3 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 2 1 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -70

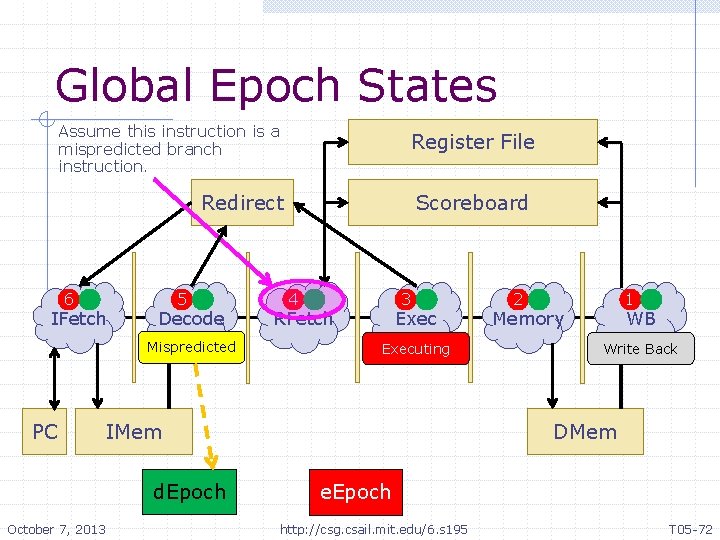

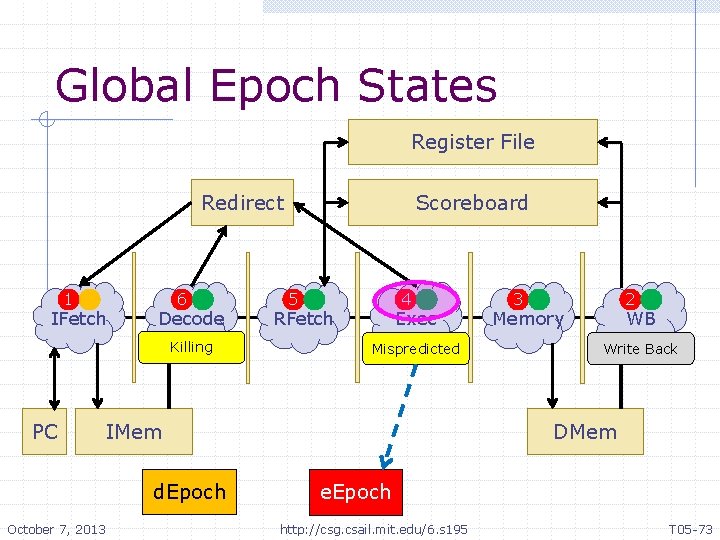

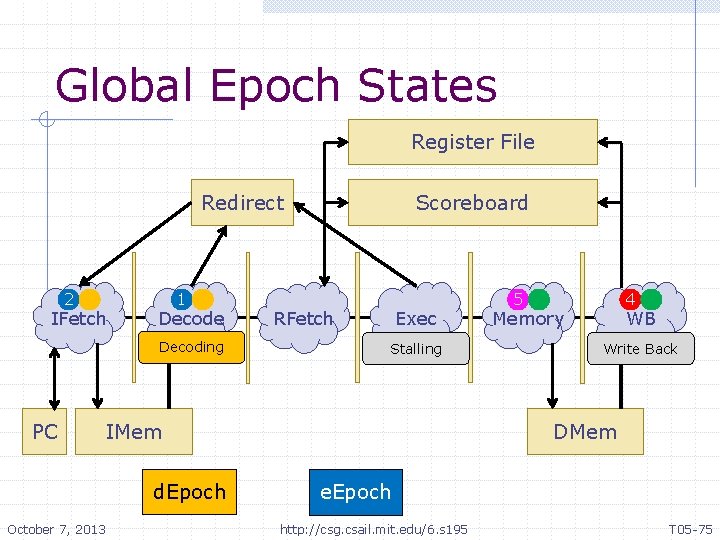

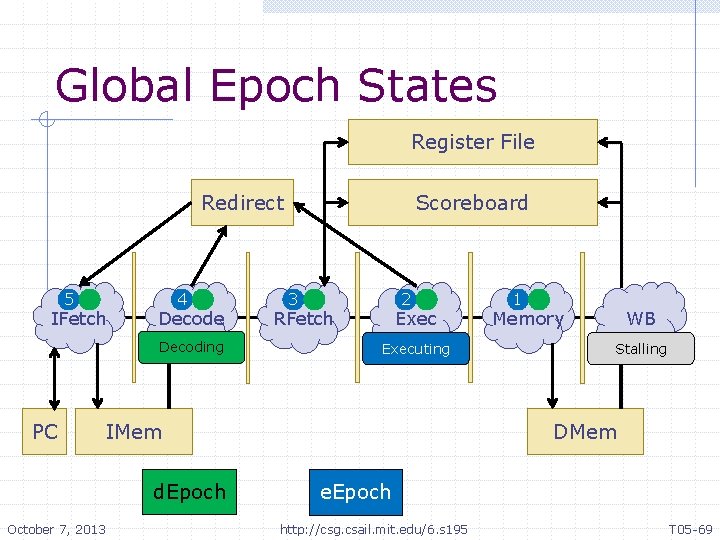

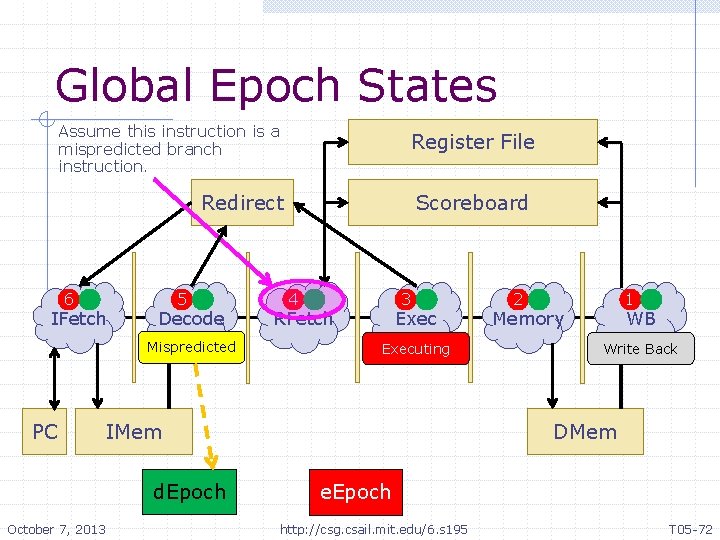

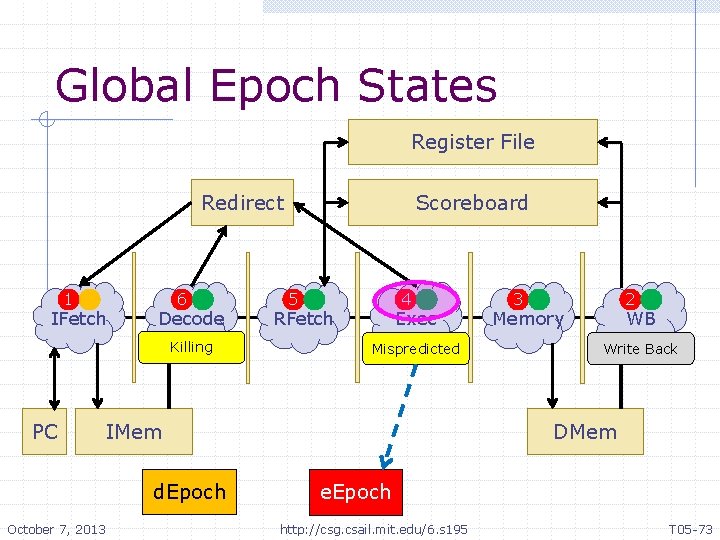

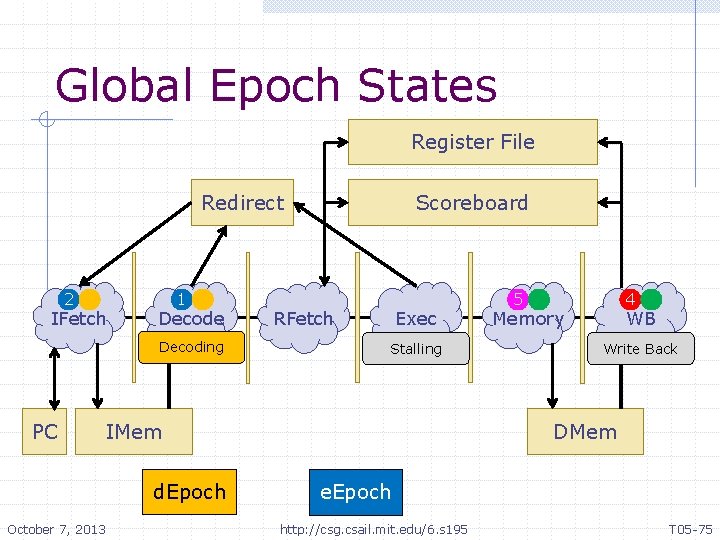

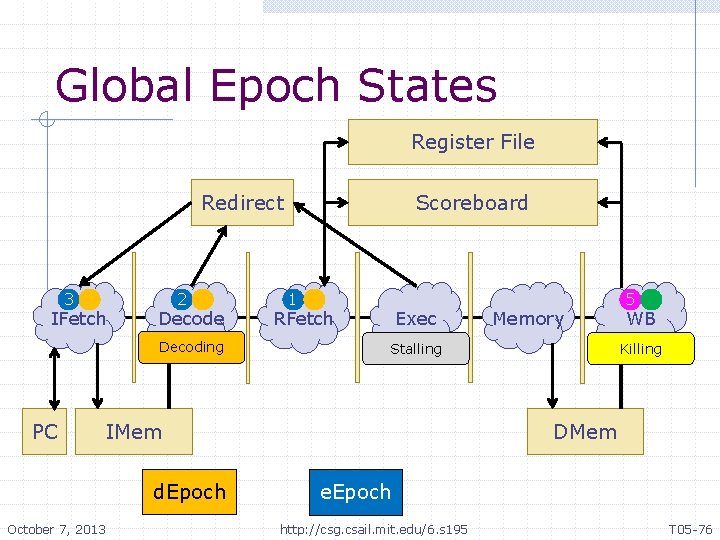

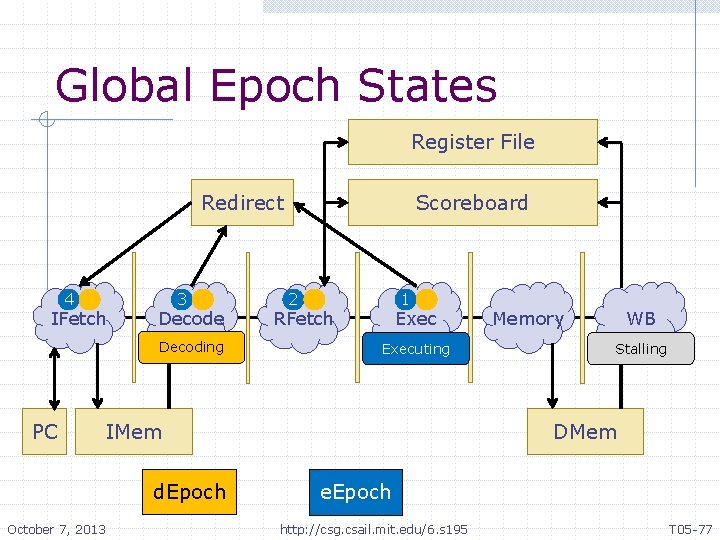

Global Epoch States What if decode sees a misprediction, then execute sees one in the next cycle? n October 7, 2013 The decode instruction will be a wrong path instruction, but it won’t be known to be wrong path until later http: //csg. csail. mit. edu/6. s 195 T 05 -71

Global Epoch States Assume this instruction is a mispredicted branch instruction. Register File Redirect 6 IFetch 5 Decode Mispredicted PC 4 3 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 2 1 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -72

Global Epoch States Register File Redirect 1 IFetch 6 Decode Killing PC 5 4 RFetch Exec Mispredicted IMem d. Epoch October 7, 2013 Scoreboard 3 2 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -73

Global Epoch States Register File Redirect 1 IFetch 1 Decode Killing PC 5 RFetch Exec Poisoning IMem d. Epoch October 7, 2013 Scoreboard 4 3 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -74

Global Epoch States Register File Redirect 2 IFetch 1 Decode Decoding PC RFetch Exec Stalling IMem d. Epoch October 7, 2013 Scoreboard 5 4 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -75

Global Epoch States Register File Redirect 3 IFetch 2 Decode Decoding PC 1 RFetch Exec Memory Stalling IMem d. Epoch October 7, 2013 Scoreboard 5 WB Killing DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -76

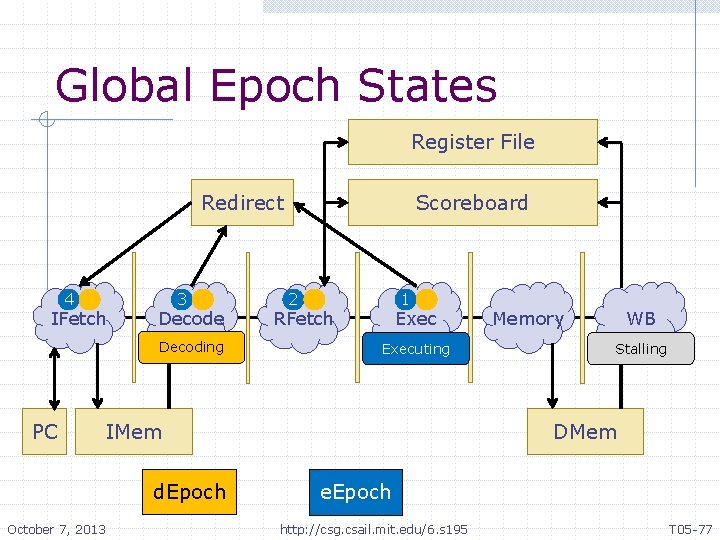

Global Epoch States Register File Redirect 4 IFetch 3 Decode Decoding PC 2 1 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard Memory WB Stalling DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -77

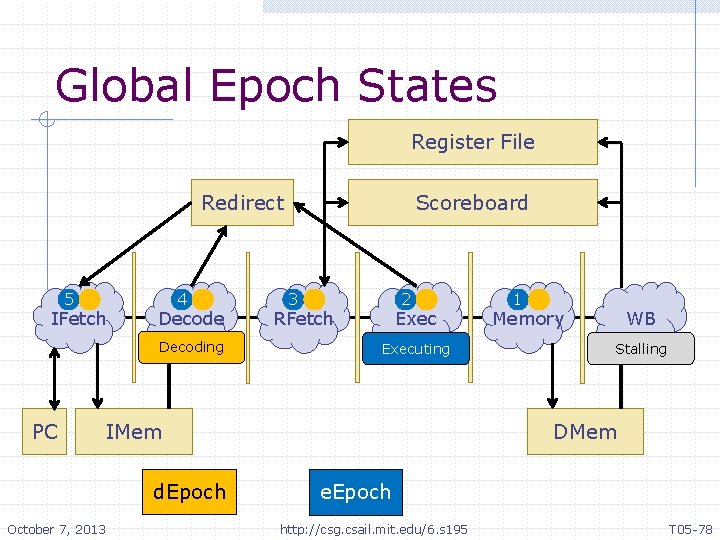

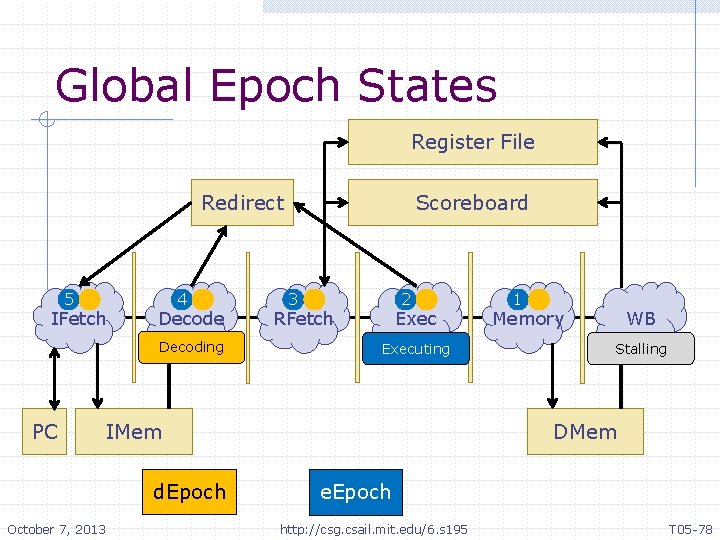

Global Epoch States Register File Redirect 5 IFetch 4 Decode Decoding PC 3 2 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 1 Memory WB Stalling DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -78

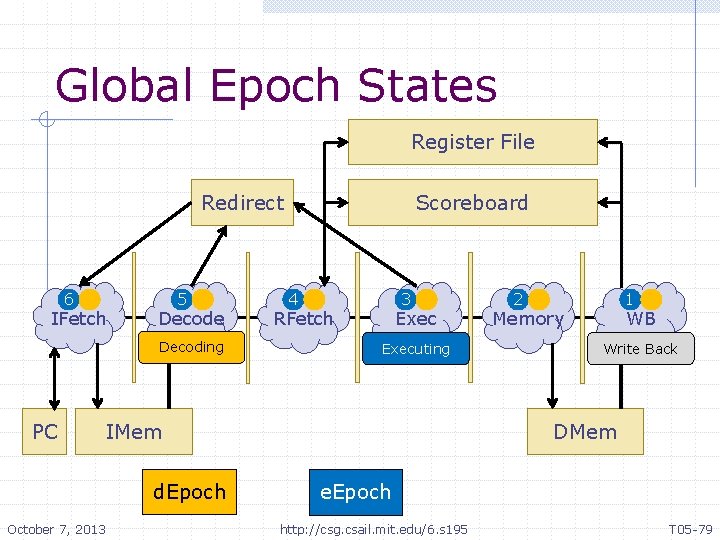

Global Epoch States Register File Redirect 6 IFetch 5 Decode Decoding PC 4 3 RFetch Executing IMem d. Epoch October 7, 2013 Scoreboard 2 1 Memory WB Write Back DMem e. Epoch http: //csg. csail. mit. edu/6. s 195 T 05 -79

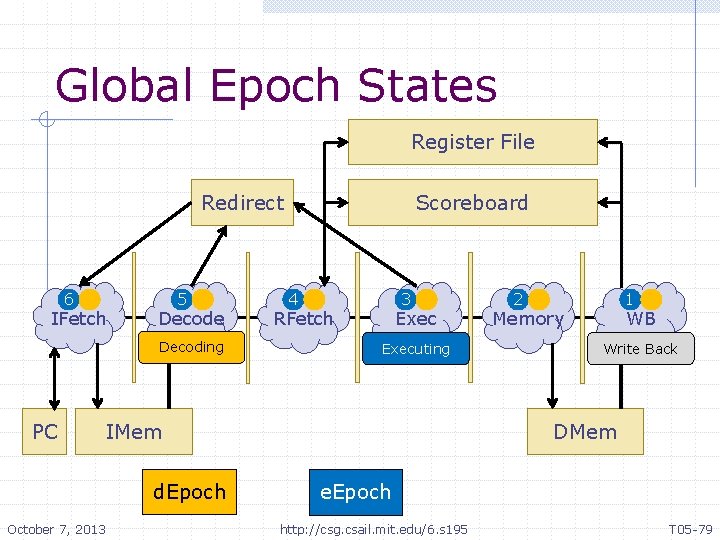

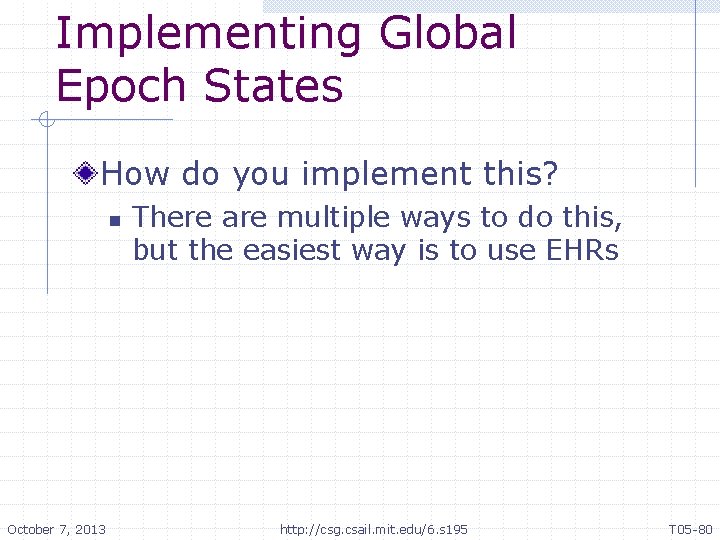

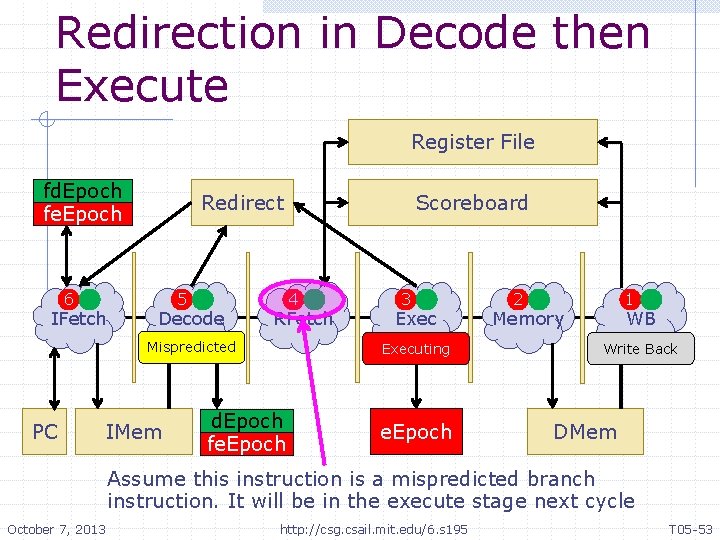

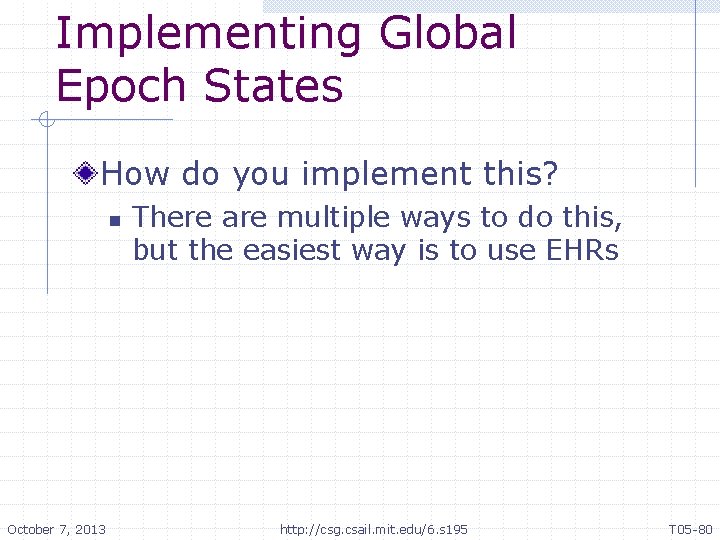

Implementing Global Epoch States How do you implement this? n October 7, 2013 There are multiple ways to do this, but the easiest way is to use EHRs http: //csg. csail. mit. edu/6. s 195 T 05 -80

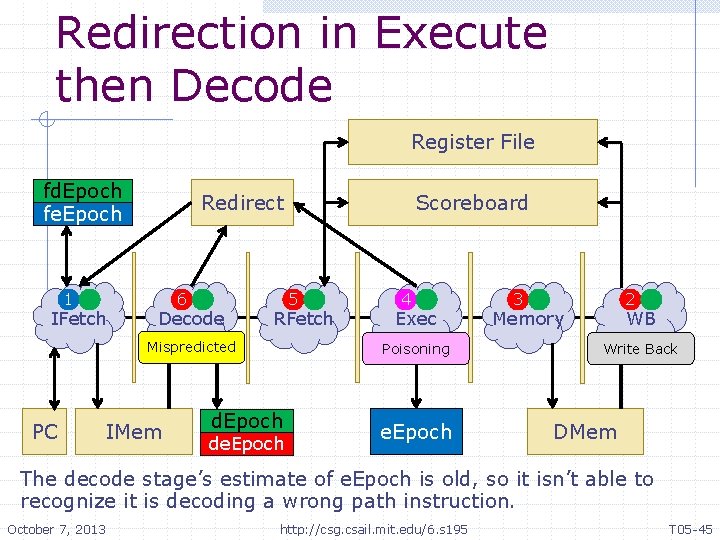

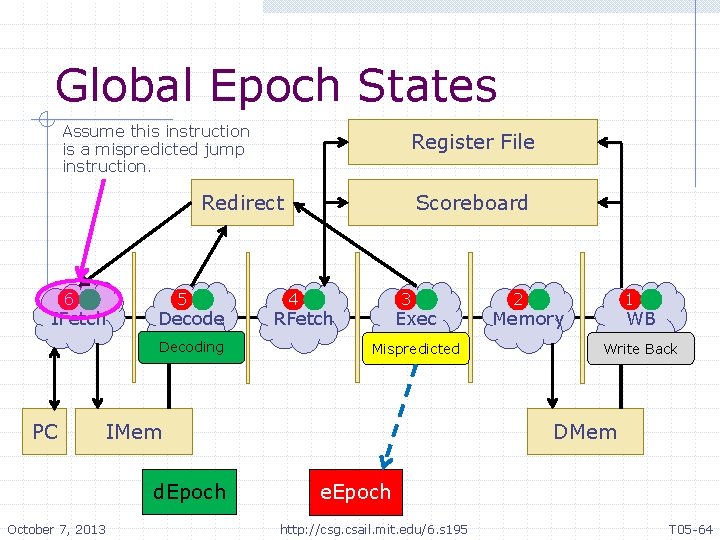

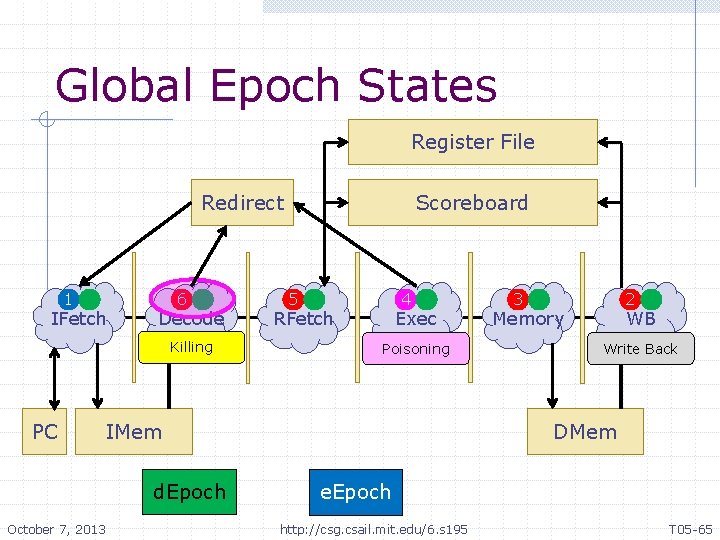

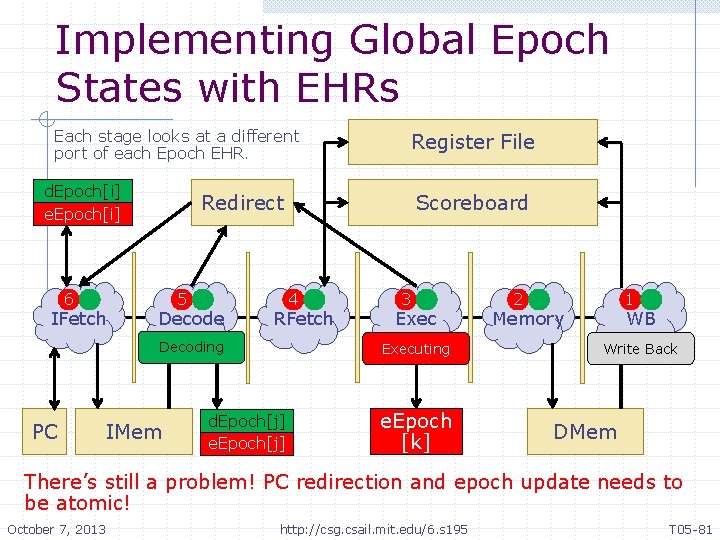

Implementing Global Epoch States with EHRs Each stage looks at a different port of each Epoch EHR. d. Epoch[i] e. Epoch[i] 6 IFetch Redirect 5 Decode IMem Scoreboard 4 RFetch Decoding PC Register File 3 Executing d. Epoch[j] e. Epoch [k] 2 1 Memory WB Write Back DMem There’s still a problem! PC redirection and epoch update needs to be atomic! October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -81

![Implementing Global Epoch States with EHRs Register File d Epochi e Epochi 6 IFetch Implementing Global Epoch States with EHRs Register File d. Epoch[i] e. Epoch[i] 6 IFetch](https://slidetodoc.com/presentation_image_h/0378a2bcf6329996c4f169636e5734a6/image-82.jpg)

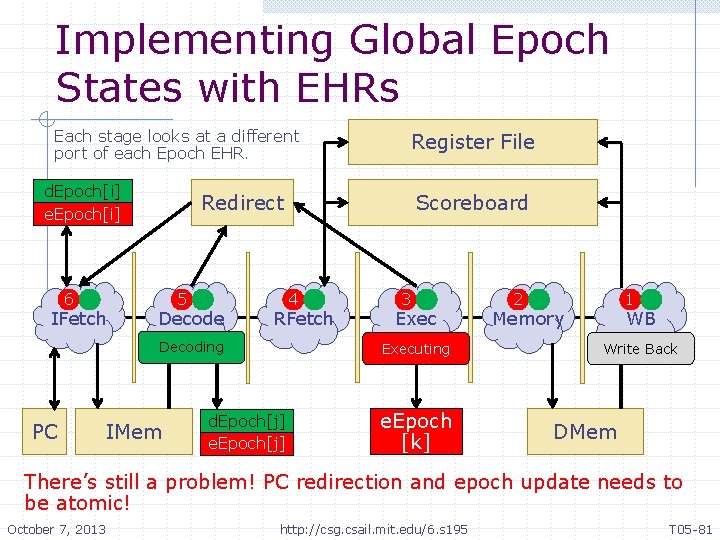

Implementing Global Epoch States with EHRs Register File d. Epoch[i] e. Epoch[i] 6 IFetch Scoreboard 5 Decode 4 RFetch Decoding PC [i] IMem PC [j] 3 Exec PC [k] 1 Memory Executing d. Epoch[j] e. Epoch[j] 2 e. Epoch [k] WB Write Back DMem Make PC an EHR and have each pipeline stage redirect the PC directly October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -82

New Logic for Global Epoch EHRs Fetch n Sends PC to instruction memory, pass current epoch states along with PC in fetch to decode FIFO Decode n n n Kill in place if instruction epochs don’t match global epochs If current instruction is valid, but PPC is incorrect, update decode epoch and PC EHR Drop decode epoch from instruction structure sent to next stage Execute n n n October 7, 2013 Poison if instruction execute epoch doesn’t match global execute epoch If current instruction is valid, but PPC is incorrect, update execute epoch and PC EHR Drop execute epoch from instruction structure passed to next stage http: //csg. csail. mit. edu/6. s 195 T 05 -83

Why is Fecth so Simple? Fetch stage used to have to prioritize between the two redirect FIFOs and drop decode redirection if the execute epochs don’t match n Why isn’t this needed anymore? w Try reasoning about this on your own October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -84

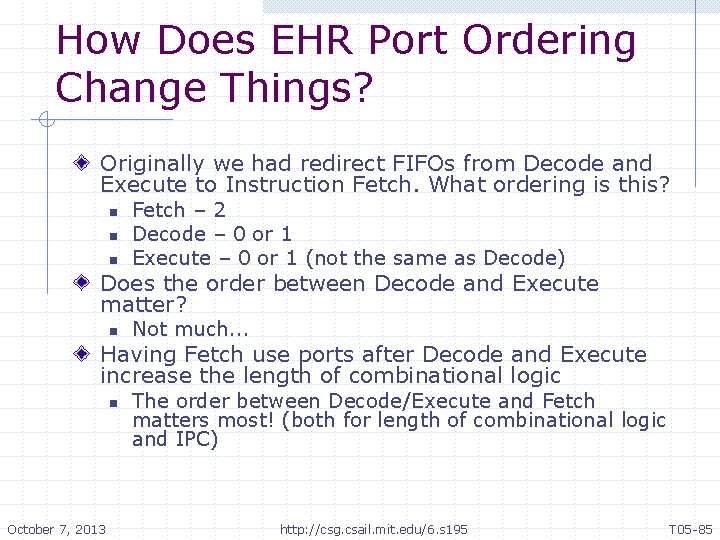

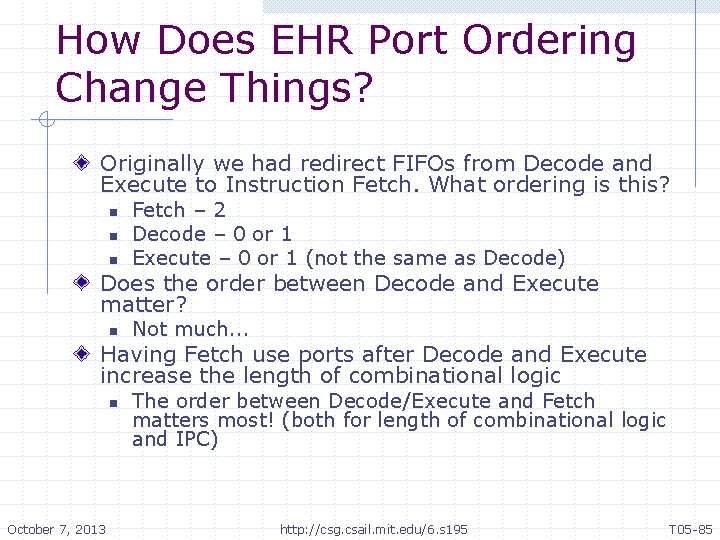

How Does EHR Port Ordering Change Things? Originally we had redirect FIFOs from Decode and Execute to Instruction Fetch. What ordering is this? n n n Fetch – 2 Decode – 0 or 1 Execute – 0 or 1 (not the same as Decode) Does the order between Decode and Execute matter? n Not much. . . Having Fetch use ports after Decode and Execute increase the length of combinational logic n October 7, 2013 The order between Decode/Execute and Fetch matters most! (both for length of combinational logic and IPC) http: //csg. csail. mit. edu/6. s 195 T 05 -85

Questions? October 7, 2013 http: //csg. csail. mit. edu/6. s 195 T 05 -86