COMPACT RECONFIGURABLE AVIONICS RDHC MIDDLEWARE A SOFTWARE EXECUTION

COMPACT RECONFIGURABLE AVIONICS –RDHC MIDDLEWARE: A SOFTWARE EXECUTION PLATFORM FOR CORA-RHDC ON-BOARD COMPUTER AUTHOR: MAXIME GUIMARD PRESENTER: PATRICIA LOPEZ CUEVA GR 740 USER DAY 2019 Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

TABLE OF CONTENTS 1 Overview of Co. RA-RDHC study 4 GR 740 HW Experience 2 Overview of Co. RA-RDHC OBC 5 GR 740 Coding Experience 3 Overview of Co. RA-RDHC SW 6 GR 740 Debug Experience Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

CORA-RDHC STUDY OVERVIEW Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

CORA-RDHC STUDY - OBJECTIVE Design and manufacture an OBC SYSTEM hosting: • A high performance microprocessor and high capacity reconfigurable FPGAs • The associated Elegant Bread Board (EBB) • Standardised interfaces (Mil 1553 B, CAN, Space. Wire) to be used directly with digital devices or as a proxy toward analog interface devices This module acts as the HW execution platform for the “Compact Reconfigurable Avionics” Identify, procure and delivery a suitable SW execution platform for the development: • Boot Software for the CRDHC • Middleware Software execution platform encompassing: Board Support Package and device drivers (HDSW), PUS library and FPGA reconfiguration Software Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

RDHC TEAM- ORGANISATION ESA § Technical Officer: Jørgen Ilstad, TEC-EDD –> EOP-PPE Cobham Gaisler AB, Sweden (prime) § Responsible for the development of hardware, VHDL design, boot software and drivers Thales Alenia Space France § Responsible for middleware software design and SW integration Thales Alenia Space España S. A. , Spain § Responsible for FPGA reconfiguration code Airbus Defence & Space, France § Contribution to the systems analysis and trade-off, requirements and system architecture Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

CORA-RDHC ON BOARD COMPUTER OVERVIEW Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

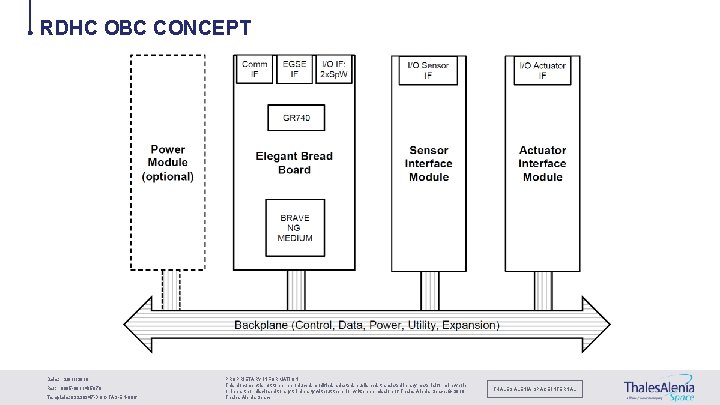

RDHC OBC CONCEPT Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

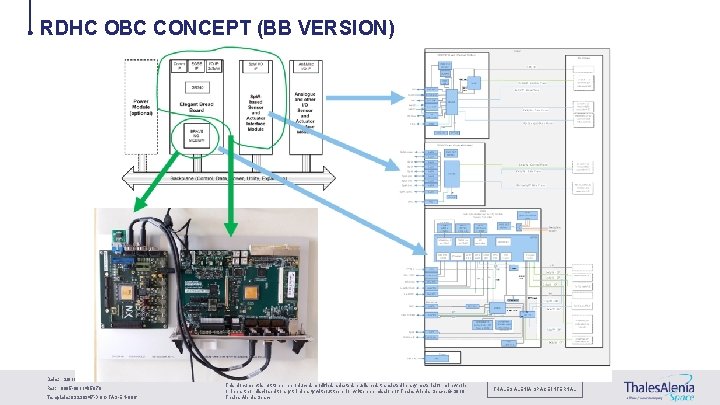

RDHC OBC CONCEPT (BB VERSION) Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

RDHC OBC CONCEPT (EBB VERSION) Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

CORA-RDHC SOFTWARE OVERVIEW Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

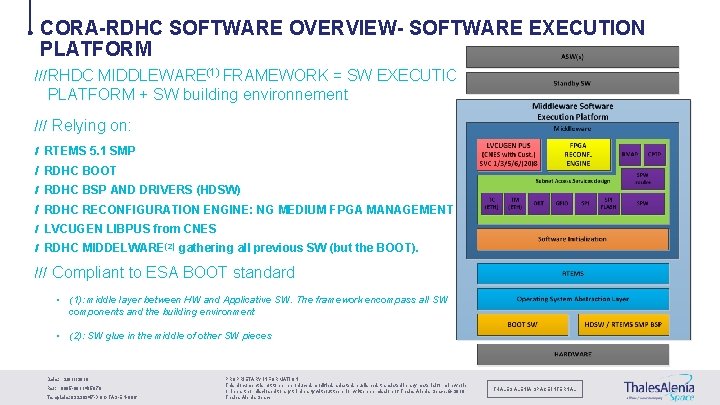

CORA-RDHC SOFTWARE OVERVIEW- SOFTWARE EXECUTION PLATFORM RHDC MIDDLEWARE(1) FRAMEWORK = SW EXECUTION PLATFORM + SW building environnement Relying on: RTEMS 5. 1 SMP RDHC BOOT RDHC BSP AND DRIVERS (HDSW) RDHC RECONFIGURATION ENGINE: NG MEDIUM FPGA MANAGEMENT LVCUGEN LIBPUS from CNES RDHC MIDDELWARE(2) gathering all previous SW (but the BOOT). Compliant to ESA BOOT standard • (1): middle layer between HW and Applicative SW. The framework encompass all SW components and the building environment • (2): SW glue in the middle of other SW pieces Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

GR 740 HW EXPERIENCE Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

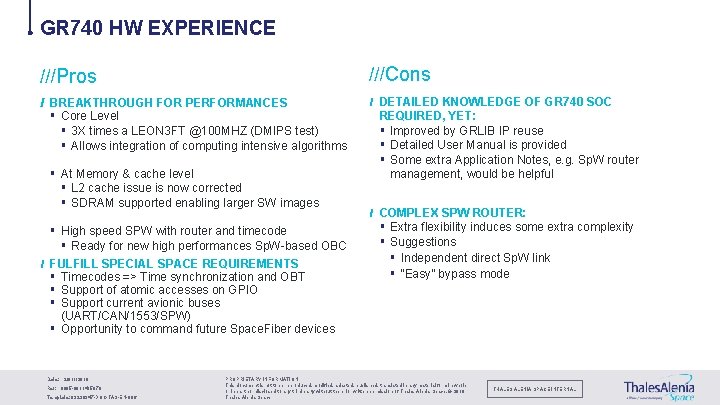

GR 740 HW EXPERIENCE Cons Pros BREAKTHROUGH FOR PERFORMANCES § Core Level § 3 X times a LEON 3 FT @100 MHZ (DMIPS test) § Allows integration of computing intensive algorithms § At Memory & cache level § L 2 cache issue is now corrected § SDRAM supported enabling larger SW images § High speed SPW with router and timecode § Ready for new high performances Sp. W-based OBC FULFILL SPECIAL SPACE REQUIREMENTS § Timecodes => Time synchronization and OBT § Support of atomic accesses on GPIO § Support current avionic buses (UART/CAN/1553/SPW) § Opportunity to command future Space. Fiber devices Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 DETAILED KNOWLEDGE OF GR 740 SOC REQUIRED, YET: § Improved by GRLIB IP reuse § Detailed User Manual is provided § Some extra Application Notes, e. g. Sp. W router management, would be helpful COMPLEX SPW ROUTER: § Extra flexibility induces some extra complexity § Suggestions § Independent direct Sp. W link § “Easy” bypass mode PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

GR 740 CODING EXPERIENCE Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

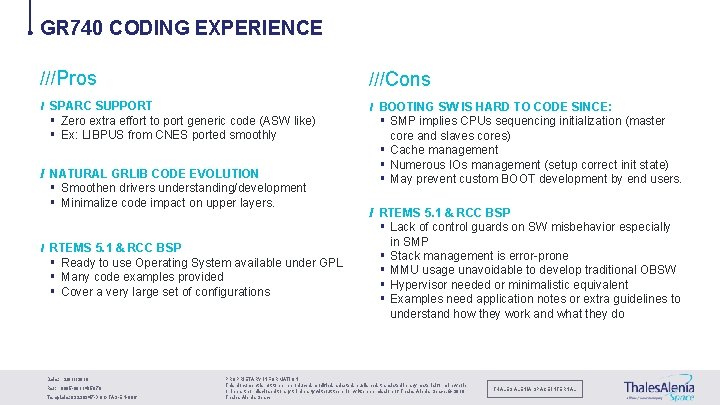

GR 740 CODING EXPERIENCE Pros Cons SPARC SUPPORT § Zero extra effort to port generic code (ASW like) § Ex: LIBPUS from CNES ported smoothly NATURAL GRLIB CODE EVOLUTION § Smoothen drivers understanding/development § Minimalize code impact on upper layers. RTEMS 5. 1 & RCC BSP § Ready to use Operating System available under GPL § Many code examples provided § Cover a very large set of configurations Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 BOOTING SW IS HARD TO CODE SINCE: § SMP implies CPUs sequencing initialization (master core and slaves cores) § Cache management § Numerous IOs management (setup correct init state) § May prevent custom BOOT development by end users. RTEMS 5. 1 & RCC BSP § Lack of control guards on SW misbehavior especially in SMP § Stack management is error-prone § MMU usage unavoidable to develop traditional OBSW § Hypervisor needed or minimalistic equivalent § Examples need application notes or extra guidelines to understand how they work and what they do PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

GR 740 DEBUG EXPERIENCE Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

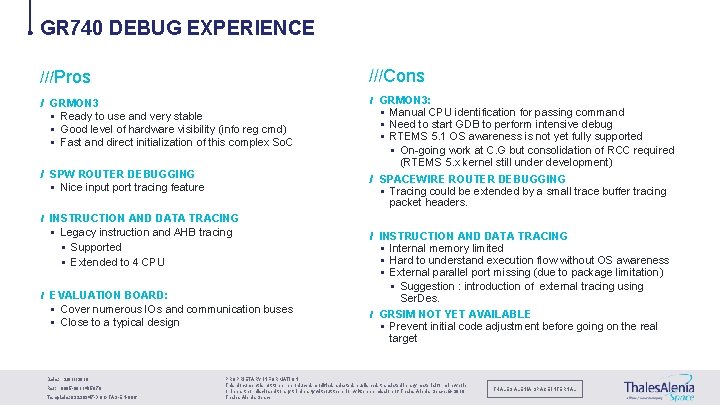

GR 740 DEBUG EXPERIENCE Cons Pros GRMON 3 § Ready to use and very stable § Good level of hardware visibility (info reg cmd) § Fast and direct initialization of this complex So. C SPW ROUTER DEBUGGING § Nice input port tracing feature SPACEWIRE ROUTER DEBUGGING § Tracing could be extended by a small trace buffer tracing packet headers. INSTRUCTION AND DATA TRACING § Legacy instruction and AHB tracing § Supported § Extended to 4 CPU EVALUATION BOARD: § Cover numerous IOs and communication buses § Close to a typical design Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 GRMON 3: § Manual CPU identification for passing command § Need to start GDB to perform intensive debug § RTEMS 5. 1 OS awareness is not yet fully supported § On-going work at C. G but consolidation of RCC required (RTEMS 5. x kernel still under development) INSTRUCTION AND DATA TRACING § Internal memory limited § Hard to understand execution flow without OS awareness § External parallel port missing (due to package limitation) § Suggestion : introduction of external tracing using Ser. Des. GRSIM NOT YET AVAILABLE § Prevent initial code adjustment before going on the real target PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

QUESTIONS? Contact Us maxime. guimard@thalesaleniaspace. com Date: 28/11/2019 Ref: 0005 -0011485879 Template: 83230347 -DOC-TAS-EN-006 PROPRIETARY INFORMATION This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space THALES ALENIA SPACE INTERNAL

- Slides: 18