Reconfigurable Systems Conceptual Design Review 1 Reconfigurable Systems

Reconfigurable Systems Conceptual Design Review 1

Reconfigurable Systems n Team ¨ ¨ ¨ n Client / Faculty Mentor ¨ n Dr. Joe Law Graduate Mentor ¨ n Dr. Greg Donohoe Lead Instructor ¨ n Chris Canine Terseer Ityavyar Cameron D. Dennis John Geidl Sponsor ¨ ¨ NASA UI CAMBR 2

Background 3

Embedded Computing n Invisible to the user ¨ Example: The modern day vehicle has about 40 microprocessors n Goal: High speed with smallest footprint ¨ Small footprint n Size n Weight n Power consumption ¨ Speed (computing power) n Linear system ¨ Computing is done ¨ Resources take up logically memory 4

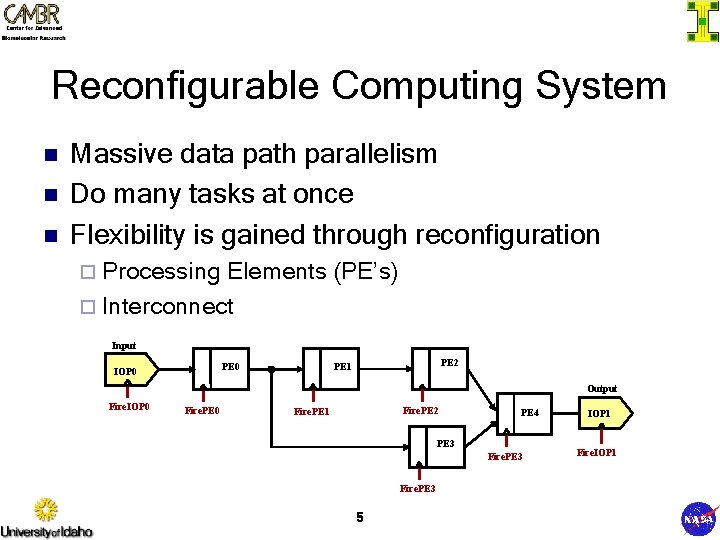

Reconfigurable Computing System n n n Massive data path parallelism Do many tasks at once Flexibility is gained through reconfiguration ¨ Processing Elements (PE’s) ¨ Interconnect Input PE 0 IOP 0 PE 2 PE 1 Output Fire. IOP 0 Fire. PE 2 Fire. PE 1 PE 4 PE 3 Fire. PE 3 5 IOP 1 Fire. IOP 1

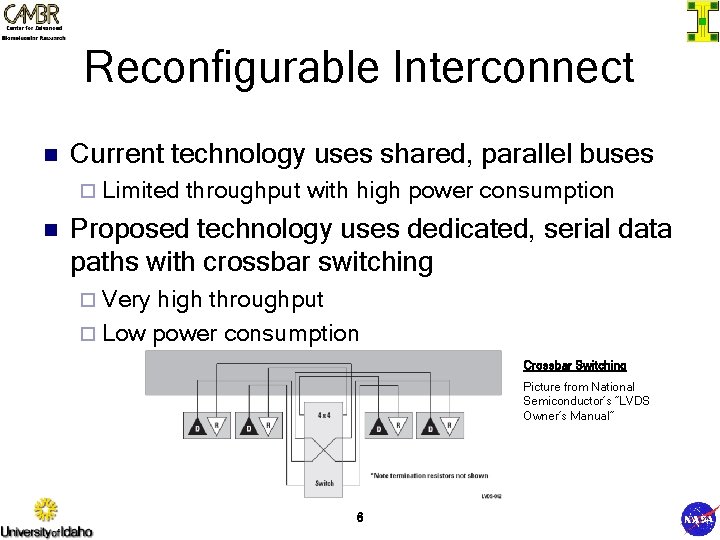

Reconfigurable Interconnect n Current technology uses shared, parallel buses ¨ Limited n throughput with high power consumption Proposed technology uses dedicated, serial data paths with crossbar switching ¨ Very high throughput ¨ Low power consumption Crossbar Switching Picture from National Semiconductor’s “LVDS Owner’s Manual” 6

Last Year’s S. D. Project Configurable Memory Module Interconnect Control Global Clock Processor Node 7

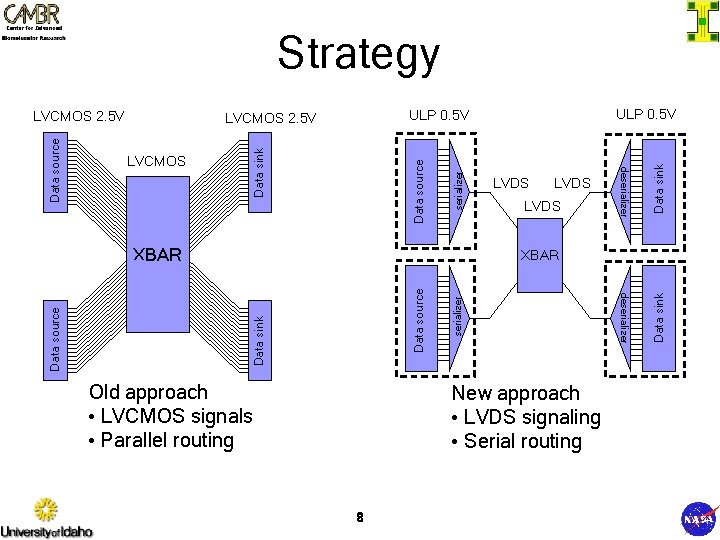

Strategy Data sink LVDS Data sink serializer Data source Data sink LVDS Old approach • LVCMOS signals • Parallel routing serializer Data source XBAR Data sink Data source XBAR LVDS deserializer LVCMOS ULP 0. 5 V LVCMOS 2. 5 V deserializer Data source LVCMOS 2. 5 V New approach • LVDS signaling • Serial routing 8

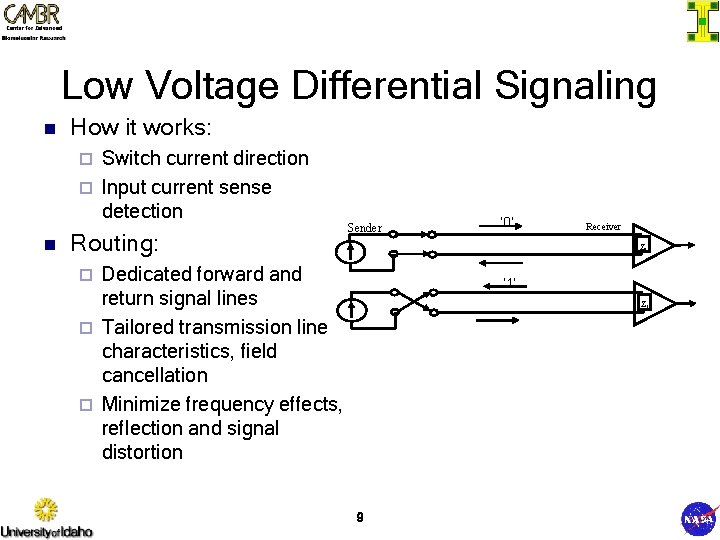

Low Voltage Differential Signaling n How it works: Switch current direction ¨ Input current sense detection ¨ n Routing: Sender ‘ 0’ Receiver ZL Dedicated forward and return signal lines ¨ Tailored transmission line characteristics, field cancellation ¨ Minimize frequency effects, reflection and signal distortion ¨ ‘ 1’ ZL 9

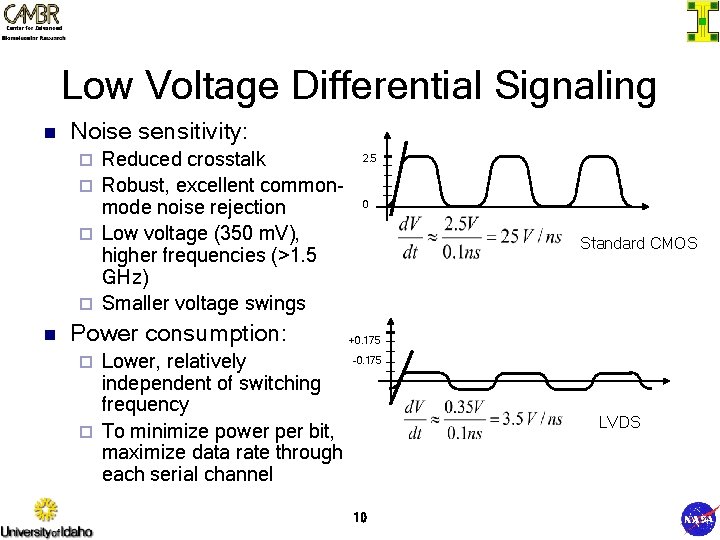

Low Voltage Differential Signaling n Noise sensitivity: Reduced crosstalk ¨ Robust, excellent commonmode noise rejection ¨ Low voltage (350 m. V), higher frequencies (>1. 5 GHz) ¨ Smaller voltage swings ¨ n Power consumption: Lower, relatively independent of switching frequency ¨ To minimize power per bit, maximize data rate through each serial channel ¨ 2. 5 0 Standard CMOS +0. 175 -0. 175 LVDS 10

What We Will Do 11

Our Goal n n n To compare serial communication versus parallel communication Show that Low Voltage Differential Signaling (LVDS) communication is a viable implementation method Highlight the benefits of LVDS including ¨ High-speed data transfer ¨ Lowered Electro-Magnetic Interference ¨ Low power consumption ¨ Reduced circuit board area 12 (EMI)

Needs n A study that will ¨ Convince a spacecraft system engineer to use serial LVDS designs for reconfigurable systems ¨ Provide the documentation to allow the implementation of serial LVDS designs 13

Constraints n n n No slower than 800 data Mbits per second Variable path delay Function with different delays in the communication path No errors detected in a bit error rate test (BERT) in 15 minutes of continuous operation Preferred all on one printed circuit board 14

Specifications n Proof of concept ¨ Compare differential, sequential communication vs. single-ended, parallel communication. ¨ Power consumption – “Gigahertz @ milli. Watts” n Reduced watts per bit ¨ Circuit board area – Show a greatly reduced area vs. parallel system 15

Specifications (cont. ) n n Two Source Nodes Two Destination Nodes ¨ Transmit from either source to either destination depending on a specific control signal sent to switch the central crosspoint switch n Desirable ¨ Go to two destinations from one source ¨ Full bidirectional communication 16

Deliverables n Reports ¨ Compare serial vs. parallel implementations for power and area ¨ Describe a design flow using the Cadence Tools ¨ Proper documentation to pass on to someone else to duplicate the design 17

Deliverables (cont. ) n Hardware ¨ Demo a working serial system meeting the specifications above ¨ Instrument as necessary to demonstrate the specifications n n Measure and report Bit Error Rate (BERT) Measure and report power consumption 18

Design Implementation Options 19

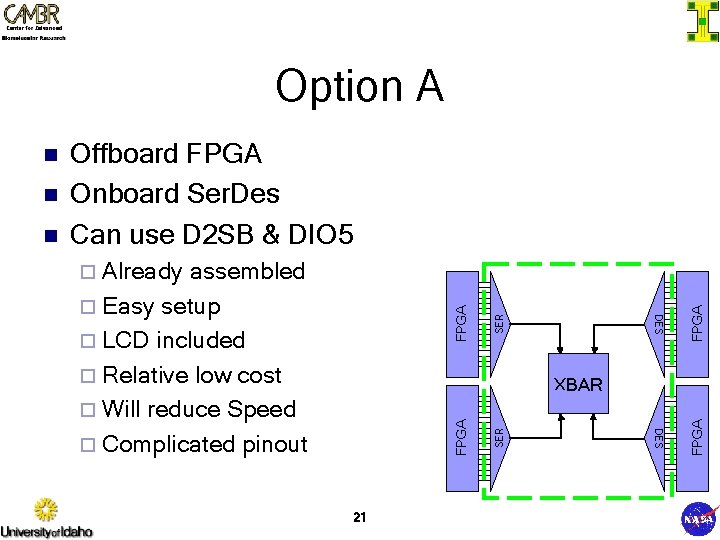

Components Needed n n 4 Field Programmable Gate Arrays (FPGA) 4 Serializer/Deserializer’s (Ser. Des) 1 Crosspoint Switch (XBAR) LCD Displays 20

Option A DES FPGA assembled ¨ Easy setup ¨ LCD included ¨ Relative low cost ¨ Will reduce Speed ¨ Complicated pinout SER ¨ Already XBAR 21 SER n FPGA n Offboard FPGA Onboard Ser. Des Can use D 2 SB & DIO 5 FPGA n

Option A Specifics n Offboard FPGA ¨ Digilent n D 2 SB/DIO 5 Kit with Xilinx Spartan IIE FPGA Onboard Ser. Des ¨ National n Onboard Crosspoint Switch ¨ National n Semiconductor DS 92 LV 18 Semiconductor SCAN 90 CP 02 Additional Onboard Hardware ¨ LCD and other display hardware is included on the D 2 SB/DIO 5 board 22

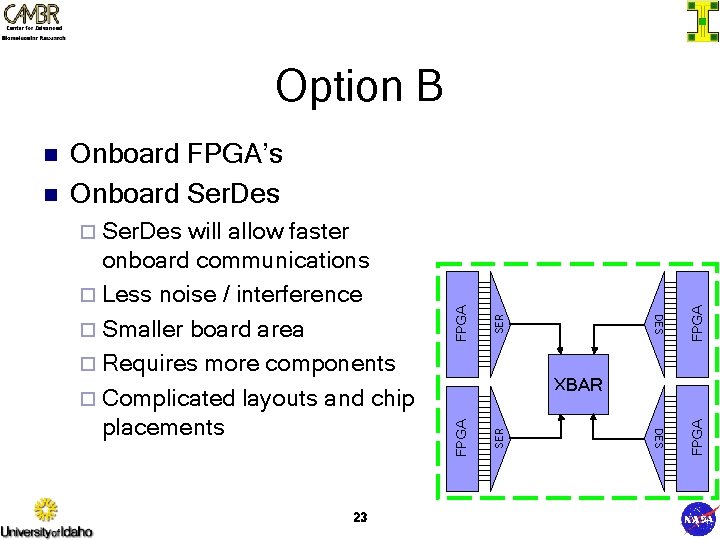

Option B FPGA DES 23 DES FPGA XBAR SER will allow faster onboard communications ¨ Less noise / interference ¨ Smaller board area ¨ Requires more components ¨ Complicated layouts and chip placements SER ¨ Ser. Des FPGA n Onboard FPGA’s Onboard Ser. Des FPGA n

Option B Specifics n Onboard FPGA ¨ Xilinx n Spartan IIE FPGA Onboard Ser. Des ¨ National n Onboard Crosspoint Switch ¨ National n Semiconductor DS 92 LV 18 Semiconductor SCAN 90 CP 02 Additional Onboard Hardware ¨ LCD to display BERT results 24

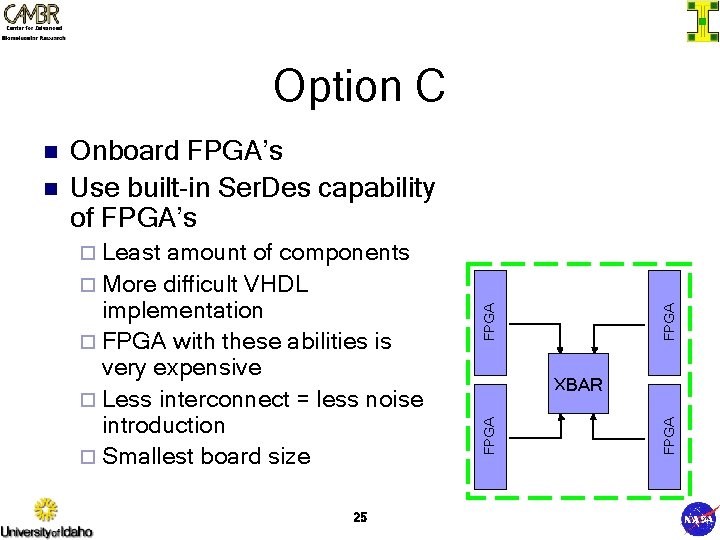

Option C 25 XBAR FPGA amount of components ¨ More difficult VHDL implementation ¨ FPGA with these abilities is very expensive ¨ Less interconnect = less noise introduction ¨ Smallest board size FPGA ¨ Least FPGA n Onboard FPGA’s Use built-in Ser. Des capability of FPGA’s FPGA n

Option C Specifics n Onboard FPGA ¨ Xilinx n Onboard Ser. Des ¨ None n Virtex Family FPGA Required Onboard Crosspoint Switch ¨ National n Semiconductor SCAN 90 CP 02 Additional Onboard Hardware ¨ LCD to display BERT results 26

Our Recommendation - Option B Reduced cost n Ease of implementation n All on one printed circuit board n 27

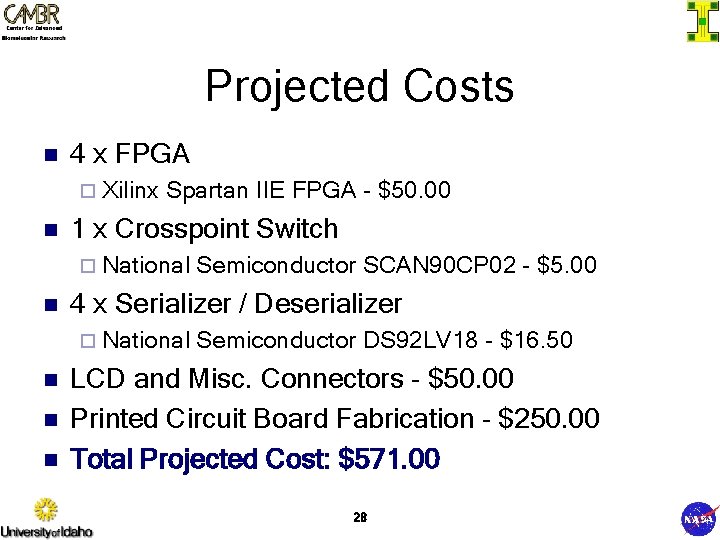

Projected Costs n 4 x FPGA ¨ Xilinx n Spartan IIE FPGA - $50. 00 1 x Crosspoint Switch ¨ National n 4 x Serializer / Deserializer ¨ National n n n Semiconductor SCAN 90 CP 02 - $5. 00 Semiconductor DS 92 LV 18 - $16. 50 LCD and Misc. Connectors - $50. 00 Printed Circuit Board Fabrication - $250. 00 Total Projected Cost: $571. 00 28

Questions & Comments 29

Work Breakdown Structure 30

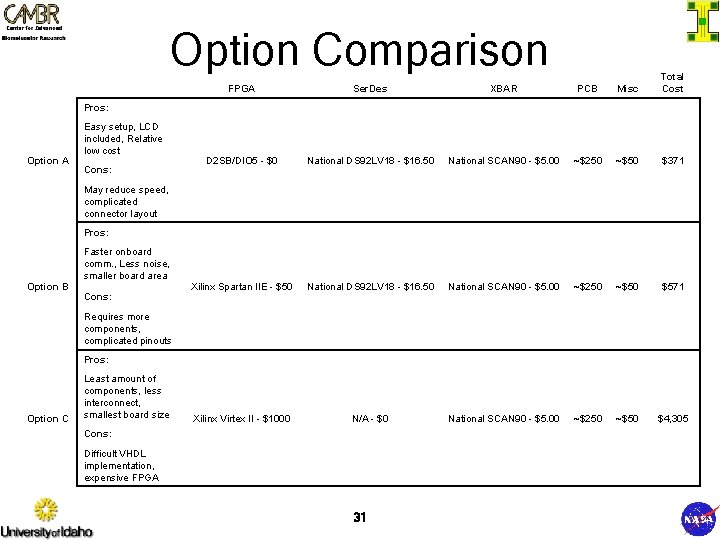

Option Comparison FPGA Ser. Des XBAR PCB Misc Total Cost D 2 SB/DIO 5 - $0 National DS 92 LV 18 - $16. 50 National SCAN 90 - $5. 00 ~$250 ~$50 $371 Xilinx Spartan IIE - $50 National DS 92 LV 18 - $16. 50 National SCAN 90 - $5. 00 ~$250 ~$50 $571 Xilinx Virtex II - $1000 N/A - $0 National SCAN 90 - $5. 00 ~$250 ~$50 $4, 305 Pros: Option A Easy setup, LCD included, Relative low cost Cons: May reduce speed, complicated connector layout Pros: Option B Faster onboard comm. , Less noise, smaller board area Cons: Requires more components, complicated pinouts Pros: Option C Least amount of components, less interconnect, smallest board size Cons: Difficult VHDL implementation, expensive FPGA 31

- Slides: 31