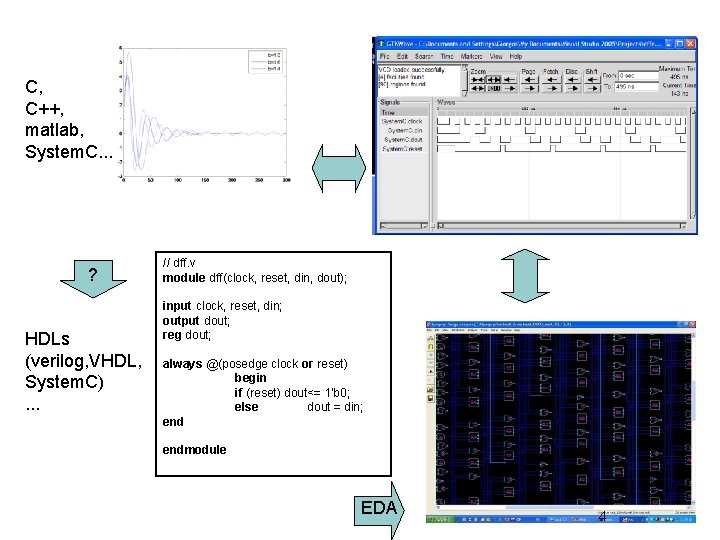

C C matlab System C HDLs verilog VHDL

C, C++, matlab, System. C. . . ? HDLs (verilog, VHDL, System. C). . . // dff. v module dff(clock, reset, din, dout); input clock, reset, din; output dout; reg dout; always @(posedge clock or reset) begin if (reset) dout<= 1'b 0; else dout = din; endmodule EDA 4

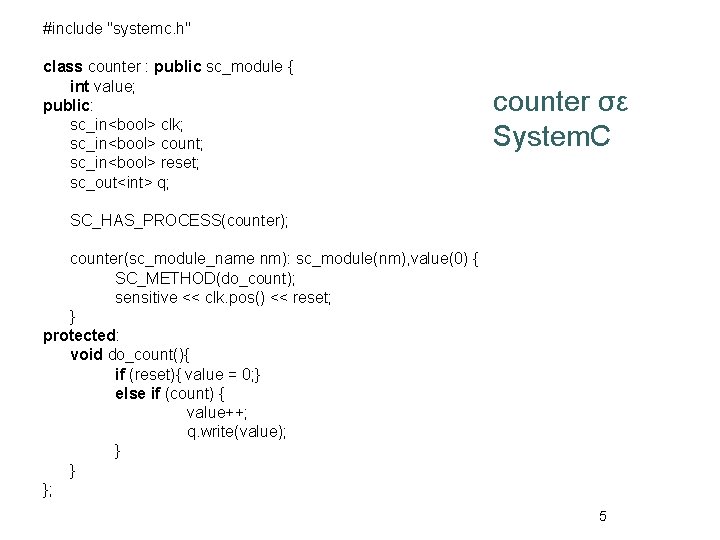

#include "systemc. h" class counter : public sc_module { int value; public: sc_in<bool> clk; sc_in<bool> count; sc_in<bool> reset; sc_out<int> q; counter σε System. C SC_HAS_PROCESS(counter); counter(sc_module_name nm): sc_module(nm), value(0) { SC_METHOD(do_count); sensitive << clk. pos() << reset; } protected: void do_count(){ if (reset){ value = 0; } else if (count) { value++; q. write(value); } } }; 5

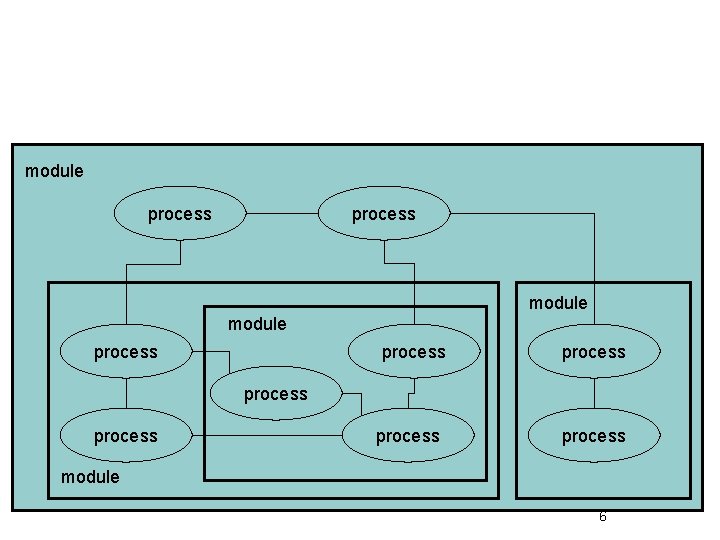

module process process process module 6

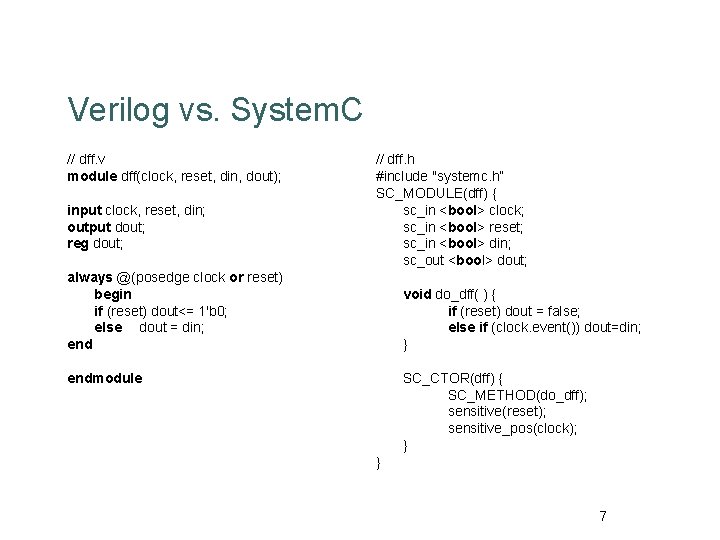

Verilog vs. System. C // dff. v module dff(clock, reset, din, dout); input clock, reset, din; output dout; reg dout; // dff. h #include "systemc. h“ SC_MODULE(dff) { sc_in <bool> clock; sc_in <bool> reset; sc_in <bool> din; sc_out <bool> dout; always @(posedge clock or reset) begin if (reset) dout<= 1'b 0; else dout = din; end void do_dff( ) { if (reset) dout = false; else if (clock. event()) dout=din; } endmodule SC_CTOR(dff) { SC_METHOD(do_dff); sensitive(reset); sensitive_pos(clock); } } 7

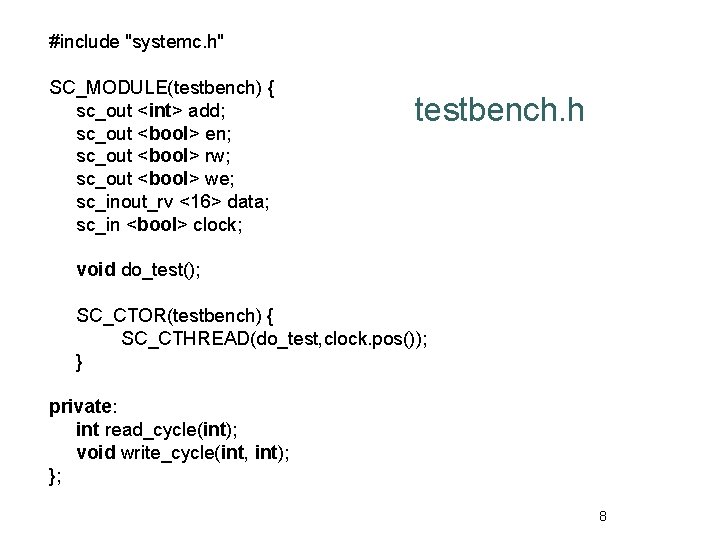

#include "systemc. h" SC_MODULE(testbench) { sc_out <int> add; sc_out <bool> en; sc_out <bool> rw; sc_out <bool> we; sc_inout_rv <16> data; sc_in <bool> clock; testbench. h void do_test(); SC_CTOR(testbench) { SC_CTHREAD(do_test, clock. pos()); } private: int read_cycle(int); void write_cycle(int, int); }; 8

#include "testbench. h" testbench. cpp void testbench: : do_test() { int i, j, flag, tmp. A, tmp. DW, tmp. DR; for(j=0; 1; j++) { flag=0; wait(2); tmp. A=1; tmp. DW=123; for (i=0; i<3; i++) read_cycle(tmp. A+i+j); for (i=0; i<3; i++) write_cycle(tmp. A+i+j, tmp. DW+i+j); for (i=0; i<3; i++) { tmp. DR=read_cycle(tmp. A+i+j); if (tmp. DR!=(tmp. DW+i+j)) { fprintf(stderr, "error: expected 0 x%x, but 0 x%x", tmp. DW+i+j, tmp. DR); flag =1; } } if (!flag) fprintf(stderr, "test passed. . . Wn"); } } 9

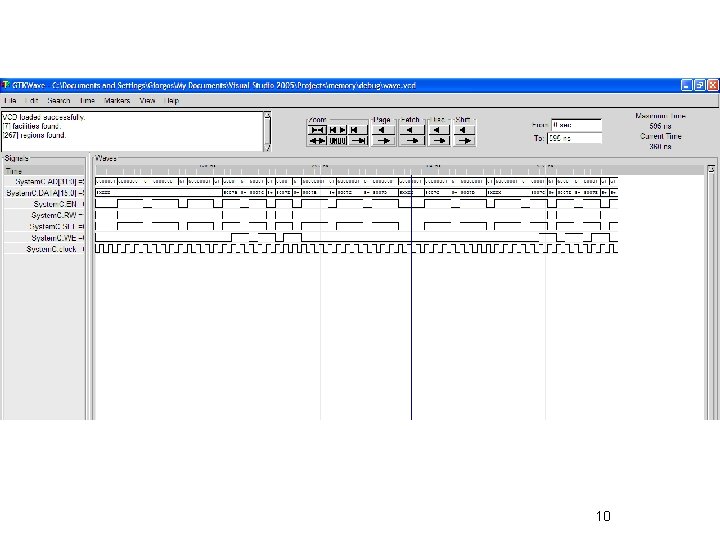

10

- Slides: 10