Limbajul Verilog Istoric Limbajele de descriere hardware HDLs

Limbajul Verilog. Istoric Limbajele de descriere hardware (HDL’s) sunt limbaje de programare utilizate pentru descrierea diferitelor circuite electrice, în special a celor digitale. Aceste limbaje pot fi folosite pentru a descrie un circuit • din punctul de vedere al alcătuirii fizice a acestuia • pentru descrierea unor circuite din punctul de vedere al funcţionalităţii lor, fără a interesa structura lor fizică.

Limbajul Verilog. Istoric Limbajul Verilog a fost brevetat pentru prima dată de compania Gateway Design Automation Inc în 1984 şi are drept precursori limbajele: • Hi. Lo (limbaj de descriere hardware) • C În momentul creării limbajului acesta nu era standardizat şi a suferit foarte multe modificări de la lansarea sa iniţială.

Limbajul Verilog. Istoric • În perioada 1985 - 1987 a fost creat şi primul simulator de Verilog ce a fost îmbunătăţit odată cu fiecare nouă lansare pe piaţă. Prima extensie importantă a limbajului a fost Verilog-XL ce a adus printre altele o nouă şi eficientă metodă pentru simulare la nivelul de poartă logică. • În 1990 compania Cadence Design System a luat decizia de a cumpăra Gateway Design Automation, preluând în acelaşi timp şi destinele limbajului Verilog. În acelaşi an, Cadence a luat hotărârea de a face din Verilog un limbaj de programare ce aparţine domeniului public. Aceasta hotărâre a dat şansa oricărei companii rivale de a dezvolta simulatoare de Verilog.

Limbajul Verilog. Istoric După puţin timp Cadence a realizat că oricare dintre aceste companii producătoare de simulatoare Verilog pot modifica limbajul Verilog la fel cum au făcut la timpul lor Gateway Design sau Cadence. Acest lucru putea duce la îndepărtarea de scopul iniţial al lansării Verilog-ului în proprietatea domeniului public. Drept urmare, a fost creată organizaţia Open Verilog International (OVI) în care erau reprezentate toate companiile mari care se ocupau cu oferirea de unelte pentru dezvoltare hardware.

Limbajul Verilog. Istoric Sarcina principală primită standardizarea limbajului. de OVI a fost Primele schiţe ale standardului propus au fost copii aproape identice ale manualului Verilog lansat de Cadence. Între timp, popularitatea limbajului Verilog creştea aproape exponenţial. Verilog ca şi limbaj de descriere hardware a atras mai mulţi utilizatori decât VHDL ce era deja bine definit şi sprijinit cu fonduri federale. Prin urmare, la mijlocul anului 1993 a fost format comitetul IEEE cu numărul 1364 ce a lansat standardul Verilog în mai 1995, cunoscut mai ales sub denumirea de IEEE Std. 1364 -1995.

Introducere în Verilog Limbajul Verilog, ca de altfel orice limbaj de descriere hardware permite descrierea circuitelor atât folosind metodologiile: • Bottom-Up • Top-Down.

Introducere în Verilog. Bottom Up Metoda tradiţională de proiectare a circuitelor electrice este Bottom -Up. Fiecare circuit este descris la nivelul de porţi logice utilizând celulele standard. Ţinând cont de complexitatea circuitelor moderne, această apropiere este din ce în ce mai puţin folosită şi aproape imposibil de întreţinut. Sistemele noi constau din ASIC-uri sau FPGA-uri cu o complexitate de milioane de tranzistori. Acest tip de proiectare trebuie să dispară în favoarea noilor metodologii structurale şi ierarhice.

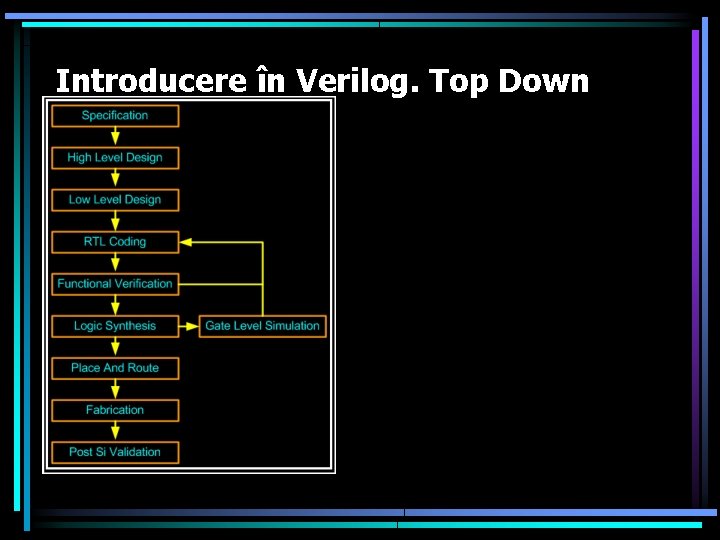

Introducere în Verilog. Top Down Tipul de proiectare dorit de toţi proiectanţii moderni este cel Top-Down. Un design Top-Down real permite testarea circuitelor încă din faza de proiectare permiţând schimbarea tehnologiilor atunci când acestea nu mai corespund. O strategie pur Top-Down este de obicei foarte greu de urmat şi de aceea este de preferat o structurare a proiectului folosind această metodă dar o dezvoltare a diferitelor module aflate la nivelul cel mai de jos folosind strategia Bottom. Up.

Introducere în Verilog. Top Down

Nivele de abstractizare hardware Orice limbaj de descriere hardware modern poate fi folosit pentru proiectarea la orice nivel de abstractizare începând de la modelele arhitecturale de nivel înalt şi până la modelele de nivel cel mai scăzut (switch, poartă logică, tranzistor). Din punctul de vedere al nivelelor de abstractizare, descrierea cu ajutorul limbajului Verilog poate fi împărţită în: – funcţională (behavioural models) – structurală (structural models)

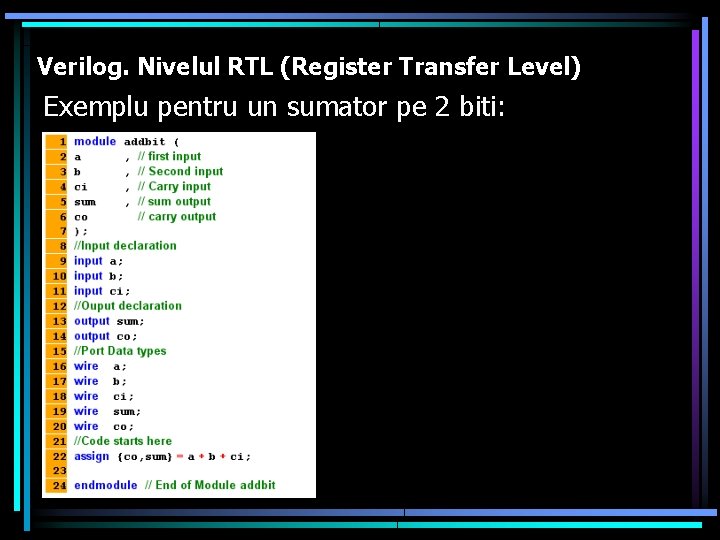

Verilog. Nivelul RTL (Register Transfer Level) Exemplu pentru un sumator pe 2 biti:

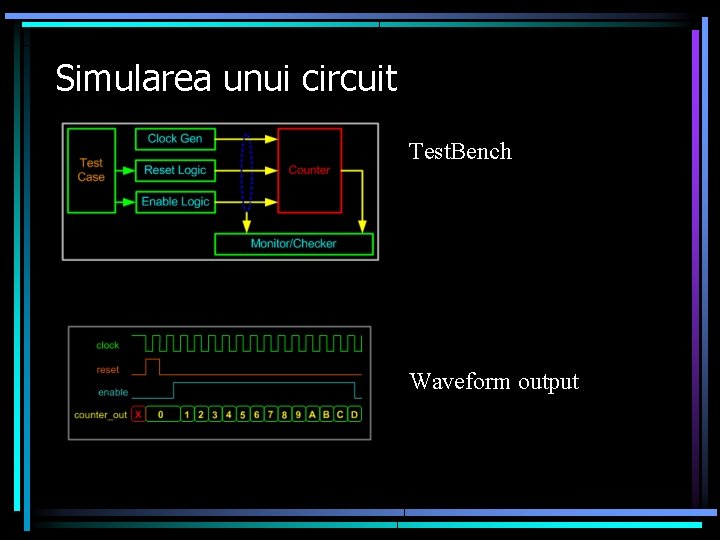

Simularea unui circuit Test. Bench Waveform output

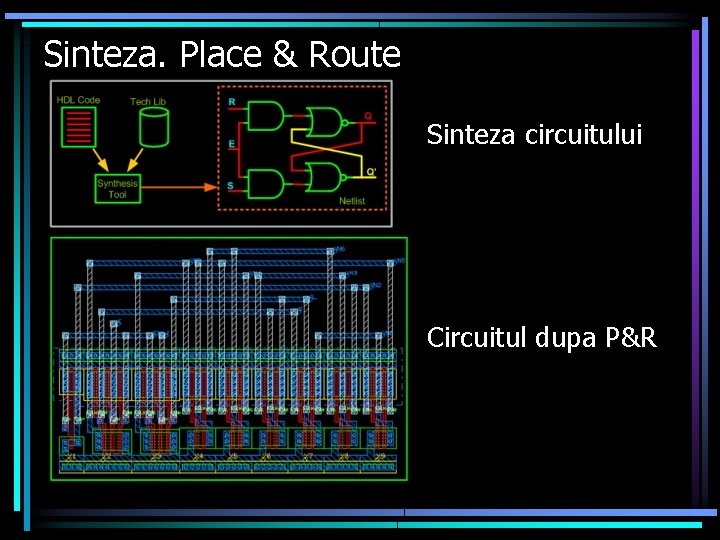

Sinteza. Place & Route Sinteza circuitului Circuitul dupa P&R

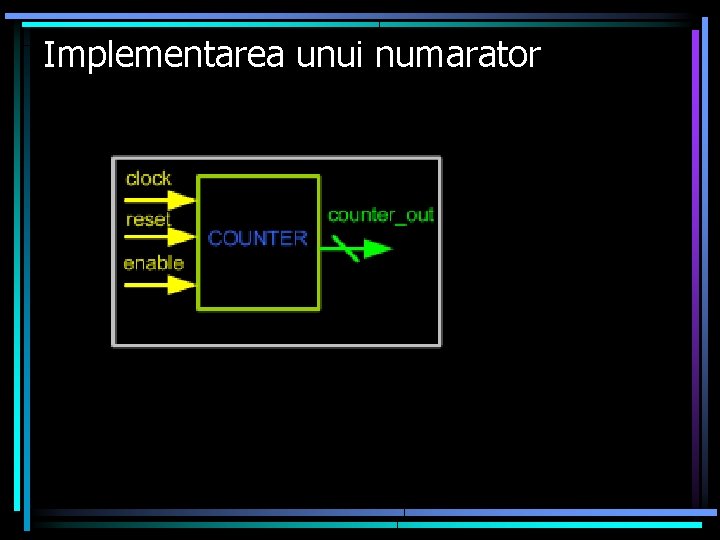

Implementarea unui numarator

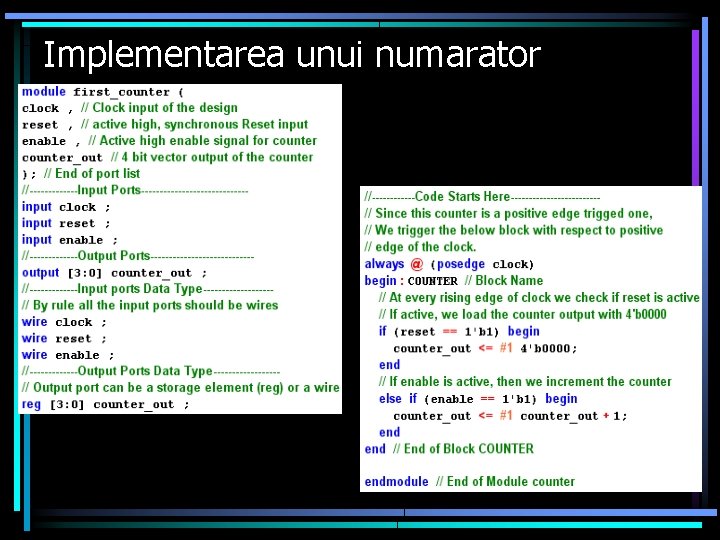

Implementarea unui numarator

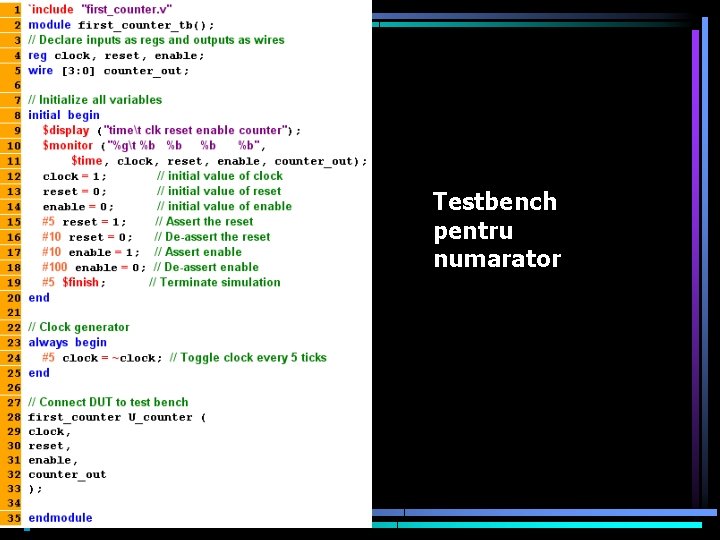

Testbench pentru numarator

- Slides: 16