Arrays under System Verilog Arrays SV supports both

Arrays under System. Verilog

Arrays • SV supports both packed and unpacked arrays • As the name suggests, packed arrays are stored in contiguous memory locations and are treated as a single vector • Thus, packed arrays may only hold bit-wise types (e. g. , logic) unlike unpacked arrays • For synthesis stick to packed arrays

Arrays Specification • The array type is set when the array is declared • Packed arrays are designated by including the index range to the left of the name, unpacked on the right • This declares an unpacked array with 256 elements, each being a 3 -bit (packed) vector logic [2: 0] sreg [255: 0]

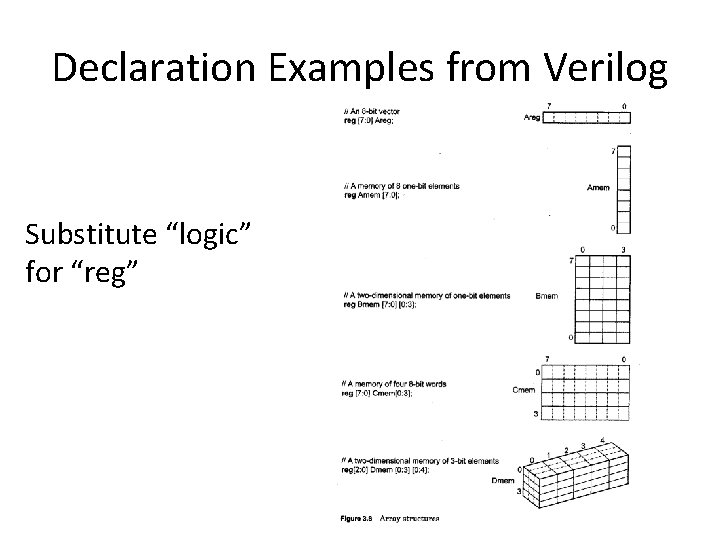

Declaration Examples from Verilog Substitute “logic” for “reg”

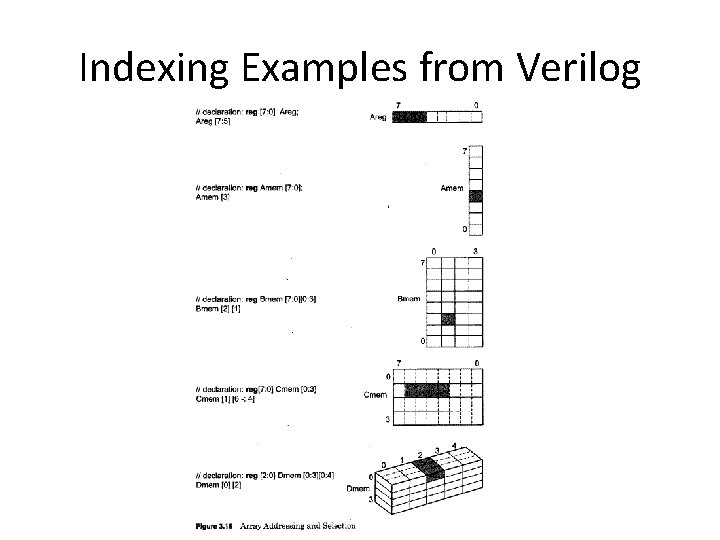

Indexing Examples from Verilog

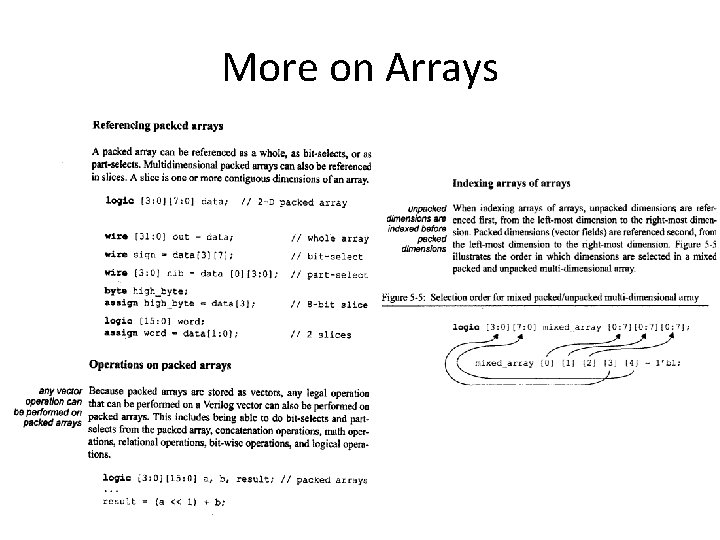

More on Arrays

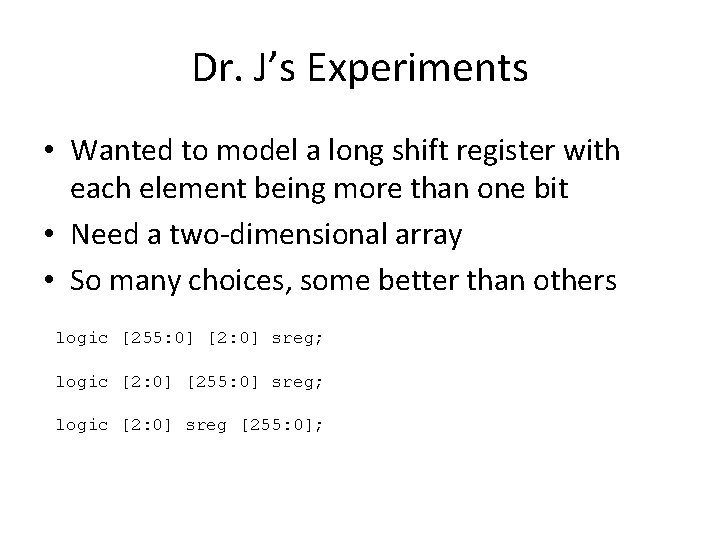

Dr. J’s Experiments • Wanted to model a long shift register with each element being more than one bit • Need a two-dimensional array • So many choices, some better than others logic [255: 0] [2: 0] sreg; logic [2: 0] [255: 0] sreg; logic [2: 0] sreg [255: 0];

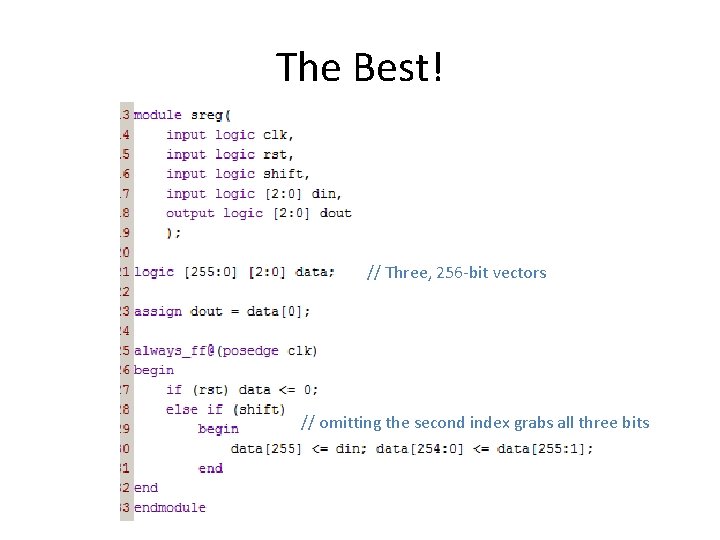

The Best! // Three, 256 -bit vectors // omitting the second index grabs all three bits

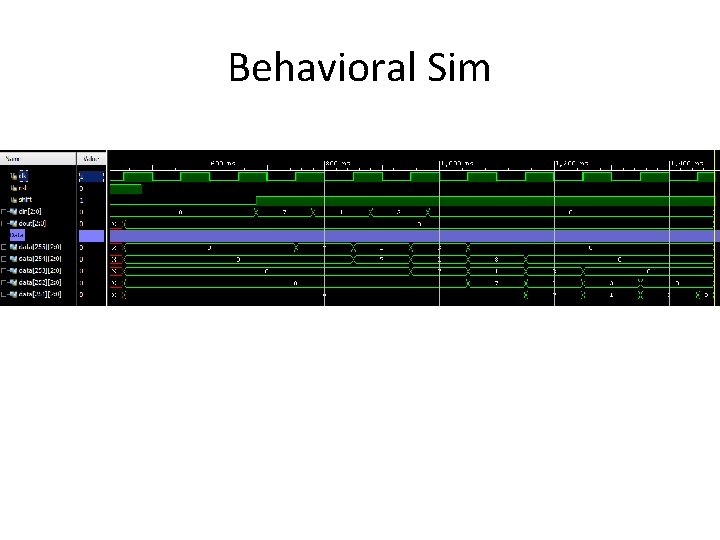

Behavioral Sim

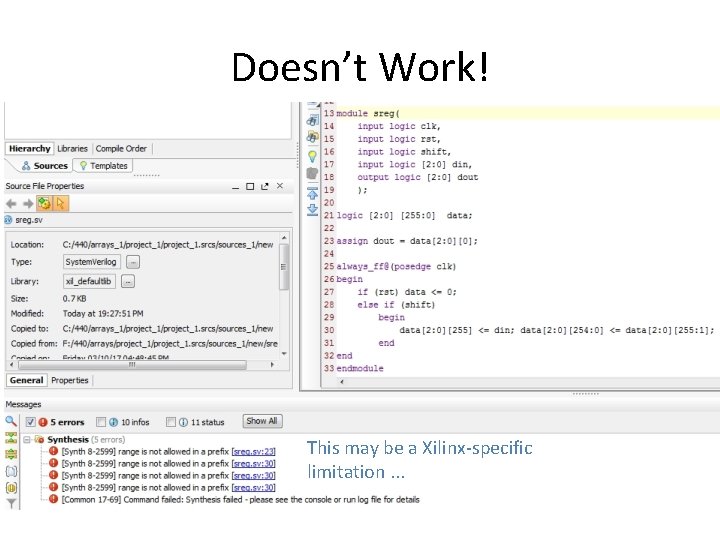

Doesn’t Work! This may be a Xilinx-specific limitation. . .

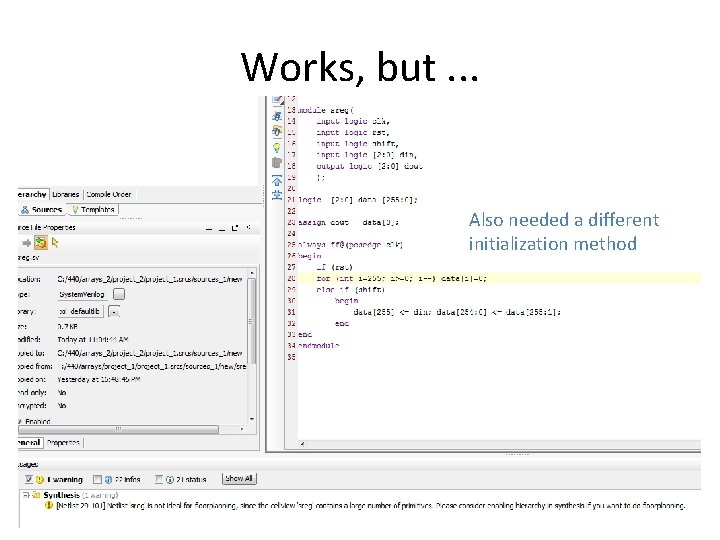

Works, but. . . Also needed a different initialization method

Guidelines • Use packed arrays to model – vectors of 1 -bit types, e. g. , logic – vectors where it is useful to access subfields • Use unpacked arrays to model – Arrays of byte, int, real, etc. – Arrays accessed one element at a time, e. g. , RAM

- Slides: 12