A FaultIndependent Transitive Closure Algorithm for Redundancy Identification

- Slides: 23

A Fault-Independent Transitive Closure Algorithm for Redundancy Identification Vishal J. Mehta Kunal K. Dave Vishwani D. Agrawal Michael L. Bushnell ECE Dept. , Rutgers University Piscataway, New Jersey, USA 12/4/2020 A Fault-Independent etc… 1

Talk Outline • Problem statement • Background • Implication graph • Partial implications • Transitive closure • Redundancy identification • Node fixation • Results • Conclusion 12/4/2020 A Fault-Independent etc… 2

Problem Statement • We make significant improvements in Redundancy identification of combinational circuits using partial implications and transitive closure. • The new techniques have many other applications. 12/4/2020 A Fault-Independent etc… 3

Background • Implication graphs: • Chakradhar, et al. , Book, 1990 • Larrabee, IEEE-TCAD, 1992 • Zhao, et al. , IEEE-VTS, 1997 • Transitive closure: • ATPG: Chakradhar, et al. , IEEE-TCAD, 1993 • Redundancy, Agrawal, et al. , ATS, 1996 • Partial implications: • Henftling, et al. , ECAD, 1995 • Gaur, et al. , DELTA, 2002 12/4/2020 A Fault-Independent etc… 4

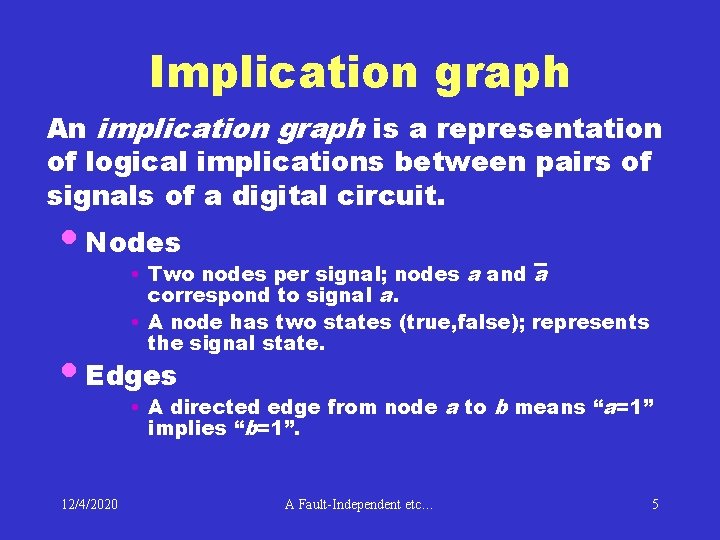

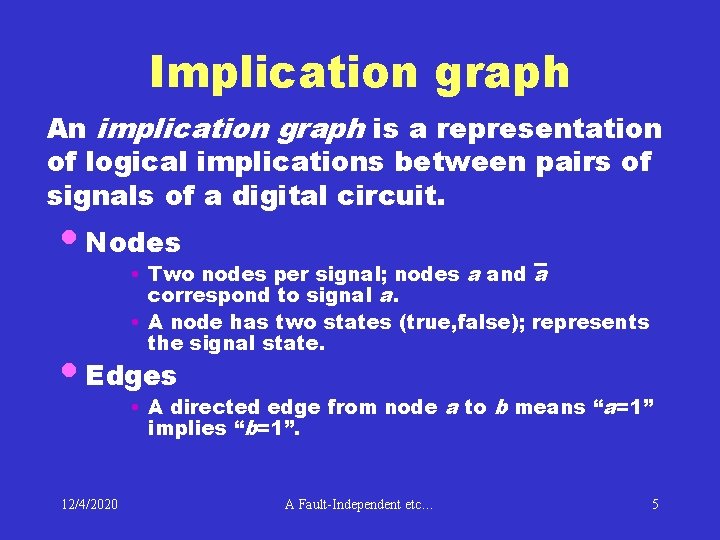

Implication graph An implication graph is a representation of logical implications between pairs of signals of a digital circuit. • Nodes • Two nodes per signal; nodes a and a correspond to signal a. • A node has two states (true, false); represents the signal state. • Edges • A directed edge from node a to b means “a=1” implies “b=1”. 12/4/2020 A Fault-Independent etc… 5

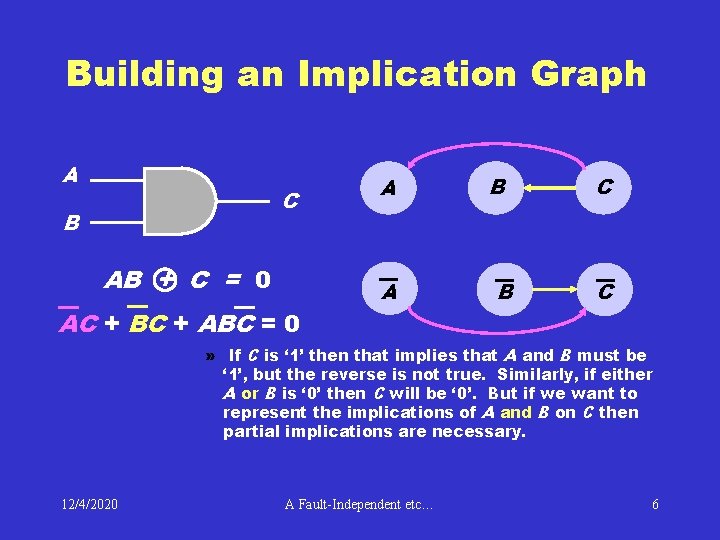

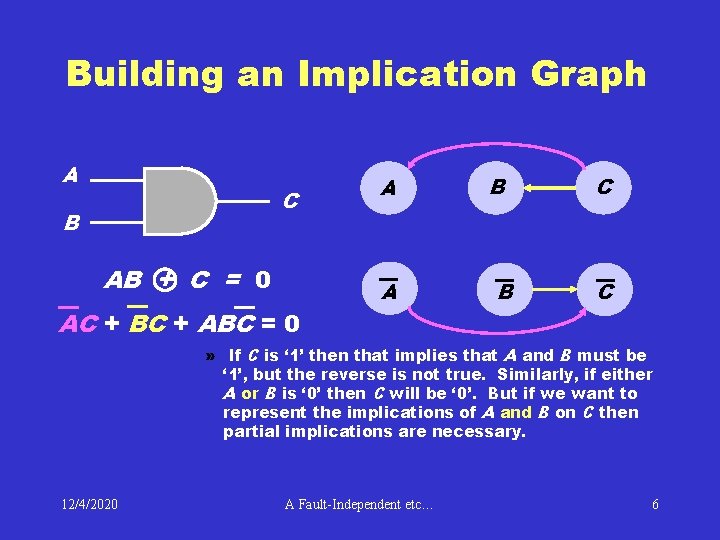

Building an Implication Graph A C B AB + C = 0 AC + BC + ABC = 0 A A B B C C » If C is ‘ 1’ then that implies that A and B must be ‘ 1’, but the reverse is not true. Similarly, if either A or B is ‘ 0’ then C will be ‘ 0’. But if we want to represent the implications of A and B on C then partial implications are necessary. 12/4/2020 A Fault-Independent etc… 6

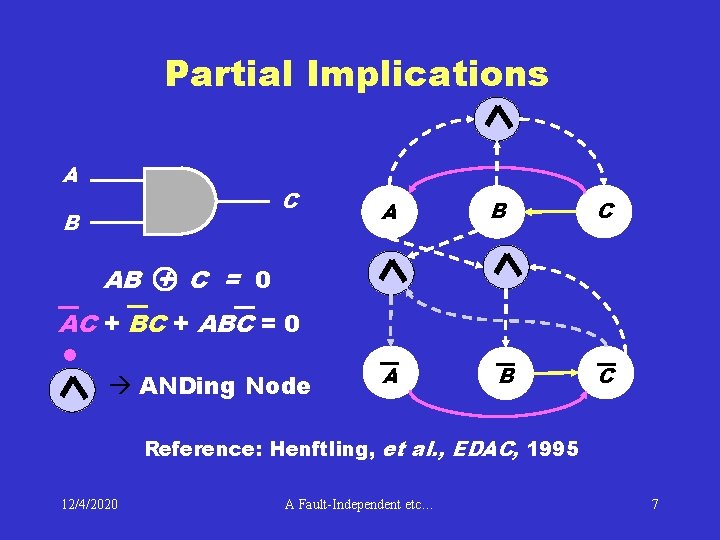

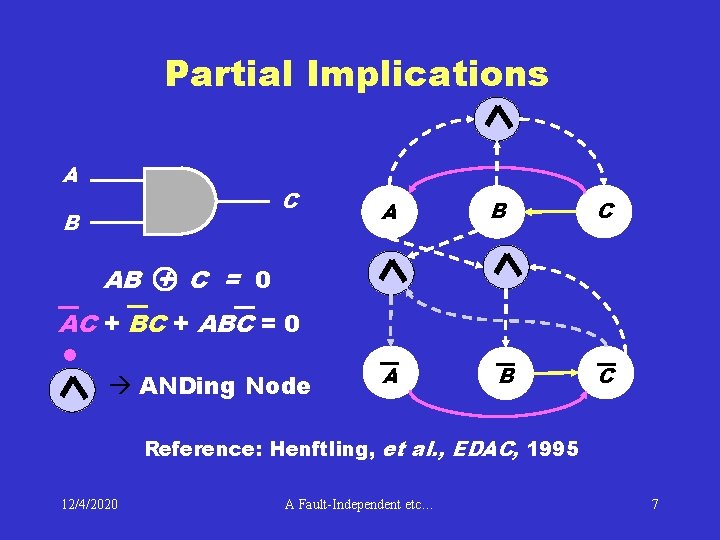

Partial Implications A C B A B C AB + C = 0 AC + BC + ABC = 0 • ANDing Node A B C Reference: Henftling, et al. , EDAC, 1995 12/4/2020 A Fault-Independent etc… 7

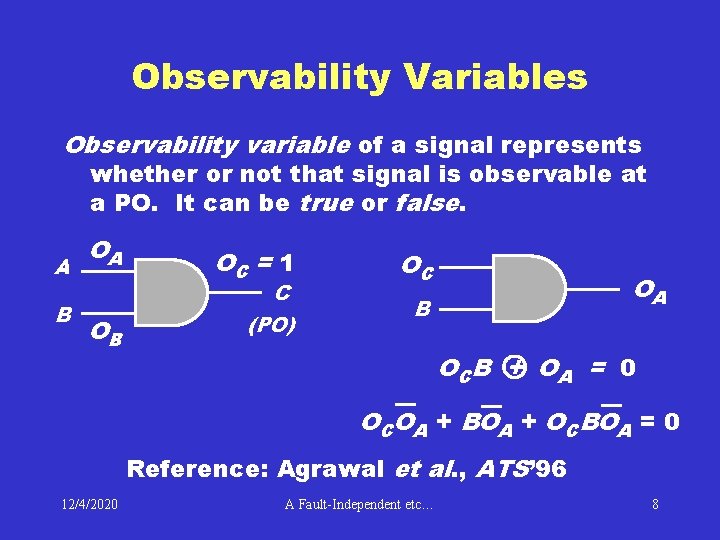

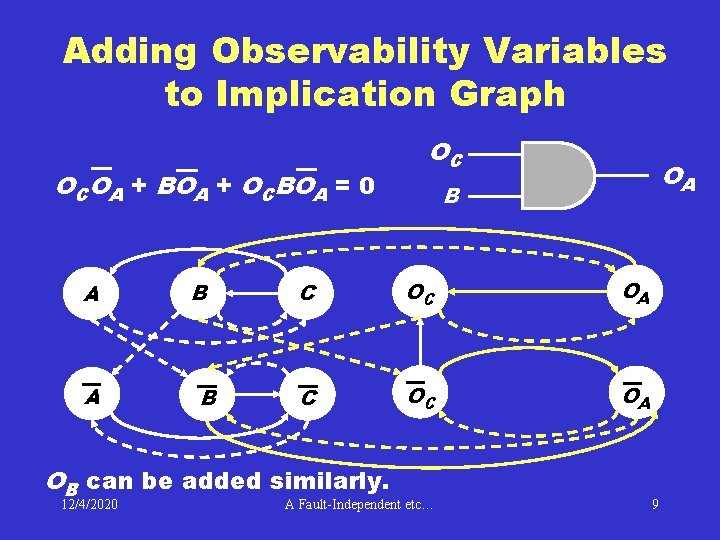

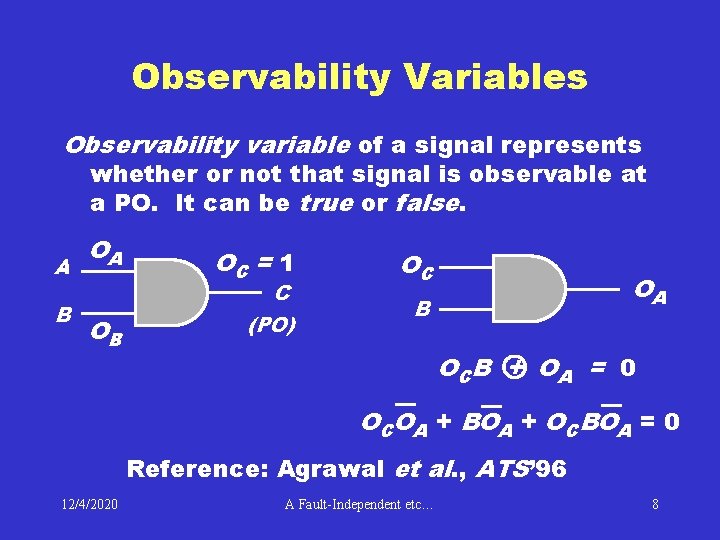

Observability Variables Observability variable of a signal represents whether or not that signal is observable at a PO. It can be true or false. A B OA OB OC = 1 C (PO) OC OA B OC B + O A = 0 OCOA + BOA + OCBOA = 0 Reference: Agrawal et al. , ATS’ 96 12/4/2020 A Fault-Independent etc… 8

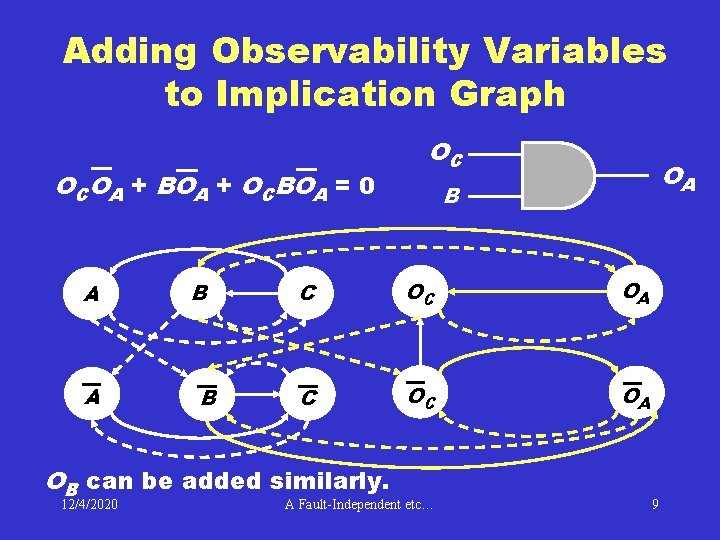

Adding Observability Variables to Implication Graph OCOA + BOA + OCBOA = 0 A A B B OA B C OC OA OB can be added similarly. 12/4/2020 OC A Fault-Independent etc… 9

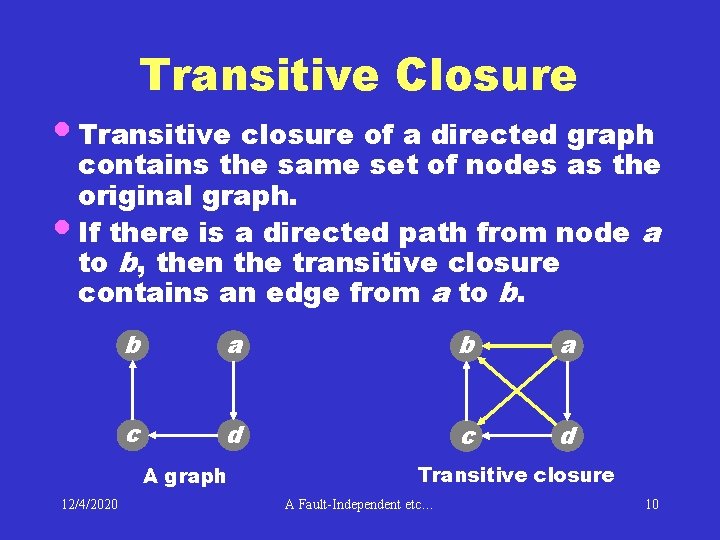

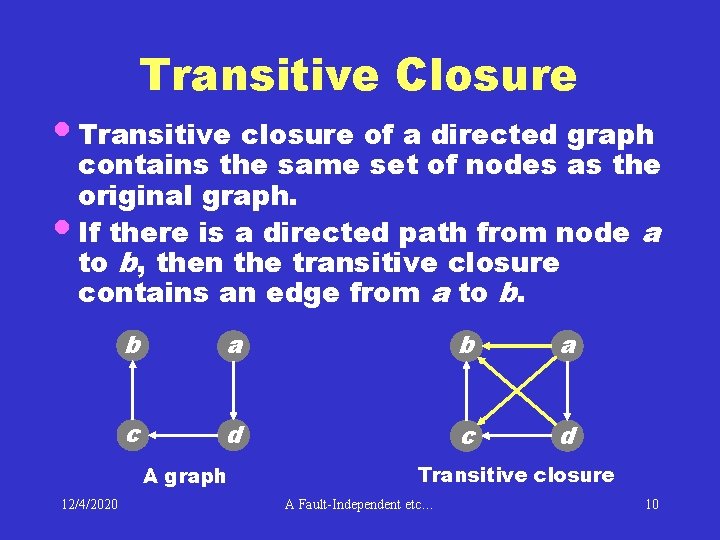

Transitive Closure • Transitive closure of a directed graph contains the same set of nodes as the original graph. • If there is a directed path from node a to b, then the transitive closure contains an edge from a to b. b a c d A graph 12/4/2020 Transitive closure A Fault-Independent etc… 10

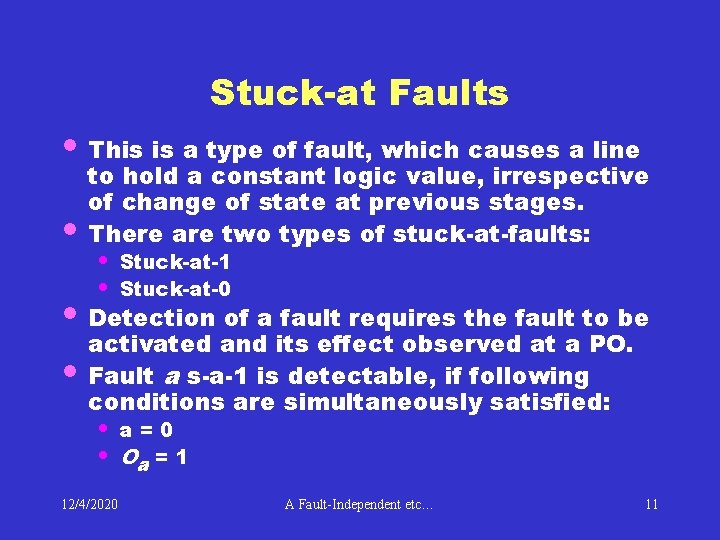

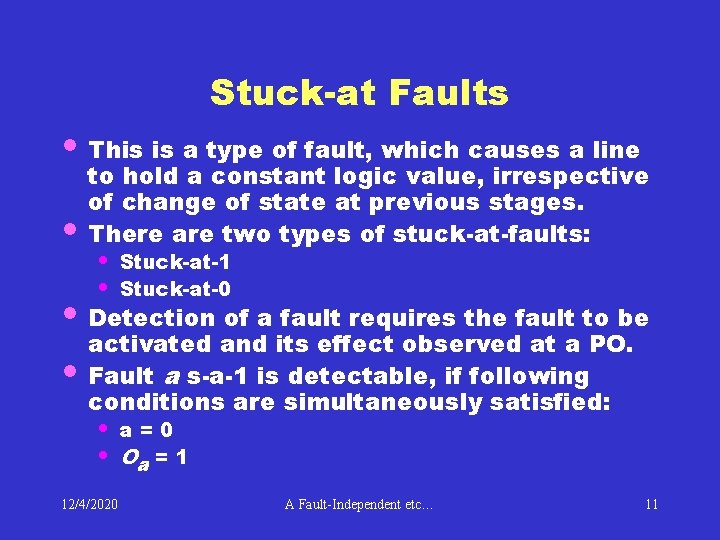

Stuck-at Faults • This is a type of fault, which causes a line • to hold a constant logic value, irrespective of change of state at previous stages. There are two types of stuck-at-faults: • • Stuck-at-1 Stuck-at-0 • Detection of a fault requires the fault to be • activated and its effect observed at a PO. Fault a s-a-1 is detectable, if following conditions are simultaneously satisfied: • a=0 • Oa = 1 12/4/2020 A Fault-Independent etc… 11

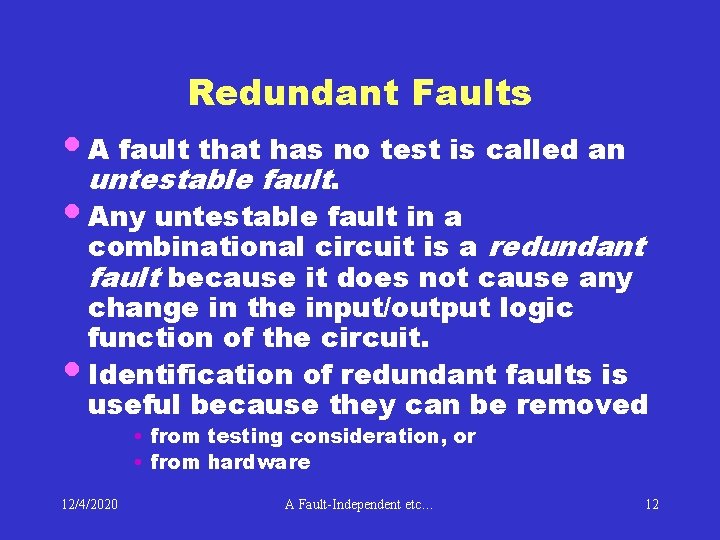

Redundant Faults • A fault that has no test is called an untestable fault. • Any untestable fault in a combinational circuit is a redundant fault because it does not cause any change in the input/output logic function of the circuit. • Identification of redundant faults is useful because they can be removed • from testing consideration, or • from hardware 12/4/2020 A Fault-Independent etc… 12

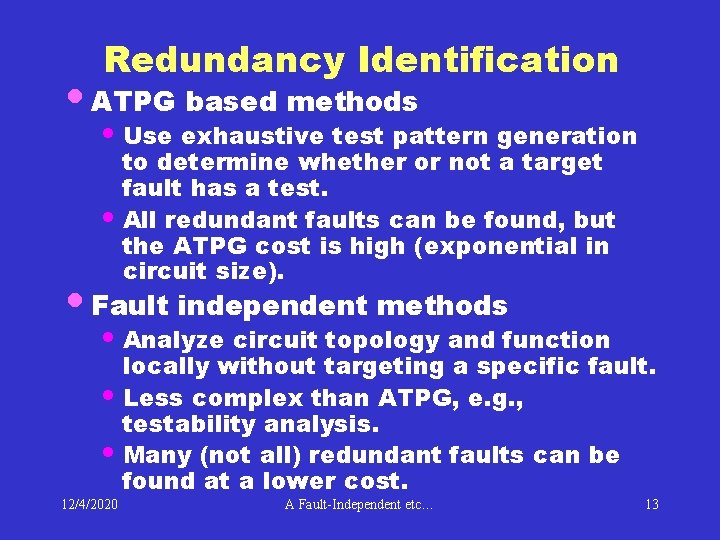

Redundancy Identification • ATPG based methods • Use exhaustive test pattern generation • to determine whether or not a target fault has a test. All redundant faults can be found, but the ATPG cost is high (exponential in circuit size). • Fault independent methods • Analyze circuit topology and function • • 12/4/2020 locally without targeting a specific fault. Less complex than ATPG, e. g. , testability analysis. Many (not all) redundant faults can be found at a lower cost. A Fault-Independent etc… 13

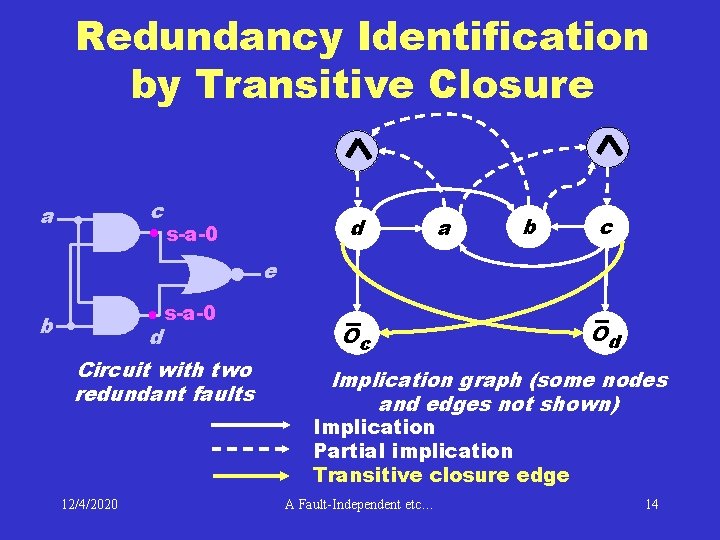

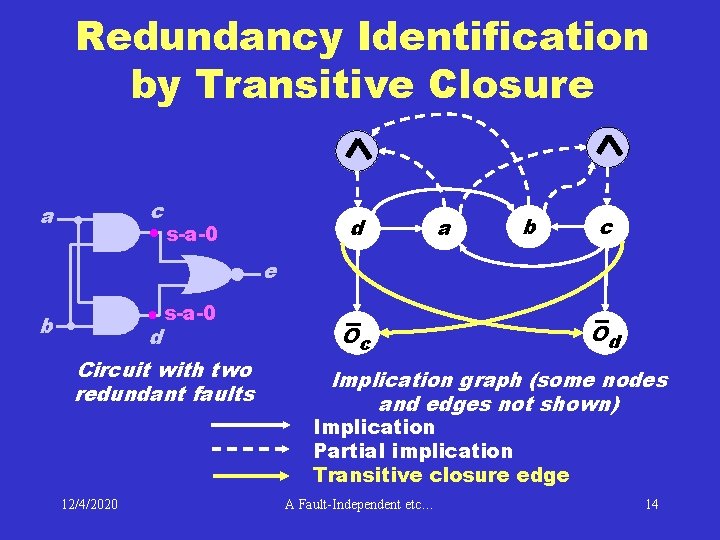

Redundancy Identification by Transitive Closure c a d s-a-0 a b c e b d s-a-0 Circuit with two redundant faults Oc Od Implication graph (some nodes and edges not shown) Implication Partial implication Transitive closure edge 12/4/2020 A Fault-Independent etc… 14

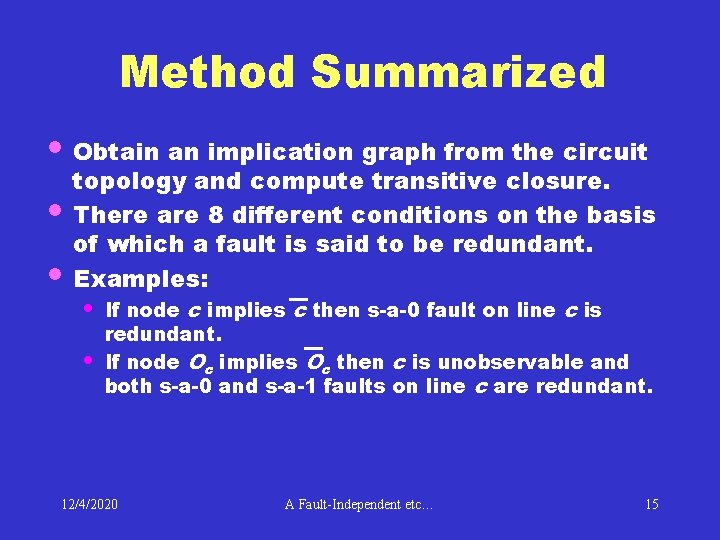

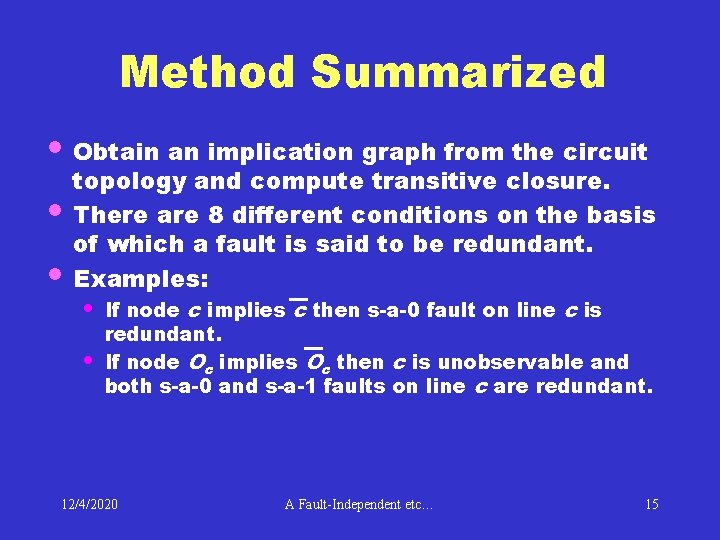

Method Summarized • Obtain an implication graph from the circuit • • topology and compute transitive closure. There are 8 different conditions on the basis of which a fault is said to be redundant. Examples: • • If node c implies c then s-a-0 fault on line c is redundant. If node Oc implies Oc then c is unobservable and both s-a-0 and s-a-1 faults on line c are redundant. 12/4/2020 A Fault-Independent etc… 15

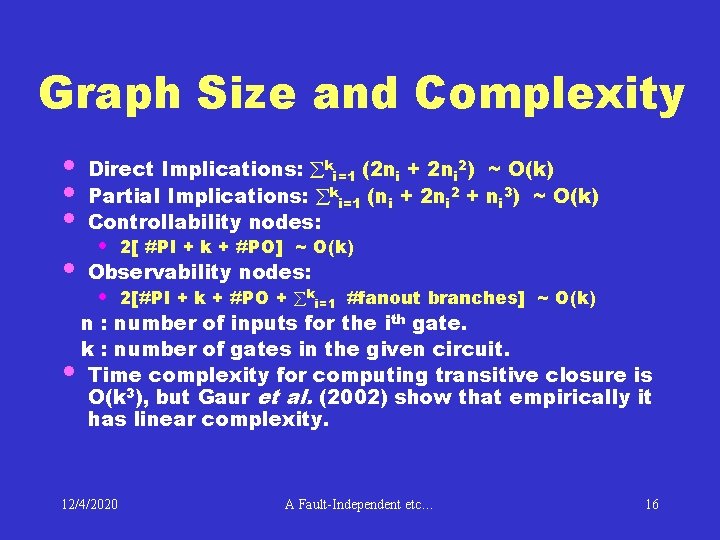

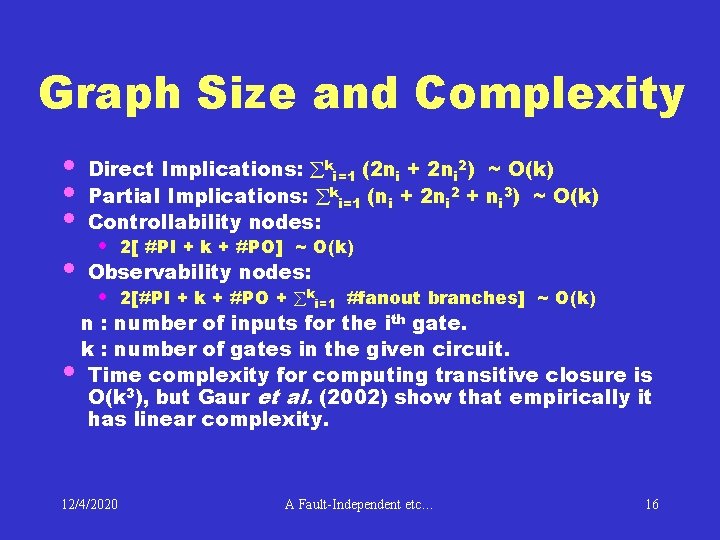

Graph Size and Complexity • • • Direct Implications: ki=1 (2 ni + 2 ni 2) ~ O(k) Partial Implications: ki=1 (ni + 2 ni 2 + ni 3) ~ O(k) Controllability nodes: • Observability nodes: • 2[ #PI + k + #PO] ~ O(k) • 2[#PI + k + #PO + ki=1 #fanout branches] ~ O(k) n : number of inputs for the ith gate. k : number of gates in the given circuit. • Time complexity for computing transitive closure is O(k 3), but Gaur et al. (2002) show that empirically it has linear complexity. 12/4/2020 A Fault-Independent etc… 16

Node Fixation • Node fixation occurs when a signal implies its own complement, or vice-versa. • Edges from all other nodes are added in the implication graph to model the unconditional fixation. 12/4/2020 A Fault-Independent etc… 17

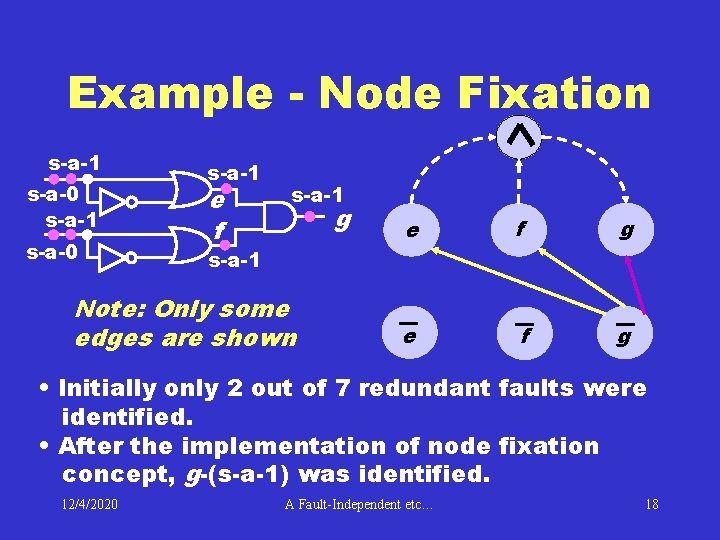

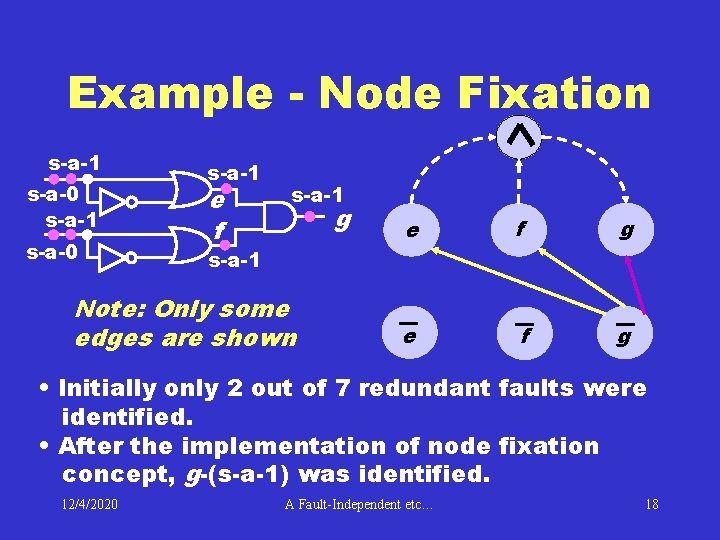

Example - Node Fixation s-a-1 s-a-0 s-a-1 e f s-a-1 g e f g s-a-1 Note: Only some edges are shown • Initially only 2 out of 7 redundant faults were identified. • After the implementation of node fixation concept, g-(s-a-1) was identified. 12/4/2020 A Fault-Independent etc… 18

Contrapositive Rule • If a signal p implies another signal q then q implies p (Zhao et al. VTS’ 97). • This rule gives more implications in the graph after the node fixation is implemented and we are yet to verify how many more redundant faults will be found. 12/4/2020 A Fault-Independent etc… 19

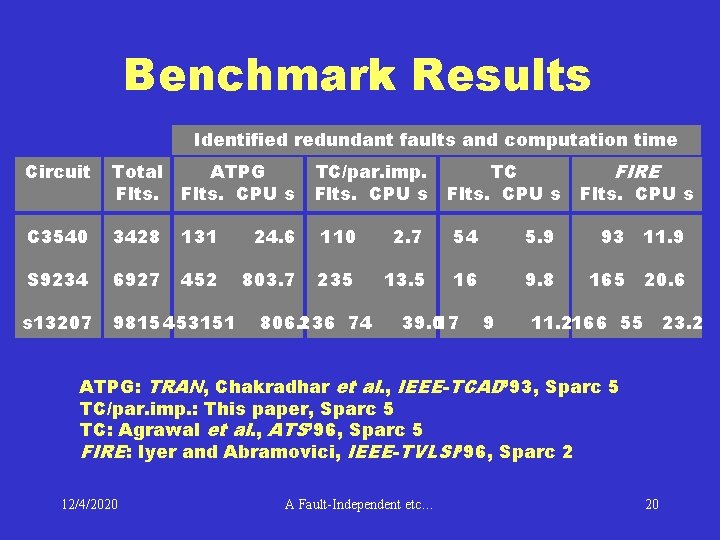

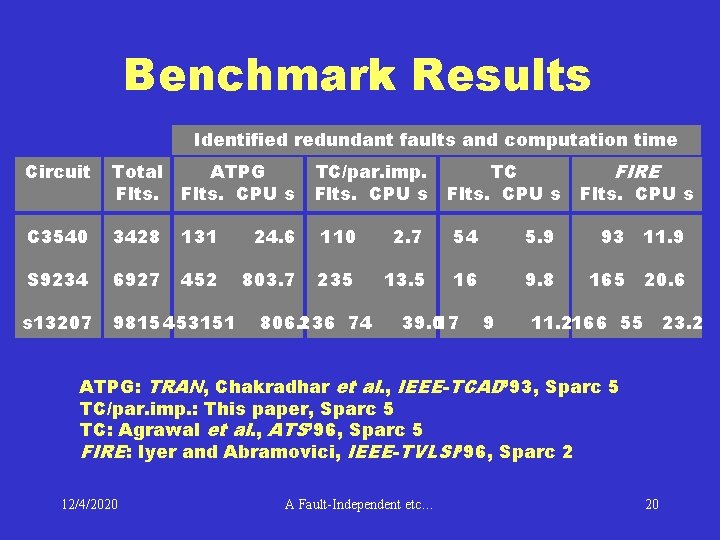

Benchmark Results Identified redundant faults and computation time TC/par. imp. Flts. CPU s Total Flts. ATPG Flts. CPU s C 3540 3428 131 24. 6 110 2. 7 54 5. 9 93 11. 9 S 9234 6927 452 803. 7 235 13. 5 16 9. 8 165 20. 6 s 13207 9815 453151 806. 5 236 74 TC Flts. CPU s FIRE Circuit 39. 0 17 9 Flts. CPU s 11. 2166 55 23. 2 ATPG: TRAN, Chakradhar et al. , IEEE-TCAD’ 93, Sparc 5 TC/par. imp. : This paper, Sparc 5 TC: Agrawal et al. , ATS’ 96, Sparc 5 FIRE: Iyer and Abramovici, IEEE-TVLSI’ 96, Sparc 2 12/4/2020 A Fault-Independent etc… 20

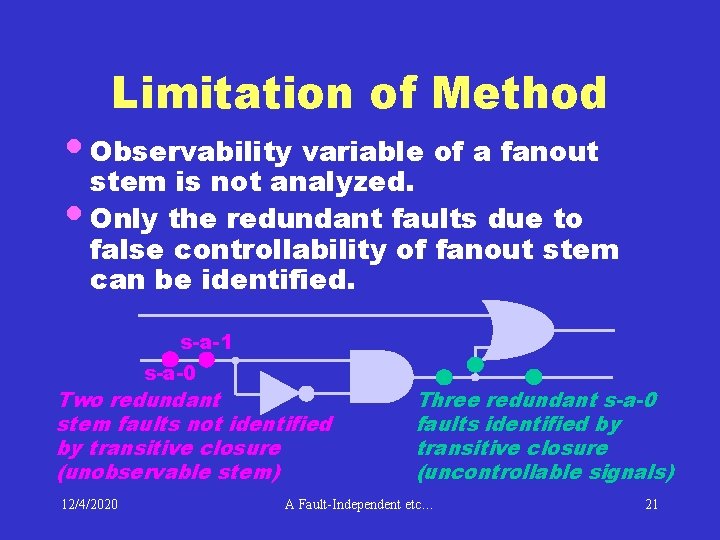

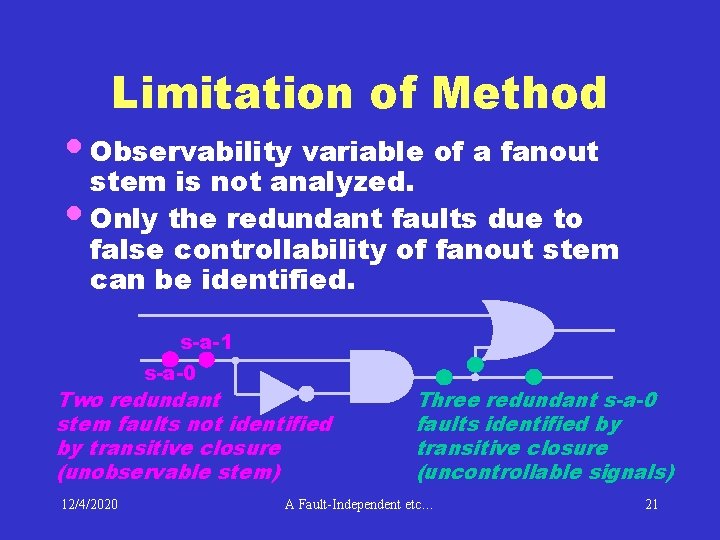

Limitation of Method • Observability variable of a fanout stem is not analyzed. • Only the redundant faults due to false controllability of fanout stem can be identified. s-a-1 s-a-0 Two redundant stem faults not identified by transitive closure (unobservable stem) 12/4/2020 Three redundant s-a-0 faults identified by transitive closure (uncontrollable signals) A Fault-Independent etc… 21

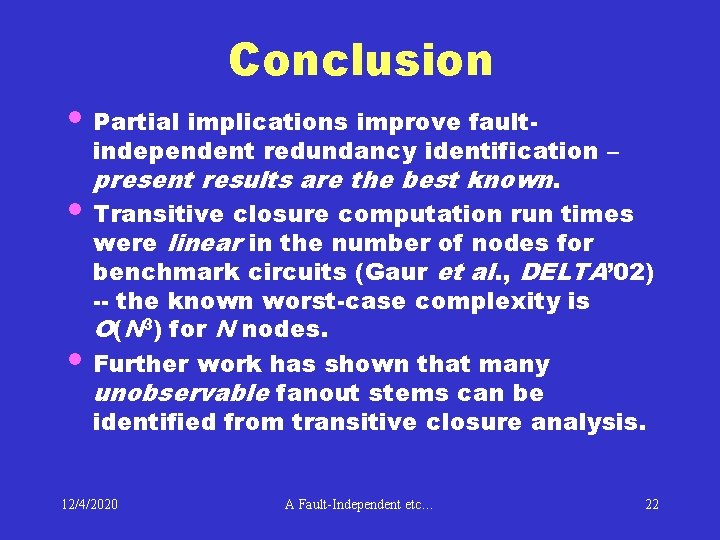

Conclusion • Partial implications improve fault • • independent redundancy identification – present results are the best known. Transitive closure computation run times were linear in the number of nodes for benchmark circuits (Gaur et al. , DELTA’ 02) -- the known worst-case complexity is O(N 3) for N nodes. Further work has shown that many unobservable fanout stems can be identified from transitive closure analysis. 12/4/2020 A Fault-Independent etc… 22

THANK YOU 12/4/2020 A Fault-Independent etc… 23